#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                    |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 4K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 28-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc502-i-ss |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

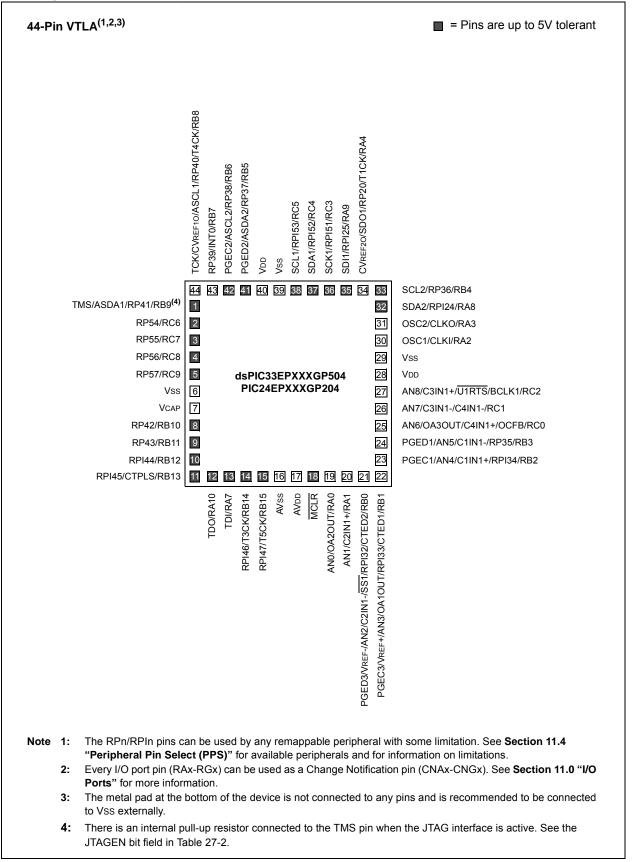

## **Pin Diagrams (Continued)**

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

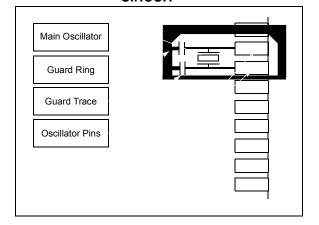

## 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator. For details, see **Section 9.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

# 3.6 CPU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

# 3.6.1 KEY RESOURCES

- "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

|                                               | Vector           | IRQ   |                   | Interrupt Bit Location |          |             |

|-----------------------------------------------|------------------|-------|-------------------|------------------------|----------|-------------|

| Interrupt Source                              | # #              |       | IVT Address       | Flag                   | Enable   | Priority    |

|                                               | I Order Priority |       |                   |                        |          |             |

| INT0 – External Interrupt 0                   | 8                | 0     | 0x000014          | IFS0<0>                | IEC0<0>  | IPC0<2:0>   |

| IC1 – Input Capture 1                         | 9                | 1     | 0x000016          | IFS0<1>                | IEC0<1>  | IPC0<6:4>   |

| OC1 – Output Compare 1                        | 10               | 2     | 0x000018          | IFS0<2>                | IEC0<2>  | IPC0<10:8>  |

| T1 – Timer1                                   | 11               | 3     | 0x00001A          | IFS0<3>                | IEC0<3>  | IPC0<14:12> |

| DMA0 – DMA Channel 0                          | 12               | 4     | 0x00001C          | IFS0<4>                | IEC0<4>  | IPC1<2:0>   |

| IC2 – Input Capture 2                         | 13               | 5     | 0x00001E          | IFS0<5>                | IEC0<5>  | IPC1<6:4>   |

| OC2 – Output Compare 2                        | 14               | 6     | 0x000020          | IFS0<6>                | IEC0<6>  | IPC1<10:8>  |

| T2 – Timer2                                   | 15               | 7     | 0x000022          | IFS0<7>                | IEC0<7>  | IPC1<14:12> |

| T3 – Timer3                                   | 16               | 8     | 0x000024          | IFS0<8>                | IEC0<8>  | IPC2<2:0>   |

| SPI1E – SPI1 Error                            | 17               | 9     | 0x000026          | IFS0<9>                | IEC0<9>  | IPC2<6:4>   |

| SPI1 – SPI1 Transfer Done                     | 18               | 10    | 0x000028          | IFS0<10>               | IEC0<10> | IPC2<10:8>  |

| U1RX – UART1 Receiver                         | 19               | 11    | 0x00002A          | IFS0<11>               | IEC0<11> | IPC2<14:12> |

| U1TX – UART1 Transmitter                      | 20               | 12    | 0x00002C          | IFS0<12>               | IEC0<12> | IPC3<2:0>   |

| AD1 – ADC1 Convert Done                       | 21               | 13    | 0x00002E          | IFS0<13>               | IEC0<13> | IPC3<6:4>   |

| DMA1 – DMA Channel 1                          | 22               | 14    | 0x000030          | IFS0<14>               | IEC0<14> | IPC3<10:8>  |

| Reserved                                      | 23               | 15    | 0x000032          |                        |          | _           |

| SI2C1 – I2C1 Slave Event                      | 24               | 16    | 0x000034          | IFS1<0>                | IEC1<0>  | IPC4<2:0>   |

| MI2C1 – I2C1 Master Event                     | 25               | 17    | 0x000036          | IFS1<1>                | IEC1<1>  | IPC4<6:4>   |

| CM – Comparator Combined Event                | 26               | 18    | 0x000038          | IFS1<2>                | IEC1<2>  | IPC4<10:8>  |

| CN – Input Change Interrupt                   | 27               | 19    | 0x00003A          | IFS1<3>                | IEC1<3>  | IPC4<14:12> |

| INT1 – External Interrupt 1                   | 28               | 20    | 0x00003C          | IFS1<4>                | IEC1<4>  | IPC5<2:0>   |

| Reserved                                      | 29-31            | 21-23 | 0x00003E-0x000042 |                        |          | _           |

| DMA2 – DMA Channel 2                          | 32               | 24    | 0x000044          | IFS1<8>                | IEC1<8>  | IPC6<2:0>   |

| OC3 – Output Compare 3                        | 33               | 25    | 0x000046          | IFS1<9>                | IEC1<9>  | IPC6<6:4>   |

| OC4 – Output Compare 4                        | 34               | 26    | 0x000048          | IFS1<10>               | IEC1<10> | IPC6<10:8>  |

| T4 – Timer4                                   | 35               | 27    | 0x00004A          | IFS1<11>               | IEC1<11> | IPC6<14:12> |

| T5 – Timer5                                   | 36               | 28    | 0x00004C          | IFS1<12>               | IEC1<12> | IPC7<2:0>   |

| INT2 – External Interrupt 2                   | 37               | 29    | 0x00004E          | IFS1<13>               | IEC1<13> | IPC7<6:4>   |

| U2RX – UART2 Receiver                         | 38               | 30    | 0x000050          | IFS1<14>               | IEC1<14> | IPC7<10:8>  |

| U2TX – UART2 Transmitter                      | 39               | 31    | 0x000052          | IFS1<15>               | IEC1<15> | IPC7<14:12> |

| SPI2E – SPI2 Error                            | 40               | 32    | 0x000054          | IFS2<0>                | IEC2<0>  | IPC8<2:0>   |

| SPI2 – SPI2 Transfer Done                     | 41               | 33    | 0x000056          | IFS2<1>                | IEC2<1>  | IPC8<6:4>   |

| C1RX – CAN1 RX Data Ready <sup>(1)</sup>      | 42               | 34    | 0x000058          | IFS2<2>                | IEC2<2>  | IPC8<10:8>  |

| C1 – CAN1 Event <sup>(1)</sup>                | 43               | 35    | 0x00005A          | IFS2<3>                | IEC2<3>  | IPC8<14:12> |

| DMA3 – DMA Channel 3                          | 44               | 36    | 0x00005C          | IFS2<4>                | IEC2<4>  | IPC9<2:0>   |

| IC3 – Input Capture 3                         | 45               | 37    | 0x00005E          | IFS2<5>                | IEC2<5>  | IPC9<6:4>   |

| IC4 – Input Capture 4                         | 46               | 38    | 0x000060          | IFS2<6>                | IEC2<6>  | IPC9<10:8>  |

| Reserved                                      | 47-56            | 39-48 | 0x000062-0x000074 | —                      | —        | —           |

| SI2C2 – I2C2 Slave Event                      | 57               | 49    | 0x000076          | IFS3<1>                | IEC3<1>  | IPC12<6:4>  |

| MI2C2 – I2C2 Master Event                     | 58               | 50    | 0x000078          | IFS3<2>                | IEC3<2>  | IPC12<10:8> |

| Reserved                                      | 59-64            | 51-56 | 0x00007A-0x000084 |                        | _        |             |

| PSEM – PWM Special Event Match <sup>(2)</sup> | 65               | 57    | 0x000086          | IFS3<9>                | IEC3<9>  | IPC14<6:4>  |

## TABLE 7-1: INTERRUPT VECTOR DETAILS

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

2: This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

# REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 4 | MATHERR: Math Error Status bit                                                                        |

|-------|-------------------------------------------------------------------------------------------------------|

|       | 1 = Math error trap has occurred                                                                      |

|       | 0 = Math error trap has not occurred                                                                  |

| bit 3 | ADDRERR: Address Error Trap Status bit                                                                |

|       | <ul><li>1 = Address error trap has occurred</li><li>0 = Address error trap has not occurred</li></ul> |

| bit 2 | STKERR: Stack Error Trap Status bit                                                                   |

|       | 1 = Stack error trap has occurred                                                                     |

|       | 0 = Stack error trap has not occurred                                                                 |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit                                                    |

|       | 1 = Oscillator failure trap has occurred                                                              |

|       | 0 = Oscillator failure trap has not occurred                                                          |

| bit 0 | Unimplemented: Read as '0'                                                                            |

Note 1: These bits are available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER 7-5: | INTCON3: INTERRUPT CONTROL REGISTER 3 |

|---------------|---------------------------------------|

| U-0          | U-0          | U-0             | U-0              | U-0                                     | U-0              | U-0    | U-0   |

|--------------|--------------|-----------------|------------------|-----------------------------------------|------------------|--------|-------|

|              | —            | _               | —                | —                                       | —                | —      | _     |

| bit 15       |              |                 |                  |                                         |                  | •      | bit 8 |

|              |              |                 |                  |                                         |                  |        |       |

| U-0          | U-0          | R/W-0           | R/W-0            | U-0                                     | U-0              | U-0    | U-0   |

| —            | —            | DAE             | DOOVR            | —                                       | —                | —      | —     |

| bit 7        |              |                 |                  |                                         |                  |        | bit 0 |

|              |              |                 |                  |                                         |                  |        |       |

| Legend:      |              |                 |                  |                                         |                  |        |       |

| R = Readab   | le bit       | W = Writable    | bit              | U = Unimplei                            | mented bit, read | as '0' |       |

| -n = Value a | It POR       | '1' = Bit is se | t                | '0' = Bit is cleared x = Bit is unknown |                  |        | nown  |

|              |              |                 |                  |                                         |                  |        |       |

| bit 15-6     | Unimplemen   | ted: Read as    | '0'              |                                         |                  |        |       |

| bit 5        | DAE: DMA A   | ddress Error S  | Soft Trap Status | s bit                                   |                  |        |       |

|              | 1 = DMA add  | ress error soft | trap has occur   | red                                     |                  |        |       |

|              | 0 = DMA add  | ress error soft | trap has not o   | ccurred                                 |                  |        |       |

| bit 4        | DOOVR: DO    | Stack Overflov  | v Soft Trap Sta  | tus bit                                 |                  |        |       |

|              | 1 = DO stack | overflow soft t | rap has occurre  | ed                                      |                  |        |       |

| I = D0 | Stack Overnow  | 3011 11 ap 11 a3 | occurred     |

|--------|----------------|------------------|--------------|

| 0 = DO | stack overflow | soft trap has    | not occurred |

| bit 3-0 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

# REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|-----|-----|-----|-----|-----|-----|-------|

| —       | —   | —   | —   | —   | —   | —   | —     |

| bit 15  |     |     |     |     | •   |     | bit 8 |

|         |     |     |     |     |     |     |       |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

| _       | _   | —   |     | —   | —   | —   | SGHT  |

| bit 7   |     |     |     |     | •   |     | bit 0 |

|         |     |     |     |     |     |     |       |

| Legend: |     |     |     |     |     |     |       |

| 3                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

|                   |                  |                        |                    |

bit 0

SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

| R/W-0         | R/W-0        | R/W-0                                                 | R/W-0   | R/W-0             | R/W-0                 | R/W-0                | U-0   |

|---------------|--------------|-------------------------------------------------------|---------|-------------------|-----------------------|----------------------|-------|

| T5MD          | T4MD         | T3MD                                                  | T2MD    | T1MD              | QEI1MD <sup>(1)</sup> | PWMMD <sup>(1)</sup> | _     |

| bit 15        |              |                                                       |         |                   |                       |                      | bit   |

|               |              |                                                       |         |                   |                       |                      |       |

| R/W-0         | R/W-0        | R/W-0                                                 | R/W-0   | R/W-0             | U-0                   | R/W-0                | R/W-0 |

| I2C1MD        | U2MD         | U1MD                                                  | SPI2MD  | SPI1MD            | —                     | C1MD <sup>(2)</sup>  | AD1MD |

| bit 7         |              |                                                       |         |                   |                       |                      | bit   |

| Legend:       |              |                                                       |         |                   |                       |                      |       |

| R = Readabl   | e bit        | W = Writable                                          | bit     | U = Unimplen      | nented bit, read      | d as '0'             |       |

| -n = Value at | POR          | '1' = Bit is set                                      |         | '0' = Bit is clea | ared                  | x = Bit is unkno     | own   |

| bit 15        | 1 = Timer5 m | 5 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 14        | 1 = Timer4 m | 4 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 13        | 1 = Timer3 m | 3 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 12        | 1 = Timer2 m | 2 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 11        | 1 = Timer1 m | 1 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 10        | 1 = QEI1 mod | 11 Module Disa<br>Iule is disablec<br>Iule is enabled |         |                   |                       |                      |       |

| bit 9         | 1 = PWM mod  | /M Module Dis<br>dule is disabled<br>dule is enabled  | 1       |                   |                       |                      |       |

| bit 8         | Unimplemen   | ted: Read as '                                        | כי      |                   |                       |                      |       |

| bit 7         | 1 = I2C1 mod | 1 Module Disal<br>ule is disabled<br>ule is enabled   | ble bit |                   |                       |                      |       |

| bit 6         | 1 = UART2 m  | 2 Module Disa<br>odule is disabl<br>odule is enable   | ed      |                   |                       |                      |       |

| bit 5         | 1 = UART1 m  | 1 Module Disa<br>odule is disabl<br>odule is enable   | ed      |                   |                       |                      |       |

| bit 4         | 1 = SPI2 mod | 2 Module Disa<br>lule is disabled<br>lule is enabled  | ole bit |                   |                       |                      |       |

# REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This bit is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

| U-0       R/W-0       R/W       R/W       R/W       R/W <th>R/W-0</th> <th>R/W-0</th> <th>R/W-0</th> <th>R/W-0</th> <th>R/W-0</th> <th>R/W-0</th> <th>U-0</th> <th>U-0</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0         | R/W-0                                                                                                                                                                                   | R/W-0              | R/W-0              | R/W-0             | R/W-0            | U-0             | U-0           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|-------------------|------------------|-----------------|---------------|

| U-0       U-0       RW-0       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PHR           | PHF                                                                                                                                                                                     | PLR                | PLF                | FLTLEBEN          | CLLEBEN          | —               |               |

| -         BCH <sup>(1)</sup> BCL <sup>(1)</sup> BPH         BPHL         BPLH         BE         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 15        |                                                                                                                                                                                         |                    |                    |                   |                  |                 | bit           |

| bit 7       t         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PHR: PWMxH Rising Edge Trigger Enable bit       1 = Rising edge of PWMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PWMxH         bit 14       PHF: PWMxH Falling Edge Trigger Enable bit       1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores rising edge of PWMxL       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL       1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking is applied to selected Fault input       1 = Leading-Edge Blanking is applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected Current-limit input       0 = Leading-Edge Blanking is applied to selected current-limit input         0 = Leading-Edge Blanking is applied to selected current-limit input       0 = Leading-Edge Blanking is applied to selected current-limit input         0 = Leading-Edge Blanking is applied to selected Current-limit input       0 = Leading-Edge Blanking is applied to sel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0           | U-0                                                                                                                                                                                     | R/W-0              | R/W-0              | R/W-0             | R/W-0            | R/W-0           | R/W-0         |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>nn = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 PHR: PWMxH Rising Edge Trigger Enable bit<br>1 = Rising edge of PWMxH will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxH<br>1 = Falling edge of PWMxH will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxH<br>1 = Falling edge of PWMxH will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores falling edge of PWMxH<br>1 = Rising edge of PWMxH will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxL<br>1 = Rising edge of PWMxL will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxL<br>1 = Falling edge of PWMxL will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxL<br>1 = Falling edge of PWMxL will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores falling edge of PWMxL<br>1 = Falling edge of PWMxL will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores falling edge of PWMxL<br>1 = Leading-Edge Blanking is applied to selected Fault input<br>0 = Leading-Edge Blanking is applied to selected Fault input<br>1 = Leading-Edge Blanking is applied to selected Current-limit input<br>1 = Leading-Edge Blanking is not applied to selected current-limit input<br>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high<br>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low<br>0 = No blanking when selected blanking signal Low Enable bit<br>1 = State blanking (of current-limit and/or Fault input signals) when Selected blanking signal is low<br>0 = No blanking when PWMxH dupt is high<br>0 = No blanking when PWMxH dupt signals) when PWMxH output is high<br>0 = No blanking when PWMxH tow Enable bit<br>1 = State blanking (of current-limit and/ | _             | _                                                                                                                                                                                       | BCH <sup>(1)</sup> | BCL <sup>(1)</sup> | BPHH              | BPHL             | BPLH            | BPLL          |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PHR: PWMxH Rising Edge Trigger Enable bit       1 = Rising edge of PWMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PWMxH         bit 14       PHF: PWMxH Falling Edge Trigger Enable bit       1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores falling edge of PWMxH         bit 13       PLR: PWMxL Rising Edge Trigger Enable bit       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PWMxL         bit 13       PLR: PWMxL Falling Edge Trigger Enable bit       1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking is not applied to selected Fault input         bit 11       FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit       1 = Leading-Edge Blanking is not applied to selected current-limit input         bit 5       BCH: Blanking is not applied to selected current-limit input       0 = Leading-Edge Blanking is not applied to selected current-limit input         bit 9-6       Unimplemented: Read as '0'       1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high         bit 4       BCL: Blanking in Selected Blanking signal is high       1 = State blanking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 7         |                                                                                                                                                                                         |                    |                    |                   |                  |                 | bit           |

| n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PHR: PWMxH Rising Edge Trigger Enable bit       1 = Rising edge of PWMxH will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores rising edge of PWMxH       11 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxH       11 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores fising edge of PWMxL       0 = Leading-Edge Blanking ignores falling edge of PWMxL         bit 12       PLF: PWMxL Falling Edge Trigger Enable bit       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL       0 = Leading-Edge Blanking ignores falling edge of PWMxL         bit 11       FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit       1 = Leading-Edge Blanking is not applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected Fault input       0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input       0 = Leading-Edge Blanking signal Figh Enable bit         1 = State blanking in Selected Blanking Singal High Enable bit <sup>(1)</sup> 1 = State blanking in Sel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Legend:       |                                                                                                                                                                                         |                    |                    |                   |                  |                 |               |

| <ul> <li>PHR: PWMxH Rising Edge Trigger Enable bit         <ol> <li>Rising edge of PWMxH will trigger Leading-Edge Blanking counter</li></ol></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R = Readabl   | e bit                                                                                                                                                                                   | W = Writable       | bit                | U = Unimpler      | mented bit, read | as '0'          |               |

| <ul> <li>1 = Rising edge of PWMxH will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxH</li> <li>PHF: PWMxH Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxH</li> <li>PLR: PVMxL Rising Edge Trigger Enable bit</li> <li>1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>PLF: PWMxL Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>Det Leading-Edge Blanking ignores ralling edge of PWMxL</li> <li>D = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking Signal High Enable bit</li> <li>1 = Leading-Edge Blanking Signal Liph Enable bit<sup>(1)</sup></li> <li>1 = State blanking (or current-limit and/or Fault input signals) when selected blanking signal is high</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> <li>0 = No b</li></ul>                                                                                                                                                                | -n = Value at | POR                                                                                                                                                                                     | '1' = Bit is set   | :                  | '0' = Bit is cle  | ared             | x = Bit is unkr | nown          |

| <ul> <li>1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxH</li> <li>bit 13 PLR: PWMxL Rising Edge Trigger Enable bit</li> <li>1 = Rising edge of PWMxL. will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>bit 12 PLF: PWMxL Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxL. will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxL</li> <li>bit 12 FLTLEBEN: Fault Input Leading-Edge Blanking Counter</li> <li>0 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when PWMxH output is nigh</li> <li>0 = No bla</li></ul>                                                                                                                                                                 | bit 15        | 1 = Rising ed                                                                                                                                                                           | ge of PWMxH        | will trigger Le    | ading-Edge Bla    |                  |                 |               |

| <ul> <li>1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>pLF: PWMxL Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxL</li> <li>bit 11</li> <li>FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit</li> <li>1 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = No blanking when selected Blanking Signal Low Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when PWMxH dutput is high</li> <li>0 = No blanking when PWMxH Low Enable bit</li> <li>1 = State blanking (of</li></ul>                                                                                                                                                         | bit 14        | 1 = Falling ed                                                                                                                                                                          | lge of PWMxH       | will trigger Le    | eading-Edge Bla   | 0                |                 |               |

| bit 12       PLF: PWMxL Falling Edge Trigger Enable bit         1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL         bit 11       FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit         1 = Leading-Edge Blanking is not applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected Fault input         0 = Leading-Edge Blanking is applied to selected Fault input         0 = Leading-Edge Blanking is applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = No blanking when selected Blanking signal Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low         0 = No blanking when P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 13        | 1 = Rising ed                                                                                                                                                                           | ge of PWMxL        | will trigger Le    | ading-Edge Bla    |                  |                 |               |

| <ul> <li>1 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>1 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxL output is low</li> <li>0 = No blanking when PWMxL output is low</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li></ul>                                                                                                                                                             | bit 12        | 1 = Falling ed                                                                                                                                                                          | lge of PWMxL       | will trigger Le    | ading-Edge Bla    |                  |                 |               |

| <ul> <li>1 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>bit 9-6</li> <li>Unimplemented: Read as '0'</li> <li>bit 5</li> <li>BCH: Blanking in Selected Blanking Signal High Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is hig</li> <li>0 = No blanking when selected blanking Signal Low Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is hig</li> <li>bit 4</li> <li>BCL: Blanking in Selected Blanking Signal Low Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is low</li> <li>0 = No blanking when PWMxL output is low</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxL Ligh Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking in PWMxL Low Enable bit</li> <li>1 = State blanking in PWMxL Low Enable bit</li> <li>1 = State blanking in PWMxL output is high</li> </ul>                                                                                                                                                                                                 | bit 11        | 1 = Leading-E                                                                                                                                                                           | Edge Blanking      | is applied to      | selected Fault in | nput             |                 |               |

| bit 5       BCH: Blanking in Selected Blanking Signal High Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high         bit 4       BCL: Blanking in Selected Blanking Signal Low Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low         bit 4       BCL: Blanking in Selected Blanking Signal Low Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low         bit 3       BPHH: Blanking in PWMxH High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high         0 = No blanking when PWMxH output is high         bit 2       BPHL: Blanking in PWMxH Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low         0 = No blanking when PWMxH output is low         bit 1       State blanking in PWMxH Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low         0 = No blanking when PWMxL output is low         bit 1       BPLH: Blanking in PWMxL High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high         0 = No blanking when PWMxL output is high         bit 0       BPLL: Blanking in PWMxL Low Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 10        | 1 = Leading-E                                                                                                                                                                           | Edge Blanking      | is applied to      | selected current  | t-limit input    |                 |               |

| <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is hig</li> <li>0 = No blanking when selected blanking signal Low Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking in PWMxH High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> <li>0 = No blanking in PWMxH High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>0 = No blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 1 BPLH: Blanking in PWMxL High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is low</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit 9-6       | Unimplemen                                                                                                                                                                              | ted: Read as '     | 0'                 |                   |                  |                 |               |

| <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>BPHH: Blanking in PWMxH High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> <li>bit 2</li> <li>BPHL: Blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxL High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxL High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>bit 0</li> <li>BPLL: Blanking in PWMxL Low Enable bit</li> <li>1 = State blanking when PWMxL output is high</li> <li>bit 0</li> <li>BPLL: Blanking in PWMxL Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 5         | 1 = State blar                                                                                                                                                                          | nking (of currer   | nt-limit and/or    | Fault input sigr  |                  | cted blanking s | ignal is high |

| <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> <li>bit 2</li> <li>BPHL: Blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxL High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>bit 1</li> <li>BPLH: Blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>bit 0</li> <li>BPLL: Blanking in PWMxL Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | bit 4         | <b>BCL:</b> Blanking in Selected Blanking Signal Low Enable bit <sup>(1)</sup><br>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low |                    |                    |                   |                  |                 | ignal is low  |

| 1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low         0 = No blanking when PWMxH output is low         bit 1       BPLH: Blanking in PWMxL High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high         0 = No blanking when PWMxL output is high         0 = No blanking when PWMxL output is high         bit 0       BPLL: Blanking in PWMxL Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 3         | <b>BPHH:</b> Blanking in PWMxH High Enable bit<br>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high                                            |                    |                    |                   |                  |                 |               |

| bit 1       BPLH: Blanking in PWMxL High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high         0 = No blanking when PWMxL output is high         bit 0       BPLL: Blanking in PWMxL Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 2         | 1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low                                                                                               |                    |                    |                   |                  |                 |               |

| bit 0 <b>BPLL:</b> Blanking in PWMxL Low Enable bit<br>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 1         | <b>BPLH:</b> Blanking in PWMxL High Enable bit<br>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high                                            |                    |                    |                   |                  |                 | gh            |

| $\sim$ i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 0         | <b>BPLL:</b> Blanking in PWMxL Low Enable bit<br>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is low                                              |                    |                    |                   |                  |                 |               |

# REGISTER 16-16: LEBCONX: PWMx LEADING-EDGE BLANKING CONTROL REGISTER

Note 1: The blanking signal is selected via the BLANKSELx bits in the AUXCONx register.

# 21.2 Modes of Operation

The ECAN module can operate in one of several operation modes selected by the user. These modes include:

- · Initialization mode

- Disable mode

- Normal Operation mode

- · Listen Only mode

- Listen All Messages mode

- Loopback mode

Modes are requested by setting the REQOP<2:0> bits (CxCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CxCTRL1<7:5>). The module does not change the mode and the OPMODEx bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

## 21.3 ECAN Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 21.3.1 KEY RESOURCES

- "Enhanced Controller Area Network (ECAN™)" (DS70353) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- · Development Tools

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X