Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 25                                                                               |

| Program Memory Size        | 64KB (22K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 4K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

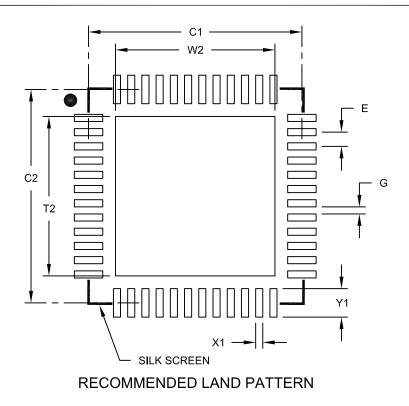

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 36-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 36-VTLA (5x5)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc503t-e-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

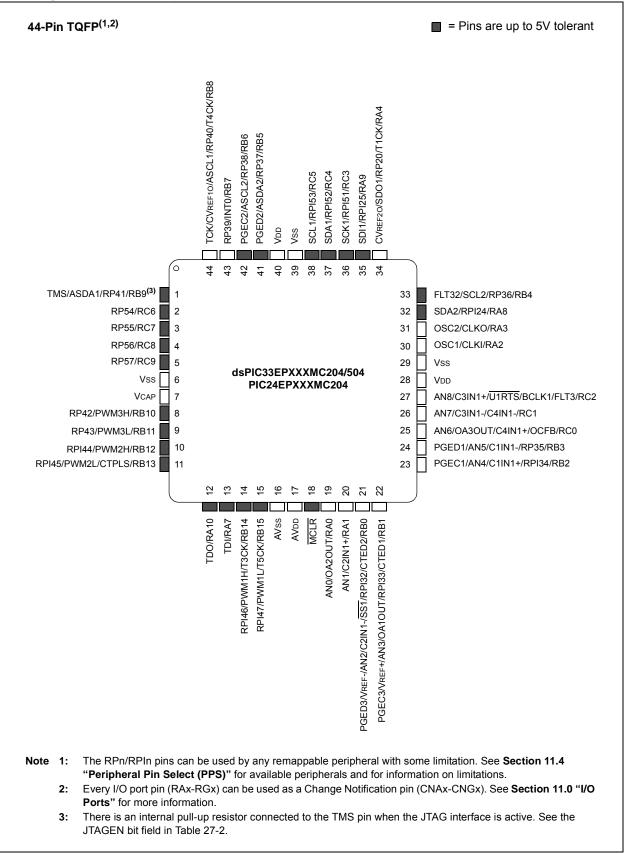

#### Pin Diagrams (Continued)

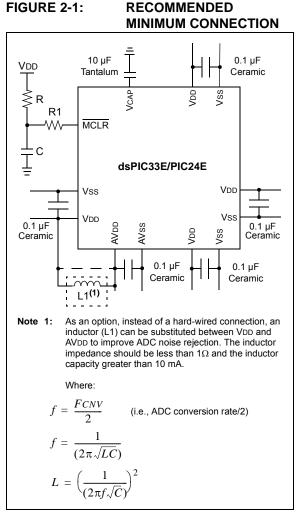

#### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

#### 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 1 Ohm) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor greater than 4.7  $\mu$ F (10  $\mu$ F is recommended), 16V connected to ground. The type can be ceramic or tantalum. See **Section 30.0** "**Electrical Characteristics**" for additional information.

The placement of this capacitor should be close to the VCAP pin. It is recommended that the trace length not exceeds one-quarter inch (6 mm). See **Section 27.3 "On-Chip Voltage Regulator"** for details.

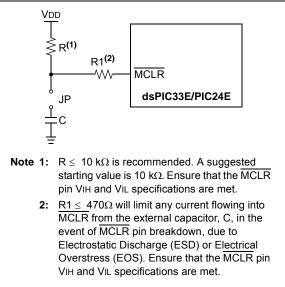

# 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor, C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components as shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

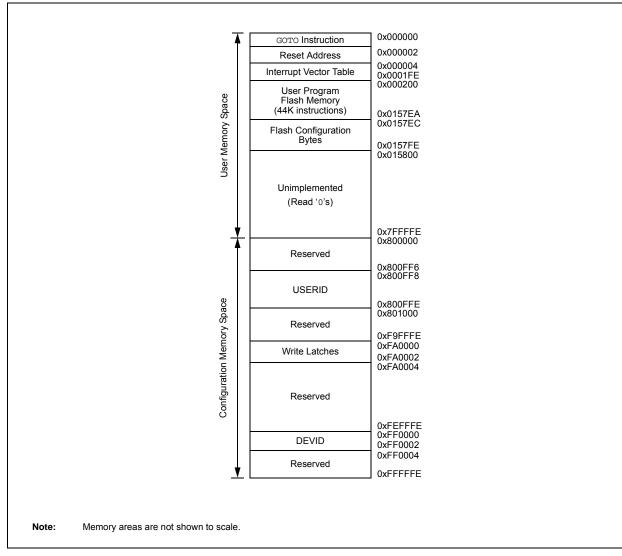

#### FIGURE 4-3: PROGRAM MEMORY MAP FOR dsPIC33EP128GP50X, dsPIC33EP128MC20X/50X AND PIC24EP128GP/MC20X DEVICES

| IABLE 4   | -14:  | PVVIVI G | ENERA  | IUR Z R | EGIST               |          | FOR as  | PIC33EP  |            | 202/202  |         | 16246   | PXXX    |          |         | CES ONL | _ T     |               |

|-----------|-------|----------|--------|---------|---------------------|----------|---------|----------|------------|----------|---------|---------|---------|----------|---------|---------|---------|---------------|

| File Name | Addr. | Bit 15   | Bit 14 | Bit 13  | Bit 12              | Bit 11   | Bit 10  | Bit 9    | Bit 8      | Bit 7    | Bit 6   | Bit 5   | Bit 4   | Bit 3    | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

| PWMCON2   | 0C40  | FLTSTAT  | CLSTAT | TRGSTAT | FLTIEN              | CLIEN    | TRGIEN  | ITB      | MDCS       | DTC      | <1:0>   | DTCP    | _       | MTBS     | CAM     | XPRES   | IUE     | 0000          |

| IOCON2    | 0C42  | PENH     | PENL   | POLH    | POLL                | PMOD     | 0<1:0>  | OVRENH   | OVRENL     | OVRDA    | \T<1:0> | FLTD    | \T<1:0> | CLDA     | AT<1:0> | SWAP    | OSYNC   | C000          |

| FCLCON2   | 0C44  | _        |        | (       | CLSRC<4:0           | )>       |         | CLPOL    | CLMOD      |          | FLT     | SRC<4:0 | >       |          | FLTPOL  | FLTMO   | D<1:0>  | 00F8          |

| PDC2      | 0C46  |          |        |         | PDC2<15:0>          |          |         |          |            |          |         | 0000    |         |          |         |         |         |               |

| PHASE2    | 0C48  |          |        |         | PHASE2<15:0>        |          |         |          |            |          |         | 0000    |         |          |         |         |         |               |

| DTR2      | 0C4A  | _        | _      |         | DTR2<13:0>          |          |         |          |            |          | 0000    |         |         |          |         |         |         |               |

| ALTDTR2   | 0C4C  | _        | _      |         |                     |          |         |          | AL         | TDTR2<13 | :0>     |         |         |          |         |         |         | 0000          |

| TRIG2     | 0C52  |          |        |         |                     |          |         | TI       | RGCMP<15:0 | )>       |         |         |         |          |         |         |         | 0000          |

| TRGCON2   | 0C54  |          | TRGDI  | V<3:0>  | /<3:0> TRGSTRT<5:0> |          |         |          |            |          | 0>      |         | 0000    |          |         |         |         |               |

| LEBCON2   | 0C5A  | PHR      | PHF    | PLR     | PLF                 | FLTLEBEN | CLLEBEN | _        | _          | _        | -       | BCH     | BCL     | BPHH     | BPHL    | BPLH    | BPLL    | 0000          |

| LEBDLY2   | 0C5C  | _        | _      | _       | LEB<11:0>           |          |         |          |            |          |         | 0000    |         |          |         |         |         |               |

| AUXCON2   | 0C5E  | _        | _      | —       | —                   |          | BLANK   | SEL<3:0> |            | _        | —       |         | CHOPS   | SEL<3:0> |         | CHOPHEN | CHOPLEN | 0000          |

I- DIGGOEDV/VMOGOV/EGV AND DIGGAEDV/VMOGOV DEVICED ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-15: PWM GENERATOR 3 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12                                                | Bit 11   | Bit 10  | Bit 9  | Bit 8      | Bit 7    | Bit 6    | Bit 5 | Bit 4   | Bit 3 | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|---------|--------|---------|-------------------------------------------------------|----------|---------|--------|------------|----------|----------|-------|---------|-------|----------|-------|-------|---------------|

| PWMCON3   | 0C60  | FLTSTAT | CLSTAT | TRGSTAT | FLTIEN                                                | CLIEN    | TRGIEN  | ITB    | MDCS       | DTC<     | <1:0>    | DTCP  | —       | MTBS  | CAM      | XPRES | IUE   | 0000          |

| IOCON3    | 0C62  | PENH    | PENL   | POLH    | POLL                                                  | PMOD     | )<1:0>  | OVRENH | OVRENL     | OVRDA    | T<1:0>   | FLTD  | AT<1:0> | CLD   | AT<1:0>  | SWAP  | OSYNC | C000          |

| FCLCON3   | 0C64  |         |        | (       | CLSRC<4:0> CLPOL CLMOD FLTSRC<4:0> FLTPOL FLTMOD<1:0> |          |         |        |            |          | D<1:0>   | 00F8  |         |       |          |       |       |               |

| PDC3      | 0C66  |         |        |         |                                                       |          |         |        | PDC3<15:0> | •        |          |       |         |       |          |       |       | 0000          |

| PHASE3    | 0C68  |         |        |         | PHASE3<15:0>                                          |          |         |        |            | 0000     |          |       |         |       |          |       |       |               |

| DTR3      | 0C6A  |         | —      |         | DTR3<13:0>                                            |          |         |        |            | 0000     |          |       |         |       |          |       |       |               |

| ALTDTR3   | 0C6C  |         | —      |         |                                                       |          |         |        | AL         | TDTR3<13 | :0>      |       |         |       |          |       |       | 0000          |

| TRIG3     | 0C72  |         |        |         |                                                       |          |         | Т      | RGCMP<15:  | 0>       |          |       |         |       |          |       |       | 0000          |

| TRGCON3   | 0C74  |         | TRGDI  | V<3:0>  |                                                       | _        | _       | _      | _          | _        | _        |       |         | TR    | GSTRT<5: | 0>    |       | 0000          |

| LEBCON3   | 0C7A  | PHR     | PHF    | PLR     | PLF                                                   | FLTLEBEN | CLLEBEN | —      | —          |          | —        | BCH   | BCL     | BPHH  | BPHL     | BPLH  | BPLL  | 0000          |

| LEBDLY3   | 0C7C  |         | —      | _       | _                                                     |          |         |        |            |          | LEB<11:0 | )>    |         |       |          |       |       | 0000          |

| AUXCON3   | 0C7E  |         | —      | —       | BLANKSEL<3:0> CHOPSEL<3:0> CHOPHEN CHOP               |          |         |        |            | CHOPLEN  | 0000     |       |         |       |          |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

.

----

.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0   | U-0              | U-0   | U-0              | U-0              | U-0             | U-0   |

|-----------------|-------|------------------|-------|------------------|------------------|-----------------|-------|

| —               | —     | —                | —     | —                | —                | _               | —     |

| bit 15          |       |                  |       |                  | •                |                 | bit 8 |

|                 |       |                  |       |                  |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | STB<  | 23:16>           |                  |                 |       |

| bit 7           |       |                  |       |                  |                  |                 | bit 0 |

|                 |       |                  |       |                  |                  |                 |       |

| Legend:         |       |                  |       |                  |                  |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimpler     | mented bit, read | l as '0'        |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | eared            | x = Bit is unkr | nown  |

|                 |       |                  |       |                  |                  |                 |       |

#### REGISTER 8-5: DMAXSTBH: DMA CHANNEL X START ADDRESS REGISTER B (HIGH)

bit 15-8 Unimplemented: Read as '0'

bit 7-0 STB<23:16>: Secondary Start Address bits (source or destination)

#### REGISTER 8-6: DMAXSTBL: DMA CHANNEL X START ADDRESS REGISTER B (LOW)

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | STB   | <15:8>            |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | STE   | 3<7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkı | nown  |

bit 15-0 **STB<15:0>:** Secondary Start Address bits (source or destination)

| U-0          | U-0                                                                                                                               | U-0               | U-0   | U-0              | U-0              | U-0             | U-0   |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|------------------|------------------|-----------------|-------|--|--|--|--|

| —            | —                                                                                                                                 | —                 | _     | —                | —                | —               | _     |  |  |  |  |

| bit 15       |                                                                                                                                   |                   |       |                  |                  |                 | bit 8 |  |  |  |  |

|              |                                                                                                                                   |                   |       |                  |                  |                 |       |  |  |  |  |

| U-0          | R/W-0                                                                                                                             | R/W-0             | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

| —            |                                                                                                                                   |                   |       | INT2R<6:0>       |                  |                 |       |  |  |  |  |

| bit 7        |                                                                                                                                   |                   |       |                  |                  |                 | bit 0 |  |  |  |  |

|              |                                                                                                                                   |                   |       |                  |                  |                 |       |  |  |  |  |

| Legend:      |                                                                                                                                   |                   |       |                  |                  |                 |       |  |  |  |  |

| R = Readal   | ole bit                                                                                                                           | W = Writable      | bit   | U = Unimpler     | mented bit, read | as '0'          |       |  |  |  |  |

| -n = Value a | at POR                                                                                                                            | '1' = Bit is set  |       | '0' = Bit is cle | ared             | x = Bit is unkr | iown  |  |  |  |  |

|              |                                                                                                                                   |                   |       |                  |                  |                 |       |  |  |  |  |

| bit 15-7     | Unimplemen                                                                                                                        | ted: Read as 'd   | )'    |                  |                  |                 |       |  |  |  |  |

| bit 6-0      | INT2R<6:0>: Assign External Interrupt 2 (INT2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |                   |       |                  |                  |                 |       |  |  |  |  |

|              | 1111001 <b>= lr</b>                                                                                                               | put tied to RPI   | 121   |                  |                  |                 |       |  |  |  |  |

|              |                                                                                                                                   |                   |       |                  |                  |                 |       |  |  |  |  |

|              |                                                                                                                                   |                   |       |                  |                  |                 |       |  |  |  |  |

|              | 0000001 – Ir                                                                                                                      | put tied to CMI   | ⊃1    |                  |                  |                 |       |  |  |  |  |

|              |                                                                                                                                   | put tied to Civil |       |                  |                  |                 |       |  |  |  |  |

|              |                                                                                                                                   |                   |       |                  |                  |                 |       |  |  |  |  |

|              |                                                                                                                                   |                   |       |                  |                  |                 |       |  |  |  |  |

#### REGISTER 11-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

#### REGISTER 11-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0<br>— T2CKR<6:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |                     |                  |       |                  |                  |                 |       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------|------------------|-------|------------------|------------------|-----------------|-------|

| U-0       R/W-0       R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0          | U-0                 | U-0              | U-0   | U-0              | U-0              | U-0             | U-0   |

| U-0       R/W-0       R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _            | -                   | —                | _     | —                | —                | —               | —     |

| —       T2CKR<6:0>         bit 7       t         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 15       |                     |                  |       |                  |                  |                 | bit 8 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                  |                  |                 |       |

| bit 7       Image: Constraint of the system of | U-0          | R/W-0               | R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . <td< td=""><td>—</td><td></td><td></td><td></td><td>T2CKR&lt;6:0&gt;</td><td>&gt;</td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —            |                     |                  |       | T2CKR<6:0>       | >                |                 |       |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 7        |                     |                  |       |                  |                  |                 | bit 0 |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |                     |                  |       |                  |                  |                 |       |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Legend:      |                     |                  |       |                  |                  |                 |       |

| bit 15-7 Unimplemented: Read as '0'<br>bit 6-0 T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121<br>0000001 = Input tied to CMP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R = Readab   | ole bit             | W = Writable I   | bit   | U = Unimpler     | mented bit, read | as '0'          |       |

| bit 6-0 <b>T2CKR&lt;6:0&gt;:</b> Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -n = Value a | at POR              | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

| bit 6-0 <b>T2CKR&lt;6:0&gt;:</b> Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                     |                  |       |                  |                  |                 |       |

| (see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121<br>0000001 = Input tied to CMP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 15-7     | Unimplemen          | ted: Read as 'd  | )'    |                  |                  |                 |       |

| 1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 6-0      |                     | •                |       | · · ·            | he Correspondir  | ng RPn pin bits | 5     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       | ,                |                  |                 |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                  |                  |                 |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                  |                  |                 |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | 0000001 = Ir        | nout tied to CM  | ⊃1    |                  |                  |                 |       |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |                     |                  |       |                  |                  |                 |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | 0000000 <b>- II</b> | iput tied to vss |       |                  |                  |                 |       |

| U-0              | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|------------------|--------------|----------------------------------------------------------|---------------|-------------------|-----------------|-----------------|-------|

| —                |              |                                                          |               | IC4R<6:0>         |                 |                 |       |

| bit 15           |              |                                                          |               |                   |                 |                 | bit 8 |

|                  |              |                                                          |               |                   |                 |                 |       |

| U-0              | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| —                |              |                                                          |               | IC3R<6:0>         |                 |                 |       |

| bit 7            |              |                                                          |               |                   |                 |                 | bit C |

|                  |              |                                                          |               |                   |                 |                 |       |

| Legend:          |              |                                                          |               |                   |                 |                 |       |

| R = Readab       | ole bit      | W = Writable I                                           | bit           | U = Unimplem      | nented bit, rea | d as '0'        |       |

| n = Value at POR |              | '1' = Bit is set                                         |               | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|                  | 0000001 =    | nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss | ⊃1            |                   |                 |                 |       |

| bit 7            | Unimpleme    | nted: Read as 'o                                         | )'            |                   |                 |                 |       |

| bit 6-0          | (see Table 1 | Assign Input Ca<br>1-2 for input pin<br>nput tied to RPI | selection nun |                   | onding RPn Pi   | n bits          |       |

#### REGISTER 11-5: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

# 14.2 Input Capture Registers

#### REGISTER 14-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0   |

|--------|-----|--------|---------|---------|---------|-----|-------|

| _      | —   | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 |     | —     |

| bit 15 |     |        |         |         |         |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/HC/HS-0 | R/HC/HS-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----------|-----------|-------|-------|-------|

| —     | ICI1  | ICI0  | ICOV      | ICBNE     | ICM2  | ICM1  | ICM0  |

| bit 7 |       |       |           |           |       |       | bit 0 |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable b  | bit                |

|-------------------|-----------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared      | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture Stop in Idle Control bit                                                                                                              |

|           | 1 = Input capture will Halt in CPU Idle mode                                                                                                                |

|           | 0 = Input capture will continue to operate in CPU Idle mode                                                                                                 |

| bit 12-10 | ICTSEL<2:0>: Input Capture Timer Select bits                                                                                                                |

|           | 111 = Peripheral clock (FP) is the clock source of the ICx                                                                                                  |

|           | 110 = Reserved                                                                                                                                              |

|           | 101 = Reserved                                                                                                                                              |

|           | 100 = T1CLK is the clock source of the ICx (only the synchronous clock is supported)<br>011 = T5CLK is the clock source of the ICx                          |

|           | 010 = T4CLK is the clock source of the ICx                                                                                                                  |

|           | 001 = T2CLK is the clock source of the ICx                                                                                                                  |

|           | 000 = T3CLK is the clock source of the ICx                                                                                                                  |

| bit 9-7   | Unimplemented: Read as '0'                                                                                                                                  |

| bit 6-5   | ICI<1:0>: Number of Captures per Interrupt Select bits (this field is not used if ICM<2:0> = 001 or 111)                                                    |

|           | 11 = Interrupt on every fourth capture event                                                                                                                |

|           | 10 = Interrupt on every third capture event                                                                                                                 |

|           | 01 = Interrupt on every second capture event<br>00 = Interrupt on every capture event                                                                       |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                    |

| bit 4     | 1 = Input capture buffer overflow occurred                                                                                                                  |

|           | 0 = No input capture buffer overflow occurred                                                                                                               |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                                |

|           | 1 = Input capture buffer is not empty, at least one more capture value can be read                                                                          |

|           | 0 = Input capture buffer is empty                                                                                                                           |

| bit 2-0   | ICM<2:0>: Input Capture Mode Select bits                                                                                                                    |

|           | 111 = Input capture functions as interrupt pin only in CPU Sleep and Idle modes (rising edge detect only, all other control bits are not applicable)        |

|           | 110 = Unused (module is disabled)                                                                                                                           |

|           | 101 = Capture mode, every 16th rising edge (Prescaler Capture mode)                                                                                         |

|           | <ul> <li>100 = Capture mode, every 4th rising edge (Prescaler Capture mode)</li> <li>011 = Capture mode, every rising edge (Simple Capture mode)</li> </ul> |

|           | 010 = Capture mode, every falling edge (Simple Capture mode)                                                                                                |

|           | 001 = Capture mode, every edge rising and falling (Edge Detect mode (ICI<1:0>) is not used in this mode)                                                    |

|           | 000 = Input capture module is turned off                                                                                                                    |

# 16.2 PWM Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 16.2.1 KEY RESOURCES

- "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 20-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement is disabled or completed</li> </ul> |

| bit 4   | URXINV: UARTx Receive Polarity Inversion bit                                                                                                                                                                                              |

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                                                  |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                                                                           |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul>                                                        |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                                                                                |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                                                                             |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                                                                             |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                                                                                     |

|         | Refer to the " <b>UART</b> " (DS70582) section in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for receive or transmit operation.                                                             |

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

- 3: This feature is only available on 44-pin and 64-pin devices.

- 4: This feature is only available on 64-pin devices.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 21-13: CxBUFPNT2: ECANx FILTER 4-7 BUFFER POINTER REGISTER 2

| R/W-0                              |       |        |                     |                |                 |        |       |

|------------------------------------|-------|--------|---------------------|----------------|-----------------|--------|-------|

|                                    | R/W-0 | R/W-0  | R/W-0               | R/W-0          | R/W-0           | R/W-0  | R/W-0 |

|                                    | F7BF  | °<3:0> |                     |                | F6BF            | P<3:0> |       |

| bit 15                             |       |        |                     |                |                 |        | bit 8 |

| R/W-0                              | R/W-0 | R/W-0  | R/W-0               | R/W-0          | R/W-0           | R/W-0  | R/W-0 |