Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                    |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc504-e-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.0 CPU

Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for digital signal processing. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

## 3.1 Registers

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can act as a data, address or address offset register. The 16th working register (W15) operates as a Software Stack Pointer for interrupts and calls.

#### 3.2 Instruction Set

The instruction set for dsPIC33EPXXXGP50X and dsPIC33EPXXXMC20X/50X devices has two classes of instructions: the MCU class of instructions and the DSP class of instructions. The instruction set for PIC24EPXXXGP/MC20X devices has the MCU class of instructions only and does not support DSP instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

### 3.3 Data Space Addressing

The base Data Space can be addressed as 64 Kbytes (32K words).

The Data Space includes two ranges of memory, referred to as X and Y data memory. Each memory range is accessible through its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. On dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Spaces have memory locations that are device-specific, and are described further in the data memory maps in Section 4.2 "Data Address Space".

The upper 32 Kbytes of the Data Space memory map can optionally be mapped into Program Space (PS) at any 32-Kbyte aligned program word boundary. The Program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Moreover, the Base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space (EDS) address. The EDS can be addressed as 8M words or 16 Mbytes. Refer to the "Data Memory" (DS70595) and "Program Memory" (DS70613) sections in the "dsPIC33/PIC24 Family Reference Manual" for more details on EDS, PSV and table accesses.

On the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data re-ordering for radix-2 FFT algorithms. PIC24EPXXXGP/MC20X devices do not support Modulo and Bit-Reversed Addressing.

#### 3.4 Addressing Modes

The CPU supports these addressing modes:

- · Inherent (no operand)

- Relative

- Literal

- · Memory Direct

- · Register Direct

- Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

TABLE 4-53: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|---------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | 1      | _      | 1      | _      | TRISA10 | TRISA9 | TRISA8 | TRISA7 | -     | -     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 079F          |

| PORTA        | 0E02  | 1      | -      | _      | _      | _      | RA10    | RA9    | RA8    | RA7    | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | 1      | -      | _      | _      | _      | LATA10  | LATA9  | LATA8  | LATA7  | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | 1      | -      | _      | _      | _      | ODCA10  | ODCA9  | ODCA8  | ODCA7  | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | 1      | -      | _      | _      | _      | CNIEA10 | CNIEA9 | CNIEA8 | CNIEA7 | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | 1      | -      | _      | _      | _      | CNPUA10 | CNPUA9 | CNPUA8 | CNPUA7 | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | 1      | -      | _      | _      | _      | CNPDA10 | CNPDA9 | CNPDA8 | CNPDA7 | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | -      | 1      | _      | ı      | 1      | _       | _      | _      | _      | ı     | -     | ANSA4  | -      | _      | ANSA1  | ANSA0  | 0013          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-54: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | _       | _      | ANSB8  | _      | _      | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-55: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISC        | 0E20  | _      | _      | _      | _      | _      | -      | TRISC9 | TRISC8 | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 03FF          |

| PORTC        | 0E22  | -      | _      |        | _      |        | 1      | RC9    | RC8    | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xxxx          |

| LATC         | 0E24  | -      | _      |        | _      |        | 1      | LATC9  | LATC8  | LATC7  | LATC6  | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  | _      | _      | ı      |        | ı      | -      | ODCC9  | ODCC8  | ODCC7  | ODCC6  | ODCC5  | ODCC4  | ODCC3  | ODCC2  | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | -      | _      |        | _      |        | 1      | CNIEC9 | CNIEC8 | CNIEC7 | CNIEC6 | CNIEC5 | CNIEC4 | CNIEC3 | CNIEC2 | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  | -      | _      | -      | -      | -      | _      | CNPUC9 | CNPUC8 | CNPUC7 | CNPUC6 | CNPUC5 | CNPUC4 | CNPUC3 | CNPUC2 | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  | -      | _      | -      | _      | _      | _      | CNPDC9 | CNPDC8 | CNPDC7 | CNPDC6 | CNPDC5 | CNPDC4 | CNPDC3 | CNPDC2 | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _      | _      | _      | _      | ANSC2  | ANSC1  | ANSC0  | 0007          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

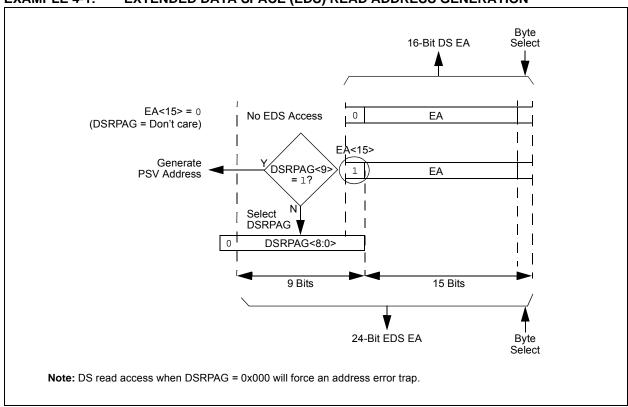

#### 4.4.1 PAGED MEMORY SCHEME

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre-modified and post-modified Effective Addresses (EA). The upper half of the base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Read Page register (DSRPAG) or the 9-bit Write Page register (DSWPAG), to form an Extended Data Space (EDS)

address or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

Construction of the EDS address is shown in Example 4-1. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when base address bit, EA<15> = 1, DSWPAG<8:0> are concatenated onto EA<14:0> to form the 24-bit EDS write address.

EXAMPLE 4-1: EXTENDED DATA SPACE (EDS) READ ADDRESS GENERATION

### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

W = Writable bit

| R/W-0  | R/W-0                 | R/W-0                 | R/W-0                  | R/W-0                  | R/W-0                | R/W-0                | R/W-0                |

|--------|-----------------------|-----------------------|------------------------|------------------------|----------------------|----------------------|----------------------|

| NSTDIS | OVAERR <sup>(1)</sup> | OVBERR <sup>(1)</sup> | COVAERR <sup>(1)</sup> | COVBERR <sup>(1)</sup> | OVATE <sup>(1)</sup> | OVBTE <sup>(1)</sup> | COVTE <sup>(1)</sup> |

| bit 15 | •                     |                       |                        |                        |                      |                      | bit 8                |

| R/W-0                   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0   | U-0   |

|-------------------------|---------|---------|---------|---------|--------|---------|-------|

| SFTACERR <sup>(1)</sup> | DIV0ERR | DMACERR | MATHERR | ADDRERR | STKERR | OSCFAIL | _     |

| bit 7                   |         |         |         |         |        |         | bit 0 |

U = Unimplemented bit, read as '0'

x = Bit is unknown

| -n = Value at Po | OR '1' = Bit is set                                                                                                     | '0' = Bit is cleared                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| bit 15           | <b>NSTDIS:</b> Interrupt Nesting Disable bit 1 = Interrupt nesting is disabled                                          |                                          |

|                  | 0 = Interrupt nesting is enabled                                                                                        |                                          |

| bit 14           | <b>OVAERR:</b> Accumulator A Overflow Trap                                                                              | · · · · · · · · · · · · · · · · · · ·    |

|                  | <ul><li>1 = Trap was caused by overflow of Acc</li><li>0 = Trap was not caused by overflow of</li></ul>                 |                                          |

| bit 13           | <b>OVBERR:</b> Accumulator B Overflow Tra                                                                               | p Flag bit <sup>(1)</sup>                |

|                  | <ul><li>1 = Trap was caused by overflow of Acc</li><li>0 = Trap was not caused by overflow of</li></ul>                 |                                          |

| bit 12           | <b>COVAERR:</b> Accumulator A Catastrophi 1 = Trap was caused by catastrophic ov 0 = Trap was not caused by catastrophi | erflow of Accumulator A                  |

| bit 11           | COVBERR: Accumulator B Catastrophi                                                                                      | ic Overflow Trap Flag bit <sup>(1)</sup> |

|                  | 1 = Trap was caused by catastrophic ov 0 = Trap was not caused by catastrophi                                           | ic overflow of Accumulator B             |

| bit 10           | <b>OVATE:</b> Accumulator A Overflow Trap I                                                                             | Enable bit <sup>(1)</sup>                |

|                  | <ul><li>1 = Trap overflow of Accumulator A</li><li>0 = Trap is disabled</li></ul>                                       |                                          |

| bit 9            | <b>OVBTE:</b> Accumulator B Overflow Trap                                                                               | Enable bit <sup>(1)</sup>                |

|                  | <ul><li>1 = Trap overflow of Accumulator B</li><li>0 = Trap is disabled</li></ul>                                       |                                          |

| bit 8            | COVTE: Catastrophic Overflow Trap Er                                                                                    | nable bit <sup>(1)</sup>                 |

|                  | <ul><li>1 = Trap on catastrophic overflow of Ac</li><li>0 = Trap is disabled</li></ul>                                  | cumulator A or B is enabled              |

| bit 7            | SFTACERR: Shift Accumulator Error St                                                                                    |                                          |

|                  | 1 = Math error trap was caused by an ir<br>0 = Math error trap was not caused by a                                      |                                          |

| bit 6            | <b>DIV0ERR:</b> Divide-by-Zero Error Status                                                                             |                                          |

|                  | 1 = Math error trap was caused by a div<br>0 = Math error trap was not caused by a                                      | -                                        |

| bit 5            | DMACERR: DMAC Trap Flag bit                                                                                             |                                          |

|                  |                                                                                                                         |                                          |

1 = DMAC trap has occurred0 = DMAC trap has not occurred

Note 1: These bits are available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

Legend:

R = Readable bit

# REGISTER 8-7: DMAXPAD: DMA CHANNEL X PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|--------|-------|-------|-------|

|        |       |       | PAD<  | :15:8> |       |       |       |

| bit 15 |       |       |       |        |       |       | bit 8 |

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|----------|-------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| PAD<7:0> |       |       |       |       |       |       |       |  |  |  |  |

| bit 7    |       |       |       |       |       |       | bit 0 |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

## REGISTER 8-8: DMAXCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0                | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|----------------------|-------|-------|

| _      | _   |       |       | CNT<  | 13:8> <sup>(2)</sup> |       |       |

| bit 15 |     |       |       |       |                      |       | bit 8 |

| R/W-0                   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |  |

|-------------------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|--|--|

| CNT<7:0> <sup>(2)</sup> |       |       |       |       |       |       |       |  |  |  |  |  |

| bit 7                   |       |       |       |       |       |       | bit 0 |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

2: The number of DMA transfers = CNT<13:0> + 1.

#### **REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER**

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R-0    | R-0 R-0 F |        | R-0    |

|-------|-----|-----|-----|--------|-----------|--------|--------|

| _     | _   | _   | _   | RQCOL3 | RQCOL2    | RQCOL1 | RQCOL0 |

| bit 7 |     |     |     |        |           |        | bit 0  |

Legend:

R = Readable bit U = Unimplemented bit, read as '0' W = Writable bit

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-4 Unimplemented: Read as '0' bit 3 RQCOL3: DMA Channel 3 Transfer Request Collision Flag bit 1 = User force and interrupt-based request collision is detected 0 = No request collision is detected bit 2 RQCOL2: DMA Channel 2 Transfer Request Collision Flag bit 1 = User force and interrupt-based request collision is detected 0 = No request collision is detected bit 1 RQCOL1: DMA Channel 1 Transfer Request Collision Flag bit 1 = User force and interrupt-based request collision is detected

0 = No request collision is detected

bit 0 RQCOLO: DMA Channel 0 Transfer Request Collision Flag bit

1 = User force and interrupt-based request collision is detected

0 = No request collision is detected

#### **TIMER2/3 AND TIMER4/5** 13.0

Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

> 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 operate in three modes:

- · Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with all 16-Bit Operating modes (except Asynchronous Counter mode)

- · Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

They also support these features:

- · Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare Modules (Timer2 and Timer3 only)

- · ADC1 Event Trigger (32-bit timer pairs, and Timer3 and Timer5 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, and T4CON, T5CON registers. T2CON and T4CON are shown in generic form in Register 13-1. T3CON and T5CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word (lsw); Timer3 and Timer5 are the most significant word (msw) of the 32-bit timers.

For 32-bit operation, T3CON and T5CON

control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

A block diagram for an example 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 13-3.

Only Timer2, 3, 4 and 5 can trigger a DMA data transfer.

## 17.2 QEI Control Registers

#### REGISTER 17-1: QEI1CON: QEI1 CONTROL REGISTER

| R/W-0  | U-0 | R/W-0   | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0               | R/W-0               |

|--------|-----|---------|-----------------------|-----------------------|-----------------------|---------------------|---------------------|

| QEIEN  | _   | QEISIDL | PIMOD2 <sup>(1)</sup> | PIMOD1 <sup>(1)</sup> | PIMOD0 <sup>(1)</sup> | IMV1 <sup>(2)</sup> | IMV0 <sup>(2)</sup> |

| bit 15 |     |         |                       |                       |                       |                     | bit 8               |

| U-0   | R/W-0                  | R/W-0                  | R/W-0      | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-------|------------------------|------------------------|------------|--------|-------|-------|-------|

| _     | INTDIV2 <sup>(3)</sup> | INTDIV1 <sup>(3)</sup> | INTDIV0(3) | CNTPOL | GATEN | CCM1  | CCM0  |

| bit 7 |                        |                        |            |        |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 QEIEN: Quadrature Encoder Interface Module Counter Enable bit

1 = Module counters are enabled

0 = Module counters are disabled, but SFRs can be read or written to

bit 14 **Unimplemented:** Read as '0'

bit 13 QEISIDL: QEI Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12-10 PIMOD<2:0>: Position Counter Initialization Mode Select bits<sup>(1)</sup>

111 = Reserved

110 = Modulo Count mode for position counter

101 = Resets the position counter when the position counter equals QEI1GEC register

100 = Second index event after home event initializes position counter with contents of QEI1IC register

011 = First index event after home event initializes position counter with contents of QEI1IC register

010 = Next index input event initializes the position counter with contents of QEI1IC register

001 = Every index input event resets the position counter

000 = Index input event does not affect position counter

bit 9 **IMV1:** Index Match Value for Phase B bit<sup>(2)</sup>

1 = Phase B match occurs when QEB = 1

0 = Phase B match occurs when QEB = 0

bit 8 IMV0: Index Match Value for Phase A bit<sup>(2)</sup>

1 = Phase A match occurs when QEA = 1

0 = Phase A match occurs when QEA = 0

bit 7 **Unimplemented:** Read as '0'

Note 1: When CCM<1:0> = 10 or 11, all of the QEI counters operate as timers and the PIMOD<2:0> bits are ignored.

- 2: When CCM<1:0> = 00, and QEA and QEB values match the Index Match Value (IMV), the POSCNTH and POSCNTL registers are reset. QEA/QEB signals used for the index match have swap and polarity values applied, as determined by the SWPAB and QEAPOL/QEBPOL bits.

- 3: The selected clock rate should be at least twice the expected maximum quadrature count rate.

## REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

bit 3 S: Start bit

1 = Indicates that a Start (or Repeated Start) bit has been detected last

0 = Start bit was not detected last

Hardware is set or clear when a Start, Repeated Start or Stop is detected.

bit 2 **R\_W:** Read/Write Information bit (when operating as I<sup>2</sup>C slave)

1 = Read – Indicates data transfer is output from the slave

0 = Write - Indicates data transfer is input to the slave

Hardware is set or clear after reception of an I<sup>2</sup>C device address byte.

bit 1 RBF: Receive Buffer Full Status bit

1 = Receive is complete, I2CxRCV is full

0 = Receive is not complete, I2CxRCV is empty

Hardware is set when I2CxRCV is written with a received byte. Hardware is clear when software reads

I2CxRCV.

bit 0 TBF: Transmit Buffer Full Status bit

1 = Transmit in progress, I2CxTRN is full

0 = Transmit is complete, I2CxTRN is empty

Hardware is set when software writes to I2CxTRN. Hardware is clear at completion of a data transmission.

#### REGISTER 23-6: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER

| R/W-0      | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |  |

|------------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|--|

| CH0NB      | _   | _   | CH0SB4 <sup>(1)</sup> | CH0SB3 <sup>(1)</sup> | CH0SB2 <sup>(1)</sup> | CH0SB1 <sup>(1)</sup> | CH0SB0 <sup>(1)</sup> |  |

| bit 15 bit |     |     |                       |                       |                       |                       |                       |  |

| R/W-0 | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| CH0NA | _   | _   | CH0SA4 <sup>(1)</sup> | CH0SA3 <sup>(1)</sup> | CH0SA2 <sup>(1)</sup> | CH0SA1 <sup>(1)</sup> | CH0SA0 <sup>(1)</sup> |

| bit 7 |     |     |                       |                       |                       |                       | bit 0                 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 CHONB: Channel 0 Negative Input Select for Sample MUXB bit

1 = Channel 0 negative input is AN1(1)

0 = Channel 0 negative input is VREFL

bit 14-13 Unimplemented: Read as '0'

bit 12-8 CH0SB<4:0>: Channel 0 Positive Input Select for Sample MUXB bits<sup>(1)</sup>

11111 = Open; use this selection with CTMU capacitive and time measurement

11110 = Channel 0 positive input is connected to the CTMU temperature measurement diode (CTMU TEMP)

11101 = Reserved

11100 = Reserved

11011 = Reserved

11010 = Channel 0 positive input is the output of OA3/AN6(2,3)

11001 = Channel 0 positive input is the output of OA2/AN0<sup>(2)</sup>

11000 = Channel 0 positive input is the output of OA1/AN3<sup>(2)</sup>

10111 = Reserved

٠

\_

10000 = Reserved

01111 = Channel 0 positive input is AN15<sup>(3)</sup>

01110 = Channel 0 positive input is AN14<sup>(3)</sup>

01101 = Channel 0 positive input is AN13<sup>(3)</sup>

•

.

00010 = Channel 0 positive input is AN2<sup>(3)</sup>

00001 = Channel 0 positive input is AN1(3)

00000 = Channel 0 positive input is AN0<sup>(3)</sup>

bit 7 CHONA: Channel 0 Negative Input Select for Sample MUXA bit

1 = Channel 0 negative input is AN1<sup>(1)</sup>

0 = Channel 0 negative input is VREFL

bit 6-5 **Unimplemented:** Read as '0'

- **Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

- 3: See the "Pin Diagrams" section for the available analog channels for each device.

#### REGISTER 25-4: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT **CONTROL REGISTER (CONTINUED)**

bit 3-0 SELSRCA<3:0>: Mask A Input Select bits

1111 = FLT4

1110 = FLT2

1101 = PTGO19

1100 **= PTGO18**

1011 = Reserved

1010 = Reserved

1001 = Reserved

1000 = Reserved

0111 = Reserved

0110 = Reserved

0101 = PWM3H

0100 **= PWM3L**

0011 **= PWM2H**

0010 = PWM2L0001 = PWM1H

0000 = PWM1L

| dsPIC33EPXXXGP | '50X, dsPIC33EPX | XXMC20X/50X A | AND PIC24EPXX | XGP/MC20X |

|----------------|------------------|---------------|---------------|-----------|

| NOTES:         |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

|                |                  |               |               |           |

| SPIC33EPXXX | SP50X, dsPIC3 | 3EPXXXMC2 | 0X/50X AND | PIC24EPX | XXGP/MC2 | 20X |

|-------------|---------------|-----------|------------|----------|----------|-----|

| OTES:       |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4

OSC1

OS20

OS25

OS41

OS41

OS41

OS41

FIGURE 30-2: EXTERNAL CLOCK TIMING

**TABLE 30-17: EXTERNAL CLOCK TIMING REQUIREMENTS**

| AC CHA       | AC CHARACTERISTICS |                                                                                    | Standard Ope<br>(unless other)<br>Operating tem | vise state          |             |            |                               |

|--------------|--------------------|------------------------------------------------------------------------------------|-------------------------------------------------|---------------------|-------------|------------|-------------------------------|

| Param<br>No. | Symb               | Characteristic                                                                     | Min.                                            | Typ. <sup>(1)</sup> | Max.        | Units      | Conditions                    |

| OS10         | FIN                | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC                                              | _                   | 60          | MHz        | EC                            |

|              |                    | Oscillator Crystal Frequency                                                       | 3.5<br>10                                       | _                   | 10<br>25    | MHz<br>MHz | XT<br>HS                      |

| OS20         | Tosc               | Tosc = 1/Fosc                                                                      | 8.33                                            | _                   | DC          | ns         | +125°C                        |

|              |                    | Tosc = 1/Fosc                                                                      | 7.14                                            | _                   | DC          | ns         | +85°C                         |

| OS25         | TCY                | Instruction Cycle Time <sup>(2)</sup>                                              | 16.67                                           | _                   | DC          | ns         | +125°C                        |

|              |                    | Instruction Cycle Time <sup>(2)</sup>                                              | 14.28                                           | _                   | DC          | ns         | +85°C                         |

| OS30         | TosL,<br>TosH      | External Clock in (OSC1)<br>High or Low Time                                       | 0.45 x Tosc                                     | _                   | 0.55 x Tosc | ns         | EC                            |

| OS31         | TosR,<br>TosF      | External Clock in (OSC1)<br>Rise or Fall Time                                      | _                                               | _                   | 20          | ns         | EC                            |

| OS40         | TckR               | CLKO Rise Time <sup>(3,4)</sup>                                                    | _                                               | 5.2                 | _           | ns         |                               |

| OS41         | TckF               | CLKO Fall Time <sup>(3,4)</sup>                                                    | _                                               | 5.2                 | _           | ns         |                               |

| OS42         | Gм                 | External Oscillator<br>Transconductance <sup>(4)</sup>                             | _                                               | 12                  | _           | mA/V       | HS, VDD = 3.3V,<br>TA = +25°C |

|              |                    |                                                                                    | _                                               | 6                   | _           | mA/V       | XT, VDD = 3.3V,<br>TA = +25°C |

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- 2: Instruction cycle period (TcY) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Minimum" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "Maximum" cycle time limit is "DC" (no clock) for all devices.

- 3: Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

- 4: This parameter is characterized, but not tested in manufacturing.

TABLE 30-37: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING REQUIREMENTS

| AC CHA | Characteristic(1)     |                                            |              | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |                          |       |                             |  |  |

|--------|-----------------------|--------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------|-----------------------------|--|--|

| Param. | Symbol                | Characteristic <sup>(1)</sup>              | Min.         | Typ. <sup>(2)</sup>                                                                                                                                                                                                                              | Max.                     | Units | Conditions                  |  |  |

| SP70   | FscP                  | Maximum SCK2 Input<br>Frequency            | _            | _                                                                                                                                                                                                                                                | Lesser<br>of FP<br>or 15 | MHz   | (Note 3)                    |  |  |

| SP72   | TscF                  | SCK2 Input Fall Time                       | _            | _                                                                                                                                                                                                                                                | _                        | ns    | See Parameter DO32 (Note 4) |  |  |

| SP73   | TscR                  | SCK2 Input Rise Time                       | _            | _                                                                                                                                                                                                                                                | _                        | ns    | See Parameter DO31 (Note 4) |  |  |

| SP30   | TdoF                  | SDO2 Data Output Fall Time                 | _            | _                                                                                                                                                                                                                                                | _                        | ns    | See Parameter DO32 (Note 4) |  |  |

| SP31   | TdoR                  | SDO2 Data Output Rise Time                 | _            | _                                                                                                                                                                                                                                                | _                        | ns    | See Parameter DO31 (Note 4) |  |  |

| SP35   | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after SCK2 Edge     | _            | 6                                                                                                                                                                                                                                                | 20                       | ns    |                             |  |  |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to First SCK2 Edge  | 30           | _                                                                                                                                                                                                                                                | _                        | ns    |                             |  |  |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge | 30           | _                                                                                                                                                                                                                                                | _                        | ns    |                             |  |  |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge  | 30           | _                                                                                                                                                                                                                                                | _                        | ns    |                             |  |  |

| SP50   | TssL2scH,<br>TssL2scL | SS2 ↓ to SCK2 ↑ or SCK2 ↓ Input            | 120          | _                                                                                                                                                                                                                                                | _                        | ns    |                             |  |  |

| SP51   | TssH2doZ              | SS2 ↑ to SDO2 Output<br>High-Impedance     | 10           | _                                                                                                                                                                                                                                                | 50                       | ns    | (Note 4)                    |  |  |

| SP52   | TscH2ssH<br>TscL2ssH  | SS2 ↑ after SCK2 Edge                      | 1.5 Tcy + 40 | _                                                                                                                                                                                                                                                | _                        | ns    | (Note 4)                    |  |  |

| SP60   | TssL2doV              | SDO2 Data Output Valid after<br>SS2 Edge   | _            | _                                                                                                                                                                                                                                                | 50                       | ns    |                             |  |  |

- Note 1: These parameters are characterized, but are not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK2 is 66.7 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

- 4: Assumes 50 pF load on all SPI2 pins.

TABLE 30-40: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0)

TIMING REQUIREMENTS

| AC CHA | AC CHARACTERISTICS    |                                            | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                     |      |       |                             |

|--------|-----------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>              | Min.                                                                                                                                                                                                                                             | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |

| SP70   | FscP                  | Maximum SCK2 Input Frequency               | _                                                                                                                                                                                                                                                | _                   | 11   | MHz   | (Note 3)                    |

| SP72   | TscF                  | SCK2 Input Fall Time                       | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP73   | TscR                  | SCK2 Input Rise Time                       | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP30   | TdoF                  | SDO2 Data Output Fall Time                 | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP31   | TdoR                  | SDO2 Data Output Rise Time                 | _                                                                                                                                                                                                                                                |                     | _    | ns    | See Parameter DO31 (Note 4) |

| SP35   | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge  | _                                                                                                                                                                                                                                                | 6                   | 20   | ns    |                             |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to First SCK2 Edge  | 30                                                                                                                                                                                                                                               | _                   | _    | ns    |                             |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge | 30                                                                                                                                                                                                                                               | _                   | _    | ns    |                             |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge  | 30                                                                                                                                                                                                                                               | _                   | _    | ns    |                             |

| SP50   | TssL2scH,<br>TssL2scL | SS2 ↓ to SCK2 ↑ or SCK2 ↓ Input            | 120                                                                                                                                                                                                                                              | _                   | _    | ns    |                             |

| SP51   | TssH2doZ              | SS2 ↑ to SDO2 Output<br>High-Impedance     | 10                                                                                                                                                                                                                                               | _                   | 50   | ns    | (Note 4)                    |

| SP52   | TscH2ssH<br>TscL2ssH  | SS2 ↑ after SCK2 Edge                      | 1.5 Tcy + 40                                                                                                                                                                                                                                     | _                   | _    | ns    | (Note 4)                    |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

- **2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK2 is 91 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

- 4: Assumes 50 pF load on all SPI2 pins.

# **Revision D (December 2011)**

This revision includes typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in Table A-3.

TABLE A-3: MAJOR SECTION UPDATES

| Section Name                                                                                                                                                            | Update Description                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "16-bit Microcontrollers<br>and Digital Signal<br>Controllers (up to<br>512-Kbyte Flash and<br>48-Kbyte SRAM) with High-<br>Speed PWM, Op amps, and<br>Advanced Analog" | Removed the Analog Comparators column and updated the Op amps/Comparators column in Table 1 and Table 2.                                                                                                                                         |

| Section 21.0 "Enhanced<br>CAN (ECAN™) Module<br>(dsPIC33EPXXXGP/MC50X<br>Devices Only)"                                                                                 | Updated the CANCKS bit value definitions in CiCTRL1: ECAN Control Register 1 (see Register 21-1).                                                                                                                                                |

| Section 30.0 "Electrical Characteristics"                                                                                                                               | Updated the VBOR specifications and/or its related note in the following electrical characteristics tables:  • Table 30-1  • Table 30-4  • Table 30-12  • Table 30-15  • Table 30-16  • Table 30-56  • Table 30-57  • Table 30-59  • Table 30-60 |

| Remappable Input for U1RX                                        | 176        | Memory Map for PIC24EP256GP/MC20X/50X   |                |

|------------------------------------------------------------------|------------|-----------------------------------------|----------------|

| Reset System                                                     |            | Devices                                 | 60             |

| Shared Port Structure                                            |            | Memory Map for PIC24EP32GP/MC20X/50X    | <br>00         |

| Single-Phase Synchronous Buck Converter                          |            | Devices                                 | 57             |

| SPIx Module                                                      |            | Memory Map for PIC24EP512GP/MC20X/50X   | 51             |

| Suggested Oscillator Circuit Placement                           |            | Devices                                 | 61             |

| Type B Timer (Timer2 and Timer4)                                 |            | Memory Map for PIC24EP64GP/MC20X/50X    | <br>0 1        |

| Type B/Type C Timer Pair (32-Bit Timer)                          |            | Devices                                 | 58             |

| Type C Timer (Timer3 and Timer5)                                 |            | Near Data Space                         |                |

| UARTx Module                                                     |            | Organization, Alignment                 |                |

| User-Programmable Blanking Function                              |            | SFR Space                               |                |

| Watchdog Timer (WDT)                                             |            | Width                                   |                |

| Brown-out Reset (BOR)                                            |            | Data Memory                             | <br><b>3</b> I |

| Blown-out Reset (BOR)                                            |            | Arbitration and Bus Master Priority     | 110            |

| C                                                                |            | Data Space                              | <br>110        |

| C Compilers                                                      |            | Extended X                              | 100            |

| MPLAB XC Compilers                                               | 398        | Paged Memory Scheme                     |                |

| Charge Time Measurement Unit. See CTMU.                          |            | DC and AC Characteristics               | <br>100        |

| Code Examples                                                    |            | Graphs                                  | 175            |

| IC1 Connection to QEI1 Input on                                  |            | DC Characteristics                      | <br>475        |

| Pin 43 of dsPIC33EPXXXMC206                                      | 176        | BOR                                     | 111            |

| Port Write/Read                                                  |            | CTMU Current Source Requirements        |                |

| PWMx Write-Protected Register                                    |            | Doze Current (IDOZE)                    |                |

| Unlock Sequence                                                  | 226        | High Temperature                        |                |

| PWRSAV Instruction Syntax                                        |            | I/O Pin Input Specifications            |                |

| Code Protection                                                  |            | I/O Pin Output Specifications           |                |

| CodeGuard Security                                               | ,          | Idle Current (IDLE)                     |                |

| Configuration Bits                                               |            | Op Amp/Comparator Requirements          |                |

| Description                                                      |            |                                         | <br>400        |

| Configuration Byte Register Map                                  |            | Op Amp/Comparator Voltage Reference     | 157            |

| Configuring Analog and Digital Port Pins                         |            | Requirements                            |                |

| CPU                                                              | 174        | Operating Current (IDD)                 |                |

| Addressing Modes                                                 | 35         | Operating MIPS vs. Voltage              |                |

| Clocking System Options                                          |            | Power-Down Current (IPD)                |                |

| Fast RC (FRC) Oscillator                                         |            | Program Memory                          |                |

| FRC Oscillator with PLL                                          |            | Temperature and Voltage                 |                |

|                                                                  |            | Temperature and Voltage Specifications  |                |

| FRC Oscillator with Postscaler<br>Low-Power RC (LPRC) Oscillator |            | Thermal Operating Conditions            |                |

| Primary (XT, HS, EC) Oscillator                                  |            | Watchdog Timer Delta Current            | <br>407        |

| * '                                                              |            | Demo/Development Boards, Evaluation and | 400            |

| Primary Oscillator with PLL                                      |            | Starter Kits                            |                |

| Control Registers                                                |            | Development Support                     |                |

| Data Space Addressing                                            |            | Third-Party Tools                       | <br>400        |

| Instruction Set<br>Resources                                     |            | DMA Controller                          | 440            |

| CTMU                                                             |            | Channel to Peripheral Associations      |                |

|                                                                  | 217        | Control Registers                       |                |

| Control Registers Resources                                      |            | DMAxCNT                                 |                |

|                                                                  |            | DMAxCON                                 |                |

| Customer Change Notification Service                             |            | DMAxPAD                                 |                |

| Customer Notification Service                                    |            | DMAxREQ                                 |                |

| Customer Support                                                 | 524        | DMAxSTA                                 |                |

| D                                                                |            | DMAxSTB                                 |                |

| Data Address Space                                               | 51         | Resources                               |                |

| Memory Map for dsPIC33EP128MC20X/50X,                            |            | Supported Peripherals                   |                |

| dsPIC33EP128GP50X Devices                                        |            | Doze Mode                               |                |

|                                                                  |            | DSP Engine                              | <br>44         |

| Memory Map for dsPIC33EP256MC20X/50X,                            |            | E                                       |                |

| dsPIC33EP256GP50X Devices                                        | 55         | _                                       |                |

| , , , , , , , , , , , , , , , , , , ,                            | <b>5</b> 0 | ECAN Message Buffers                    | 040            |

| dsPIC33EP32GP50X Devices                                         |            | Word 0                                  |                |

| Memory Map for dsPIC33EP512MC20X/50X,                            |            | Word 1                                  |                |

| dsPIC33EP512GP50X Devices                                        | 00         | Word 2                                  |                |

| Memory Map for dsPIC33EP64MC20X/50X,                             | 50         | Word 3                                  |                |

| dsPIC33EP64GP50X Devices                                         |            | Word 4                                  |                |

| Memory Map for PIC24EP128GP/MC20X/50X                            |            | Word 5                                  |                |

| Devices                                                          | 59         | Word 6                                  |                |

|                                                                  |            | Word 7                                  | 313            |

| PMD (PIC24EPXXXMC20X Devices)94             | CMxMSKCON (Comparator x Mask              |     |

|---------------------------------------------|-------------------------------------------|-----|

| PORTA (PIC24EPXXXGP/MC202,                  | Gating Control)                           | 368 |

| dsPIC33EPXXXGP/MC202/502 Devices) 104       | CMxMSKSRC (Comparator x Mask Source       |     |

| PORTA (PIC24EPXXXGP/MC203,                  | Select Control)                           | 366 |

| dsPIC33EPXXXGP/MC203/503 Devices) 103       | CORCON (Core Control)42                   |     |

| PORTA (PIC24EPXXXGP/MC204,                  | CRCCON1 (CRC Control 1)                   |     |

| dsPIC33EPXXXGP/MC204/504 Devices) 102       | CRCCON2 (CRC Control 2)                   |     |

| PORTA (PIC24EPXXXGP/MC206,                  | CRCXORH (CRC XOR Polynomial High)         |     |

| ·                                           |                                           |     |

| dsPIC33EPXXXGP/MC206/506 Devices) 99        | CRCXORL (CRC XOR Polynomial Low)          |     |

| PORTB (PIC24EPXXXGP/MC202,                  | CTMUCON1 (CTMU Control 1)                 |     |

| dsPIC33EPXXXGP/MC202/502 Devices) 104       | CTMUCON2 (CTMU Control 2)                 |     |

| PORTB (PIC24EPXXXGP/MC203,                  | CTMUICON (CTMU Current Control)           | 319 |

| dsPIC33EPXXXGP/MC203/503 Devices) 103       | CVRCON (Comparator Voltage                |     |

| PORTB (PIC24EPXXXGP/MC204,                  | Reference Control)                        | 371 |

| dsPIC33EPXXXGP/MC204/504 Devices) 102       | CxBUFPNT1 (ECANx Filter 0-3               |     |

| PORTB (PIC24EPXXXGP/MC206,                  | Buffer Pointer 1)                         | 300 |

| dsPIC33EPXXXGP/MC206/506 Devices) 99        | CxBUFPNT2 (ECANx Filter 4-7               |     |

| PORTC (PIC23EPXXXGP/MC203,                  | Buffer Pointer 2)                         | 301 |

| dsPIC33EPXXXGP/MC203/503 Devices) 103       | CxBUFPNT3 (ECANx Filter 8-11              |     |

| PORTC (PIC24EPXXXGP/MC204,                  | Buffer Pointer 3)                         | 301 |

| dsPIC33EPXXXGP/MC204/504 Devices) 102       | CxBUFPNT4 (ECANx Filter 12-15             |     |

| PORTC (PIC24EPXXXGP/MC206,                  | Buffer Pointer 4)                         | 302 |

| dsPIC33EPXXXGP/MC206/506 Devices) 99        | CxCFG1 (ECANx Baud Rate Configuration 1)  |     |

| PORTD (PIC24EPXXXGP/MC206,                  | CxCFG2 (ECANx Baud Rate Configuration 2)  |     |

| dsPIC33EPXXXGP/MC206/506 Devices) 100       | CxCTRL1 (ECANx Control 1)                 |     |

| PORTE (PIC24EPXXXGP/MC206,                  | CxCTRL2 (ECANx Control 2)                 |     |

| dsPIC33EPXXXGP/MC206/506 Devices) 100       | CxEC (ECANx Transmit/Receive Error Count) |     |

| PORTF (PIC24EPXXXGP/MC206,                  | CxFCTRL (ECANx FIFO Control)              |     |

| dsPIC33EPXXXGP/MC206/506 Devices) 100       | CxFEN1 (ECANx Acceptance Filter Enable 1) |     |

| PORTG (PIC24EPXXXGP/MC206 and               | CxFIFO (ECANx FIFO Status)                |     |

| dsPIC33EPXXXGP/MC206/506 Devices) 101       | CxFMSKSEL1 (ECANx Filter 7-0              | 204 |

| PTG78                                       | Mask Selection 1)                         | 304 |

| PWM (dsPIC33EPXXXMC20X/50X,                 | CxFMSKSEL2 (ECANx Filter 15-8             | 504 |

| •                                           |                                           | 205 |

| PIC24EPXXXMC20X Devices)79                  | Mask Selection 2)                         |     |

| PWM Generator 1 (dsPIC33EPXXXMC20X/50X,     | CXINTE (ECANX Interrupt Enable)           |     |

| PIC24EPXXXMC20X Devices)79                  | CxINTF (ECANx Interrupt Flag)             | 295 |

| PWM Generator 2 (dsPIC33EPXXXMC20X/50X,     | CxRXFnEID (ECANx Acceptance Filter n      | 004 |

| PIC24EPXXXMC20X Devices)80                  | Extended Identifier)                      | 304 |

| PWM Generator 3 (dsPIC33EPXXXMC20X/50X,     | CxRXFnSID (ECANx Acceptance Filter n      |     |

| PIC24EPXXXMC20X Devices)80                  | Standard Identifier)                      |     |

| QEI1 (dsPIC33EPXXXMC20X/50X,                | CxRXFUL1 (ECANx Receive Buffer Full 1)    |     |

| PIC24EPXXXMC20X Devices)81                  | CxRXFUL2 (ECANx Receive Buffer Full 2)    | 307 |

| Reference Clock93                           | CxRXMnEID (ECANx Acceptance Filter Mask n |     |

| SPI1 and SPI283                             | Extended Identifier)                      | 306 |

| System Control93                            | CxRXMnSID (ECANx Acceptance Filter Mask n |     |

| Time1 through Time575                       | Standard Identifier)                      | 306 |

| UART1 and UART282                           | CxRXOVF1 (ECANx Receive                   |     |

| Registers                                   | Buffer Overflow 1)                        | 308 |

| AD1CHS0 (ADC1 Input Channel 0 Select)       | CxRXOVF2 (ECANx Receive                   |     |

| AD1CHS123 (ADC1 Input                       | Buffer Overflow 2)                        | 308 |

| Channel 1, 2, 3 Select)                     | CxTRmnCON (ECANx TX/RX                    |     |

| AD1CON1 (ADC1 Control 1)325                 | Buffer mn Control)                        | 309 |

| AD1CON2 (ADC1 Control 2)327                 | CxVEC (ECANx Interrupt Code)              |     |

| AD1CON3 (ADC1 Control 3)329                 | DEVID (Device ID)                         |     |

| AD1CON4 (ADC1 Control 4)                    | DEVREV (Device Revision)                  |     |

| AD1CSSH (ADC1 Input Scan Select High)       | DMALCA (DMA Last Channel Active Status)   |     |

| AD1CSSL (ADC1 Input Scan Select Low)        | DMAPPS (DMA Ping-Pong Status)             |     |

| ALTDTRx (PWMx Alternate Dead-Time)238       | DMAPWC (DMA Peripheral Write              |     |

| AUXCONx (PWMx Auxiliary Control)247         | Collision Status)                         | 1⊿Ω |

| CHOP (PWMx Chop Clock Generator)247         | DMARQC (DMA Request Collision Status)     |     |

| CLKDIV (Clock Divisor)158                   | DMAXCNT (DMA Channel x Transfer Count)    |     |

| ,                                           |                                           |     |

| CMSTAT (On Amp/Comparator Status) 360       | DMAXCON (DMA Channel x Control)           | 142 |

| CMSTAT (Op Amp/Comparator Status)           | DMAXPAD (DMA Channel x                    | 146 |

| CMxCON (Comparator x Control, x = 1,2,3)362 | Peripheral Address)                       |     |

| CMxFLTR (Comparator x Filter Control)370    | DMAxREQ (DMA Channel x IRQ Select)        | 143 |

| dsPIC33EPXXXGP5 | 0X, dsPIC33EPXXXN | 1C20X/50X AND P | IC24EPXXXGP/M | C20X |

|-----------------|-------------------|-----------------|---------------|------|

| NOTES:          |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |