Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                    |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

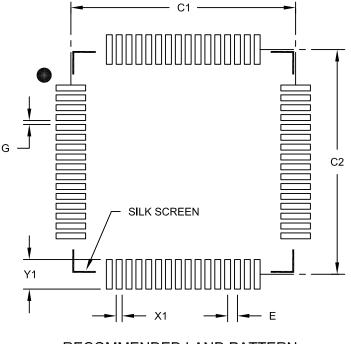

| Package / Case             | 48-UFQFN Exposed Pad                                                            |

| Supplier Device Package    | 48-UQFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc504-e-mv |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

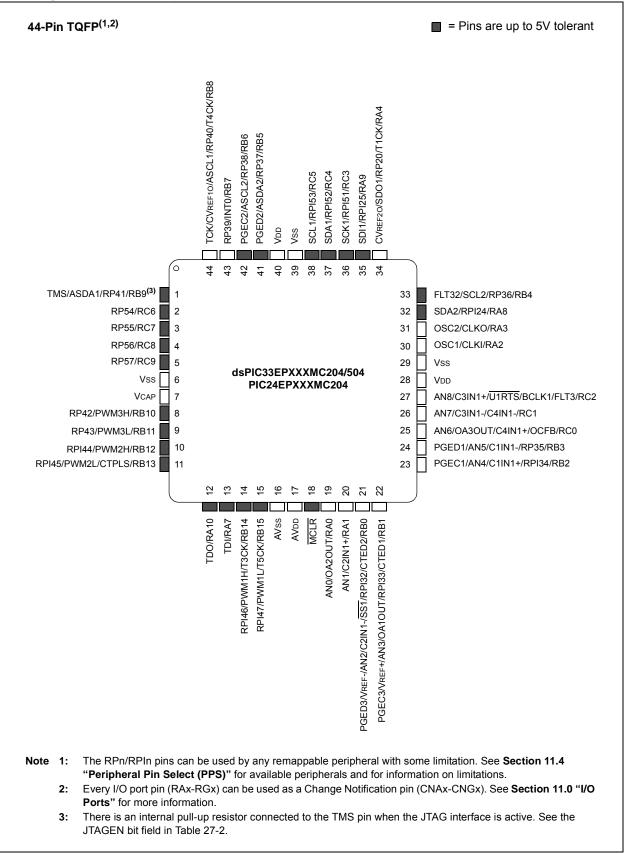

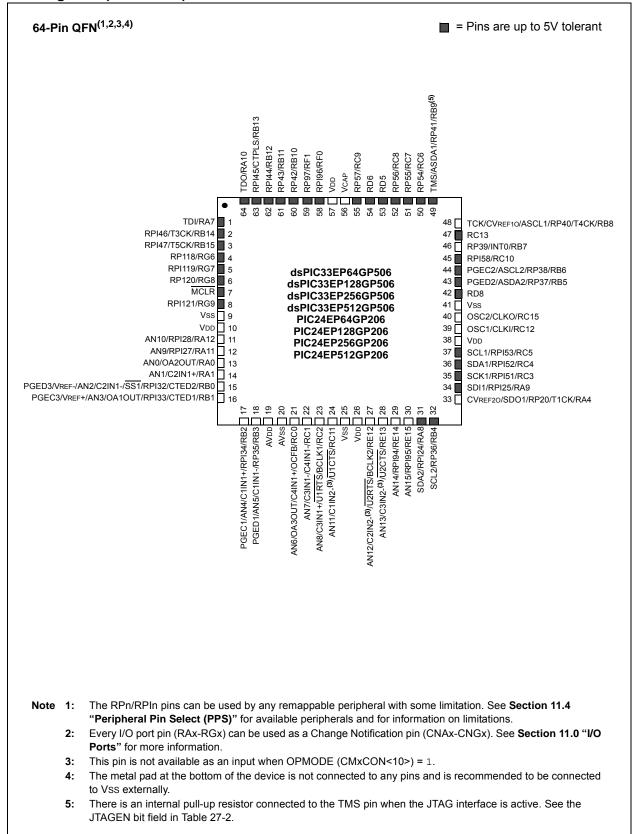

# Pin Diagrams (Continued)

# 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section of the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X Digital Signal Controller (DSC) and Microcontroller (MCU) devices.

dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

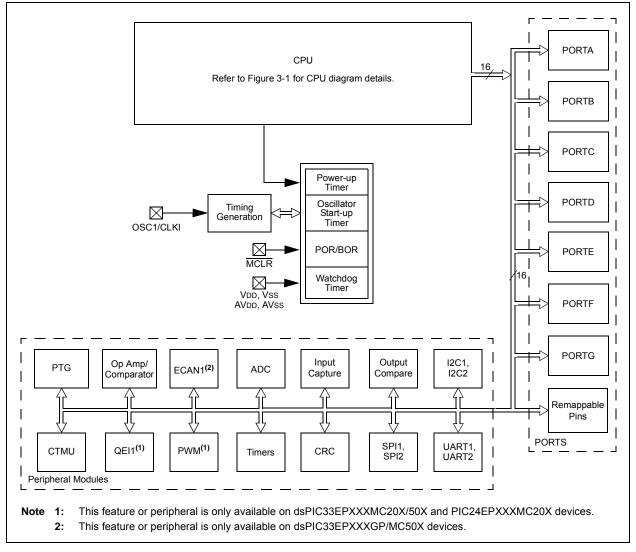

Figure 1-1 shows a general block diagram of the core and peripheral modules. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

# FIGURE 1-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X BLOCK DIAGRAM

| R/W-0               | U-0                          | R/W-0                                                                        | R/W-0                   | R/W-0                       | R-0                | R-0                | R-0                |  |  |  |

|---------------------|------------------------------|------------------------------------------------------------------------------|-------------------------|-----------------------------|--------------------|--------------------|--------------------|--|--|--|

| VAR                 | —                            | US1 <sup>(1)</sup>                                                           | US0 <sup>(1)</sup>      | EDT <sup>(1,2)</sup>        | DL2 <sup>(1)</sup> | DL1 <sup>(1)</sup> | DL0 <sup>(1)</sup> |  |  |  |

| bit 15              |                              |                                                                              |                         |                             |                    |                    | bit                |  |  |  |

| R/W-0               | R/W-0                        | R/W-1                                                                        | R/W-0                   | R/C-0                       | R-0                | R/W-0              | R/W-0              |  |  |  |

| SATA <sup>(1)</sup> | SATB <sup>(1)</sup>          | SATDW <sup>(1)</sup>                                                         | ACCSAT <sup>(1)</sup>   | IPL3(3)                     | SFA                | RND <sup>(1)</sup> | IF(1)              |  |  |  |

| bit 7               | I                            |                                                                              |                         |                             | I                  | 1                  | bit                |  |  |  |

| Legend:             |                              | C = Clearable                                                                | e bit                   |                             |                    |                    |                    |  |  |  |

| R = Readabl         | e bit                        | W = Writable                                                                 | bit                     | U = Unimpler                | mented bit, read   | d as '0'           |                    |  |  |  |

| -n = Value at       | POR                          | '1' = Bit is set                                                             | t                       | '0' = Bit is cle            | ared               | x = Bit is unkr    | nown               |  |  |  |

| bit 15              | 1 = Variable                 | le Exception Pro<br>exception proce                                          | essing latency          | is enabled                  |                    |                    |                    |  |  |  |

| bit 14              |                              | nted: Read as '                                                              |                         |                             |                    |                    |                    |  |  |  |

| bit 13-12           | -                            | SP Multiply Uns                                                              |                         | Control bits <sup>(1)</sup> |                    |                    |                    |  |  |  |

|                     | 01 = DSP er<br>00 = DSP er   | ngine multiplies<br>ngine multiplies<br>ngine multiplies                     | are unsigned are signed |                             |                    |                    |                    |  |  |  |

| bit 11              | •                            | O Loop Terminatives executing Dot<br>t                                       |                         |                             | iteration          |                    |                    |  |  |  |

| bit 10-8            |                              | Loop Nesting<br>oops are active                                              |                         | (1)                         |                    |                    |                    |  |  |  |

|                     | •                            |                                                                              |                         |                             |                    |                    |                    |  |  |  |

|                     | •                            |                                                                              |                         |                             |                    |                    |                    |  |  |  |

|                     | 001 = 1 DO k<br>000 = 0 DO k | oop is active<br>oops are active                                             |                         |                             |                    |                    |                    |  |  |  |

| bit 7               | SATA: ACCA                   | A Saturation En                                                              | able bit <sup>(1)</sup> |                             |                    |                    |                    |  |  |  |

|                     |                              | ator A saturatio<br>ator A saturatio                                         |                         |                             |                    |                    |                    |  |  |  |

| bit 6               | SATB: ACCE                   | B Saturation En                                                              | able bit <sup>(1)</sup> |                             |                    |                    |                    |  |  |  |

|                     |                              | ator B saturatio<br>ator B saturatio                                         |                         |                             |                    |                    |                    |  |  |  |

| bit 5               | SATDW: Dat                   | SATDW: Data Space Write from DSP Engine Saturation Enable bit <sup>(1)</sup> |                         |                             |                    |                    |                    |  |  |  |

|                     |                              | ace write satura<br>ace write satura                                         |                         | I                           |                    |                    |                    |  |  |  |

| bit 4               |                              | cumulator Satu                                                               |                         | elect bit <sup>(1)</sup>    |                    |                    |                    |  |  |  |

|                     |                              | uration (super s<br>uration (normal                                          | ,                       |                             |                    |                    |                    |  |  |  |

| bit 3               |                              | nterrupt Priority                                                            |                         |                             |                    |                    |                    |  |  |  |

|                     |                              | errupt Priority Le<br>errupt Priority Le                                     |                         |                             |                    |                    |                    |  |  |  |

|                     | nis bit is availabl          |                                                                              | PXXXMC20X/              | 50X and dsPl                | C33EPXXXGP         | 50X devices on     | ly.                |  |  |  |

| 2: Th               | nis bit is always            | reau as 0.                                                                   |                         |                             |                    |                    |                    |  |  |  |

# REGISTER 3-2: CORCON: CORE CONTROL REGISTER

**3:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

# 4.2.5 X AND Y DATA SPACES

# The dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X core has two Data Spaces, X and Y. These Data Spaces can be considered either separate (for some DSP instructions) or as one unified linear address range (for MCU instructions). The Data Spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X Data Space is used by all instructions and supports all addressing modes. X Data Space has separate read and write data buses. The X read data bus is the read data path for all instructions that view Data Space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y Data Space is used in concert with the X Data Space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y Data Spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X Data Space. Modulo Addressing and Bit-Reversed Addressing are not present in PIC24EPXXXGP/MC20X devices.

All data memory writes, including in DSP instructions, view Data Space as combined X and Y address space. The boundary between the X and Y Data Spaces is device-dependent and is not user-programmable.

# 4.3 Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

# 4.3.1 KEY RESOURCES

- "Program Memory" (DS70613) in the "dsPIC33/ PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

# TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|---------|---------|--------|-------|-------|----------|---------|---------|---------|---------|--------|---------|--------|---------------|

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR | COVAERR | COVBERR | OVATE  | OVBTE | COVTE | SFTACERR | DIV0ERR | DMACERR | MATHERR | ADDRERR | STKERR | OSCFAIL |        | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP | _       | _       | _      | _     | _     | _        | —       | _       | _       | —       | INT2EP | INT1EP  | INT0EP | 8000          |

| INTCON3      | 08C4  |        | _      | _      | —       | _       | _      |       | _     | _        | —       | DAE     | DOOVR   | —       | _      | _       |        | 0000          |

| INTCON4      | 08C6  |        | _      |        |         |         | Ι      | _     |       |          | —       | _       |         | —       |        |         | SGHT   | 0000          |

| INTTREG      | 08C8  | _      | _      | _      | _       |         | ILR<   | 3:0>  |       |          |         |         | VECNU   | M<7:0>  |        |         |        | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 7.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

# 7.3.1 KEY RESOURCES

- "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

# 7.4 Interrupt Control and Status Registers

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- INTTREG

# 7.4.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior and also contains the Global Interrupt Enable bit (GIE).

INTCON3 contains the status flags for the DMA and DO stack overflow status trap sources.

The INTCON4 register contains the software generated hard trap status bit (SGHT).

# 7.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

# 7.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

# 7.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

# 7.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number bits (VECNUM<7:0>) and Interrupt Priority Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

# 7.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers refer to "**CPU**" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

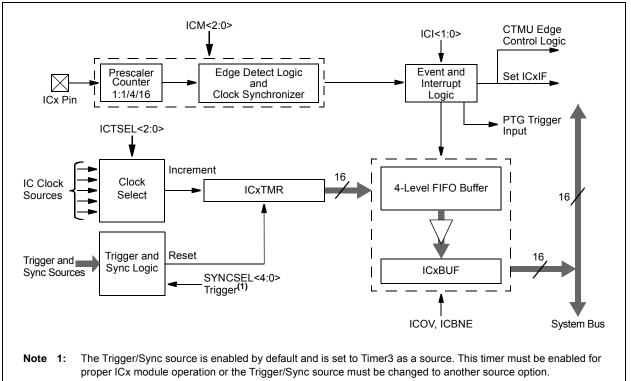

# 14.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70352) in the "dsPIC33/dsPIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices support four input capture channels.

Key features of the input capture module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 19 user-selectable Trigger/Sync sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- Configurable interrupt generation

- Up to six clock sources available for each module, driving a separate internal 16-bit counter

# 14.2 Input Capture Registers

# REGISTER 14-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0   |

|--------|-----|--------|---------|---------|---------|-----|-------|

| _      | —   | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 |     | —     |

| bit 15 |     |        |         |         |         |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/HC/HS-0 | R/HC/HS-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----------|-----------|-------|-------|-------|

| —     | ICI1  | ICI0  | ICOV      | ICBNE     | ICM2  | ICM1  | ICM0  |

| bit 7 |       |       |           |           |       |       | bit 0 |

| Legend: HC = Hardware Clearable bit HS = Hardware Se |                  | HS = Hardware Settable b  | bit                |

|------------------------------------------------------|------------------|---------------------------|--------------------|

| R = Readable bit                                     | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR                                    | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture Stop in Idle Control bit                                                                                                              |

|           | 1 = Input capture will Halt in CPU Idle mode                                                                                                                |

|           | 0 = Input capture will continue to operate in CPU Idle mode                                                                                                 |

| bit 12-10 | ICTSEL<2:0>: Input Capture Timer Select bits                                                                                                                |

|           | 111 = Peripheral clock (FP) is the clock source of the ICx                                                                                                  |

|           | 110 = Reserved                                                                                                                                              |

|           | 101 = Reserved                                                                                                                                              |

|           | 100 = T1CLK is the clock source of the ICx (only the synchronous clock is supported)<br>011 = T5CLK is the clock source of the ICx                          |

|           | 010 = T4CLK is the clock source of the ICx                                                                                                                  |

|           | 001 = T2CLK is the clock source of the ICx                                                                                                                  |

|           | 000 = T3CLK is the clock source of the ICx                                                                                                                  |

| bit 9-7   | Unimplemented: Read as '0'                                                                                                                                  |

| bit 6-5   | ICI<1:0>: Number of Captures per Interrupt Select bits (this field is not used if ICM<2:0> = 001 or 111)                                                    |

|           | 11 = Interrupt on every fourth capture event                                                                                                                |

|           | 10 = Interrupt on every third capture event                                                                                                                 |

|           | 01 = Interrupt on every second capture event<br>00 = Interrupt on every capture event                                                                       |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                    |

| bit 4     | 1 = Input capture buffer overflow occurred                                                                                                                  |

|           | 0 = No input capture buffer overflow occurred                                                                                                               |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                                |

|           | 1 = Input capture buffer is not empty, at least one more capture value can be read                                                                          |

|           | 0 = Input capture buffer is empty                                                                                                                           |

| bit 2-0   | ICM<2:0>: Input Capture Mode Select bits                                                                                                                    |

|           | 111 = Input capture functions as interrupt pin only in CPU Sleep and Idle modes (rising edge detect only, all other control bits are not applicable)        |

|           | 110 = Unused (module is disabled)                                                                                                                           |

|           | 101 = Capture mode, every 16th rising edge (Prescaler Capture mode)                                                                                         |

|           | <ul> <li>100 = Capture mode, every 4th rising edge (Prescaler Capture mode)</li> <li>011 = Capture mode, every rising edge (Simple Capture mode)</li> </ul> |

|           | 010 = Capture mode, every falling edge (Simple Capture mode)                                                                                                |

|           | 001 = Capture mode, every edge rising and falling (Edge Detect mode (ICI<1:0>) is not used in this mode)                                                    |

|           | 000 = Input capture module is turned off                                                                                                                    |

# 17.0 QUADRATURE ENCODER INTERFACE (QEI) MODULE (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Quadrature Encoder Interface (QEI)" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This chapter describes the Quadrature Encoder Interface (QEI) module and associated operational modes. The QEI module provides the interface to incremental encoders for obtaining mechanical position data.

The operational features of the QEI module include:

- 32-Bit Position Counter

- 32-Bit Index Pulse Counter

- 32-Bit Interval Timer

- 16-Bit Velocity Counter

- 32-Bit Position Initialization/Capture/Compare High register

- 32-Bit Position Compare Low register

- x4 Quadrature Count mode

- External Up/Down Count mode

- External Gated Count mode

- External Gated Timer mode

- Internal Timer mode

Figure 17-1 illustrates the QEI block diagram.

| U-0                     | U-0                                                                | U-0                                | R-0     | R-0              | R-0             | R-0             | R-0     |  |  |  |  |

|-------------------------|--------------------------------------------------------------------|------------------------------------|---------|------------------|-----------------|-----------------|---------|--|--|--|--|

| _                       | _                                                                  |                                    | FILHIT4 | FILHIT3          | FILHIT2         | FILHIT1         | FILHIT0 |  |  |  |  |

| bit 15                  | <b>I</b>                                                           | •                                  |         |                  |                 |                 | bit 8   |  |  |  |  |

|                         |                                                                    |                                    |         |                  |                 |                 |         |  |  |  |  |

| U-0                     | R-1                                                                | R-0                                | R-0     | R-0              | R-0             | R-0             | R-0     |  |  |  |  |

| _                       | ICODE6                                                             | ICODE5                             | ICODE4  | ICODE3           | ICODE2          | ICODE1          | ICODE0  |  |  |  |  |

| bit 7                   |                                                                    |                                    |         |                  |                 |                 | bit     |  |  |  |  |

| Logondi                 |                                                                    |                                    |         |                  |                 |                 |         |  |  |  |  |

| Legend:<br>R = Readable | - hit                                                              |                                    | hit.    |                  | nonted hit rea  | d aa 'O'        |         |  |  |  |  |

| -n = Value at           |                                                                    | W = Writable                       |         | '0' = Bit is cle | mented bit, rea |                 |         |  |  |  |  |

| -n = value at           | POR                                                                | '1' = Bit is set                   |         | 0 = Bit is cie   | ared            | x = Bit is unkr | IOWN    |  |  |  |  |

| bit 15-13               | Unimplemen                                                         | ted: Read as '                     | 0'      |                  |                 |                 |         |  |  |  |  |

| bit 12-8                | =                                                                  | Filter Hit Num                     |         |                  |                 |                 |         |  |  |  |  |

|                         |                                                                    | 1 = Reserved                       |         |                  |                 |                 |         |  |  |  |  |

|                         | 01111 <b>= Filte</b>                                               | r 15                               |         |                  |                 |                 |         |  |  |  |  |

|                         | •                                                                  |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         | •                                                                  |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         | •<br>00001 = Filter 1                                              |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         | 00001 = Filte                                                      |                                    |         |                  |                 |                 |         |  |  |  |  |

| bit 7                   |                                                                    |                                    | 0'      |                  |                 |                 |         |  |  |  |  |

| bit 6-0                 | Unimplemented: Read as '0'<br>ICODE<6:0>: Interrupt Flag Code bits |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         | 1000101-1111111 = Reserved                                         |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         |                                                                    | IFO almost full                    |         |                  |                 |                 |         |  |  |  |  |

|                         |                                                                    | eceiver overflo                    |         |                  |                 |                 |         |  |  |  |  |

|                         | 1000010 = K<br>1000001 = E                                         | /ake-up interru<br>rror interrupt  | μ       |                  |                 |                 |         |  |  |  |  |

|                         | 1000000 = N                                                        |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         | •                                                                  |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         | •                                                                  |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         | •                                                                  |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         |                                                                    | 11111 = Rese                       |         |                  |                 |                 |         |  |  |  |  |

|                         | 0001111 = RB15 buffer interrupt                                    |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         | •                                                                  |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         |                                                                    |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         | 0001001 <b>= R</b>                                                 |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         |                                                                    | B8 buffer inter                    |         |                  |                 |                 |         |  |  |  |  |

|                         |                                                                    | RB7 buffer inte<br>RB6 buffer inte |         |                  |                 |                 |         |  |  |  |  |

|                         |                                                                    | RB5 buffer inte                    |         |                  |                 |                 |         |  |  |  |  |

|                         |                                                                    | RB4 buffer inte                    |         |                  |                 |                 |         |  |  |  |  |

|                         | 0000011 <b>= T</b>                                                 | RB3 buffer inte                    | errupt  |                  |                 |                 |         |  |  |  |  |

|                         |                                                                    |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         |                                                                    | RB2 buffer inte<br>RB1 buffer inte |         |                  |                 |                 |         |  |  |  |  |

# REGISTER 21-3: CxVEC: ECANx INTERRUPT CODE REGISTER

# 22.2 CTMU Control Registers

| REGISTER 2    | 22-1: CTM                    | UCON1: CTMU                                           | J CONTROL                         | REGISTER          | 1                |                        |        |

|---------------|------------------------------|-------------------------------------------------------|-----------------------------------|-------------------|------------------|------------------------|--------|

| R/W-0         | U-0                          | R/W-0                                                 | R/W-0                             | R/W-0             | R/W-0            | R/W-0                  | R/W-0  |

| CTMUEN        | _                            | CTMUSIDL                                              | TGEN                              | EDGEN             | EDGSEQEN         | IDISSEN <sup>(1)</sup> | CTTRIG |

| bit 15        |                              |                                                       |                                   |                   |                  |                        | bit 8  |

|               |                              |                                                       |                                   |                   |                  |                        |        |

| U-0           | U-0                          | U-0                                                   | U-0                               | U-0               | U-0              | U-0                    | U-0    |

|               |                              | —                                                     | _                                 |                   | <u> </u>         |                        | _      |

| bit 7         |                              |                                                       |                                   |                   |                  |                        | bit 0  |

|               |                              |                                                       |                                   |                   |                  |                        |        |

| Legend:       |                              |                                                       |                                   |                   |                  |                        |        |

| R = Readable  | e bit                        | W = Writable b                                        | oit                               | U = Unimplen      | nented bit, read | as '0'                 |        |

| -n = Value at | POR                          | '1' = Bit is set                                      |                                   | '0' = Bit is clea | own              |                        |        |

| bit 15        | 1 = Module                   | TMU Enable bit<br>is enabled<br>is disabled           |                                   |                   |                  |                        |        |

| bit 14        | Unimpleme                    | nted: Read as '0                                      | 3                                 |                   |                  |                        |        |

| bit 13        | 1 = Disconti<br>0 = Continue | CTMU Stop in lo<br>nues module ope<br>es module opera | eration when a<br>tion in Idle ma |                   | lle mode         |                        |        |

| bit 12        | TGEN: Time                   | Generation Ena                                        | ble bit                           |                   |                  |                        |        |

### REGISTER 22-1: CTMUCON1: CTMU CONTROL REGISTER 1

|         | <ul> <li>1 = Hardware modules are used to trigger edges (TMRx, CTEDx, etc.)</li> <li>0 = Software is used to trigger edges (manual set of EDGxSTAT)</li> </ul> |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10  | EDGSEQEN: Edge Sequence Enable bit                                                                                                                             |

|         | <ul> <li>1 = Edge 1 event must occur before Edge 2 event can occur</li> <li>0 = No edge sequence is needed</li> </ul>                                          |

| bit 9   | IDISSEN: Analog Current Source Control bit <sup>(1)</sup>                                                                                                      |

|         | <ul> <li>1 = Analog current source output is grounded</li> <li>0 = Analog current source output is not grounded</li> </ul>                                     |

| bit 8   | CTTRIG: ADC Trigger Control bit                                                                                                                                |

|         | 1 = CTMU triggers ADC start of conversion                                                                                                                      |

|         | 0 = CTMU does not trigger ADC start of conversion                                                                                                              |

| bit 7-0 | Unimplemented: Read as '0'                                                                                                                                     |

1 = Enables edge delay generation0 = Disables edge delay generation

**EDGEN:** Edge Enable bit

bit 11

**Note 1:** The ADC module Sample-and-Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitance measurement must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|               | 23-2: Al         |                                                      | CONTROL REG                   |                 |                   |                  |              |

|---------------|------------------|------------------------------------------------------|-------------------------------|-----------------|-------------------|------------------|--------------|

| R/W-0         | R/W-             | -0 R/W-0                                             | U-0                           | U-0             | R/W-0             | R/W-0            | R/W-0        |

| VCFG2         | VCFC             | G1 VCFG0                                             | —                             | —               | CSCNA             | CHPS1            | CHPS0        |

| bit 15        |                  |                                                      |                               |                 |                   |                  | bit          |

| R-0           | R/W-             | -0 R/W-0                                             | R/W-0                         | R/W-0           | R/W-0             | R/W-0            | R/W-0        |

| BUFS          | SMP              |                                                      | SMPI2                         | SMPI1           | SMPI0             | BUFM             | ALTS         |

| bit 7         | Sivil            |                                                      | SIVILIZ                       |                 |                   | BOTIM            | bit          |

| Logondi       |                  |                                                      |                               |                 |                   |                  |              |

| Legend:       | . hit            | VV - VV/ritable                                      |                               |                 | montod hit roo    |                  |              |

| R = Readable  |                  | W = Writable                                         |                               |                 | mented bit, read  |                  |              |

| -n = Value at | POR              | '1' = Bit is se                                      | et '(                         | )' = Bit is cle | eared             | x = Bit is unkr  | nown         |

| bit 15-13     | VCFG<2           | 2:0>: Converter Vol                                  | tage Reference C              | onfiguration    | bits              |                  |              |

|               | Value            | VREFH                                                | VREFL                         |                 |                   |                  |              |

|               | 000              | Avdd                                                 | Avss                          |                 |                   |                  |              |

|               | 001              | External VREF+                                       | Avss                          |                 |                   |                  |              |

|               | 010              | Avdd                                                 | External VREF-                |                 |                   |                  |              |

|               | 011              | External VREF+                                       | External VREF-                |                 |                   |                  |              |

|               | 1xx              | Avdd                                                 | Avss                          |                 |                   |                  |              |

| bit 12-11     | Unimple          | emented: Read as                                     | '0'                           |                 |                   |                  |              |

| bit 10        | -                | : Input Scan Select                                  |                               |                 |                   |                  |              |

|               |                  | ns inputs for CH0+                                   |                               | JXA             |                   |                  |              |

|               |                  | s not scan inputs                                    | 5 1                           |                 |                   |                  |              |

| bit 9-8       | CHPS<1           | 1:0>: Channel Sele                                   | ct bits                       |                 |                   |                  |              |

|               | <u>In 12-bit</u> | mode (AD21B = 1                                      | <u>), the CHPS&lt;1:0&gt;</u> | bits are Uni    | mplemented an     | d are Read as    | <u>'0':</u>  |

|               |                  | nverts CH0, CH1, (                                   |                               |                 |                   |                  |              |

|               |                  | nverts CH0 and CH<br>nverts CH0                      | 11                            |                 |                   |                  |              |

| L:1 7         |                  |                                                      |                               |                 |                   |                  |              |

| bit 7         |                  | Buffer Fill Status bit<br>C is currently filling t   |                               | -               | o ucor opplicat   | ion chould coor  | oo data in t |

|               |                  | half of the buffer                                   | the second hall of            | line buller, li | ie user applicat  |                  |              |

|               |                  | C is currently filling                               | the first half of the         | e buffer; the   | e user applicatio | on should acce   | ss data in t |

|               |                  | ond half of the buffe                                |                               |                 |                   |                  |              |

| bit 6-2       | SMPI<4           | :0>: Increment Rat                                   | e bits                        |                 |                   |                  |              |

|               |                  | DDMAEN = 0:                                          |                               |                 |                   |                  |              |

|               |                  | Generates interru                                    |                               |                 |                   |                  |              |

|               | x1110 =          | Generates interru                                    | pt after completion           | of every 15     | oth sample/conv   | ersion operation | on           |

|               | •                |                                                      |                               |                 |                   |                  |              |

|               | •                |                                                      |                               |                 |                   |                  |              |

|               |                  | Generates interru                                    |                               |                 |                   |                  | n            |

|               |                  | <ul> <li>Generates interru</li> </ul>                | pt after completior           | of every sa     | ample/conversion  | n operation      |              |

|               |                  | $\frac{\text{DDMAEN} = 1}{\text{Increments the DN}}$ | 11 address offer a            | omplation of    | four 20rd of      | male (een verei  | on onoratio  |

|               |                  | Increments the DI<br>Increments the DI               |                               |                 |                   |                  |              |

|               | •                |                                                      |                               | ompletion (     | n every orac sa   |                  |              |

|               |                  |                                                      |                               |                 |                   |                  |              |

|               | •                |                                                      |                               |                 |                   |                  |              |

|               | •                | - Increments the DI                                  |                               |                 |                   |                  |              |

#### . . ACOND. ADCA CONTROL DECISTED 2

| R/W-0                                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

|----------------------------------------------------|-------|-------|-------|------------------------------------|-------|-------|-------|--|

| CSS15                                              | CSS14 | CSS13 | CSS12 | CSS11                              | CSS10 | CSS9  | CSS8  |  |

| bit 15                                             |       |       |       | ·                                  | •     | ·     | bit 8 |  |

|                                                    |       |       |       |                                    |       |       |       |  |

| R/W-0                                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

| CSS7                                               | CSS6  | CSS5  | CSS4  | CSS3                               | CSS2  | CSS1  | CSS0  |  |

| bit 7                                              | -     |       |       |                                    | •     |       | bit ( |  |

|                                                    |       |       |       |                                    |       |       |       |  |

| Legend:                                            |       |       |       |                                    |       |       |       |  |

| R = Readable bit W = Writable bit                  |       |       | bit   | U = Unimplemented bit, read as '0' |       |       |       |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cl |       |       | eared | x = Bit is unk                     | nown  |       |       |  |

# REGISTER 23-8: AD1CSSL: ADC1 INPUT SCAN SELECT REGISTER LOW<sup>(1,2)</sup>

bit 15-0 CSS<15:0>: ADC1 Input Scan Selection bits

1 = Selects ANx for input scan

0 = Skips ANx for input scan

**Note 1:** On devices with less than 16 analog inputs, all AD1CSSL bits can be selected by the user. However, inputs selected for scan, without a corresponding input on the device, convert VREFL.

**2:** CSSx = ANx, where x = 0-15.

| DC CHARACTER  | ISTICS |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |            |       |  |  |

|---------------|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|--|--|

| Parameter No. | Тур.   | Max. | Units                                                                                                                                                                                                                                                                                 | Conditions |       |  |  |

| DC61d         | 8      |      | μΑ                                                                                                                                                                                                                                                                                    | -40°C      |       |  |  |

| DC61a         | 10     | —    | μA                                                                                                                                                                                                                                                                                    | +25°C      | 2.21/ |  |  |

| DC61b         | 12     | —    | μA                                                                                                                                                                                                                                                                                    | +85°C      | 3.3V  |  |  |

| DC61c         | 13     | —    | μA                                                                                                                                                                                                                                                                                    | +125°C     |       |  |  |

# TABLE 30-9: DC CHARACTERISTICS: WATCHDOG TIMER DELTA CURRENT ( $\Delta$ Iwdt)<sup>(1)</sup>

**Note 1:** The  $\triangle$ IwDT current is the additional current consumed when the module is enabled. This current should be added to the base IPD current. All parameters are characterized but not tested during manufacturing.

# TABLE 30-10: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARACTER         | (unless oth                         | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |       |            |        |       |                |  |  |

|----------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|--------|-------|----------------|--|--|

| Parameter No.        | Doze<br>Ratio                       | Units                                                                                                                                                                                                                                                                                   |       | Conditions |        |       |                |  |  |

| Doze Current (IDC    | Doze Current (IDOZE) <sup>(1)</sup> |                                                                                                                                                                                                                                                                                         |       |            |        |       |                |  |  |

| DC73a <sup>(2)</sup> | 35                                  |                                                                                                                                                                                                                                                                                         | 1:2   | mA         | -40°C  | 3.3V  | Fosc = 140 MHz |  |  |

| DC73g                | 20                                  | 30                                                                                                                                                                                                                                                                                      | 1:128 | mA         | -40 C  |       |                |  |  |

| DC70a <sup>(2)</sup> | 35                                  | _                                                                                                                                                                                                                                                                                       | 1:2   | mA         | +25°C  | 3.3V  |                |  |  |

| DC70g                | 20                                  | 30                                                                                                                                                                                                                                                                                      | 1:128 | mA         | +25 C  | 3.3V  | Fosc = 140 MHz |  |  |

| DC71a <sup>(2)</sup> | 35                                  | _                                                                                                                                                                                                                                                                                       | 1:2   | mA         | 105%0  | 2.21/ |                |  |  |

| DC71g                | 20                                  | 30                                                                                                                                                                                                                                                                                      | 1:128 | mA         | +85°C  | 3.3V  | Fosc = 140 MHz |  |  |

| DC72a <sup>(2)</sup> | 28                                  | —                                                                                                                                                                                                                                                                                       | 1:2   | mA         | +125°C | 2 21/ | Fosc = 120 MHz |  |  |

| DC72g                | 15                                  | 30                                                                                                                                                                                                                                                                                      | 1:128 | mA         | +125 C | 3.3V  |                |  |  |

**Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

- Oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU is executing while(1) statement

- · JTAG is disabled

- 2: Parameter is characterized but not tested in manufacturing.

# 30.2 AC Characteristics and Timing Parameters

This section defines dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X AC characteristics and timing parameters.

# TABLE 30-15: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated) |

|--------------------|--------------------------------------------------------------------------|

| AC CHARACTERISTICS | $\begin{array}{llllllllllllllllllllllllllllllllllll$                     |

|                    | Characteristics".                                                        |

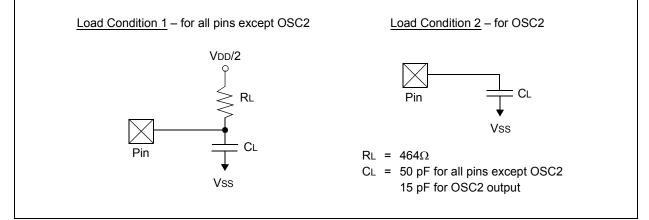

# FIGURE 30-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

# TABLE 30-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                          |

|--------------|--------|-----------------------|------|------|------|-------|---------------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              | _    | —    | 15   |       | In XT and HS modes, when<br>external clock is used to drive<br>OSC1 |

| DO56         | Сю     | All I/O Pins and OSC2 | —    |      | 50   | pF    | EC mode                                                             |

| DO58         | Св     | SCLx, SDAx            | _    | _    | 400  | pF    | In I <sup>2</sup> C™ mode                                           |

| AC CHARACTERISTICS |           |                                       |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |               |       |                                                                               |

|--------------------|-----------|---------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|-------|-------------------------------------------------------------------------------|

| Param<br>No.       | Symbol    | Charao                                | cteristic <sup>(1)</sup>  | Min.                                                                                                                                                                                                                                                                                | Тур. | Max.          | Units | Conditions                                                                    |

| TB10               | TtxH      | TxCK High<br>Time                     | Synchronous<br>mode       | Greater of:<br>20 or<br>(Tcy + 20)/N                                                                                                                                                                                                                                                | _    | _             | ns    | Must also meet<br>Parameter TB15,<br>N = prescale<br>value<br>(1, 8, 64, 256) |

| TB11               | TtxL      | TxCK Low<br>Time                      | Synchronous<br>mode       | Greater of:<br>20 or<br>(Tcy + 20)/N                                                                                                                                                                                                                                                | _    |               | ns    | Must also meet<br>Parameter TB15,<br>N = prescale<br>value<br>(1, 8, 64, 256) |

| TB15               | TtxP      | TxCK<br>Input<br>Period               | Synchronous<br>mode       | Greater of:<br>40 or<br>(2 Tcy + 40)/N                                                                                                                                                                                                                                              | —    | —             | ns    | N = prescale<br>value<br>(1, 8, 64, 256)                                      |

| TB20               | TCKEXTMRL | Delay from<br>Clock Edge<br>Increment | External TxCK<br>to Timer | 0.75 Tcy + 40                                                                                                                                                                                                                                                                       | —    | 1.75 Tcy + 40 | ns    |                                                                               |

| <b>TABLE 30-24</b> | TIMER2 AND TIM | IER4 (TYPE B TIMER | ER) EXTERNAL CLOCK TIMING REQUIREMENTS | j. |

|--------------------|----------------|--------------------|----------------------------------------|----|

|--------------------|----------------|--------------------|----------------------------------------|----|

Note 1: These parameters are characterized, but are not tested in manufacturing.

# TABLE 30-25: TIMER3 AND TIMER5 (TYPE C TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |           |                                           |                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |   |   |    |                                          |

|--------------------|-----------|-------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|----|------------------------------------------|

| Param<br>No.       | Symbol    | Charac                                    | teristic <sup>(1)</sup>     | Min. Typ. Max. Units Conditions                                                                                                                                                                                                                                                     |   |   |    | Conditions                               |

| TC10               | TtxH      | TxCK High<br>Time                         | Synchronous                 | Tcy + 20                                                                                                                                                                                                                                                                            |   |   | ns | Must also meet<br>Parameter TC15         |

| TC11               | TtxL      | TxCK Low<br>Time                          | Synchronous                 | Тсү + 20                                                                                                                                                                                                                                                                            | _ | — | ns | Must also meet<br>Parameter TC15         |

| TC15               | TtxP      | TxCK Input<br>Period                      | Synchronous, with prescaler | 2 Tcy + 40                                                                                                                                                                                                                                                                          | — | _ | ns | N = prescale<br>value<br>(1, 8, 64, 256) |

| TC20               | TCKEXTMRL | Delay from E<br>Clock Edge t<br>Increment | xternal TxCK<br>o Timer     | 0.75 Tcy + 40 — 1.75 Tcy + 40 ns                                                                                                                                                                                                                                                    |   |   |    |                                          |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

| AC CHA       | RACTER          | ISTICS           |                           | Standard Operatin<br>(unless otherwise<br>Operating tempera | stated)<br>iture -40 | )°C ≤ Ta ≤ | +85°C for Industrial   |  |

|--------------|-----------------|------------------|---------------------------|-------------------------------------------------------------|----------------------|------------|------------------------|--|

| Param<br>No. | Symbol          | Characte         | eristic <sup>(4)</sup>    | Min. <sup>(1)</sup> Max.                                    |                      | Units      | Conditions             |  |

| IM10         | TLO:SCL         | Clock Low Time   | 100 kHz mode              | Tcy/2 (BRG + 2)                                             | _                    | μS         |                        |  |

|              |                 |                  | 400 kHz mode              | TCY/2 (BRG + 2)                                             |                      | μ <b>S</b> |                        |  |

|              |                 |                  | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                             |                      | μs         |                        |  |

| IM11         | THI:SCL         | Clock High Time  | 100 kHz mode              | Tcy/2 (BRG + 2)                                             |                      | μS         |                        |  |

|              |                 |                  | 400 kHz mode              | Tcy/2 (BRG + 2)                                             |                      | μs         |                        |  |

|              |                 |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                             | _                    | μS         |                        |  |

| IM20         | TF:SCL          | SDAx and SCLx    | 100 kHz mode              | _                                                           | 300                  | ns         | CB is specified to be  |  |

|              |                 | Fall Time        | 400 kHz mode              | 20 + 0.1 Св                                                 | 300                  | ns         | from 10 to 400 pF      |  |

|              |                 |                  | 1 MHz mode <sup>(2)</sup> | _                                                           | 100                  | ns         |                        |  |

| IM21         | TR:SCL          | SDAx and SCLx    | 100 kHz mode              | _                                                           | 1000                 | ns         | CB is specified to be  |  |

|              |                 | Rise Time        | 400 kHz mode              | 20 + 0.1 Св                                                 | 300                  | ns         | from 10 to 400 pF      |  |

|              |                 |                  | 1 MHz mode <sup>(2)</sup> |                                                             | 300                  | ns         |                        |  |

| IM25         | TSU:DAT         | Data Input       | 100 kHz mode              | 250                                                         |                      | ns         |                        |  |

|              |                 | Setup Time       | 400 kHz mode              | 100                                                         |                      | ns         |                        |  |