Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                    |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 44-VTLA (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc504-e-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

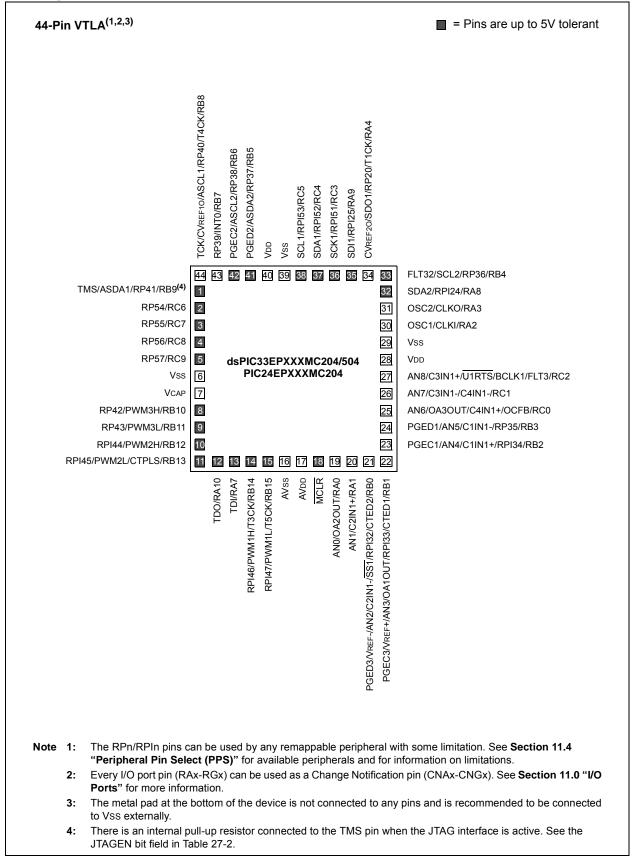

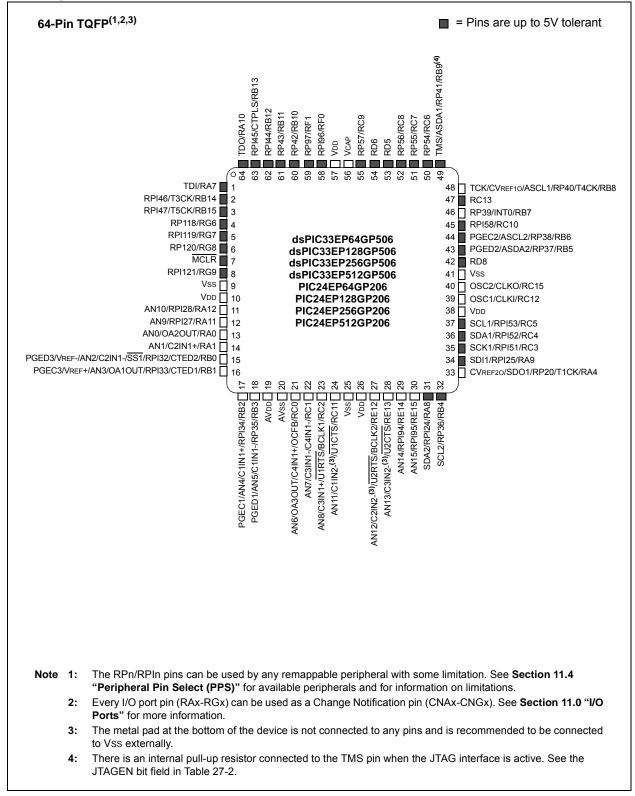

### Pin Diagrams (Continued)

### **Pin Diagrams (Continued)**

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

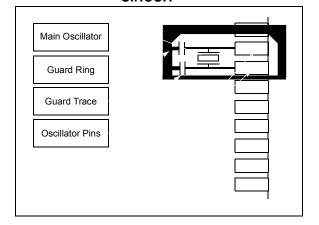

### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator. For details, see **Section 9.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

| TABLE 4   | 4-9:  | INPUT  |        | JRE 1 T | HROUG  | H INPU    | Т САРТ | URE 4 | REGIST       | ER MA        | Р        |       |       |       |          |          |       |               |

|-----------|-------|--------|--------|---------|--------|-----------|--------|-------|--------------|--------------|----------|-------|-------|-------|----------|----------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8        | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2    | Bit 1    | Bit 0 | All<br>Resets |

| IC1CON1   | 0140  | _      | —      | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | -            | _            | ICI<     | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC1CON2   | 0142  | _      | _      |         | _      |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC1BUF    | 0144  |        |        |         |        |           |        | Inp   | ut Capture ' | 1 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC1TMR    | 0146  |        |        |         |        |           |        |       | Input Capt   | ture 1 Time  | r        |       |       |       |          |          |       | 0000          |

| IC2CON1   | 0148  |        | _      | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC2CON2   | 014A  |        | _      |         |        |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC2BUF    | 014C  |        |        |         |        |           |        | Inp   | ut Capture 2 | 2 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC2TMR    | 014E  |        |        |         |        |           |        |       | Input Capt   | ture 2 Time  | r        |       |       |       |          |          |       | 0000          |

| IC3CON1   | 0150  |        | _      | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC3CON2   | 0152  |        | _      |         |        |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC3BUF    | 0154  |        |        |         |        |           |        | Inp   | ut Capture 3 | 3 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC3TMR    | 0156  |        |        |         |        |           |        |       | Input Capt   | ture 3 Time  | r        |       |       |       |          |          |       | 0000          |

| IC4CON1   | 0158  |        | _      | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC4CON2   | 015A  | _      | _      |         | _      |           | -      | _     | IC32         | ICTRIG       | TRIGSTAT | -     |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC4BUF    | 015C  |        |        |         |        |           |        | Inp   | ut Capture 4 | 4 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC4TMR    | 015E  |        |        |         |        |           |        |       | Input Capt   | ure 4 Time   | r        |       |       |       |          |          |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4         | -16:  | QEI1   | REGR               |          | P FOR d    | SPIC33E    | PXXXMO   | 20X/50)  | ( AND PI    | C24EP) |        | 20X DE     | VICES O  | NLY    | 1      |        |        | r             |

|-----------------|-------|--------|--------------------|----------|------------|------------|----------|----------|-------------|--------|--------|------------|----------|--------|--------|--------|--------|---------------|

| File Name       | Addr. | Bit 15 | Bit 14             | Bit 13   | Bit 12     | Bit 11     | Bit 10   | Bit 9    | Bit 8       | Bit 7  | Bit 6  | Bit 5      | Bit 4    | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| QEI1CON         | 01C0  | QEIEN  | —                  | QEISIDL  |            | PIMOD<2:0> |          | IMV      | <1:0>       | -      |        | INTDIV<2:0 | >        | CNTPOL | GATEN  | CCM    | <1:0>  | 0000          |

| QEI1IOC         | 01C2  | QCAPEN | FLTREN             |          | QFDIV<2:0> |            | OUTFN    | NC<1:0>  | SWPAB       | HOMPOL | IDXPOL | QEBPOL     | QEAPOL   | HOME   | INDEX  | QEB    | QEA    | 000x          |

| <b>QEI1STAT</b> | 01C4  | _      | _                  | PCHEQIRQ | PCHEQIEN   | PCLEQIRQ   | PCLEQIEN | POSOVIRQ | POSOVIEN    | PCIIRQ | PCIIEN | VELOVIRQ   | VELOVIEN | HOMIRQ | HOMIEN | IDXIRQ | IDXIEN | 0000          |

| POS1CNTL        | 01C6  |        |                    |          |            |            |          |          | POSCNT<15   | :0>    |        |            |          |        |        |        |        | 0000          |

| POS1CNTH        | 01C8  |        | POSCNT<31:16> 0001 |          |            |            |          |          |             | 0000   |        |            |          |        |        |        |        |               |

| POS1HLD         | 01CA  |        |                    |          |            |            |          |          | POSHLD<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| VEL1CNT         | 01CC  |        |                    |          |            |            |          |          | VELCNT<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| INT1TMRL        | 01CE  |        |                    |          |            |            |          |          | INTTMR<15:  | 0>     |        |            |          |        |        |        |        | 0000          |

| INT1TMRH        | 01D0  |        |                    |          |            |            |          |          | INTTMR<31:  | 6>     |        |            |          |        |        |        |        | 0000          |

| INT1HLDL        | 01D2  |        |                    |          |            |            |          |          | INTHLD<15:  | )>     |        |            |          |        |        |        |        | 0000          |

| INT1HLDH        | 01D4  |        |                    |          |            |            |          |          | INTHLD<31:1 | 6>     |        |            |          |        |        |        |        | 0000          |

| INDX1CNTL       | 01D6  |        |                    |          |            |            |          |          | INDXCNT<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| INDX1CNTH       | 01D8  |        |                    |          |            |            |          |          | NDXCNT<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| INDX1HLD        | 01DA  |        |                    |          |            |            |          |          | INDXHLD<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| QEI1GECL        | 01DC  |        |                    |          |            |            |          |          | QEIGEC<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| <b>QEI1ICL</b>  | 01DC  |        |                    |          |            |            |          |          | QEIIC<15:0  | >      |        |            |          |        |        |        |        | 0000          |

| QEI1GECH        | 01DE  |        |                    |          |            |            |          |          | QEIGEC<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| QEI1ICH         | 01DE  |        | QEIIC<31:16> 000   |          |            |            |          |          |             | 0000   |        |            |          |        |        |        |        |               |

| QEI1LECL        | 01E0  |        | QEILEC<15:0> 0000  |          |            |            |          |          |             | 0000   |        |            |          |        |        |        |        |               |

| <b>QEI1LECH</b> | 01E2  |        |                    |          |            |            |          |          | QEILEC<31:1 | 6>     |        |            |          |        |        |        |        | 0000          |

TABLE 4-16: QEI1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### REGISTER 8-9: DSADRH: DMA MOST RECENT RAM HIGH ADDRESS REGISTER

| U-0            | U-0 | U-0             | U-0   | U-0          | U-0              | U-0    | U-0   |

|----------------|-----|-----------------|-------|--------------|------------------|--------|-------|

| —              | —   | —               | —     | —            | —                | -      | —     |

| bit 15         |     |                 |       |              |                  |        | bit 8 |

|                |     |                 |       |              |                  |        |       |

| R-0            | R-0 | R-0             | R-0   | R-0          | R-0              | R-0    | R-0   |

|                |     |                 | DSADR | <23:16>      |                  |        |       |

| bit 7          |     |                 |       |              |                  |        | bit 0 |

|                |     |                 |       |              |                  |        |       |

| Legend:        |     |                 |       |              |                  |        |       |

| R = Readable b | it  | W = Writable bi | t     | U = Unimpler | nented bit, read | as '0' |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

|-------------------|------------------|------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

#### bit 15-8 Unimplemented: Read as '0'

bit 7-0 DSADR<23:16>: Most Recent DMA Address Accessed by DMA bits

#### REGISTER 8-10: DSADRL: DMA MOST RECENT RAM LOW ADDRESS REGISTER

| R-0              | R-0 | R-0              | R-0  | R-0                  | R-0         | R-0             | R-0   |

|------------------|-----|------------------|------|----------------------|-------------|-----------------|-------|

|                  |     |                  | DSAD | DR<15:8>             |             |                 |       |

| bit 15           |     |                  |      |                      |             |                 | bit 8 |

|                  |     |                  |      |                      |             |                 |       |

| R-0              | R-0 | R-0              | R-0  | R-0                  | R-0         | R-0             | R-0   |

|                  |     |                  | DSA  | DR<7:0>              |             |                 |       |

| bit 7            |     |                  |      |                      |             |                 | bit 0 |

|                  |     |                  |      |                      |             |                 |       |

| Legend:          |     |                  |      |                      |             |                 |       |

| R = Readable b   | it  | W = Writable bit |      | U = Unimplemen       | ted bit, re | ad as '0'       |       |

| -n = Value at PC | OR  | '1' = Bit is set |      | '0' = Bit is cleared | d           | x = Bit is unkn | own   |

bit 15-0 DSADR<15:0>: Most Recent DMA Address Accessed by DMA bits

NOTES:

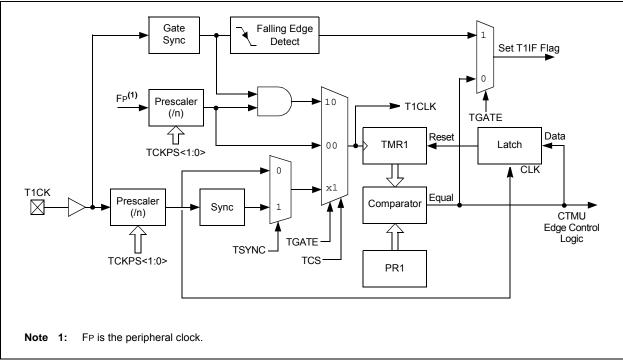

### 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer that can operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated in Asynchronous Counter mode from an external clock source

- The external clock input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler

- A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FCY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit setting for different operating modes are given in the Table 12-1.

| Mode                    | TCS | TGATE | TSYNC |

|-------------------------|-----|-------|-------|

| Timer                   | 0   | 0     | х     |

| Gated Timer             | 0   | 1     | x     |

| Synchronous<br>Counter  | 1   | х     | 1     |

| Asynchronous<br>Counter | 1   | x     | 0     |

#### TABLE 12-1: TIMER MODE SETTINGS

### FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

### REGISTER 17-7: VEL1CNT: VELOCITY COUNTER 1 REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | VELC  | NT<15:8>          |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | VELC  | NT<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable I  | bit   | W = Writable b   | oit   | U = Unimplen      | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 VELCNT<15:0>: Velocity Counter bits

### REGISTER 17-8: INDX1CNTH: INDEX COUNTER 1 HIGH WORD REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0               | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|---------------------|----------|-------|-------|-------|

|        |       |       | INDXCN <sup>®</sup> | T<31:24> |       |       |       |

| bit 15 |       |       |                     |          |       |       | bit 8 |

|        |       |       |                     |          |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0               | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | INDXCN              | T<23:16> |       |       |       |

| bit 7  |       |       |                     |          |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 INDXCNT<31:16>: High Word Used to Form 32-Bit Index Counter Register (INDX1CNT) bits

#### REGISTER 17-9: INDX1CNTL: INDEX COUNTER 1 LOW WORD REGISTER

'1' = Bit is set

| <b>Legend:</b><br>R = Readable b | it    | W = Writable bit |        | U = Unimplen | nented bit, reac | l as '0' |       |

|----------------------------------|-------|------------------|--------|--------------|------------------|----------|-------|

| bit 7                            |       |                  |        |              |                  |          | bit 0 |

|                                  |       |                  | INDXC  | NT<7:0>      |                  |          |       |

| R/W-0                            | R/W-0 | R/W-0            | R/W-0  | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

| bit 15                           |       |                  |        |              |                  |          | bit 8 |

|                                  |       |                  | INDXCN | NT<15:8>     |                  |          |       |

| R/W-0                            | R/W-0 | R/W-0            | R/W-0  | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

'0' = Bit is cleared

bit 15-0 INDXCNT<15:0>: Low Word Used to Form 32-Bit Index Counter Register (INDX1CNT) bits

-n = Value at POR

x = Bit is unknown

# **19.2** I<sup>2</sup>C Control Registers

#### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER

| R/W-0        | U-0                          | R/W-0                                  | R/W-1, HC                  | R/W-0                        | R/W-0            | R/W-0           | R/W-0          |

|--------------|------------------------------|----------------------------------------|----------------------------|------------------------------|------------------|-----------------|----------------|

| I2CEN        | _                            | I2CSIDL                                | SCLREL                     | IPMIEN <sup>(1)</sup>        | A10M             | DISSLW          | SMEN           |

| bit 15       |                              |                                        |                            |                              |                  |                 | bit 8          |

|              |                              |                                        |                            |                              |                  |                 |                |

| R/W-0        | R/W-0                        | R/W-0                                  | R/W-0, HC                  | R/W-0, HC                    | R/W-0, HC        | R/W-0, HC       | R/W-0, HC      |

| GCEN         | STREN                        | ACKDT                                  | ACKEN                      | RCEN                         | PEN              | RSEN            | SEN            |

| bit 7        |                              |                                        |                            |                              |                  |                 | bit 0          |

| Legend:      |                              | HC = Hardware                          | Cloarable bit              |                              |                  |                 |                |

| R = Readab   | le hit                       | W = Writable bi                        |                            | II = I Inimpler              | mented bit, rea  | d as '0'        |                |

| -n = Value a |                              | '1' = Bit is set                       | L .                        | '0' = Bit is cle             |                  | x = Bit is unk  | nown           |

|              |                              |                                        |                            |                              |                  |                 | nown           |

| bit 15       | <b>12CEN:</b> 12Cx           | Enable bit                             |                            |                              |                  |                 |                |

|              |                              | he I2Cx module                         |                            |                              |                  |                 | ;              |

|              | 0 = Disables                 | the I2Cx module;                       | all l <sup>2</sup> C™ pins | are controlled               | by port functior | ıs              |                |

| bit 14       | Unimplemen                   | ted: Read as '0'                       |                            |                              |                  |                 |                |

| bit 13       |                              | x Stop in Idle Mo                      |                            |                              |                  |                 |                |

|              |                              | ues module oper<br>s module operation  |                            |                              | dle mode         |                 |                |

| bit 12       |                              | Lx Release Conf                        |                            | _                            | ( clave)         |                 |                |

|              | 1 = Releases                 |                                        |                            |                              | slave)           |                 |                |

|              |                              | Lx clock low (clo                      | ck stretch)                |                              |                  |                 |                |

|              | If STREN = 1                 | <u>:</u>                               | -                          |                              |                  |                 |                |

|              | •                            | ., software can w                      |                            |                              |                  | ,               |                |

|              |                              | ing of every slav<br>reception. Hardw  |                            |                              |                  |                 | t every slave  |

|              | If STREN = 0                 | -                                      |                            |                              |                  |                 |                |

|              |                              | <u>.</u><br>, software can or          | nly write '1' to re        | elease clock). I             | Hardware is cle  | ar at the begir | ning of every  |

|              | -                            | te transmission.                       |                            |                              | -                | address byte re | eception.      |

| bit 11       |                              | ligent Peripheral                      |                            |                              |                  |                 |                |

|              | 1 = IPMI mod<br>0 = IPMI mod | e is enabled; all                      | addresses are              | Acknowledged                 | 1                |                 |                |

| bit 10       |                              | Slave Address b                        | i+                         |                              |                  |                 |                |

|              |                              | is a 10-bit slave                      |                            |                              |                  |                 |                |

|              |                              | is a 7-bit slave a                     |                            |                              |                  |                 |                |

| bit 9        | DISSLW: Dis                  | able Slew Rate C                       | Control bit                |                              |                  |                 |                |

|              |                              | control is disable                     |                            |                              |                  |                 |                |

|              |                              | control is enable                      |                            |                              |                  |                 |                |

| bit 8        |                              | us Input Levels b                      |                            | 0145                         | <b>c</b>         |                 |                |

|              |                              | /O pin thresholds<br>SMBus input thre  |                            | n SMBus speci                | fication         |                 |                |

| bit 7        |                              | ral Call Enable b                      |                            | ing as I <sup>2</sup> C slav | /e)              |                 |                |

|              | 1 = Enables in               | terrupt when a ge<br>all address disat | neral call addre           | -                            |                  | dule is enabled | for reception) |

|              |                              |                                        |                            |                              |                  |                 |                |

Note 1: When performing master operations, ensure that the IPMIEN bit is set to '0'.

| U-0                          | U-0                                  | U-0                                                                                            | U-0            | U-0          | U-0              | U-0             | U-0   |  |  |  |  |

|------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------|----------------|--------------|------------------|-----------------|-------|--|--|--|--|

| _                            | —                                    | —                                                                                              |                | —            | —                | —               | _     |  |  |  |  |

| bit 15                       |                                      |                                                                                                |                |              |                  |                 | bit   |  |  |  |  |

|                              |                                      |                                                                                                |                |              |                  |                 |       |  |  |  |  |

| R/W-0                        | R/W-0                                | R/W-0                                                                                          | U-0            | R/W-0        | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

| IVRIE                        | WAKIE                                | ERRIE                                                                                          | —              | FIFOIE       | RBOVIE           | RBIE            | TBIE  |  |  |  |  |

| bit 7                        |                                      |                                                                                                |                |              |                  |                 | bit   |  |  |  |  |

|                              |                                      |                                                                                                |                |              |                  |                 |       |  |  |  |  |

| <b>Legend:</b><br>R = Readab | la hit                               | W = Writable b                                                                                 | .it            |              | montod bit rook  | l oo 'O'        |       |  |  |  |  |

| n = Value a                  |                                      | '1' = Bit is set                                                                               | אנ             | 0 = Onimpler | mented bit, read | x = Bit is unkr |       |  |  |  |  |

|                              | IL POR                               | I = DILIS SEL                                                                                  |                |              | areu             |                 | IOWI  |  |  |  |  |

| bit 15-8                     | Unimplemen                           | ted: Read as '0                                                                                | ,              |              |                  |                 |       |  |  |  |  |

| bit 7                        | -                                    | Message Inter                                                                                  |                | bit          |                  |                 |       |  |  |  |  |

|                              |                                      | request is enabl                                                                               | •              | ~            |                  |                 |       |  |  |  |  |

|                              |                                      | request is not er                                                                              |                |              |                  |                 |       |  |  |  |  |

| bit 6                        | WAKIE: Bus                           | Wake-up Activit                                                                                | y Interrupt E  | nable bit    |                  |                 |       |  |  |  |  |

|                              |                                      | equest is enabl                                                                                |                |              |                  |                 |       |  |  |  |  |

|                              |                                      | request is not er                                                                              |                |              |                  |                 |       |  |  |  |  |

| bit 5                        |                                      | Interrupt Enabl                                                                                |                |              |                  |                 |       |  |  |  |  |

|                              |                                      | request is enabl<br>request is not er                                                          |                |              |                  |                 |       |  |  |  |  |

| bit 4                        |                                      | ted: Read as '0                                                                                |                |              |                  |                 |       |  |  |  |  |

| bit 3                        | -                                    | Almost Full Int                                                                                |                | o hit        |                  |                 |       |  |  |  |  |

| DIL J                        |                                      |                                                                                                | •              | ebit         |                  |                 |       |  |  |  |  |

|                              |                                      | <ol> <li>I = Interrupt request is enabled</li> <li>Interrupt request is not enabled</li> </ol> |                |              |                  |                 |       |  |  |  |  |

| bit 2                        | <b>RBOVIE:</b> RX                    | Buffer Overflow                                                                                | / Interrupt Er | nable bit    |                  |                 |       |  |  |  |  |

|                              | 1 = Interrupt                        | 1 = Interrupt request is enabled                                                               |                |              |                  |                 |       |  |  |  |  |

|                              | 0 = Interrupt i                      | 0 = Interrupt request is not enabled                                                           |                |              |                  |                 |       |  |  |  |  |

| bit 1                        | RBIE: RX Buffer Interrupt Enable bit |                                                                                                |                |              |                  |                 |       |  |  |  |  |

|                              |                                      | equest is enabl                                                                                |                |              |                  |                 |       |  |  |  |  |

|                              |                                      | request is not er                                                                              | nabled         |              |                  |                 |       |  |  |  |  |

|                              | •                                    | •                                                                                              |                |              |                  |                 |       |  |  |  |  |

| bit 0                        | TBIE: TX Buf                         | fer Interrupt Ena<br>request is enabl                                                          | able bit       |              |                  |                 |       |  |  |  |  |

### REGISTER 21-7: CXINTE: ECANX INTERRUPT ENABLE REGISTER

| REGISTER 21-26: | CxTRmnCON: ECANx TX/RX BUFFER mn CONTROL REGISTER |

|-----------------|---------------------------------------------------|

|                 | (m = 0,2,4,6; n = 1,3,5,7)                        |

|               | (                                                                                                                                                       | ,_, ., ., ., .,                   | -,-,-,                |                          |                  |                 |                 |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------|--------------------------|------------------|-----------------|-----------------|

| R/W-0         | R-0                                                                                                                                                     | R-0                               | R-0                   | R/W-0                    | R/W-0            | R/W-0           | R/W-0           |

| TXENn         | TXABTn                                                                                                                                                  | TXLARBn                           | TXERRn                | TXREQn                   | RTRENn           | TXnPRI1         | TXnPRI0         |

| bit 15        |                                                                                                                                                         |                                   |                       |                          |                  |                 | bit 8           |

| R/W-0         | R-0                                                                                                                                                     | R-0                               | R-0                   | R/W-0                    | R/W-0            | R/W-0           | R/W-0           |

| TXENm         | TXABTm <sup>(1)</sup>                                                                                                                                   | TXLARBm <sup>(1)</sup>            | TXERRm <sup>(1)</sup> | TXREQm                   | RTRENm           | TXmPRI1         | TXmPRI0         |

| bit 7         |                                                                                                                                                         |                                   |                       |                          |                  |                 | bit C           |

| Legend:       |                                                                                                                                                         |                                   |                       |                          |                  |                 |                 |

| R = Readabl   | le bit                                                                                                                                                  | W = Writable                      | bit                   | U = Unimpler             | mented bit, read | d as '0'        |                 |

| -n = Value at | t POR                                                                                                                                                   | '1' = Bit is set                  |                       | '0' = Bit is cle         | ared             | x = Bit is unki | nown            |

| bit 15-8      | See Definitio                                                                                                                                           | n for bits<7:0>,                  | Controls Buffe        | <u>er n</u>              |                  |                 |                 |

| bit 7         |                                                                                                                                                         | RX Buffer Sele                    |                       |                          |                  |                 |                 |

|               |                                                                                                                                                         | RBn is a transm                   |                       |                          |                  |                 |                 |

|               | 0 = Buffer TR                                                                                                                                           | RBn is a receive                  | buffer                |                          |                  |                 |                 |

| bit 6         | TXABTm: Me                                                                                                                                              | essage Aborted                    | d bit <sup>(1)</sup>  |                          |                  |                 |                 |

|               | 1 = Message                                                                                                                                             |                                   |                       |                          |                  |                 |                 |

|               |                                                                                                                                                         | completed tran                    |                       |                          |                  |                 |                 |

| bit 5         |                                                                                                                                                         | Message Lost A                    |                       |                          |                  |                 |                 |

|               |                                                                                                                                                         | lost arbitration did not lose ar  |                       |                          |                  |                 |                 |

| bit 4         | TXERRm: Er                                                                                                                                              | ror Detected D                    | uring Transmis        | ssion bit <sup>(1)</sup> |                  |                 |                 |

|               |                                                                                                                                                         | or occurred wh<br>or did not occu |                       |                          |                  |                 |                 |

| bit 3         |                                                                                                                                                         | essage Send F                     |                       |                          |                  |                 |                 |

|               |                                                                                                                                                         | 0                                 | •                     | bit automatic            | ally clears wher | n the message   | is successfully |

|               | 0 = Clearing                                                                                                                                            | the bit to '0' wh                 | nile set reques       | ts a message             | abort            |                 |                 |

| bit 2         | RTRENm: Au                                                                                                                                              | uto-Remote Tra                    | Insmit Enable         | bit                      |                  |                 |                 |

|               | <ul> <li>1 = When a remote transmit is received, TXREQ will be set</li> <li>0 = When a remote transmit is received, TXREQ will be unaffected</li> </ul> |                                   |                       |                          |                  |                 |                 |

| bit 1-0       | TXmPRI<1:0                                                                                                                                              | >: Message Tra                    | ansmission Pri        | iority bits              |                  |                 |                 |

|               | 11 = Highest                                                                                                                                            | message prior                     | ity                   |                          |                  |                 |                 |

|               | 0                                                                                                                                                       | ermediate mes                     |                       |                          |                  |                 |                 |

|               |                                                                                                                                                         | ermediate mess<br>message priori  |                       |                          |                  |                 |                 |

|               |                                                                                                                                                         |                                   | -                     |                          |                  |                 |                 |

| Note 1: ⊤     | his bit is cleared                                                                                                                                      | when TXREQ                        | s set.                |                          |                  |                 |                 |

Note: The buffers, SID, EID, DLC, Data Field, and Receive Status registers are located in DMA RAM.

| _                                                                                                                                                                                                   |                                                                       |                                |                         |                        |                      |                      |                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------|-------------------------|------------------------|----------------------|----------------------|----------------------|

| R/W-0                                                                                                                                                                                               | U-0                                                                   | U-0                            | R/W-0                   | R/W-0                  | R/W-0                | R/W-0                | R/W-0                |

| ADRC                                                                                                                                                                                                | —                                                                     | —                              | SAMC4 <sup>(1)</sup>    | SAMC3 <sup>(1)</sup>   | SAMC2 <sup>(1)</sup> | SAMC1 <sup>(1)</sup> | SAMC0 <sup>(1)</sup> |

| bit 15                                                                                                                                                                                              |                                                                       |                                |                         |                        |                      |                      | bit 8                |

|                                                                                                                                                                                                     |                                                                       |                                |                         |                        |                      |                      |                      |

| R/W-0                                                                                                                                                                                               | R/W-0                                                                 | R/W-0                          | R/W-0                   | R/W-0                  | R/W-0                | R/W-0                | R/W-0                |

| ADCS7 <sup>(2)</sup>                                                                                                                                                                                | ADCS6 <sup>(2)</sup>                                                  | ADCS5 <sup>(2)</sup>           | ADCS4 <sup>(2)</sup>    | ADCS3 <sup>(2)</sup>   | ADCS2 <sup>(2)</sup> | ADCS1 <sup>(2)</sup> | ADCS0 <sup>(2)</sup> |

| bit 7                                                                                                                                                                                               |                                                                       |                                |                         |                        |                      |                      | bit 0                |

| r                                                                                                                                                                                                   |                                                                       |                                |                         |                        |                      |                      |                      |

| Legend:                                                                                                                                                                                             |                                                                       |                                |                         |                        |                      |                      |                      |

| R = Readable b                                                                                                                                                                                      |                                                                       | W = Writable k                 | bit                     | •                      | nented bit, read     | l as '0'             |                      |

| -n = Value at P                                                                                                                                                                                     | OR                                                                    | '1' = Bit is set               |                         | '0' = Bit is clea      | ared                 | x = Bit is unkr      | nown                 |

| bit 15                                                                                                                                                                                              | 5 ADRC: ADC1 Conversion Clock Source bit<br>1 = ADC internal RC clock |                                |                         |                        |                      |                      |                      |

|                                                                                                                                                                                                     |                                                                       | ved from syste                 |                         |                        |                      |                      |                      |

| bit 14-13                                                                                                                                                                                           | •                                                                     | ted: Read as '0                |                         |                        |                      |                      |                      |

| bit 12-8                                                                                                                                                                                            |                                                                       | Auto-Sample T                  | ime bits <sup>(1)</sup> |                        |                      |                      |                      |

|                                                                                                                                                                                                     | 11111 = <b>31</b> T                                                   | AD                             |                         |                        |                      |                      |                      |

|                                                                                                                                                                                                     | •                                                                     |                                |                         |                        |                      |                      |                      |

|                                                                                                                                                                                                     | •                                                                     |                                |                         |                        |                      |                      |                      |

|                                                                                                                                                                                                     | 00001 = 1 TA<br>00000 = 0 TA                                          |                                |                         |                        |                      |                      |                      |

| bit 7-0                                                                                                                                                                                             | ADCS<7:0>:                                                            | ADC1 Convers                   | ion Clock Sele          | ct bits <sup>(2)</sup> |                      |                      |                      |

|                                                                                                                                                                                                     | 11111111 = <sup>-</sup><br>•                                          | TP • (ADCS<7:                  | 0> + 1) = TP •          | 256 = Tad              |                      |                      |                      |

|                                                                                                                                                                                                     | •                                                                     |                                |                         |                        |                      |                      |                      |

|                                                                                                                                                                                                     | 00000010 = -                                                          | TP • (ADCS<7:                  | 0> + 1) = TP •          | 3 = TAD                |                      |                      |                      |

|                                                                                                                                                                                                     | 0000001 =                                                             | TP • (ADCS<7:<br>TP • (ADCS<7: | 0> + 1) = TP •          | 2 <b>=</b> Tad         |                      |                      |                      |

| <ul> <li>Note 1: This bit is only used if SSRC&lt;2:0&gt; (AD1CON1&lt;7:5&gt;) = 111 and SSRCG (AD1CON1&lt;4&gt;) = 0.</li> <li>2: This bit is not used if ADRC (AD1CON3&lt;15&gt;) = 1.</li> </ul> |                                                                       |                                |                         |                        |                      |                      |                      |

### REGISTER 23-3: AD1CON3: ADC1 CONTROL REGISTER 3

### REGISTER 27-1: DEVID: DEVICE ID REGISTER

|        | R = Read-Only bit |   |         | U = Unimplem          |   |   |        |

|--------|-------------------|---|---------|-----------------------|---|---|--------|

|        |                   |   |         |                       |   |   |        |

| bit 7  |                   |   |         |                       |   |   | bit 0  |

|        |                   |   | DEVID   | <7:0> <sup>(1)</sup>  |   |   |        |

| R      | R                 | R | R       | R                     | R | R | R      |

| bit 15 |                   |   |         |                       |   |   | bit 8  |

|        |                   |   | DEVID<  | :15:8> <sup>(1)</sup> |   |   |        |

| R      | R                 | R | R       | R                     | R | R | R      |

| bit 23 |                   |   |         |                       |   |   | bit 16 |

|        |                   |   | DEVID<2 | 23:16>(1)             |   |   |        |

| R      | R                 | R | R       | R                     | R | R | R      |

bit 23-0 **DEVID<23:0>:** Device Identifier bits<sup>(1)</sup>

**Note 1:** Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration *Bits*" (DS70663) for the list of device ID values.

### **REGISTER 27-2: DEVREV: DEVICE REVISION REGISTER**

| R           | R             | R | R      | R                      | R          | R | R      |

|-------------|---------------|---|--------|------------------------|------------|---|--------|

|             |               |   | DEVREV | <23:16> <sup>(1)</sup> |            |   |        |

| bit 23      |               |   |        |                        |            |   | bit 16 |

|             |               |   |        |                        |            |   |        |

| R           | R             | R | R      | R                      | R          | R | R      |

|             |               |   | DEVREV | <15:8>(1)              |            |   |        |

| bit 15      |               |   |        |                        |            |   | bit 8  |

| R           | R             | R | R      | R                      | R          | R | R      |

|             |               |   | DEVRE\ | /<7:0> <sup>(1)</sup>  |            |   |        |

| bit 7       |               |   |        |                        |            |   | bit 0  |

|             |               |   |        |                        |            |   |        |

| Legend: R = | Read-only bit |   |        | U = Unimplem           | nented bit |   |        |

### bit 23-0 **DEVREV<23:0>:** Device Revision bits<sup>(1)</sup>

**Note 1:** Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration *Bits*" (DS70663) for the list of device revision values.

### 27.6 JTAG Interface

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement a JTAG interface, which supports boundary scan device testing. Detailed information on this interface is provided in future revisions of the document.

| Note: | Refer to "Programming and Diagnostics"       |

|-------|----------------------------------------------|

|       | (DS70608) in the "dsPIC33/PIC24 Family       |

|       | Reference Manual" for further information    |

|       | on usage, configuration and operation of the |

|       | JTAG interface.                              |

### 27.7 In-Circuit Serial Programming

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices can be serially programmed while in the end application circuit. This is done with two lines for clock and data, and three other lines for power, ground and the programming sequence. Serial programming allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. Serial programming also allows the most recent firmware or a custom firmware to be programmed. Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration Bits" (DS70663) for details about In-Circuit Serial Programming (ICSP).

Any of the three pairs of programming clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

### 27.8 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3 or REAL ICE<sup>™</sup> is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx (Emulation/Debug Clock) and PGEDx (Emulation/Debug Data) pin functions.

Any of the three pairs of debugging clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

To use the in-circuit debugger function of the device, the design must implement ICSP connections to  $\overline{MCLR}$ , VDD, Vss and the PGECx/PGEDx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins (PGECx and PGEDx).

### 27.9 Code Protection and CodeGuard™ Security

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X, and PIC24EPXXXGP/MC20X devices offer basic implementation of CodeGuard Security that supports only General Segment (GS) security. This feature helps protect individual Intellectual Property.

Note: Refer to "CodeGuard<sup>™</sup> Security" (DS70634) in the "dsPIC33/PIC24 Family Reference Manual" for further information on usage, configuration and operation of CodeGuard Security.

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax                                  | Description                               | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|--------|--------------------------------------------------|-------------------------------------------|---------------|-------------------------------|--------------------------|

| 46                 | MOV                  | MOV    | f,Wn                                             | Move f to Wn                              | 1             | 1                             | None                     |

|                    |                      | MOV    | f                                                | Move f to f                               | 1             | 1                             | None                     |

|                    |                      | MOV    | f,WREG                                           | Move f to WREG                            | 1             | 1                             | None                     |

|                    |                      | MOV    | #litl6,Wn                                        | Move 16-bit literal to Wn                 | 1             | 1                             | None                     |

|                    |                      | MOV.b  | #lit8,Wn                                         | Move 8-bit literal to Wn                  | 1             | 1                             | None                     |

|                    |                      | MOV    | Wn,f                                             | Move Wn to f                              | 1             | 1                             | None                     |

|                    |                      | MOV    | Wso,Wdo                                          | Move Ws to Wd                             | 1             | 1                             | None                     |

|                    |                      | MOV    | WREG, f                                          | Move WREG to f                            | 1             | 1                             | None                     |

|                    |                      | MOV.D  | Wns,Wd                                           | Move Double from W(ns):W(ns + 1) to<br>Wd | 1             | 2                             | None                     |

|                    |                      | MOV.D  | Ws , Wnd                                         | Move Double from Ws to W(nd +<br>1):W(nd) | 1             | 2                             | None                     |

| 47                 | MOVPAG               | MOVPAG | #lit10,DSRPAG                                    | Move 10-bit literal to DSRPAG             | 1             | 1                             | None                     |

|                    |                      | MOVPAG | #lit9,DSWPAG                                     | Move 9-bit literal to DSWPAG              | 1             | 1                             | None                     |

|                    |                      | MOVPAG | #lit8,TBLPAG                                     | Move 8-bit literal to TBLPAG              | 1             | 1                             | None                     |

|                    |                      | MOVPAG | Ws, DSRPAG                                       | Move Ws<9:0> to DSRPAG                    | 1             | 1                             | None                     |

|                    |                      | MOVPAG | Ws, DSWPAG                                       | Move Ws<8:0> to DSWPAG                    | 1             | 1                             | None                     |

|                    |                      | MOVPAG | Ws, TBLPAG                                       | Move Ws<7:0> to TBLPAG                    | 1             | 1                             | None                     |

| 48                 | MOVSAC               | MOVSAC | Acc,Wx,Wxd,Wy,Wyd,AWB <sup>(1)</sup>             | Prefetch and store accumulator            | 1             | 1                             | None                     |

| 49                 | MPY                  | MPY    | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd <sup>(1)</sup>           | Multiply Wm by Wn to Accumulator          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MPY    | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd <sup>(1)</sup>           | Square Wm to Accumulator                  | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 50                 | MPY.N                | MPY.N  | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd(1)                       | -(Multiply Wm by Wn) to Accumulator       | 1             | 1                             | None                     |

| 51                 | MSC                  | MSC    | Wm*Wm, Acc, Wx, Wxd, Wy, Wyd, AWB <sup>(1)</sup> | Multiply and Subtract from Accumulator    | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

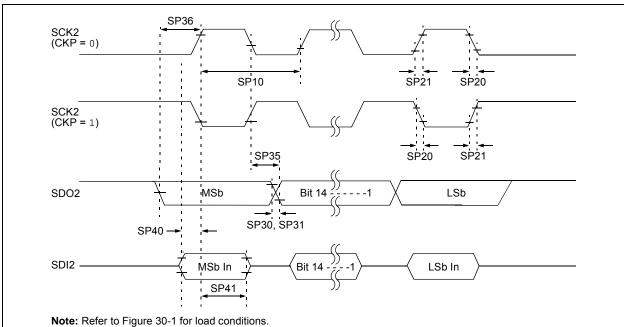

### FIGURE 30-16: SPI2 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 30-35:SPI2 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1)TIMING REQUIREMENTS

| АС СНА | AC CHARACTERISTICS    |                                               |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |                                |  |  |

|--------|-----------------------|-----------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------|--|--|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                 | Min. | Typ. <sup>(2)</sup>                                                                                                                                                                                                                                                                     | Max. | Units | Conditions                     |  |  |

| SP10   | FscP                  | Maximum SCK2 Frequency                        | _    | —                                                                                                                                                                                                                                                                                       | 9    | MHz   | (Note 3)                       |  |  |

| SP20   | TscF                  | SCK2 Output Fall Time                         | —    | —                                                                                                                                                                                                                                                                                       |      | ns    | See Parameter DO32 (Note 4)    |  |  |

| SP21   | TscR                  | SCK2 Output Rise Time                         | —    | —                                                                                                                                                                                                                                                                                       | —    | ns    | See Parameter DO31 (Note 4)    |  |  |