Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                    |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 4K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc504-i-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

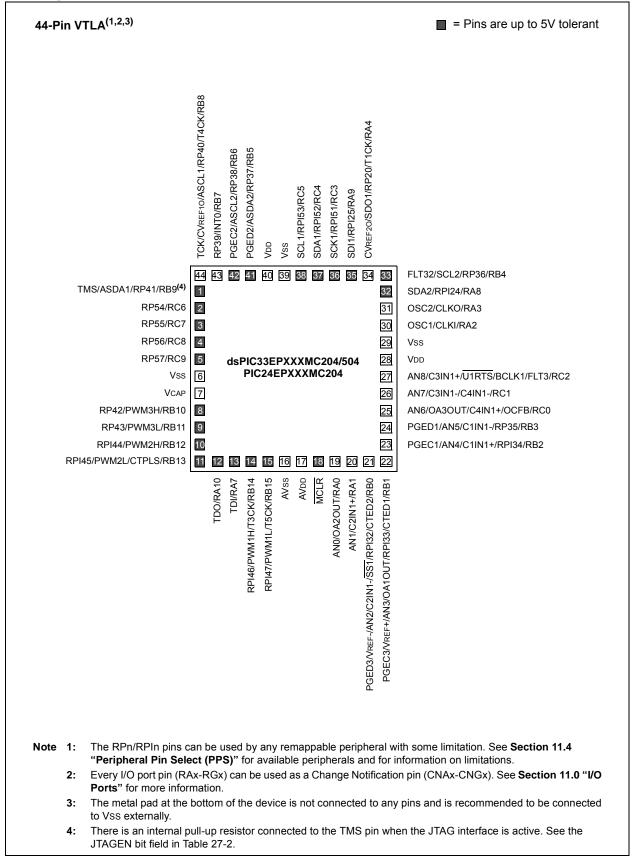

## Pin Diagrams (Continued)

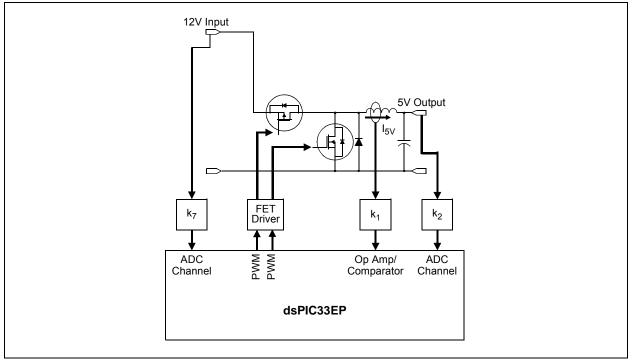

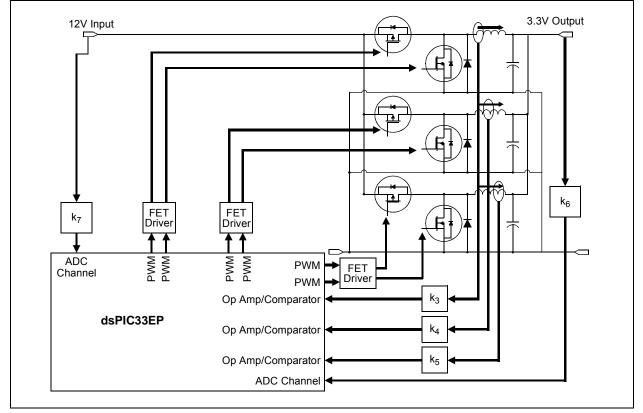

#### FIGURE 2-5: SINGLE-PHASE SYNCHRONOUS BUCK CONVERTER

|             |       |                 |                   |        |        |        |        | •            |              |               |              |       |        |       |       |       |       |               |

|-------------|-------|-----------------|-------------------|--------|--------|--------|--------|--------------|--------------|---------------|--------------|-------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15          | Bit 14            | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8        | Bit 7         | Bit 6        | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1        | 0100  | Timer1 Register |                   |        |        |        |        |              |              |               | xxxx         |       |        |       |       |       |       |               |

| PR1         | 0102  |                 |                   |        |        |        |        |              | Period F     | Register 1    |              |       |        |       |       |       |       | FFFF          |

| T1CON       | 0104  | TON             | _                 | TSIDL  | _      | _      | _      | _            | _            | _             | TGATE        | TCKP  | S<1:0> | —     | TSYNC | TCS   |       | 0000          |

| TMR2        | 0106  |                 |                   |        |        |        |        |              | Timer2       | Register      |              |       |        |       |       |       |       | xxxx          |

| TMR3HLD     | 0108  |                 |                   |        |        |        | Time   | er3 Holding  | Register (fo | r 32-bit time | r operations | only) |        |       |       |       |       | xxxx          |

| TMR3        | 010A  |                 | Timer3 Register   |        |        |        |        |              |              | xxxx          |              |       |        |       |       |       |       |               |

| PR2         | 010C  |                 | Period Register 2 |        |        |        |        |              |              |               | FFFF         |       |        |       |       |       |       |               |

| PR3         | 010E  |                 |                   |        |        |        |        |              | Period F     | Register 3    |              |       |        |       |       |       |       | FFFF          |

| T2CON       | 0110  | TON             | —                 | TSIDL  | —      | —      | —      | _            | —            | —             | TGATE        | TCKP  | S<1:0> | T32   | _     | TCS   |       | 0000          |

| T3CON       | 0112  | TON             | -                 | TSIDL  | _      | _      | _      | _            | _            | _             | TGATE        | TCKP  | S<1:0> | _     | _     | TCS   |       | 0000          |

| TMR4        | 0114  |                 |                   | •      | •      | •      | •      | •            | Timer4       | Register      |              |       |        | •     |       | •     |       | xxxx          |

| TMR5HLD     | 0116  |                 |                   |        |        |        | Т      | imer5 Holdir | ng Register  | (for 32-bit o | perations on | ly)   |        |       |       |       |       | xxxx          |

| TMR5        | 0118  |                 |                   |        |        |        |        |              | Timer5       | Register      |              |       |        |       |       |       |       | xxxx          |

| PR4         | 011A  |                 |                   |        |        |        |        |              | Period F     | Register 4    |              |       |        |       |       |       |       | FFFF          |

| PR5         | 011C  |                 |                   |        |        |        |        |              | Period F     | Register 5    |              |       |        |       |       |       |       | FFFF          |

| T4CON       | 011E  | TON             | —                 | TSIDL  | —      | —      | —      | —            | _            | _             | TGATE        | TCKP  | S<1:0> | T32   | —     | TCS   | —     | 0000          |

| T5CON       | 0120  | TON             | _                 | TSIDL  | _      | _      | _      | _            | _            | _             | TGATE        | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

# TABLE 4-8: TIMER1 THROUGH TIMER5 REGISTER MAP

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# **REGISTER 8-7:** DMAXPAD: DMA CHANNEL X PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0                                                                      | R/W-0        | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |  |  |

|----------------------------------------------------------------------------|--------------|-------|-------|--------|-------|-------|-------|--|--|

|                                                                            |              |       | PAD   | <15:8> |       |       |       |  |  |

| bit 15                                                                     | bit 15 bit 8 |       |       |        |       |       |       |  |  |

|                                                                            |              |       |       |        |       |       |       |  |  |

| R/W-0                                                                      | R/W-0        | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |  |  |

|                                                                            |              |       | PAE   | )<7:0> |       |       |       |  |  |

| bit 7                                                                      |              |       |       |        |       |       | bit 0 |  |  |

|                                                                            |              |       |       |        |       |       |       |  |  |

| Legend:                                                                    |              |       |       |        |       |       |       |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'       |              |       |       |        |       |       |       |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |              |       |       |        | nown  |       |       |  |  |

#### bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

### REGISTER 8-8: DMAXCNT: DMA CHANNEL X TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0                               | U-0   | R/W-0            | R/W-0                    | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |

|-----------------------------------|-------|------------------|--------------------------|-----------------------------------------|-------|-------|-------|--|--|

| —                                 |       |                  | CNT<13:8> <sup>(2)</sup> |                                         |       |       |       |  |  |

| bit 15                            |       |                  |                          |                                         |       |       | bit 8 |  |  |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                    | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |

|                                   |       |                  | CNT<                     | <7:0> <b>(2)</b>                        |       |       |       |  |  |

| bit 7                             |       |                  |                          |                                         |       |       | bit 0 |  |  |

| Legend:                           |       |                  |                          |                                         |       |       |       |  |  |

| R = Readable bit W = Writable bit |       |                  | bit                      | U = Unimplemented bit, read as '0'      |       |       |       |  |  |

| -n = Value at P                   | OR    | '1' = Bit is set |                          | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

**2:** The number of DMA transfers = CNT<13:0> + 1.

# 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.4.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

#### 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs. In comparison, some digital-only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include  $I^2C^{TM}$  and the PWM. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheralselectable pin is handled in two different ways, depending on whether an input or output is being mapped.

| Input Name <sup>(1)</sup>                   | Function Name | Register | Configuration Bits |

|---------------------------------------------|---------------|----------|--------------------|

| External Interrupt 1                        | INT1          | RPINR0   | INT1R<6:0>         |

| External Interrupt 2                        | INT2          | RPINR1   | INT2R<6:0>         |

| Timer2 External Clock                       | T2CK          | RPINR3   | T2CKR<6:0>         |

| Input Capture 1                             | IC1           | RPINR7   | IC1R<6:0>          |

| Input Capture 2                             | IC2           | RPINR7   | IC2R<6:0>          |

| Input Capture 3                             | IC3           | RPINR8   | IC3R<6:0>          |

| Input Capture 4                             | IC4           | RPINR8   | IC4R<6:0>          |

| Output Compare Fault A                      | OCFA          | RPINR11  | OCFAR<6:0>         |

| PWM Fault 1 <sup>(3)</sup>                  | FLT1          | RPINR12  | FLT1R<6:0>         |

| PWM Fault 2 <sup>(3)</sup>                  | FLT2          | RPINR12  | FLT2R<6:0>         |

| QEI1 Phase A <sup>(3)</sup>                 | QEA1          | RPINR14  | QEA1R<6:0>         |

| QEI1 Phase B <sup>(3)</sup>                 | QEB1          | RPINR14  | QEB1R<6:0>         |

| QEI1 Index <sup>(3)</sup>                   | INDX1         | RPINR15  | INDX1R<6:0>        |

| QEI1 Home <sup>(3)</sup>                    | HOME1         | RPINR15  | HOM1R<6:0>         |

| UART1 Receive                               | U1RX          | RPINR18  | U1RXR<6:0>         |

| UART2 Receive                               | U2RX          | RPINR19  | U2RXR<6:0>         |

| SPI2 Data Input                             | SDI2          | RPINR22  | SDI2R<6:0>         |

| SPI2 Clock Input                            | SCK2          | RPINR22  | SCK2R<6:0>         |

| SPI2 Slave Select                           | SS2           | RPINR23  | SS2R<6:0>          |

| CAN1 Receive <sup>(2)</sup>                 | C1RX          | RPINR26  | C1RXR<6:0>         |

| PWM Sync Input 1 <sup>(3)</sup>             | SYNCI1        | RPINR37  | SYNCI1R<6:0>       |

| PWM Dead-Time Compensation 1 <sup>(3)</sup> | DTCMP1        | RPINR38  | DTCMP1R<6:0>       |

| PWM Dead-Time Compensation 2 <sup>(3)</sup> | DTCMP2        | RPINR39  | DTCMP2R<6:0>       |

| PWM Dead-Time Compensation 3 <sup>(3)</sup> | DTCMP3        | RPINR39  | DTCMP3R<6:0>       |

# TABLE 11-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)

**Note 1:** Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

2: This input source is available on dsPIC33EPXXXGP/MC50X devices only.

3: This input source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

# 15.2 Output Compare Control Registers

# REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0           | U-0                          | R/W-0                                  | R/W-0             | R/W-0             | R/W-0            | U-0              | R/W-0  |  |

|---------------|------------------------------|----------------------------------------|-------------------|-------------------|------------------|------------------|--------|--|

|               | 0-0                          | OCSIDL                                 | OCTSEL2           | OCTSEL1           | OCTSEL0          |                  | ENFLTB |  |

| <br>bit 15    |                              | COOIDE                                 |                   | OUTOLLI           | OUTOLLU          |                  | bit 8  |  |

| Sit 10        |                              |                                        |                   |                   |                  |                  | bit 0  |  |

| R/W-0         | U-0                          | R/W-0, HSC                             | R/W-0, HSC        | R/W-0             | R/W-0            | R/W-0            | R/W-0  |  |

| ENFLT         |                              | OCFLTB                                 | OCFLTA            | TRIGMODE          | OCM2             | OCM1             | OCM0   |  |

| bit 7         |                              |                                        |                   |                   |                  |                  | bit 0  |  |

|               |                              |                                        |                   |                   |                  |                  |        |  |

| Legend:       |                              | HSC = Hardw                            | are Settable/Cl   | earable bit       |                  |                  |        |  |

| R = Read      | able bit                     | W = Writable I                         | oit               | U = Unimplem      | nented bit, read | as '0'           |        |  |

| -n = Value    | e at POR                     | '1' = Bit is set                       |                   | '0' = Bit is clea | ared             | x = Bit is unkn  | own    |  |

|               |                              |                                        |                   |                   |                  |                  |        |  |

| bit 15-14     | Unimplemen                   | ted: Read as 'o                        | )'                |                   |                  |                  |        |  |

| bit 13        | OCSIDL: Out                  | tput Compare x                         | Stop in Idle Mo   | de Control bit    |                  |                  |        |  |

|               |                              | ompare x Halts                         |                   |                   |                  |                  |        |  |

|               | •                            | compare x conti                        | •                 |                   | ode              |                  |        |  |

| bit 12-10     |                              | )>: Output Com                         | pare x Clock S    | elect bits        |                  |                  |        |  |

|               | 111 = Periph<br>110 = Reserv | eral clock (FP)                        |                   |                   |                  |                  |        |  |

|               | 101 = PTGO                   |                                        |                   |                   |                  |                  |        |  |

|               |                              | is the clock so                        |                   |                   | hronous clock    | is supported)    |        |  |

|               |                              | is the clock so                        |                   |                   |                  |                  |        |  |

|               |                              | ( is the clock so<br>( is the clock so |                   |                   |                  |                  |        |  |

|               |                              | is the clock so                        |                   |                   |                  |                  |        |  |

| bit 9         | Unimplemen                   | ted: Read as '0                        | )'                |                   |                  |                  |        |  |

| bit 8         | ENFLTB: Fau                  | ult B Input Enab                       | le bit            |                   |                  |                  |        |  |

|               |                              | compare Fault B<br>compare Fault B     |                   |                   |                  |                  |        |  |

| bit 7         | -                            | ult A Input Enab                       |                   |                   |                  |                  |        |  |

|               | 1 = Output C                 | ompare Fault A<br>compare Fault A      | input (OCFA)      |                   |                  |                  |        |  |

| bit 6         | •                            | ted: Read as '0                        | • • •             |                   |                  |                  |        |  |

| bit 5         | OCFLTB: PW                   | M Fault B Con                          | dition Status bit |                   |                  |                  |        |  |

|               |                              | ult B condition of Fault B condition   |                   |                   |                  |                  |        |  |

| bit 4         |                              | /M Fault A Cond                        | •                 |                   |                  |                  |        |  |

|               |                              | ult A condition o                      |                   |                   |                  |                  |        |  |

| Note 1:       | OCvR and OCvE                | 29 are double h                        | uffered in D\\//  | / mode only       |                  |                  |        |  |

| Note 1.<br>2: |                              |                                        |                   |                   |                  |                  |        |  |

| 2.            | Generator (PTG               |                                        |                   |                   |                  | 5.1 2 7.0 1 611p |        |  |

|               | PTGO4 = OC1                  | -                                      |                   |                   |                  |                  |        |  |

|               | PTGO5 = OC2                  |                                        |                   |                   |                  |                  |        |  |

|               | PTGO6 = OC3<br>PTGO7 = OC4   |                                        |                   |                   |                  |                  |        |  |

|               |                              |                                        |                   |                   |                  |                  |        |  |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0      | R/W-0                                                                    | R/W-0                                                                                     | R/W-0                           | U-0               | U-0              | U-0                    | R/W-0        |  |

|------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------|-------------------|------------------|------------------------|--------------|--|

| FLTMD      | FLTOUT                                                                   | FLTTRIEN                                                                                  | OCINV                           | —                 | _                | —                      | OC32         |  |

| bit 15     | ·                                                                        |                                                                                           |                                 |                   | ·                |                        | bit          |  |

|            |                                                                          |                                                                                           |                                 |                   |                  |                        |              |  |

| R/W-0      | R/W-0, HS                                                                | R/W-0                                                                                     | R/W-0                           | R/W-1             | R/W-1            | R/W-0                  | R/W-0        |  |

| OCTRIC     | G TRIGSTAT                                                               | OCTRIS                                                                                    | SYNCSEL4                        | SYNCSEL3          | SYNCSEL2         | SYNCSEL1               | SYNCSEL      |  |

| bit 7      |                                                                          |                                                                                           |                                 |                   |                  |                        | bit          |  |

| Legend:    |                                                                          | HS = Hardwa                                                                               | re Settable bit                 |                   |                  |                        |              |  |

| R = Reada  | able bit                                                                 | W = Writable                                                                              | bit                             | U = Unimplem      | nented bit, read | l as '0'               |              |  |

| -n = Value | at POR                                                                   | '1' = Bit is set                                                                          |                                 | '0' = Bit is clea | ared             | x = Bit is unkn        | iown         |  |

|            |                                                                          |                                                                                           |                                 |                   |                  |                        |              |  |

| bit 15     | 1 = Fault mo<br>cleared i                                                | t Mode Select b<br>ode is maintain<br>n software and                                      | ed until the Fa<br>a new PWM pe | eriod starts      |                  |                        |              |  |

|            |                                                                          | de is maintaine                                                                           | d until the Faul                | t source is rem   | loved and a ne   | w PWM period           | starts       |  |

| bit 14     | FLTOUT: Fau                                                              |                                                                                           | . –                             |                   |                  |                        |              |  |

|            |                                                                          | tput is driven hi<br>tput is driven lo                                                    |                                 |                   |                  |                        |              |  |

| bit 13     |                                                                          | •                                                                                         |                                 |                   |                  |                        |              |  |

|            |                                                                          | FLTTRIEN: Fault Output State Select bit<br>1 = OCx pin is tri-stated on a Fault condition |                                 |                   |                  |                        |              |  |

|            | •                                                                        | I/O state is defi                                                                         |                                 |                   | ault condition   |                        |              |  |

| bit 12     | OCINV: Outp                                                              | ut Compare x I                                                                            | nvert bit                       |                   |                  |                        |              |  |

|            |                                                                          | out is inverted<br>out is not invert                                                      | ed                              |                   |                  |                        |              |  |

| bit 11-9   | Unimplemen                                                               | ted: Read as '                                                                            | כי                              |                   |                  |                        |              |  |

| bit 8      | OC32: Casca                                                              | ide Two OCx M                                                                             | odules Enable                   | bit (32-bit oper  | ration)          |                        |              |  |

|            |                                                                          | module operate module operate                                                             |                                 |                   |                  |                        |              |  |

| bit 7      |                                                                          | tput Compare x                                                                            |                                 | Select bit        |                  |                        |              |  |

|            |                                                                          | OCx from the s                                                                            |                                 |                   | CSELx bits       |                        |              |  |

|            |                                                                          | nizes OCx with                                                                            |                                 |                   |                  | S                      |              |  |

| bit 6      | TRIGSTAT: T                                                              | imer Trigger St                                                                           | atus bit                        |                   |                  |                        |              |  |

|            |                                                                          | urce has been <sup>.</sup><br>urce has not be                                             |                                 |                   | d clear          |                        |              |  |

| bit 5      |                                                                          | put Compare x                                                                             |                                 | •                 |                  |                        |              |  |

|            | 1 = OCx is tr                                                            | • •                                                                                       | ·                               |                   |                  |                        |              |  |

|            | 0 = Output C                                                             | ompare x mod                                                                              | ule drives the C                | OCx pin           |                  |                        |              |  |

| Note 1:    | Do not use the O                                                         | Cx module as i                                                                            | ts own Svnchro                  | nization or Tric  | aaer source.     |                        |              |  |

|            | When the OCy m                                                           |                                                                                           | -                               |                   |                  | module uses t          | he OCv       |  |

|            | module as a Trigg                                                        |                                                                                           |                                 |                   |                  |                        |              |  |

| 3:         | Each Output Con<br><b>"Peripheral Trig</b><br>PTGO0 = OC1<br>PTGO1 = OC2 |                                                                                           |                                 |                   |                  | n source. See <b>S</b> | Section 24.0 |  |

|            | PTGO2 = OC3 $PTGO3 = OC4$                                                |                                                                                           |                                 |                   |                  |                        |              |  |

# REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

# 19.1 I<sup>2</sup>C Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this UDL increases |

|-------|---------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                                               |

|       | http://www.microchip.com/wwwproducts/                                                                   |

|       | Devices.aspx?dDocName=en555464                                                                          |

## 19.1.1 KEY RESOURCES

- "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS70330) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                             |

|-------|----------------------------------------------------------------------------------------------------------|

|       | 1 = Indicates that a Start (or Repeated Start) bit has been detected last                                |

|       | 0 = Start bit was not detected last                                                                      |

|       | Hardware is set or clear when a Start, Repeated Start or Stop is detected.                               |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                        |

|       | 1 = Read – Indicates data transfer is output from the slave                                              |

|       | 0 = Write – Indicates data transfer is input to the slave                                                |

|       | Hardware is set or clear after reception of an I <sup>2</sup> C device address byte.                     |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                      |

|       | 1 = Receive is complete, I2CxRCV is full                                                                 |

|       | 0 = Receive is not complete, I2CxRCV is empty                                                            |

|       | Hardware is set when I2CxRCV is written with a received byte. Hardware is clear when software reads      |

|       | I2CxRCV.                                                                                                 |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                     |

|       | 1 = Transmit in progress, I2CxTRN is full                                                                |

|       | 0 = Transmit is complete, I2CxTRN is empty                                                               |

|       | Hardware is set when software writes to I2CxTRN. Hardware is clear at completion of a data transmission. |

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

#### REGISTER 21-24: CxRXOVF1: ECANx RECEIVE BUFFER OVERFLOW REGISTER 1

| RXOVF7  | RXOVF6 | RXOVF5         | RXOVF4            | RXOVF3         | RXOVF2             | RXOVF1 | RXOVF0 |

|---------|--------|----------------|-------------------|----------------|--------------------|--------|--------|

| bit 7   |        |                |                   |                |                    |        | bit 0  |

|         |        |                |                   |                |                    |        |        |

| Legend: |        | C = Writable b | oit, but only '0' | can be writter | n to clear the bit |        |        |

| Legend:           | C = Writable bit, but only '0' can be written to clear the bit |                             |                    |  |  |  |

|-------------------|----------------------------------------------------------------|-----------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                                               | U = Unimplemented bit, read | l as '0'           |  |  |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared        | x = Bit is unknown |  |  |  |

bit 15-0 RXOVF<15:0>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

#### REGISTER 21-25: CxRXOVF2: ECANx RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writable bit, but or | C = Writable bit, but only '0' can be written to clear the bit |                    |  |  |  |  |

|-------------------|--------------------------|----------------------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit                                          | t, read as '0'     |  |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared                                           | x = Bit is unknown |  |  |  |  |

bit 15-0 RXOVF<31:16>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

#### REGISTER 25-1: CMSTAT: OP AMP/COMPARATOR STATUS REGISTER (CONTINUED)

- C2OUT: Comparator 2 Output Status bit<sup>(2)</sup> bit 1 When CPOL = 0: 1 = VIN + > VIN -0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -C10UT: Comparator 1 Output Status bit<sup>(2)</sup> bit 0 When CPOL = 0: 1 = VIN + > VIN -0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -

- **Note 1:** Reflects the value of the of the CEVT bit in the respective Op Amp/Comparator Control register, CMxCON<9>.

- 2: Reflects the value of the COUT bit in the respective Op Amp/Comparator Control register, CMxCON<8>.

## 27.2 User ID Words

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices contain four User ID Words, located at addresses, 0x800FF8 through 0x800FFE. The User ID Words can be used for storing product information such as serial numbers, system manufacturing dates, manufacturing lot numbers and other application-specific information.

The User ID Words register map is shown in Table 27-3.

TABLE 27-3:USER ID WORDS REGISTER<br/>MAP

| File Name | Address  | Bits 23-16 | Bits 15-0 |

|-----------|----------|------------|-----------|

| FUID0     | 0x800FF8 | _          | UID0      |

| FUID1     | 0x800FFA | _          | UID1      |

| FUID2     | 0x800FFC | _          | UID2      |

| FUID3     | 0x800FFE | _          | UID3      |

**Legend:** — = unimplemented, read as '1'.

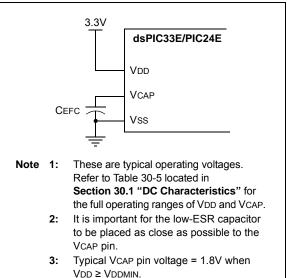

# 27.3 On-Chip Voltage Regulator

All of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X devices power their core digital logic at a nominal 1.8V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family incorporate an onchip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. A low-ESR (less than 1 Ohm) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 30-5 located in **Section 30.0 "Electrical Characteristics"**.

Note: It is important for the low-ESR capacitor to be placed as close as possible to the VCAP pin.

# FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE

REGULATOR<sup>(1,2,3)</sup>

# 27.4 Brown-out Reset (BOR)

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated supply voltage, VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT Time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM is applied. The total delay in this case is TFSCM. Refer to Parameter SY35 in Table 30-22 of **Section 30.0 "Electrical Characteristics"** for specific TFSCM values.

The BOR status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

| DC CHA       | RACTER | ISTICS                                              | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                     |      |       |                                                                |  |

|--------------|--------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|----------------------------------------------------------------|--|

| Param<br>No. | Symbol | Characteristic                                      | Min.                                                                                                                                                                                                 | Тур. <sup>(1)</sup> | Max. | Units | Conditions                                                     |  |

|              |        | Program Flash Memory                                |                                                                                                                                                                                                      |                     |      |       |                                                                |  |

| D130         | Eр     | Cell Endurance                                      | 10,000                                                                                                                                                                                               | —                   | _    | E/W   | -40°C to +125°C                                                |  |

| D131         | Vpr    | VDD for Read                                        | 3.0                                                                                                                                                                                                  | —                   | 3.6  | V     |                                                                |  |

| D132b        | VPEW   | VDD for Self-Timed Write                            | 3.0                                                                                                                                                                                                  | —                   | 3.6  | V     |                                                                |  |

| D134         | TRETD  | Characteristic Retention                            | 20                                                                                                                                                                                                   | _                   |      | Year  | Provided no other specifications are violated, -40°C to +125°C |  |

| D135         | IDDP   | Supply Current during<br>Programming <sup>(2)</sup> | —                                                                                                                                                                                                    | 10                  |      | mA    |                                                                |  |

| D136         | IPEAK  | Instantaneous Peak Current<br>During Start-up       | —                                                                                                                                                                                                    | —                   | 150  | mA    |                                                                |  |

| D137a        | TPE    | Page Erase Time                                     | 17.7                                                                                                                                                                                                 | —                   | 22.9 | ms    | TPE = 146893 FRC cycles,<br>TA = +85°C (See <b>Note 3)</b>     |  |

| D137b        | Тре    | Page Erase Time                                     | 17.5                                                                                                                                                                                                 | —                   | 23.1 | ms    | TPE = 146893 FRC cycles,<br>TA = +125°C (See <b>Note 3)</b>    |  |

| D138a        | Tww    | Word Write Cycle Time                               | 41.7                                                                                                                                                                                                 | —                   | 53.8 | μs    | Tww = 346 FRC cycles,<br>TA = +85°C (See <b>Note 3)</b>        |  |

| D138b        | Tww    | Word Write Cycle Time                               | 41.2                                                                                                                                                                                                 | —                   | 54.4 | μs    | Tww = 346 FRC cycles,<br>TA = +125°C (See <b>Note 3)</b>       |  |

#### TABLE 30-14: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

2: Parameter characterized but not tested in manufacturing.

3: Other conditions: FRC = 7.37 MHz, TUN<5:0> = 011111 (for Minimum), TUN<5:0> = 100000 (for Maximum). This parameter depends on the FRC accuracy (see Table 30-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). For complete details on calculating the Minimum and Maximum time, see Section 5.3 "Programming Operations".

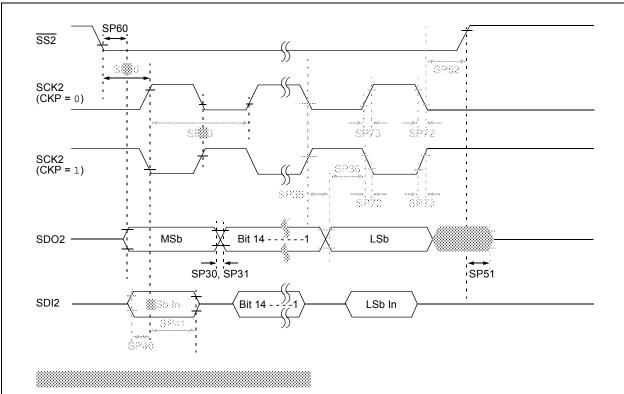

#### FIGURE 30-18: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

# TABLE 30-45:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| АС СНА |                       | rics                                         | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |                    |       |                                |  |

|--------|-----------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------|-------|--------------------------------|--|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                                                                                                                                                                                                                                                    | Тур. <sup>(2)</sup> | Max.               | Units | Conditions                     |  |

| SP70   | FscP                  | Maximum SCK1 Input<br>Frequency              | _                                                                                                                                                                                                                                                                                       |                     | Lesser of FP or 15 | MHz   | (Note 3)                       |  |

| SP72   | TscF                  | SCK1 Input Fall Time                         | _                                                                                                                                                                                                                                                                                       |                     |                    | ns    | See Parameter DO32<br>(Note 4) |  |

| SP73   | TscR                  | SCK1 Input Rise Time                         | —                                                                                                                                                                                                                                                                                       |                     | —                  | ns    | See Parameter DO31<br>(Note 4) |  |

| SP30   | TdoF                  | SDO1 Data Output Fall Time                   | —                                                                                                                                                                                                                                                                                       |                     | _                  | ns    | See Parameter DO32<br>(Note 4) |  |

| SP31   | TdoR                  | SDO1 Data Output Rise Time                   | —                                                                                                                                                                                                                                                                                       |                     | —                  | ns    | See Parameter DO31<br>(Note 4) |  |

| SP35   | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge    | —                                                                                                                                                                                                                                                                                       | 6                   | 20                 | ns    |                                |  |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge | 30                                                                                                                                                                                                                                                                                      |                     | _                  | ns    |                                |  |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge   | 30                                                                                                                                                                                                                                                                                      |                     |                    | ns    |                                |  |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge    | 30                                                                                                                                                                                                                                                                                      |                     | —                  | ns    |                                |  |

| SP50   | TssL2scH,<br>TssL2scL | SS1 ↓ to SCK1 ↑ or SCK1 ↓<br>Input           | 120                                                                                                                                                                                                                                                                                     |                     | —                  | ns    |                                |  |

| SP51   | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance       | 10                                                                                                                                                                                                                                                                                      | _                   | 50                 | ns    | (Note 4)                       |  |

| SP52   | TscH2ssH<br>TscL2ssH  | SS1 ↑ after SCK1 Edge                        | 1.5 Tcy + 40                                                                                                                                                                                                                                                                            | _                   | _                  | ns    | (Note 4)                       |  |

| SP60   | TssL2doV              | SDO1 Data Output Valid after<br>SS1 Edge     | —                                                                                                                                                                                                                                                                                       | _                   | 50                 | ns    |                                |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

**2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 66.7 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

| AC CHA       | RACTER      | ISTICS                        |                           | Standard Operatin<br>(unless otherwise<br>Operating tempera | stated)<br>iture -40 | )°C ≤ Ta ≤ | V to 3.6V<br>+85°C for Industrial<br>+125°C for Extended |  |

|--------------|-------------|-------------------------------|---------------------------|-------------------------------------------------------------|----------------------|------------|----------------------------------------------------------|--|

| Param<br>No. | Symbol      | Characte                      | eristic <sup>(4)</sup>    | Min. <sup>(1)</sup>                                         | -40<br>Max.          | Units      | Conditions                                               |  |

| IM10         | TLO:SCL     | Clock Low Time                | 100 kHz mode              | Tcy/2 (BRG + 2)                                             | _                    | μS         |                                                          |  |

|              |             |                               | 400 kHz mode              | TCY/2 (BRG + 2)                                             |                      | μ <b>S</b> |                                                          |  |

|              |             |                               | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                             |                      | μs         |                                                          |  |

| IM11         | THI:SCL (   | Clock High Time               | 100 kHz mode              | Tcy/2 (BRG + 2)                                             |                      | μS         |                                                          |  |

|              |             |                               | 400 kHz mode              | Tcy/2 (BRG + 2)                                             |                      | μs         |                                                          |  |

|              |             |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                             | _                    | μS         |                                                          |  |

| IM20         | TF:SCL      | SDAx and SCLx                 | 100 kHz mode              | _                                                           | 300                  | ns         | CB is specified to be                                    |  |

|              |             | Fall Time                     | 400 kHz mode              | 20 + 0.1 Св                                                 | 300                  | ns         | from 10 to 400 pF                                        |  |

|              |             |                               | 1 MHz mode <sup>(2)</sup> | _                                                           | 100                  | ns         |                                                          |  |

| IM21         | TR:SCL      | SDAx and SCLx                 | 100 kHz mode              | _                                                           | 1000                 | ns         | CB is specified to be                                    |  |

|              |             | Rise Time                     | 400 kHz mode              | 20 + 0.1 Св                                                 | 300                  | ns         | from 10 to 400 pF                                        |  |

|              |             |                               | 1 MHz mode <sup>(2)</sup> |                                                             | 300                  | ns         |                                                          |  |

| IM25         | M25 TSU:DAT | Data Input                    | 100 kHz mode              | 250                                                         |                      | ns         |                                                          |  |

|              |             | Setup Time                    | 400 kHz mode              | 100                                                         |                      | ns         |                                                          |  |

|              |             |                               | 1 MHz mode <sup>(2)</sup> | 40                                                          |                      | ns         |                                                          |  |

| IM26 Thd:dat | Data Input  | 100 kHz mode                  | 0                         |                                                             | μS                   |            |                                                          |  |

|              |             | Hold Time                     | 400 kHz mode              | 0                                                           | 0.9                  | μs         |                                                          |  |

|              |             |                               | 1 MHz mode <sup>(2)</sup> | 0.2                                                         |                      | μS         |                                                          |  |

| IM30         | TSU:STA     | Start Condition<br>Setup Time | 100 kHz mode              | TCY/2 (BRG + 2)                                             | _                    | μS         | Only relevant for<br>Repeated Start<br>condition         |  |

|              |             |                               | 400 kHz mode              | TCY/2 (BRG + 2)                                             | _                    | μS         |                                                          |  |

|              |             |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                             |                      | μS         |                                                          |  |

| IM31         | THD:STA     | Start Condition               | 100 kHz mode              | TCY/2 (BRG + 2)                                             | _                    | μS         | After this period, the                                   |  |

|              |             | Hold Time                     | 400 kHz mode              | TCY/2 (BRG +2)                                              | _                    | μS         | first clock pulse is                                     |  |

|              |             |                               | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                             |                      | μS         | generated                                                |  |

| IM33         | Tsu:sto     | Stop Condition                | 100 kHz mode              | TCY/2 (BRG + 2)                                             | _                    | μS         |                                                          |  |

|              |             | Setup Time                    | 400 kHz mode              | TCY/2 (BRG + 2)                                             |                      | μS         |                                                          |  |

|              |             |                               | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                             |                      | μS         |                                                          |  |

| IM34         | THD:STO     | Stop Condition                | 100 kHz mode              | TCY/2 (BRG + 2)                                             |                      | μS         |                                                          |  |

|              |             | Hold Time                     | 400 kHz mode              | TCY/2 (BRG + 2)                                             |                      | μS         |                                                          |  |

|              |             |                               | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                             |                      | μS         |                                                          |  |

| IM40         | TAA:SCL     | Output Valid                  | 100 kHz mode              | —                                                           | 3500                 | ns         |                                                          |  |

|              |             | From Clock                    | 400 kHz mode              |                                                             | 1000                 | ns         |                                                          |  |

|              |             |                               | 1 MHz mode <sup>(2)</sup> |                                                             | 400                  | ns         |                                                          |  |

| IM45         | TBF:SDA     | Bus Free Time                 | 100 kHz mode              | 4.7                                                         |                      | μS         | Time the bus must be                                     |  |

|              |             |                               | 400 kHz mode              | 1.3                                                         |                      | μS         | free before a new                                        |  |

|              |             |                               | 1 MHz mode <sup>(2)</sup> | 0.5                                                         | —                    | μS         | transmission can star                                    |  |

| IM50         | Св          | Bus Capacitive L              | oading                    | —                                                           | 400                  | pF         |                                                          |  |

| IM51         | Tpgd        | Pulse Gobbler De              | elay                      | 65                                                          | 390                  | ns         | (Note 3)                                                 |  |

### TABLE 30-49: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

Note 1: BRG is the value of the l<sup>2</sup>C<sup>™</sup> Baud Rate Generator. Refer to "Inter-Integrated Circuit (l<sup>2</sup>C<sup>™</sup>)" (DS70330) in the "dsPIC33/PIC24 Family Reference Manual". Please see the Microchip web site for the latest family reference manual sections.

- 2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

- **3:** Typical value for this parameter is 130 ns.

- 4: These parameters are characterized, but not tested in manufacturing.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| DC CHARACTERISTICS |               |      | (unless oth | Dperating Co<br>nerwise state<br>emperature | ed)  |                                               |  |  |

|--------------------|---------------|------|-------------|---------------------------------------------|------|-----------------------------------------------|--|--|

| Parameter<br>No.   | Typical       | Мах  | Units       | Conditions                                  |      |                                               |  |  |

| Power-Down         | Current (IPD) |      |             |                                             |      |                                               |  |  |

| HDC60e             | 1400          | 2500 | μA          | +150°C                                      | 3.3V | Base Power-Down Current (Notes 1, 3)          |  |  |

| HDC61c             | 15            | —    | μA          | +150°C                                      | 3.3V | Watchdog Timer Current: ∆IwDT<br>(Notes 2, 4) |  |  |

#### TABLE 31-4: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and pulled to Vss. WDT, etc., are all switched off and VREGS (RCON<8>) = 1.

2: The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

3: These currents are measured on the device containing the most memory in this family.

4: These parameters are characterized, but are not tested in manufacturing.

#### TABLE 31-5: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

| DC CHARAG        | DC CHARACTERISTICS |     |       | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |  |  |  |  |

|------------------|--------------------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Parameter<br>No. | Typical            | Мах | Units | Conditions                                                                                                                             |  |  |  |  |

| HDC44e           | 12                 | 30  | mA    | +150°C 3.3V 40 MIPS                                                                                                                    |  |  |  |  |

#### TABLE 31-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACTERISTICS |         |     | (unless othe | perating Conditions: 3.0V to 3.6V erwise stated) emperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |      |         |  |

|--------------------|---------|-----|--------------|-----------------------------------------------------------------------------------------------------|------|---------|--|

| Parameter<br>No.   | Typical | Max | Units        | Conditions                                                                                          |      |         |  |

| HDC20              | 9       | 15  | mA           | +150°C                                                                                              | 3.3V | 10 MIPS |  |

| HDC22              | 16      | 25  | mA           | +150°C                                                                                              | 3.3V | 20 MIPS |  |

| HDC23              | 30      | 50  | mA           | +150°C 3.3V 40 MIPS                                                                                 |      |         |  |

#### TABLE 31-7: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARA              | CTERISTICS | (unless oth | erwise s      | <b>Conditions</b><br>tated)<br>re -40°C ≤ |            |      |         |  |

|-----------------------|------------|-------------|---------------|-------------------------------------------|------------|------|---------|--|

| Parameter<br>No.      | Typical    | Мах         | Doze<br>Ratio | Units                                     | Conditions |      |         |  |

| HDC72a                | 24         | 35          | 1:2           | mA                                        |            |      | 40 MIPS |  |

| HDC72f <sup>(1)</sup> | 14         | —           | 1:64          | mA                                        | +150°C     | 3.3V |         |  |

| HDC72g <sup>(1)</sup> | 12         |             | 1:128         | mA                                        |            |      |         |  |

Note 1: Parameters with Doze ratios of 1:64 and 1:128 are characterized, but are not tested in manufacturing.

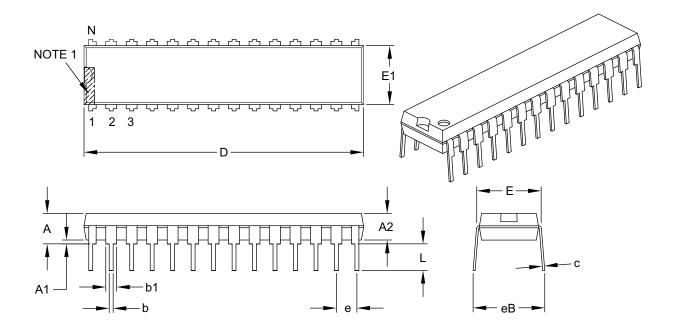

#### 33.2 Package Details

#### 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |       | INCHES   |       |  |  |

|----------------------------|------------------|-------|----------|-------|--|--|

| Dimension                  | Dimension Limits |       |          | MAX   |  |  |

| Number of Pins             | Ν                |       | 28       |       |  |  |

| Pitch                      | е                |       | .100 BSC |       |  |  |

| Top to Seating Plane       | Α                | -     | -        | .200  |  |  |

| Molded Package Thickness   | A2               | .120  | .135     | .150  |  |  |