Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I²C, IrDA, LINbus, QEI, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

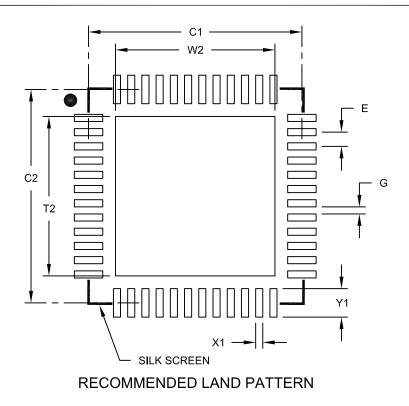

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 44-VTLA (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc504-i-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

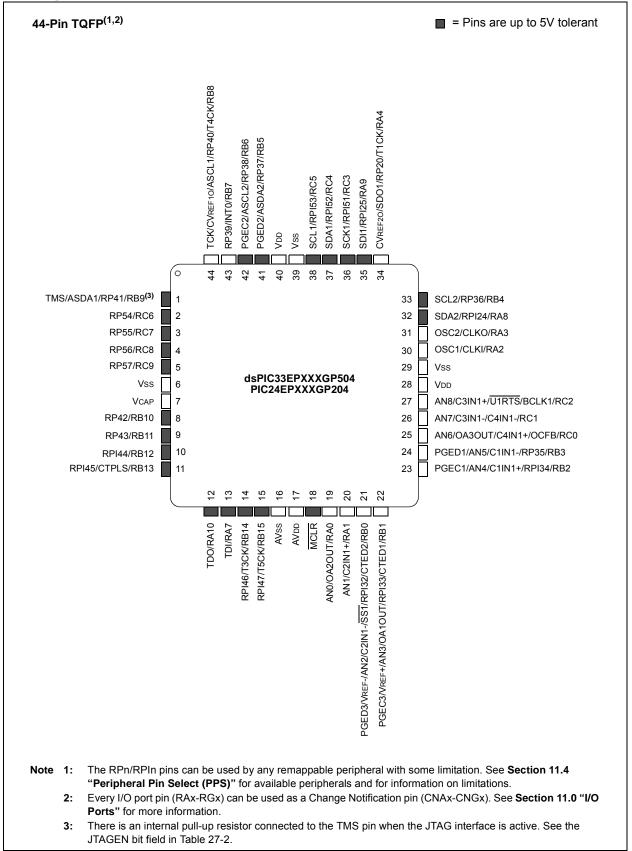

### **Pin Diagrams (Continued)**

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| Pin Name <sup>(4)</sup>       | Pin<br>Type | Buffer<br>Type | PPS     | Description                                                                                     |  |  |  |

|-------------------------------|-------------|----------------|---------|-------------------------------------------------------------------------------------------------|--|--|--|

| C1IN1-                        | I           | Analog         | No      | Op Amp/Comparator 1 Negative Input 1.                                                           |  |  |  |

| C1IN2-                        | I           | Analog         | No      | Comparator 1 Negative Input 2.                                                                  |  |  |  |

| C1IN1+                        | I           | Analog         | No      | Op Amp/Comparator 1 Positive Input 1.                                                           |  |  |  |

| OA1OUT                        | 0           | Analog         | No      | Op Amp 1 output.                                                                                |  |  |  |

| C1OUT                         | 0           | —              | Yes     | Comparator 1 output.                                                                            |  |  |  |

| C2IN1-                        | I           | Analog         | No      | Op Amp/Comparator 2 Negative Input 1.                                                           |  |  |  |

| C2IN2-                        | I           | Analog         | No      | Comparator 2 Negative Input 2.                                                                  |  |  |  |

| C2IN1+                        | I           | Analog         | No      | Op Amp/Comparator 2 Positive Input 1.                                                           |  |  |  |

| OA2OUT                        | 0           | Analog         | No      | Op Amp 2 output.                                                                                |  |  |  |

| C2OUT                         | 0           |                | Yes     | Comparator 2 output.                                                                            |  |  |  |

| C3IN1-                        | I           | Analog         | No      | Op Amp/Comparator 3 Negative Input 1.                                                           |  |  |  |

| C3IN2-                        | I           | Analog         | No      | Comparator 3 Negative Input 2.                                                                  |  |  |  |

| C3IN1+                        | I           | Analog         | No      | Op Amp/Comparator 3 Positive Input 1.                                                           |  |  |  |

| OA3OUT                        | 0           | Analog         | No      | Op Amp 3 output.                                                                                |  |  |  |

| C3OUT                         | 0           |                | Yes     | Comparator 3 output.                                                                            |  |  |  |

| C4IN1-                        | I.          | Analog         | No      | Comparator 4 Negative Input 1.                                                                  |  |  |  |

| C4IN1+                        | I.          | Analog         | No      | Comparator 4 Positive Input 1.                                                                  |  |  |  |

| C4OUT                         | 0           |                | Yes     | Comparator 4 output.                                                                            |  |  |  |

| CVREF10                       | 0           | Analog         | No      | Op amp/comparator voltage reference output.                                                     |  |  |  |

| CVREF20                       | 0           | Analog         | No      | Op amp/comparator voltage reference divided by 2 output.                                        |  |  |  |

| PGED1                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 1.                                 |  |  |  |

| PGEC1                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 1.                              |  |  |  |

| PGED2                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 2.                                 |  |  |  |

| PGEC2                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 2.                              |  |  |  |

| PGED3                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 3.                                 |  |  |  |

| PGEC3                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 3.                              |  |  |  |

| MCLR                          | I/P         | ST             | No      | Master Clear (Reset) input. This pin is an active-low Reset to the device.                      |  |  |  |

| AVDD                          | Р           | Р              | No      | Positive supply for analog modules. This pin must be connected at all times.                    |  |  |  |

| AVss                          | Р           | Р              | No      | Ground reference for analog modules. This pin must be connected at all times.                   |  |  |  |

| Vdd                           | Р           |                | No      | Positive supply for peripheral logic and I/O pins.                                              |  |  |  |

| VCAP                          | Р           |                | No      | CPU logic filter capacitor connection.                                                          |  |  |  |

| Vss                           | Р           |                | No      | Ground reference for logic and I/O pins.                                                        |  |  |  |

| VREF+                         | 1           | Analog         | No      | Analog voltage reference (high) input.                                                          |  |  |  |

| VREF-                         | Ι           | Analog         | No      | Analog voltage reference (low) input.                                                           |  |  |  |

| Legend: CMOS = C<br>ST = Schn | nitt Trigg  | jer input v    | with CI | or output     Analog = Analog input     P = Power       MOS levels     O = Output     I = Input |  |  |  |

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

PPS = Peripheral Pin Select

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

TTL = TTL input buffer

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz <  $F_{IN}$  < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

### 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

### 2.9 Application Examples

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- · Automotive HVAC, cooling fans, fuel pumps

- Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- Speech (playback, hands-free kits, answering machines, VoIP)

- Consumer audio

- Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- Data storage device management

- · Smart cards and smart card readers

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

### FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

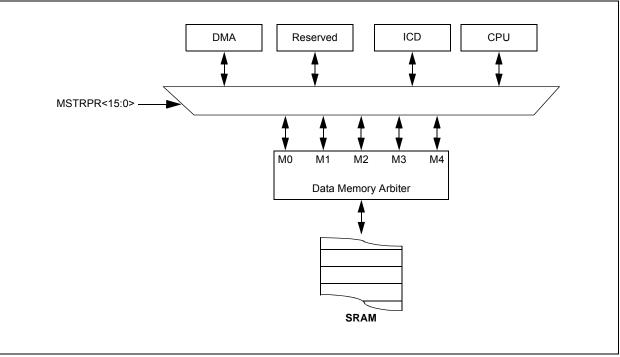

# 4.4.3 DATA MEMORY ARBITRATION AND BUS MASTER PRIORITY

EDS accesses from bus masters in the system are arbitrated.

The arbiter for data memory (including EDS) arbitrates between the CPU, the DMA and the ICD module. In the event of coincidental access to a bus by the bus masters, the arbiter determines which bus master access has the highest priority. The other bus masters are suspended and processed after the access of the bus by the bus master with the highest priority.

By default, the CPU is Bus Master 0 (M0) with the highest priority and the ICD is Bus Master 4 (M4) with the lowest priority. The remaining bus master (DMA Controller) is allocated to M3 (M1 and M2 are reserved and cannot be used). The user application may raise or lower the priority of the DMA Controller to be above that of the CPU by setting the appropriate bits in the EDS Bus Master Priority Control (MSTRPR) register. All bus masters with raised priorities will maintain the same priority relationship relative to each other (i.e., M1 being highest and M3 being lowest, with M2 in between). Also, all the bus masters with priorities below

### FIGURE 4-18: ARBITER ARCHITECTURE

that of the CPU maintain the same priority relationship relative to each other. The priority schemes for bus masters with different MSTRPR values are tabulated in Table 4-62.

This bus master priority control allows the user application to manipulate the real-time response of the system, either statically during initialization or dynamically in response to real-time events.

| TABLE 4-62: | DATA MEMORY BUS  |

|-------------|------------------|

|             | ARBITER PRIORITY |

| Drierity     | MSTRPR<15:0> Bit Setting <sup>(1)</sup> |          |  |  |  |

|--------------|-----------------------------------------|----------|--|--|--|

| Priority     | 0x0000                                  | 0x0020   |  |  |  |

| M0 (highest) | CPU                                     | DMA      |  |  |  |

| M1           | Reserved                                | CPU      |  |  |  |

| M2           | Reserved                                | Reserved |  |  |  |

| M3           | DMA                                     | Reserved |  |  |  |

| M4 (lowest)  | ICD                                     | ICD      |  |  |  |

**Note 1:** All other values of MSTRPR<15:0> are reserved.

|                                                     | Vector  | IRQ        |                   | Inte     | Interrupt Bit Location |              |  |

|-----------------------------------------------------|---------|------------|-------------------|----------|------------------------|--------------|--|

| Interrupt Source                                    | # #     |            | IVT Address       | Flag     | Enable                 | Priority     |  |

| QEI1 – QEI1 Position Counter Compare <sup>(2)</sup> | 66      | 58         | 0x000088          | IFS3<10> | IEC3<10>               | IPC14<10:8>  |  |

| Reserved                                            | 67-72   | 59-64      | 0x00008A-0x000094 | _        | _                      | _            |  |

| U1E – UART1 Error Interrupt                         | 73      | 65         | 0x000096          | IFS4<1>  | IEC4<1>                | IPC16<6:4>   |  |

| U2E – UART2 Error Interrupt                         | 74      | 66         | 0x000098          | IFS4<2>  | IEC4<2>                | IPC16<10:8>  |  |

| CRC – CRC Generator Interrupt                       | 75      | 67         | 0x00009A          | IFS4<3>  | IEC4<3>                | IPC16<14:12> |  |

| Reserved                                            | 76-77   | 68-69      | 0x00009C-0x00009E | —        | _                      | —            |  |

| C1TX – CAN1 TX Data Request <sup>(1)</sup>          | 78      | 70         | 0x000A0           | IFS4<6>  | IEC4<6>                | IPC17<10:8>  |  |

| Reserved                                            | 79-84   | 71-76      | 0x0000A2-0x0000AC | —        | _                      | —            |  |

| CTMU – CTMU Interrupt                               | 85      | 77         | 0x0000AE          | IFS4<13> | IEC4<13>               | IPC19<6:4>   |  |

| Reserved                                            | 86-101  | 78-93      | 0x0000B0-0x0000CE | —        | _                      | —            |  |

| PWM1 – PWM Generator 1 <sup>(2)</sup>               | 102     | 94         | 0x0000D0          | IFS5<14> | IEC5<14>               | IPC23<10:8>  |  |

| PWM2 – PWM Generator 2 <sup>(2)</sup>               | 103     | 95         | 0x0000D2          | IFS5<15> | IEC5<15>               | IPC23<14:12> |  |

| PWM3 – PWM Generator 3 <sup>(2)</sup>               | 104     | 96         | 0x0000D4          | IFS6<0>  | IEC6<0>                | IPC24<2:0>   |  |

| Reserved                                            | 105-149 | 97-141     | 0x0001D6-0x00012E | —        | _                      | —            |  |

| ICD – ICD Application                               | 150     | 142        | 0x000142          | IFS8<14> | IEC8<14>               | IPC35<10:8>  |  |

| JTAG – JTAG Programming                             | 151     | 143        | 0x000130          | IFS8<15> | IEC8<15>               | IPC35<14:12> |  |

| Reserved                                            | 152     | 144        | 0x000134          | —        | —                      | _            |  |

| PTGSTEP – PTG Step                                  | 153     | 145        | 0x000136          | IFS9<1>  | IEC9<1>                | IPC36<6:4>   |  |

| PTGWDT – PTG Watchdog Time-out                      | 154     | 146        | 0x000138          | IFS9<2>  | IEC9<2>                | IPC36<10:8>  |  |

| PTG0 – PTG Interrupt 0                              | 155     | 147        | 0x00013A          | IFS9<3>  | IEC9<3>                | IPC36<14:12> |  |

| PTG1 – PTG Interrupt 1                              | 156     | 148        | 0x00013C          | IFS9<4>  | IEC9<4>                | IPC37<2:0>   |  |

| PTG2 – PTG Interrupt 2                              | 157     | 149        | 0x00013E          | IFS9<5>  | IEC9<5>                | IPC37<6:4>   |  |

| PTG3 – PTG Interrupt 3                              | 158     | 150        | 0x000140          | IFS9<6>  | IEC9<6>                | IPC37<10:8>  |  |

| Reserved                                            | 159-245 | 151-245    | 0x000142-0x0001FE | —        | —                      | _            |  |

|                                                     | Lowe    | est Natura | I Order Priority  |          |                        |              |  |

### TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

2: This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 4 | MATHERR: Math Error Status bit                                                                        |

|-------|-------------------------------------------------------------------------------------------------------|

|       | 1 = Math error trap has occurred                                                                      |

|       | 0 = Math error trap has not occurred                                                                  |

| bit 3 | ADDRERR: Address Error Trap Status bit                                                                |

|       | <ul><li>1 = Address error trap has occurred</li><li>0 = Address error trap has not occurred</li></ul> |

| bit 2 | STKERR: Stack Error Trap Status bit                                                                   |

|       | 1 = Stack error trap has occurred                                                                     |

|       | 0 = Stack error trap has not occurred                                                                 |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit                                                    |

|       | 1 = Oscillator failure trap has occurred                                                              |

|       | 0 = Oscillator failure trap has not occurred                                                          |

| bit 0 | Unimplemented: Read as '0'                                                                            |

Note 1: These bits are available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 8-9: DSADRH: DMA MOST RECENT RAM HIGH ADDRESS REGISTER

| U-0            | U-0 | U-0             | U-0   | U-0          | U-0              | U-0    | U-0   |

|----------------|-----|-----------------|-------|--------------|------------------|--------|-------|

| —              | —   | —               | —     | —            | —                | -      | —     |

| bit 15         |     |                 |       |              |                  |        | bit 8 |

|                |     |                 |       |              |                  |        |       |

| R-0            | R-0 | R-0             | R-0   | R-0          | R-0              | R-0    | R-0   |

|                |     |                 | DSADR | <23:16>      |                  |        |       |

| bit 7          |     |                 |       |              |                  |        | bit 0 |

|                |     |                 |       |              |                  |        |       |

| Legend:        |     |                 |       |              |                  |        |       |

| R = Readable b | it  | W = Writable bi | t     | U = Unimpler | nented bit, read | as '0' |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

|-------------------|------------------|------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

#### bit 15-8 Unimplemented: Read as '0'

bit 7-0 DSADR<23:16>: Most Recent DMA Address Accessed by DMA bits

#### REGISTER 8-10: DSADRL: DMA MOST RECENT RAM LOW ADDRESS REGISTER

| R-0              | R-0        | R-0              | R-0                                     | R-0      | R-0 | R-0 | R-0   |

|------------------|------------|------------------|-----------------------------------------|----------|-----|-----|-------|

|                  |            |                  | DSAD                                    | DR<15:8> |     |     |       |

| bit 15           |            |                  |                                         |          |     |     | bit 8 |

|                  |            |                  |                                         |          |     |     |       |

| R-0              | R-0        | R-0              | R-0                                     | R-0      | R-0 | R-0 | R-0   |

|                  | DSADR<7:0> |                  |                                         |          |     |     |       |

| bit 7            |            |                  |                                         |          |     |     | bit 0 |

|                  |            |                  |                                         |          |     |     |       |

| Legend:          |            |                  |                                         |          |     |     |       |

| R = Readable b   | it         | W = Writable bit | bit U = Unimplemented bit, read as '0'  |          |     |     |       |

| -n = Value at PC | OR         | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |          |     |     | own   |

bit 15-0 DSADR<15:0>: Most Recent DMA Address Accessed by DMA bits

### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

### REGISTER 11-26: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|---------|-------|-------|

| —      | —   |       |       | RP118 | 3R<5:0> |       |       |

| bit 15 |     |       |       |       |         |       | bit 8 |

|        |     |       |       |       |         |       |       |

| U-0    | U-0 | U-0   | U-0   | U-0   | U-0     | U-0   | U-0   |

| —      | —   |       | —     | _     | _       | —     | _     |

| bit 7  |     |       |       |       |         |       | bit 0 |

|        |     |       |       |       |         |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP118R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP118 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 11-27: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------------|-------|-------|-------|-------|-------|

| —     | —   | RP120R<5:0> |       |       |       |       |       |

| bit 7 |     |             |       |       |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **RP120R<5:0>:** Peripheral Output Function is Assigned to RP120 Output Pin bits (see Table 11-3 for peripheral function numbers)

### 16.2 PWM Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

### 16.2.1 KEY RESOURCES

- "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|-----------------------------------|-------|------------------|------------------------------------|-----------------------------------------|-------|-------|-------|

|                                   |       |                  | INTHL                              | D<31:24>                                |       |       |       |

| bit 15                            |       |                  |                                    |                                         |       |       | bit 8 |

|                                   |       |                  |                                    |                                         |       |       |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                                   |       |                  | INTHL                              | D<23:16>                                |       |       |       |

| bit 7                             |       |                  |                                    |                                         |       |       | bit 0 |

|                                   |       |                  |                                    |                                         |       |       |       |

| Legend:                           |       |                  |                                    |                                         |       |       |       |

| R = Readable bit W = Writable bit |       |                  | U = Unimplemented bit, read as '0' |                                         |       |       |       |

| -n = Value at P                   | OR    | '1' = Bit is set |                                    | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-0 INTHLD<31:16>: Hold Register for Reading and Writing INT1TMRH bits

### REGISTER 17-20: INT1HLDL: INTERVAL 1 TIMER HOLD LOW WORD REGISTER

| R/W-0                                      | R/W-0 | R/W-0            | R/W-0        | R/W-0                                   | R/W-0    | R/W-0 | R/W-0 |

|--------------------------------------------|-------|------------------|--------------|-----------------------------------------|----------|-------|-------|

|                                            |       |                  | INTHL        | .D<15:8>                                |          |       |       |

| bit 15                                     |       |                  |              |                                         |          |       | bit 8 |

|                                            |       |                  |              |                                         |          |       |       |

| R/W-0                                      | R/W-0 | R/W-0            | R/W-0        | R/W-0                                   | R/W-0    | R/W-0 | R/W-0 |

|                                            |       |                  | INTH         | _D<7:0>                                 |          |       |       |

| bit 7                                      |       |                  |              |                                         |          |       | bit 0 |

|                                            |       |                  |              |                                         |          |       |       |

| Legend:                                    |       |                  |              |                                         |          |       |       |

| R = Readable bit W = Writable bit U = Unir |       |                  | U = Unimpler | nented bit, read                        | d as '0' |       |       |

| -n = Value at P                            | OR    | '1' = Bit is set |              | '0' = Bit is cleared x = Bit is unknown |          |       | nown  |

|                                            |       |                  |              |                                         |          |       |       |

bit 15-0 INTHLD<15:0>: Hold Register for Reading and Writing INT1TMRL bits

### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 6         | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)<br>Used in conjunction with the SCLREL bit.<br>1 = Enables software or receives clock stretching<br>0 = Disables software or receives clock stretching |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5         | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                                     |

|               | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                                       |

| bit 4         | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                   |

|               | <ul> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits ACKDT data bit. Hardware is clear at the end of the master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul>              |

| bit 3         | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                   |

|               | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware is clear at the end of the eighth bit of the master receive data byte.</li> <li>0 = Receive sequence is not in progress</li> </ul>                                             |

| bit 2         | <b>PEN:</b> Stop Condition Enable bit (when operating as $I^2C$ master)                                                                                                                                                                       |

| 511 2         | 1 = Initiates Stop condition on SDAx and SCLx pins. Hardware is clear at the end of the master Stop sequence.                                                                                                                                 |

| <b>h</b> :+ 4 | 0 = Stop condition is not in progress                                                                                                                                                                                                         |

| bit 1         | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                  |

|               | <ul> <li>1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware is clear at the end of the<br/>master Repeated Start sequence.</li> <li>0 = Repeated Start condition is not in progress</li> </ul>                            |

| bit 0         | <b>SEN:</b> Start Condition Enable bit (when operating as $l^2C$ master)                                                                                                                                                                      |

|               | <ul> <li>1 = Initiates Start condition on SDAx and SCLx pins. Hardware is clear at the end of the master Start sequence.</li> <li>0 = Start condition is not in progress</li> </ul>                                                           |

**Note 1:** When performing master operations, ensure that the IPMIEN bit is set to '0'.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|               | 23-2: Al         |                                                      | CONTROL REG                   |                 |                   |                  |              |

|---------------|------------------|------------------------------------------------------|-------------------------------|-----------------|-------------------|------------------|--------------|

| R/W-0         | R/W-             | -0 R/W-0                                             | U-0                           | U-0             | R/W-0             | R/W-0            | R/W-0        |

| VCFG2         | VCFC             | G1 VCFG0                                             | —                             | —               | CSCNA             | CHPS1            | CHPS0        |

| bit 15        |                  |                                                      |                               |                 |                   |                  | bit          |

| R-0           | R/W-             | -0 R/W-0                                             | R/W-0                         | R/W-0           | R/W-0             | R/W-0            | R/W-0        |

| BUFS          | SMP              |                                                      | SMPI2                         | SMPI1           | SMPI0             | BUFM             | ALTS         |

| bit 7         | Sivil            |                                                      | SIVILIZ                       |                 |                   | BOTIM            | bit          |

| Logondi       |                  |                                                      |                               |                 |                   |                  |              |

| Legend:       | . hit            | VV - VV/ritable                                      |                               |                 | montod hit roo    |                  |              |

| R = Readable  |                  | W = Writable                                         |                               |                 | mented bit, read  |                  |              |

| -n = Value at | POR              | '1' = Bit is se                                      | et '(                         | )' = Bit is cle | eared             | x = Bit is unkr  | nown         |

| bit 15-13     | VCFG<2           | 2:0>: Converter Vol                                  | tage Reference C              | onfiguration    | bits              |                  |              |

|               | Value            | VREFH                                                | VREFL                         |                 |                   |                  |              |

|               | 000              | Avdd                                                 | Avss                          |                 |                   |                  |              |

|               | 001              | External VREF+                                       | Avss                          |                 |                   |                  |              |

|               | 010              | Avdd                                                 | External VREF-                |                 |                   |                  |              |

|               | 011              | External VREF+                                       | External VREF-                |                 |                   |                  |              |

|               | 1xx              | Avdd                                                 | Avss                          |                 |                   |                  |              |

| bit 12-11     | Unimple          | emented: Read as                                     | 'O'                           |                 |                   |                  |              |

| bit 10        |                  | : Input Scan Select                                  |                               |                 |                   |                  |              |

|               |                  | ns inputs for CH0+                                   |                               | JXA             |                   |                  |              |

|               |                  | s not scan inputs                                    | 5 1                           |                 |                   |                  |              |

| bit 9-8       | CHPS<1           | 1:0>: Channel Sele                                   | ct bits                       |                 |                   |                  |              |

|               | <u>In 12-bit</u> | mode (AD21B = 1                                      | <u>), the CHPS&lt;1:0&gt;</u> | bits are Uni    | mplemented an     | d are Read as    | <u>'0':</u>  |

|               |                  | nverts CH0, CH1, (                                   |                               |                 |                   |                  |              |

|               |                  | nverts CH0 and CH<br>nverts CH0                      | 11                            |                 |                   |                  |              |

| L:1 7         |                  |                                                      |                               |                 |                   |                  |              |

| bit 7         |                  | Buffer Fill Status bit<br>C is currently filling t   |                               | -               | o ucor opplicat   | ion chould coor  | oo data in t |

|               |                  | half of the buffer                                   | the second hall of            | line buller, li | ie user applicat  |                  |              |

|               |                  | C is currently filling                               | the first half of the         | e buffer; the   | e user applicatio | on should acce   | ss data in t |

|               |                  | ond half of the buffe                                |                               |                 |                   |                  |              |

| bit 6-2       | SMPI<4           | :0>: Increment Rat                                   | e bits                        |                 |                   |                  |              |

|               |                  | DDMAEN = 0:                                          |                               |                 |                   |                  |              |

|               |                  | Generates interru                                    |                               |                 |                   |                  |              |

|               | x1110 =          | Generates interru                                    | pt after completion           | of every 15     | oth sample/conv   | ersion operation | on           |

|               | •                |                                                      |                               |                 |                   |                  |              |

|               | •                |                                                      |                               |                 |                   |                  |              |

|               |                  | Generates interru                                    |                               |                 |                   |                  | n            |

|               |                  | <ul> <li>Generates interru</li> </ul>                | pt after completior           | of every sa     | ample/conversion  | n operation      |              |

|               |                  | $\frac{\text{DDMAEN} = 1}{\text{Increments the DN}}$ | 11 address offer a            | omplation of    | four 20rd of      | male (conversi   | on onoratio  |

|               |                  | Increments the DI<br>Increments the DI               |                               |                 |                   |                  |              |

|               | •                |                                                      |                               | Simpletion      | n every orac sa   |                  |              |

|               |                  |                                                      |                               |                 |                   |                  |              |

|               | •                |                                                      |                               |                 |                   |                  |              |

|               | •                | - Increments the DI                                  |                               |                 |                   |                  |              |

#### . . ACOND. ADCA CONTROL DECISTED 2

### REGISTER 24-8: PTGC1LIM: PTG COUNTER 1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|----------|-------|-------|-------|

|        |       |       | PTGC1L | IM<15:8> |       |       |       |

| bit 15 |       |       |        |          |       |       | bit 8 |

|        |       |       |        |          |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | PTGC1L | IM<7:0>  |       |       |       |

| bit 7  |       |       |        |          |       |       | bit C |

| Legena.           |                                                                  |                      |                    |  |

|-------------------|------------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                                 | '0' = Bit is cleared | x = Bit is unknown |  |

bit 15-0 **PTGC1LIM<15:0>:** PTG Counter 1 Limit Register bits May be used to specify the loop count for the PTGJMPC1 Step command or as a limit register for the General Purpose Counter 1.

### REGISTER 24-9: PTGHOLD: PTG HOLD REGISTER<sup>(1)</sup>

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|---------------|-------|-------|-------|-------|-------|-------|-------|--|

| PTGHOLD<15:8> |       |       |       |       |       |       |       |  |

| bit 15        |       |       |       |       |       |       |       |  |

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|

| PTGHOLD<7:0> |       |       |       |       |       |       |       |  |

| bit 7 k      |       |       |       |       |       |       |       |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PTGHOLD<15:0>:** PTG General Purpose Hold Register bits Holds user-supplied data to be copied to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGCOPY command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

| oit 3-0 | Step<br>Command        | OPTION<3:0> | Option Description                                                                                             |  |  |  |  |  |

|---------|------------------------|-------------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|         | PTGCTRL(1)             | 0000        | Reserved.                                                                                                      |  |  |  |  |  |

|         |                        | 0001        | Reserved.                                                                                                      |  |  |  |  |  |

|         |                        | 0010        | Disable Step Delay Timer (PTGSD).                                                                              |  |  |  |  |  |

|         |                        | 0011        | Reserved.                                                                                                      |  |  |  |  |  |

|         |                        | 0100        | Reserved.                                                                                                      |  |  |  |  |  |

|         |                        | 0101        | Reserved.                                                                                                      |  |  |  |  |  |

|         |                        | 0110        | Enable Step Delay Timer (PTGSD).                                                                               |  |  |  |  |  |

|         |                        | 0111        | Reserved.                                                                                                      |  |  |  |  |  |

|         |                        | 1000        | Start and wait for the PTG Timer0 to match the Timer0 Limit Register.                                          |  |  |  |  |  |

|         |                        | 1001        | Start and wait for the PTG Timer1 to match the Timer1 Limit Register.                                          |  |  |  |  |  |

|         |                        | 1010        | Reserved.                                                                                                      |  |  |  |  |  |

|         |                        | 1011        | Wait for the software trigger bit transition from low-to-high before continuing $(PTGSWT = 0 \text{ to } 1)$ . |  |  |  |  |  |

|         |                        | 1100        | Copy contents of the Counter 0 register to the AD1CHS0 register.                                               |  |  |  |  |  |

|         |                        | 1101        | Copy contents of the Counter 1 register to the AD1CHS0 register.                                               |  |  |  |  |  |

|         |                        | 1110        | Copy contents of the Literal 0 register to the AD1CHS0 register.                                               |  |  |  |  |  |

|         |                        | 1111        | Generate triggers indicated in the Broadcast Trigger Enable register (PTGBTE).                                 |  |  |  |  |  |

|         | PTGADD <sup>(1)</sup>  | 0000        | Add contents of the PTGADJ register to the Counter 0 Limit register (PTGC0LIM).                                |  |  |  |  |  |

|         |                        | 0001        | Add contents of the PTGADJ register to the Counter 1 Limit register (PTGC1LIM).                                |  |  |  |  |  |

|         |                        | 0010        | Add contents of the PTGADJ register to the Timer0 Limit register (PTGT0LIM).                                   |  |  |  |  |  |

|         |                        | 0011        | Add contents of the PTGADJ register to the Timer1 Limit register (PTGT1LIM).                                   |  |  |  |  |  |

|         |                        | 0100        | Add contents of the PTGADJ register to the Step Delay Limit register (PTGSDLIM)                                |  |  |  |  |  |

|         |                        | 0101        | Add contents of the PTGADJ register to the Literal 0 register (PTGL0).                                         |  |  |  |  |  |

|         |                        | 0110        | Reserved.                                                                                                      |  |  |  |  |  |

|         |                        | 0111        | Reserved.                                                                                                      |  |  |  |  |  |

|         | PTGCOPY <sup>(1)</sup> | 1000        | Copy contents of the PTGHOLD register to the Counter 0 Limit register (PTGC0LIM).                              |  |  |  |  |  |

|         |                        | 1001        | Copy contents of the PTGHOLD register to the Counter 1 Limit register (PTGC1LIM).                              |  |  |  |  |  |

|         |                        | 1010        | Copy contents of the PTGHOLD register to the Timer0 Limit register (PTGT0LIM).                                 |  |  |  |  |  |

|         |                        | 1011        | Copy contents of the PTGHOLD register to the Timer1 Limit register (PTGT1LIM).                                 |  |  |  |  |  |

|         |                        | 1100        | Copy contents of the PTGHOLD register to the Step Delay Limit register (PTGSDLIM).                             |  |  |  |  |  |

|         |                        | 1101        | Copy contents of the PTGHOLD register to the Literal 0 register (PTGL0).                                       |  |  |  |  |  |

|         |                        | 1110        | Reserved.                                                                                                      |  |  |  |  |  |

|         |                        | 1111        | Reserved.                                                                                                      |  |  |  |  |  |

### TABLE 24-1: PTG STEP COMMAND FORMAT (CONTINUED)

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

2: Refer to Table 24-2 for the trigger output descriptions.

3: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

| PTG Output<br>Number | PTG Output Description                                  |

|----------------------|---------------------------------------------------------|

| PTGO0                | Trigger/Synchronization Source for OC1                  |

| PTGO1                | Trigger/Synchronization Source for OC2                  |

| PTGO2                | Trigger/Synchronization Source for OC3                  |

| PTGO3                | Trigger/Synchronization Source for OC4                  |

| PTGO4                | Clock Source for OC1                                    |

| PTGO5                | Clock Source for OC2                                    |

| PTGO6                | Clock Source for OC3                                    |

| PTGO7                | Clock Source for OC4                                    |

| PTGO8                | Trigger/Synchronization Source for IC1                  |

| PTGO9                | Trigger/Synchronization Source for IC2                  |

| PTGO10               | Trigger/Synchronization Source for IC3                  |

| PTGO11               | Trigger/Synchronization Source for IC4                  |

| PTGO12               | Sample Trigger for ADC                                  |

| PTGO13               | Sample Trigger for ADC                                  |

| PTGO14               | Sample Trigger for ADC                                  |

| PTGO15               | Sample Trigger for ADC                                  |

| PTGO16               | PWM Time Base Synchronous Source for PWM <sup>(1)</sup> |

| PTGO17               | PWM Time Base Synchronous Source for PWM <sup>(1)</sup> |

| PTGO18               | Mask Input Select for Op Amp/Comparator                 |

| PTGO19               | Mask Input Select for Op Amp/Comparator                 |

| PTGO20               | Reserved                                                |

| PTGO21               | Reserved                                                |

| PTGO22               | Reserved                                                |

| PTGO23               | Reserved                                                |

| PTGO24               | Reserved                                                |

| PTGO25               | Reserved                                                |

| PTGO26               | Reserved                                                |

| PTGO27               | Reserved                                                |

| PTGO28               | Reserved                                                |

| PTGO29               | Reserved                                                |

| PTGO30               | PTG Output to PPS Input Selection                       |

| PTGO31               | PTG Output to PPS Input Selection                       |

### TABLE 24-2: PTG OUTPUT DESCRIPTIONS

Note 1: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

| DC CHARACTE      | RISTICS                       |               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                       |                 |  |  |  |

|------------------|-------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|--|--|--|

| Parameter<br>No. | Тур.                          | Max.          | Units                                                                                                                                                                                                                                                                                   | Conditions            |                 |  |  |  |

| Power-Down Cu    | urrent (IPD) <sup>(1)</sup> - | dsPIC33EP32GI | P50X, dsPIC33EF                                                                                                                                                                                                                                                                         | 32MC20X/50X and PIC2  | 4EP32GP/MC20X   |  |  |  |

| DC60d            | 30                            | 100           | μA                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |  |

| DC60a            | 35                            | 100           | μA                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |  |

| DC60b            | 150                           | 200           | μA                                                                                                                                                                                                                                                                                      | +85°C                 | 3.3V            |  |  |  |

| DC60c            | 250                           | 500           | μA                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |  |

| Power-Down Cu    | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP64GI | P50X, dsPIC33EF                                                                                                                                                                                                                                                                         | 64MC20X/50X and PIC2  | 4EP64GP/MC20X   |  |  |  |

| DC60d            | 25                            | 100           | μA                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |  |

| DC60a            | 30                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |  |

| DC60b            | 150                           | 350           | μΑ                                                                                                                                                                                                                                                                                      | +85°C                 |                 |  |  |  |

| DC60c            | 350                           | 800           | μΑ                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |  |

| Power-Down Cu    | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP128G | P50X, dsPIC33E                                                                                                                                                                                                                                                                          | P128MC20X/50X and PIC | 24EP128GP/MC20X |  |  |  |

| DC60d            | 30                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |  |

| DC60a            | 35                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |  |

| DC60b            | 150                           | 350           | μΑ                                                                                                                                                                                                                                                                                      | +85°C                 | 5.57            |  |  |  |

| DC60c            | 550                           | 1000          | μΑ                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |  |

| Power-Down Cu    | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP256G | P50X, dsPIC33E                                                                                                                                                                                                                                                                          | P256MC20X/50X and PIC | 24EP256GP/MC20X |  |  |  |

| DC60d            | 35                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |  |

| DC60a            | 40                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |  |

| DC60b            | 250                           | 450           | μΑ                                                                                                                                                                                                                                                                                      | +85°C                 | 0.0 V           |  |  |  |

| DC60c            | 1000                          | 1200          | μΑ                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |  |

| Power-Down Cu    | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP512G | P50X, dsPIC33E                                                                                                                                                                                                                                                                          | P512MC20X/50X and PIC | 24EP512GP/MC20X |  |  |  |

| DC60d            | 40                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |  |

| DC60a            | 45                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |  |

| DC60b            | 350                           | 800           | μΑ                                                                                                                                                                                                                                                                                      | +85°C                 | 0.0 V           |  |  |  |

| DC60c            | 1100                          | 1500          | μA                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |  |

### TABLE 30-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

Note 1: IPD (Sleep) current is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all set)

- The VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to standby while the device is in Sleep mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- JTAG is disabled

| AC CHARACTERISTICS |       |                                                                                                     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |         |       |      |                                      |  |

|--------------------|-------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------|-------|------|--------------------------------------|--|

|                    |       |                                                                                                     |                                                       |         |       |      |                                      |  |

|                    |       | Cloci                                                                                               | k Parame                                              | eters   |       |      |                                      |  |

| AD50               | TAD   | ADC Clock Period                                                                                    | 76                                                    | _       | _     | ns   |                                      |  |

| AD51               | tRC   | ADC Internal RC Oscillator Period <sup>(2)</sup>                                                    |                                                       | 250     | _     | ns   |                                      |  |

|                    | •     | Conv                                                                                                | version F                                             | Rate    |       | •    |                                      |  |

| AD55               | tCONV | Conversion Time                                                                                     |                                                       | 12 Tad  | _     |      |                                      |  |

| AD56               | FCNV  | Throughput Rate                                                                                     | _                                                     | —       | 1.1   | Msps | Using simultaneous sampling          |  |

| AD57a              | TSAMP | Sample Time when Sampling any ANx Input                                                             | 2 Tad                                                 | —       | _     | —    |                                      |  |

| AD57b              | TSAMP | Sample Time when Sampling the Op Amp Outputs (Configuration A and Configuration B) <sup>(4,5)</sup> | 4 Tad                                                 | _       | —     | —    |                                      |  |

|                    |       | Timin                                                                                               | g Param                                               | eters   |       |      |                                      |  |

| AD60               | tPCS  | Conversion Start from Sample<br>Trigger <sup>(2,3)</sup>                                            | 2 Tad                                                 | —       | 3 Tad | —    | Auto-convert trigger is not selected |  |

| AD61               | tPSS  | Sample Start from Setting<br>Sample (SAMP) bit <sup>(2,3))</sup>                                    | 2 Tad                                                 | —       | 3 Tad | —    |                                      |  |

| AD62               | tcss  | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(2,3)</sup>                                | _                                                     | 0.5 Tad |       | —    |                                      |  |

| AD63               | tdpu  | Time to Stabilize Analog Stage<br>from ADC Off to ADC On <sup>(2,3)</sup>                           |                                                       | —       | 20    | μs   | (Note 6)                             |  |

### TABLE 30-61: ADC CONVERSION (10-BIT MODE) TIMING REQUIREMENTS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: Parameters are characterized but not tested in manufacturing.

- **3:** Because the sample caps will eventually lose charge, clock rates below 10 kHz may affect linearity performance, especially at elevated temperatures.

- 4: See Figure 25-6 for configuration information.

- 5: See Figure 25-7 for configuration information.

- 6: The parameter, tDPU, is the time required for the ADC module to stabilize at the appropriate level when the module is turned on (ADON (AD1CON1<15>) = 1). During this time, the ADC result is indeterminate.

### TABLE 30-62: DMA MODULE TIMING REQUIREMENTS

|              |                                | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                     |      |       |            |  |