Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                 |

|---------------------------|---------------------------------------------------------------------------------|

| Product Status            | Active                                                                          |

| Core Processor            | dsPIC                                                                           |

|                           |                                                                                 |

| Core Size                 | 16-Bit                                                                          |

| Speed                     | 60 MIPs                                                                         |

| Connectivity              | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                    |

| Peripherals               | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| lumber of I/O             | 53                                                                              |

| Program Memory Size       | 64KB (22K x 24)                                                                 |

| rogram Memory Type        | FLASH                                                                           |

| EPROM Size                | -                                                                               |

| AM Size                   | 4K x 16                                                                         |

| oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| ata Converters            | A/D 16x10b/12b                                                                  |

| Scillator Type            | Internal                                                                        |

| perating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Nounting Type             | Surface Mount                                                                   |

| ackage / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package   | 64-VQFN (9x9)                                                                   |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc506-e-mr |

# **Table of Contents**

| 1.0   | Device Overview                                                                                    | 25  |

|-------|----------------------------------------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-bit Digital Signal Controllers and Microcontrollers         | 29  |

| 3.0   | CPU                                                                                                | 35  |

| 4.0   | Memory Organization                                                                                | 45  |

| 5.0   | Flash Program Memory                                                                               | 119 |

| 6.0   | Resets                                                                                             | 123 |

| 7.0   | Interrupt Controller                                                                               | 127 |

| 8.0   | Direct Memory Access (DMA)                                                                         | 139 |

| 9.0   | Oscillator Configuration                                                                           | 153 |

| 10.0  | Power-Saving Features                                                                              | 163 |

| 11.0  | I/O Ports                                                                                          | 173 |

| 12.0  | Timer1                                                                                             | 203 |

| 13.0  | Timer2/3 and Timer4/5                                                                              | 207 |

| 14.0  | Input Capture                                                                                      | 213 |

|       | Output Compare                                                                                     |     |

| 16.0  | High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)                     | 225 |

| 17.0  | Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only) | 249 |

|       | Serial Peripheral Interface (SPI)                                                                  |     |

| 19.0  | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                                                      | 273 |

| 20.0  | Universal Asynchronous Receiver Transmitter (UART)                                                 | 281 |

| 21.0  | Enhanced CAN (ECAN™) Module (dsPIC33EPXXXGP/MC50X Devices Only)                                    | 287 |

| 22.0  | Charge Time Measurement Unit (CTMU)                                                                | 315 |

| 23.0  | 10-Bit/12-Bit Analog-to-Digital Converter (ADC)                                                    | 321 |

| 24.0  | Peripheral Trigger Generator (PTG) Module                                                          | 337 |

|       | Op Amp/Comparator Module                                                                           |     |

| 26.0  | Programmable Cyclic Redundancy Check (CRC) Generator                                               | 373 |

| 27.0  | Special Features                                                                                   | 379 |

| 28.0  | Instruction Set Summary                                                                            | 387 |

| 29.0  | Development Support                                                                                | 397 |

| 30.0  | Electrical Characteristics                                                                         | 401 |

| 31.0  | High-Temperature Electrical Characteristics                                                        | 467 |

| 32.0  | DC and AC Device Characteristics Graphs                                                            | 475 |

| 33.0  | Packaging Information                                                                              | 479 |

|       | endix A: Revision History                                                                          |     |

| Index | X                                                                                                  | 517 |

| The I | Microchip Web Site                                                                                 | 525 |

| Cust  | omer Change Notification Service                                                                   | 525 |

| Cust  | omer Support                                                                                       | 525 |

| Prod  | uct Identification System                                                                          | 527 |

# 3.5 Programmer's Model

The programmer's model for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X is shown in Figure 3-2. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions. Table 3-1 lists a description of each register.

In addition to the registers contained in the programmer's model, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/

MC20X devices contain control registers for Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only), Bit-Reversed Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only) and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory mapped, as shown in Table 4-1.

TABLE 3-1: PROGRAMMER'S MODEL REGISTER DESCRIPTIONS

| Register(s) Name                                      | Description                                               |

|-------------------------------------------------------|-----------------------------------------------------------|

| W0 through W15                                        | Working Register Array                                    |

| ACCA, ACCB                                            | 40-Bit DSP Accumulators                                   |

| PC                                                    | 23-Bit Program Counter                                    |

| SR                                                    | ALU and DSP Engine STATUS Register                        |

| SPLIM                                                 | Stack Pointer Limit Value Register                        |

| TBLPAG                                                | Table Memory Page Address Register                        |

| DSRPAG                                                | Extended Data Space (EDS) Read Page Register              |

| DSWPAG                                                | Extended Data Space (EDS) Write Page Register             |

| RCOUNT                                                | REPEAT Loop Count Register                                |

| DCOUNT <sup>(1)</sup>                                 | DO Loop Count Register                                    |

| DOSTARTH <sup>(1,2)</sup> , DOSTARTL <sup>(1,2)</sup> | DO Loop Start Address Register (High and Low)             |

| DOENDH <sup>(1)</sup> , DOENDL <sup>(1)</sup>         | DO Loop End Address Register (High and Low)               |

| CORCON                                                | Contains DSP Engine, DO Loop Control and Trap Status bits |

Note 1: This register is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

**<sup>2:</sup>** The DOSTARTH and DOSTARTL registers are read-only.

# 3.6 CPU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note:

In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en555464

#### 3.6.1 KEY RESOURCES

- "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

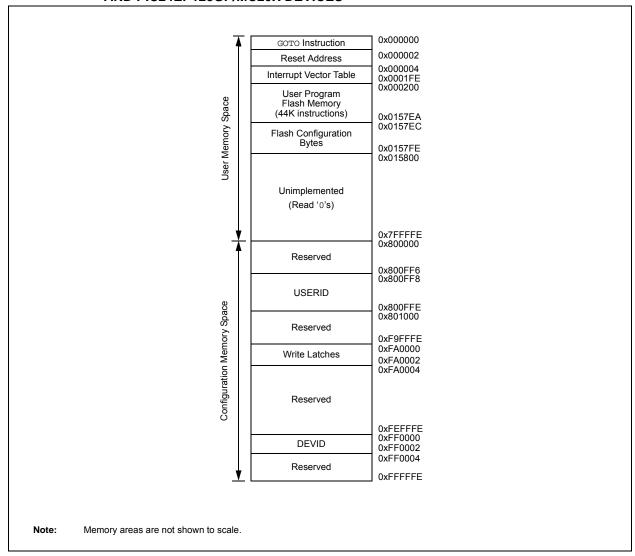

FIGURE 4-3: PROGRAM MEMORY MAP FOR dsPIC33EP128GP50X, dsPIC33EP128MC20X/50X AND PIC24EP128GP/MC20X DEVICES

| Ō          |

|------------|

| 7          |

| 0          |

| Ō          |

| Ō          |

| Ō          |

| Ō          |

| ĆΉ         |

| ₹i         |

|            |

| _          |

| $\tau$     |

| Ö          |

| $\approx$  |

| 'n         |

| മ          |

| ī          |

| 10         |

| $\sim$     |

| CH.        |

| $^{\circ}$ |

|            |

|            |

#### **TABLE 4-8: TIMER1 THROUGH TIMER5 REGISTER MAP**

| SFR<br>Name | Addr. | Bit 15 | Bit 14                                       | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8        | Bit 7         | Bit 6        | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|----------------------------------------------|--------|--------|--------|--------|--------------|--------------|---------------|--------------|-------|--------|-------|-------|-------|-------|---------------|

| TMR1        | 0100  |        |                                              |        |        |        |        |              | Timer1       | Register      |              |       |        |       |       |       |       | xxxx          |

| PR1         | 0102  |        |                                              |        |        |        |        |              | Period F     | Register 1    |              |       |        |       |       |       |       | FFFF          |

| T1CON       | 0104  | TON    | N - TSIDL TGATE TCKPS<1:0> - TSYNC TCS - 000 |        |        |        |        |              |              |               |              |       |        | 0000  |       |       |       |               |

| TMR2        | 0106  |        | Timer2 Register xxx                          |        |        |        |        |              |              |               |              |       |        | xxxx  |       |       |       |               |

| TMR3HLD     | 0108  |        |                                              |        |        |        | Time   | er3 Holding  | Register (fo | r 32-bit time | r operations | only) |        |       |       |       |       | xxxx          |

| TMR3        | 010A  |        |                                              |        |        |        |        |              | Timer3       | Register      |              |       |        |       |       |       |       | xxxx          |

| PR2         | 010C  |        |                                              |        |        |        |        |              | Period F     | Register 2    |              |       |        |       |       |       |       | FFFF          |

| PR3         | 010E  |        |                                              |        |        |        |        |              | Period F     | Register 3    |              |       |        |       |       |       |       | FFFF          |

| T2CON       | 0110  | TON    | _                                            | TSIDL  | _      | _      | _      | _            | _            | _             | TGATE        | TCKPS | S<1:0> | T32   | _     | TCS   | _     | 0000          |

| T3CON       | 0112  | TON    | _                                            | TSIDL  | _      | _      | _      | _            | _            | _             | TGATE        | TCKPS | S<1:0> | _     | _     | TCS   | _     | 0000          |

| TMR4        | 0114  |        |                                              |        |        |        |        |              | Timer4       | Register      |              |       |        |       |       |       |       | xxxx          |

| TMR5HLD     | 0116  |        |                                              |        |        |        | Т      | imer5 Holdir | ng Register  | (for 32-bit o | perations on | ly)   |        |       |       |       |       | xxxx          |

| TMR5        | 0118  |        |                                              |        |        |        |        |              | Timer5       | Register      |              |       |        |       |       |       |       | xxxx          |

| PR4         | 011A  |        | Period Register 4 FFFF                       |        |        |        |        |              |              |               |              |       |        | FFFF  |       |       |       |               |

| PR5         | 011C  |        | Period Register 5 FFFF                       |        |        |        |        |              |              |               |              |       |        |       | FFFF  |       |       |               |

| T4CON       | 011E  | TON    | _                                            | TSIDL  | _      | _      | _      | _            | _            | _             | TGATE        | TCKPS | S<1:0> | T32   | _     | TCS   | _     | 0000          |

| T5CON       | 0120  | TON    | 1                                            | TSIDL  | ı      | -      | _      | _            | _            | _             | TGATE        | TCKPS | S<1:0> | _     | _     | TCS   |       | 0000          |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

TABLE 4-17: I2C1 AND I2C2 REGISTER MAP

| File<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8                     | Bit 7 | Bit 6 | Bit 5     | Bit 4       | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|---------|--------|---------|--------|--------|--------|--------|---------------------------|-------|-------|-----------|-------------|--------------|-------|-------|-------|---------------|

| I2C1RCV      | 0200  | _       | _      | _       | _      | _      | _      | _      | _                         |       |       |           | I2C1 Recei  | ve Register  |       |       |       | 0000          |

| I2C1TRN      | 0202  | -       | _      | -       | _      | _      | _      | _      | -                         |       |       |           | I2C1 Trans  | mit Register |       |       |       | 00FF          |

| I2C1BRG      | 0204  | -       | _      | 1       | -      | _      | _      | -      |                           |       |       | Bau       | d Rate Gene | erator       |       |       |       | 0000          |

| I2C1CON      | 0206  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN                      | GCEN  | STREN | ACKDT     | ACKEN       | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT     | 0208  | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10                     | IWCOL | I2COV | D_A       | Р           | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD      | 020A  | _       | _      | _       | _      | _      | _      |        |                           |       |       | I2C1 Addr | ess Registe | r            |       |       |       | 0000          |

| I2C1MSK      | 020C  | -       | _      | -       | _      | _      | _      |        |                           |       |       | I2C1 Add  | dress Mask  |              |       |       |       | 0000          |

| I2C2RCV      | 0210  | -       | _      | -       | _      | _      | _      | _      | -                         |       |       |           | I2C2 Recei  | ve Register  |       |       |       | 0000          |

| I2C2TRN      | 0212  | -       | _      | -       | _      | _      | _      | _      | -                         |       |       |           | I2C2 Trans  | mit Register |       |       |       | 00FF          |

| I2C2BRG      | 0214  | _       | _      | _       | _      | _      | -      | _      |                           |       |       | Bau       | d Rate Gene | erator       |       |       |       | 0000          |

| I2C2CON      | 0216  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN                      | GCEN  | STREN | ACKDT     | ACKEN       | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT     | 0218  | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10                     | IWCOL | I2COV | D_A       | Р           | S            | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD      | 021A  | _       | _      | 1       | _      | _      | -      |        | I2C2 Address Register 000 |       |       |           |             |              |       |       | 0000  |               |

| I2C2MSK      | 021C  | _       | _      | _       | _      | _      | -      |        | I2C2 Address Mask 00      |       |       |           |             |              |       | 0000  |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-18: UART1 AND UART2 REGISTER MAP

|             |       | . •      |        | ,, <del></del> |        |        |        | _     |                                                         |            |          | _                 | _            |          |      |        |               |      |

|-------------|-------|----------|--------|----------------|--------|--------|--------|-------|---------------------------------------------------------|------------|----------|-------------------|--------------|----------|------|--------|---------------|------|

| SFR<br>Name | Addr. | Bit 15   | Bit 14 | Bit 13         | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0   |            |          |                   |              |          |      |        | All<br>Resets |      |

| U1MODE      | 0220  | UARTEN   | _      | USIDL          | IREN   | RTSMD  | _      | UEN<  | JEN<1:0> WAKE LPBACK ABAUD URXINV BRGH PDSEL<1:0> STSEL |            |          |                   |              |          |      | STSEL  | 0000          |      |

| U1STA       | 0222  | UTXISEL1 | UTXINV | UTXISEL0       | I      | UTXBRK | UTXEN  | UTXBF | TRMT                                                    | URXIS      | SEL<1:0> | ADDEN             | RIDLE        | PERR     | FERR | OERR   | URXDA         | 0110 |

| U1TXREG     | 0224  | _        | -      | _              | I      |        | -      | _     |                                                         |            |          | UART1             | 1 Transmit F | Register |      |        |               | xxxx |

| U1RXREG     | 0226  | _        | -      | _              | ı      |        | _      | _     |                                                         |            |          | UART <sup>2</sup> | 1 Receive R  | tegister |      |        |               | 0000 |

| U1BRG       | 0228  |          |        |                |        |        |        | Baud  | Rate Gen                                                | erator Pre | scaler   |                   |              |          |      |        |               | 0000 |

| U2MODE      | 0230  | UARTEN   | -      | USIDL          | IREN   | RTSMD  | _      | UEN<  | :1:0>                                                   | WAKE       | LPBACK   | ABAUD             | URXINV       | BRGH     | PDSE | L<1:0> | STSEL         | 0000 |

| U2STA       | 0232  | UTXISEL1 | UTXINV | UTXISEL0       | ı      | UTXBRK | UTXEN  | UTXBF | TRMT                                                    | URXIS      | SEL<1:0> | ADDEN             | RIDLE        | PERR     | FERR | OERR   | URXDA         | 0110 |

| U2TXREG     | 0234  | _        | -      | _              | ı      |        | _      | _     | UART2 Transmit Register xxx                             |            |          |                   |              |          |      |        |               | xxxx |

| U2RXREG     | 0236  | _        |        | _              | -      | _      | _      | _     | UART2 Receive Register 000                              |            |          |                   |              |          |      |        | 0000          |      |

| U2BRG       | 0238  |          |        |                |        |        |        | Baud  | Baud Rate Generator Prescaler 0000                      |            |          |                   |              |          |      |        |               |      |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TARIE 1-21. | DEDIDUEDALI | DINI SEI ECT INDI IT I | DECISTED MAD FOD | dsPIC33EPXXXGP50X DEVICES ONLY |

|-------------|-------------|------------------------|------------------|--------------------------------|

| IADLE 4-31. | FERIFIERALI | FIN SELECT INFUT       | REGIOTER WAP FUR | USPICASEPANAGPOUN DEVICES UNLT |

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6        | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|------------|--------|-------|-------|-------|--------------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR0       | 06A0  | _      |        |        |        | INT1R<6:0> |        |       |       | _     | _            | _     | _     | _          | -     | _     | _     | 0000          |

| RPINR1       | 06A2  | 1      | _      | _      | _      | _          | _      | _     | _     | _     |              |       |       | INT2R<6:0> | •     |       |       | 0000          |

| RPINR3       | 06A6  | 1      | _      | _      | _      | _          | _      | _     | _     | _     |              |       | -     | Γ2CKR<6:0  | >     |       |       | 0000          |

| RPINR7       | 06AE  | 1      |        |        |        | IC2R<6:0>  |        |       |       | _     |              |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8       | 06B0  | 1      |        |        |        | IC4R<6:0>  |        |       |       | _     | IC3R<6:0>    |       |       |            |       |       |       |               |

| RPINR11      | 06B6  | 1      | _      | _      | _      | _          | _      | _     | _     | _     | OCFAR<6:0>   |       |       |            |       |       |       |               |

| RPINR18      | 06C4  | _      | _      | _      | _      | _          | _      | _     | _     | _     | U1RXR<6:0>   |       |       |            |       |       |       | 0000          |

| RPINR19      | 06C6  | _      | _      | _      | _      | _          | _      | _     | _     | _     |              |       | ι     | J2RXR<6:0  | >     |       |       | 0000          |

| RPINR22      | 06CC  | _      |        |        | S      | CK2INR<6:0 | )>     |       |       | _     |              |       |       | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23      | 06CE  | _      |        |        |        |            |        |       |       | _     |              |       |       | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26      | 06D4  | _      | _      | _      | _      | _          | _      | _     | _     | _     | - C1RXR<6:0> |       |       |            |       |       | 0000  |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-32: PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File Name | Addr. | Bit 15 | Bit 14       | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6        | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------------|--------|--------|------------|--------|-------|-------|-------|--------------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR0    | 06A0  | _      |              |        |        | INT1R<6:0> |        |       |       | -     | _            | _     | _     | _          | _     | _     | _     | 0000          |

| RPINR1    | 06A2  | -      | ı            | _      | -      | _          | -      | ı     | _     |       |              |       | ļ     | INT2R<6:0> | •     |       |       | 0000          |

| RPINR3    | 06A6  | -      | ı            | _      | -      | _          | -      | ı     | _     |       |              |       | 7     | Γ2CKR<6:0> | >     |       |       | 0000          |

| RPINR7    | 06AE  | -      |              |        |        | IC2R<6:0>  |        |       |       |       |              |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8    | 06B0  | _      |              |        |        | IC4R<6:0>  |        |       |       | ı     |              |       |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11   | 06B6  | _      | -            | _      | -      | -          | I      | ı     | _     | ı     |              |       | (     | OCFAR<6:0  | >     |       |       | 0000          |

| RPINR12   | 06B8  | _      |              |        | ļ      | FLT2R<6:0> | •      |       |       | ı     | FLT1R<6:0>   |       |       |            |       |       |       |               |

| RPINR14   | 06BC  | _      |              |        | (      | QEB1R<6:0> | >      |       |       | I     | QEA1R<6:0>   |       |       |            |       |       |       | 0000          |

| RPINR15   | 06BE  | _      |              |        | Н      | OME1R<6:0  | )>     |       |       | I     | INDX1R<6:0>  |       |       |            |       |       |       | 0000          |

| RPINR18   | 06C4  | _      | -            | _      | -      | -          | I      | ı     | _     | I     | U1RXR<6:0>   |       |       |            |       |       |       | 0000          |

| RPINR19   | 06C6  | _      | -            | _      | -      | -          | I      | ı     | _     | I     |              |       | ι     | J2RXR<6:0  | >     |       |       | 0000          |

| RPINR22   | 06CC  | _      |              |        | S      | CK2INR<6:0 | )>     |       |       | I     |              |       | ;     | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23   | 06CE  | _      | -            | _      | -      | -          | I      | ı     | _     | ı     |              |       |       | SS2R<6:0>  | •     |       |       | 0000          |

| RPINR26   | 06D4  | _      | -            | _      | -      | -          | I      | ı     | _     | ı     |              |       | (     | C1RXR<6:0  | >     |       |       | 0000          |

| RPINR37   | 06EA  | _      |              |        | S      | YNCI1R<6:0 | )>     |       |       | ı     |              |       |       |            |       |       | ı     | 0000          |

| RPINR38   | 06EC  | _      |              |        | Dī     | CMP1R<6:   | 0>     |       |       | _     |              |       |       |            |       |       | 0000  |               |

| RPINR39   | 06EE  | _      | DTCMP3R<6:0> |        |        |            |        |       |       | _     | DTCMP2R<6:0> |       |       |            |       |       | 0000  |               |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

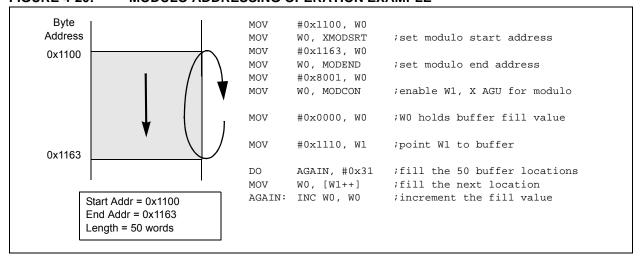

# 4.6 Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

#### 4.6.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified, and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

**Note:** Y space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear).

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

# 4.6.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W register (YWM), to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit is set at MODCON<14>.

FIGURE 4-20: MODULO ADDRESSING OPERATION EXAMPLE

#### REGISTER 7-5: INTCON3: INTERRUPT CONTROL REGISTER 3

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-------|-------|-----|-----|-----|-------|

| _     | _   | DAE   | DOOVR | _   | _   | _   | _     |

| bit 7 |     |       |       |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-6 Unimplemented: Read as '0'

bit 5 DAE: DMA Address Error Soft Trap Status bit

1 = DMA address error soft trap has occurred 0 = DMA address error soft trap has not occurred

bit 4 DOOVR: DO Stack Overflow Soft Trap Status bit

1 = DO stack overflow soft trap has occurred 0 = DO stack overflow soft trap has not occurred

bit 3-0 **Unimplemented:** Read as '0'

# REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   |     | _   | -   | _   |       |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   |     | _   | _   | _   | SGHT  |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-1 **Unimplemented:** Read as '0'

bit 0 SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

#### REGISTER 8-2: DMAXREQ: DMA CHANNEL x IRQ SELECT REGISTER

| R/S-0                | U-0   |

|----------------------|-----|-----|-----|-----|-----|-----|-------|

| FORCE <sup>(1)</sup> | _   | _   | _   | _   | _   | _   | _     |

| bit 15               |     |     |     |     |     |     | bit 8 |

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IRQSEL7 | IRQSEL6 | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | S = Settable bit |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15 **FORCE:** Force DMA Transfer bit<sup>(1)</sup>

1 = Forces a single DMA transfer (Manual mode)

0 = Automatic DMA transfer initiation by DMA request

bit 14-8 **Unimplemented:** Read as '0'

bit 7-0 IRQSEL<7:0>: DMA Peripheral IRQ Number Select bits

01000110 = ECAN1 – TX Data Request<sup>(2)</sup>

00100110 = IC4 - Input Capture 4

00100101 = IC3 - Input Capture 3

00100010 = ECAN1 – RX Data Ready<sup>(2)</sup>

00100001 = SPI2 Transfer Done

00011111 = UART2TX - UART2 Transmitter

00011110 = UART2RX - UART2 Receiver

00011100 = TMR5 - Timer5

00011011 = TMR4 - Timer4

00011010 = OC4 - Output Compare 4

00011001 = OC3 – Output Compare 3

00001101 = ADC1 - ADC1 Convert done

00001100 = UART1TX – UART1 Transmitter 00001011 = UART1RX – UART1 Receiver

OCCUPATION OF THE PROPERTY OF

00001010 = SPI1 – Transfer Done 00001000 = TMR3 – Timer3

00000111 = TMR2 - Timer2

00000110 = OC2 - Output Compare 2

00000101 = IC2 - Input Capture 2

00000010 = OC1 - Output Compare 1

00000001 = IC1 - Input Capture 1

00000000 = INT0 - External Interrupt 0

**Note 1:** The FORCE bit cannot be cleared by user software. The FORCE bit is cleared by hardware when the forced DMA transfer is complete or the channel is disabled (CHEN = 0).

2: This selection is available in dsPIC33EPXXXGP/MC50X devices only.

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRIS setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRIS settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Pin Select registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Pin Select registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

#### 11.6 I/O Ports Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/

Devices.aspx?dDocName=en555464

## 11.6.1 KEY RESOURCES

- "I/O Ports" (DS70598) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

#### 16.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FOSCSEL<6>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring, PWMLOCK = 0.

To gain write access to these locked registers, the user application must write two consecutive values of (0xABCD and 0x4321) to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 16-1.

### **EXAMPLE 16-1: PWMx WRITE-PROTECTED REGISTER UNLOCK SEQUENCE**

```

; FLT32 pin must be pulled low externally in order to clear and disable the fault

; Writing to FCLCON1 register requires unlock sequence

; Load first unlock key to w10 register

; Load second unlock key to w11 register

mov #0xabcd,w10

mov #0x4321,w11

; Load desired value of FCLCON1 register in w0

mov #0x0000,w0

mov w10, PWMKEY

; Write first unlock key to PWMKEY register

mov w11, PWMKEY

; Write second unlock key to PWMKEY register

mov w0,FCLCON1

; Write desired value to FCLCON1 register

; Set PWM ownership and polarity using the IOCON1 register

; Writing to IOCON1 register requires unlock sequence

mov #0xabcd,w10

; Load first unlock key to w10 register

mov #0x4321,w11

; Load second unlock key to wll register

mov #0xF000,w0

; Load desired value of IOCON1 register in w0

mov w10, PWMKEY

; Write first unlock key to PWMKEY register

mov w11, PWMKEY

; Write second unlock key to PWMKEY register

mov w0,IOCON1

; Write desired value to IOCON1 register

```

# 19.1 I<sup>2</sup>C Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note:

In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en555464

#### 19.1.1 KEY RESOURCES

- "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS70330) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

#### REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER

| R-0, HSC | R-0, HSC | U-0 | U-0 | U-0 | R/C-0, HS | R-0, HSC | R-0, HSC |

|----------|----------|-----|-----|-----|-----------|----------|----------|

| ACKSTAT  | TRSTAT   | _   | _   | _   | BCL       | GCSTAT   | ADD10    |

| bit 15   |          |     |     |     |           |          | bit 8    |

| R/C-0, HS | R/C-0, HS | R-0, HSC | R/C-0, HSC | R/C-0, HSC | R-0, HSC | R-0, HSC | R-0, HSC |

|-----------|-----------|----------|------------|------------|----------|----------|----------|

| IWCOL     | I2COV     | D_A      | Р          | S          | R_W      | RBF      | TBF      |

| bit 7     |           |          |            |            |          |          | bit 0    |

| Legend:           | C = Clearable bit | HS = Hardware Settable bit  | HSC = Hardware Settable/Clearable bit |

|-------------------|-------------------|-----------------------------|---------------------------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read | as '0'                                |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared        | x = Bit is unknown                    |

- bit 15 **ACKSTAT:** Acknowledge Status bit (when operating as I<sup>2</sup>C<sup>™</sup> master, applicable to master transmit operation)

- 1 = NACK received from slave

- 0 = ACK received from slave

Hardware is set or clear at the end of slave Acknowledge.

- bit 14 TRSTAT: Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = Master transmit is in progress (8 bits + ACK)

- 0 = Master transmit is not in progress

Hardware is set at the beginning of master transmission. Hardware is clear at the end of slave Acknowledge.

- bit 13-11 Unimplemented: Read as '0'

- bit 10 BCL: Master Bus Collision Detect bit

- 1 = A bus collision has been detected during a master operation

- 0 = No bus collision detected

Hardware is set at detection of a bus collision.

- bit 9 GCSTAT: General Call Status bit

- 1 = General call address was received

- 0 = General call address was not received

Hardware is set when address matches general call address. Hardware is clear at Stop detection.

- bit 8 ADD10: 10-Bit Address Status bit

- 1 = 10-bit address was matched

- 0 = 10-bit address was not matched

Hardware is set at the match of the 2nd byte of the matched 10-bit address. Hardware is clear at Stop detection.

- bit 7 IWCOL: I2Cx Write Collision Detect bit

- 1 = An attempt to write to the I2CxTRN register failed because the I2C module is busy

- 0 = No collision

Hardware is set at the occurrence of a write to I2CxTRN while busy (cleared by software).

- bit 6 I2COV: I2Cx Receive Overflow Flag bit

- 1 = A byte was received while the I2CxRCV register was still holding the previous byte

- 0 = No overflow

Hardware is set at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

- bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was a device address

Hardware is clear at a device address match. Hardware is set by reception of a slave byte.

- bit 4 **P:** Stop bit

- 1 = Indicates that a Stop bit has been detected last

- 0 = Stop bit was not detected last

Hardware is set or clear when a Start, Repeated Start or Stop is detected.

# 21.4 ECAN Control Registers

#### REGISTER 21-1: CxCTRL1: ECANx CONTROL REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-1  | R/W-0  | R/W-0  |

|--------|-----|-------|-------|--------|--------|--------|--------|

| _      | _   | CSIDL | ABAT  | CANCKS | REQOP2 | REQOP1 | REQOP0 |

| bit 15 |     |       |       |        |        |        | bit 8  |

| R-1     | R-0     | R-0     | U-0 | R/W-0  | U-0 | U-0 | R/W-0 |

|---------|---------|---------|-----|--------|-----|-----|-------|

| OPMODE2 | OPMODE1 | OPMODE0 | _   | CANCAP | _   | _   | WIN   |

| bit 7   |         |         |     |        |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13 CSIDL: ECANx Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12 ABAT: Abort All Pending Transmissions bit

1 = Signals all transmit buffers to abort transmission

0 = Module will clear this bit when all transmissions are aborted

bit 11 CANCKS: ECANx Module Clock (FCAN) Source Select bit

1 = FCAN is equal to 2 \* FP

0 = FCAN is equal to FP

bit 10-8 **REQOP<2:0>:** Request Operation Mode bits

111 = Set Listen All Messages mode

110 = Reserved

101 = Reserved

100 = Set Configuration mode

011 = Set Listen Only mode

010 = Set Loopback mode

001 = Set Disable mode

000 = Set Normal Operation mode

bit 7-5 **OPMODE<2:0>**: Operation Mode bits

111 = Module is in Listen All Messages mode

110 = Reserved

101 = Reserved

100 = Module is in Configuration mode

011 = Module is in Listen Only mode

010 = Module is in Loopback mode

001 = Module is in Disable mode

000 = Module is in Normal Operation mode

bit 4 Unimplemented: Read as '0'

bit 3 CANCAP: CAN Message Receive Timer Capture Event Enable bit

1 = Enables input capture based on CAN message receive

0 = Disables CAN capture

bit 2-1 **Unimplemented:** Read as '0'

bit 0 WIN: SFR Map Window Select bit

1 = Uses filter window

0 = Uses buffer window

# REGISTER 21-16: CxRXFnSID: ECANx ACCEPTANCE FILTER n STANDARD IDENTIFIER REGISTER (n = 0-15)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| SID10  | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-x | R/W-x | R/W-x | U-0 | R/W-x | U-0 | R/W-x | R/W-x |

|-------|-------|-------|-----|-------|-----|-------|-------|

| SID2  | SID1  | SID0  | _   | EXIDE | _   | EID17 | EID16 |

| bit 7 |       |       |     |       |     |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-5 SID<10:0>: Standard Identifier bits

1 = Message address bit, SIDx, must be '1' to match filter 0 = Message address bit, SIDx, must be '0' to match filter

bit 4 Unimplemented: Read as '0'

bit 3 **EXIDE:** Extended Identifier Enable bit

If MIDE = 1:

1 = Matches only messages with Extended Identifier addresses0 = Matches only messages with Standard Identifier addresses

If MIDE = 0:

Ignores EXIDE bit.

bit 2 Unimplemented: Read as '0'

bit 1-0 **EID<17:16>:** Extended Identifier bits

1 = Message address bit, EIDx, must be '1' to match filter 0 = Message address bit, EIDx, must be '0' to match filter

#### REGISTER 25-7: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

| U-0    | R/W-0                 | U-0 | U-0 | U-0 | R/W-0   | U-0 | U-0   |

|--------|-----------------------|-----|-----|-----|---------|-----|-------|

| _      | CVR20E <sup>(1)</sup> | _   | _   | _   | VREFSEL | _   | _     |

| bit 15 |                       |     |     |     |         |     | bit 8 |

| R/W-0 | R/W-0                 | R/W-0 | R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----------------------|-------|----------------------|-------|-------|-------|-------|

| CVREN | CVR10E <sup>(1)</sup> | CVRR  | CVRSS <sup>(2)</sup> | CVR3  | CVR2  | CVR1  | CVR0  |

| bit 7 |                       |       |                      |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 Unimplemented: Read as '0'

bit 14 CVR20E: Comparator Voltage Reference 2 Output Enable bit<sup>(1)</sup>

1 = (AVDD – AVSS)/2 is connected to the CVREF20 pin 0 = (AVDD – AVSS)/2 is disconnected from the CVREF20 pin

bit 13-11 **Unimplemented:** Read as '0'

bit 10 VREFSEL: Comparator Voltage Reference Select bit

1 = CVREFIN = VREF+

0 = CVREFIN is generated by the resistor network

bit 9-8 Unimplemented: Read as '0'

bit 7 **CVREN:** Comparator Voltage Reference Enable bit

1 = Comparator voltage reference circuit is powered on0 = Comparator voltage reference circuit is powered down

bit 6 **CVR10E**: Comparator Voltage Reference 1 Output Enable bit<sup>(1)</sup>

1 = Voltage level is output on the CVREF10 pin

0 = Voltage level is disconnected from then CVREF10 pin

bit 5 CVRR: Comparator Voltage Reference Range Selection bit

1 = CVRSRC/24 step-size

0 = CVRSRC/32 step-size

bit 4 **CVRSS:** Comparator Voltage Reference Source Selection bit<sup>(2)</sup>

1 = Comparator voltage reference source, CVRSRC = (VREF+) - (AVSS)

0 = Comparator voltage reference source, CVRSRC = AVDD - AVSS

bit 3-0 CVR<3:0> Comparator Voltage Reference Value Selection 0 ≤ CVR<3:0> ≤ 15 bits

When CVRR = 1:

CVREFIN = (CVR<3:0>/24) • (CVRSRC)

When CVRR = 0:

CVREFIN = (CVRSRC/4) + (CVR<3:0>/32) • (CVRSRC)

Note 1: CVRxOE overrides the TRISx and the ANSELx bit settings.

2: In order to operate with CVRSS = 1, at least one of the comparator modules must be enabled.

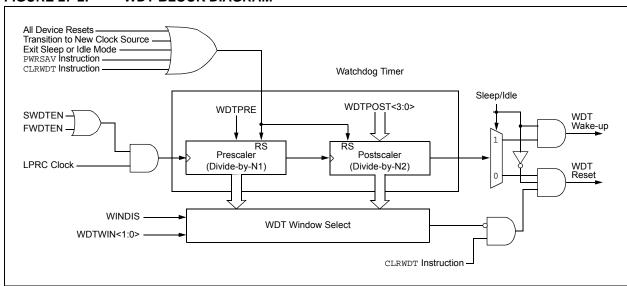

# 27.5 Watchdog Timer (WDT)

For dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

#### 27.5.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a WDT Timeout period (TWDT), as shown in Parameter SY12 in Table 30-22.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

#### 27.5.2 SLEEP AND IDLE MODES

If the WDT is enabled, it continues to run during Sleep or Idle modes. When the WDT time-out occurs, the device wakes the device and code execution continues from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bit (RCON<3,2>) needs to be cleared in software after the device wakes up.

#### 27.5.3 ENABLING WDT

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

#### 27.5.4 WDT WINDOW

The Watchdog Timer has an optional Windowed mode, enabled by programming the WINDIS bit in the WDT Configuration register (FWDT<6>). In the Windowed mode (WINDIS = 0), the WDT should be cleared based on the settings in the programmable Watchdog Timer Window select bits (WDTWIN<1:0>).

### FIGURE 27-2: WDT BLOCK DIAGRAM

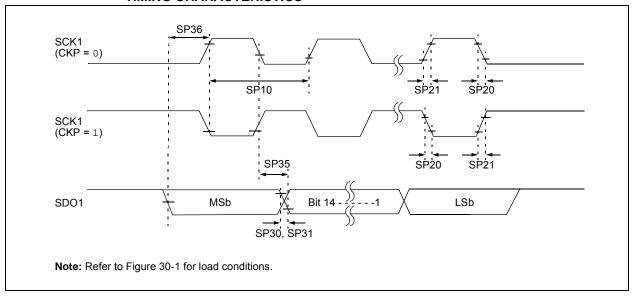

FIGURE 30-23: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 1) TIMING CHARACTERISTICS

TABLE 30-42: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                           | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |                     |      |       |                             |  |

|--------------------|-----------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------|--|

| Param.             | Symbol                | Symbol Characteristic <sup>(1)</sup>      |                                                                                                                                                                                                                                                  | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |  |

| SP10               | FscP                  | Maximum SCK1 Frequency                    | _                                                                                                                                                                                                                                                | _                   | 15   | MHz   | (Note 3)                    |  |

| SP20               | TscF                  | SCK1 Output Fall Time                     | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP21               | TscR                  | SCK1 Output Rise Time                     | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                | _                                                                                                                                                                                                                                                |                     | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after SCK1 Edge    | _                                                                                                                                                                                                                                                | 6                   | 20   | ns    |                             |  |

| SP36               | TdiV2scH,<br>TdiV2scL | SDO1 Data Output Setup to First SCK1 Edge | 30                                                                                                                                                                                                                                               | _                   | _    | ns    |                             |  |

- **Note 1:** These parameters are characterized, but are not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- 3: The minimum clock period for SCK1 is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI1 pins.

TABLE 30-48: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0)

TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                            |              |                     |      |       |                             |  |

|--------------------|-----------------------|--------------------------------------------|--------------|---------------------|------|-------|-----------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>              | Min.         | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |  |

| SP70               | FscP                  | Maximum SCK1 Input Frequency               | _            | _                   | 11   | MHz   | (Note 3)                    |  |

| SP72               | TscF                  | SCK1 Input Fall Time                       | _            | _                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP73               | TscR                  | SCK1 Input Rise Time                       | _            | _                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                 | _            | _                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                 | _            | _                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge  | _            | 6                   | 20   | ns    |                             |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to First SCK1 Edge  | 30           | _                   | _    | ns    |                             |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge | 30           | _                   | _    | ns    |                             |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge  | 30           | _                   | _    | ns    |                             |  |

| SP50               | TssL2scH,<br>TssL2scL | SS1 ↓ to SCK1 ↑ or SCK1 ↓ Input            | 120          | _                   | _    | ns    |                             |  |

| SP51               | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance     | 10           | _                   | 50   | ns    | (Note 4)                    |  |

| SP52               | TscH2ssH,<br>TscL2ssH | SS1 ↑ after SCK1 Edge                      | 1.5 Tcy + 40 | _                   | _    | ns    | (Note 4)                    |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

- **2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK1 is 91 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

- 4: Assumes 50 pF load on all SPI1 pins.