Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuns                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                    |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 4K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc506-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X PRODUCT FAMILIES

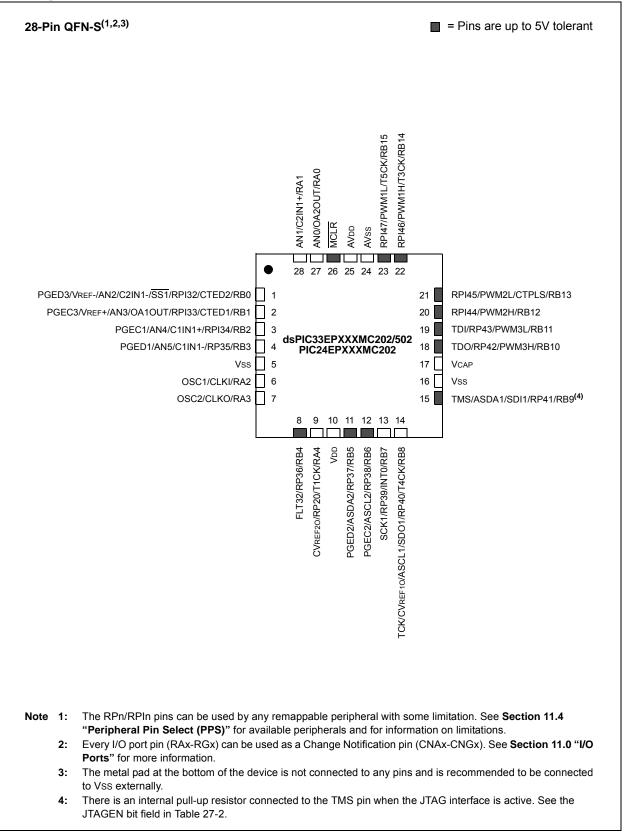

The device names, pin counts, memory sizes and peripheral availability of each device are listed in Table 1 (General Purpose Families) and Table 2 (Motor Control Families). Their pinout diagrams appear on the following pages.

|                   | â                              | (se                           |             |                      | Rei           | nappa          | ble Pe | eriphe             | rals                          |                                    |      |               |                              |                     |      |     |          |           |                                |

|-------------------|--------------------------------|-------------------------------|-------------|----------------------|---------------|----------------|--------|--------------------|-------------------------------|------------------------------------|------|---------------|------------------------------|---------------------|------|-----|----------|-----------|--------------------------------|

| Device            | Page Erase Size (Instructions) | Program Flash Memory (Kbytes) | RAM (Kbyte) | 16-Bit/32-Bit Timers | Input Capture | Output Compare | UART   | SPI <sup>(2)</sup> | ECAN <sup>TM</sup> Technology | External Interrupts <sup>(3)</sup> | I²C™ | CRC Generator | 10-Bit/12-Bit ADC (Channels) | Op Amps/Comparators | CTMU | РТС | I/O Pins | Pins      | Packages                       |

| PIC24EP32GP202    | 512                            | 32                            | 4           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           |                                |

| PIC24EP64GP202    | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           | SPDIP,                         |

| PIC24EP128GP202   | 1024                           | 128                           | 16          | 5                    | 4             | 4              | 2      | 2                  | —                             | 3                                  | 2    | 1             | 6                            | 2/3(1)              | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(4)</sup> , |

| PIC24EP256GP202   | 1024                           | 256                           | 32          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           | QFN-S                          |

| PIC24EP512GP202   | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           |                                |

| PIC24EP32GP203    | 512                            | 32                            | 4           | 5                    | 4             | 4              | 2      | 2                  |                               | 3                                  | 2    | 1             | 8                            | 3/4                 | Vaa  | Vaa | 25       | 36        | VTLA                           |

| PIC24EP64GP203    | 1024                           | 64                            | 8           | 5                    | 4             | 4              | 2      | 2                  | _                             | 3                                  | 2    |               | 0                            | 3/4                 | Yes  | Yes | 25       | 30        | VILA                           |

| PIC24EP32GP204    | 512                            | 32                            | 4           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           |                                |

| PIC24EP64GP204    | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           | VTLA <sup>(4)</sup> ,          |

| PIC24EP128GP204   | 1024                           | 128                           | 16          | 5                    | 4             | 4              | 2      | 2                  | _                             | 3                                  | 2    | 1             | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,                  |

| PIC24EP256GP204   | 1024                           | 256                           | 32          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          | 40        | UQFN                           |

| PIC24EP512GP204   | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           |                                |

| PIC24EP64GP206    | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           |                                |

| PIC24EP128GP206   | 1024                           | 128                           | 16          | _                    |               |                |        |                    |                               |                                    | -    |               |                              | ~ ~ ~               |      |     |          | ~ /       | TQFP.                          |

| PIC24EP256GP206   | 1024                           | 256                           | 32          | 5                    | 4             | 4              | 2      | 2                  | _                             | 3                                  | 2    | 1             | 16                           | 3/4                 | Yes  | Yes | 53       | 64        | QFN                            |

| PIC24EP512GP206   | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP32GP502  | 512                            | 32                            | 4           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP64GP502  | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           | SPDIP,                         |

| dsPIC33EP128GP502 | 1024                           | 128                           | 16          | 5                    | 4             | 4              | 2      | 2                  | 1                             | 3                                  | 2    | 1             | 6                            | 2/3(1)              | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(4)</sup> . |

| dsPIC33EP256GP502 | 1024                           | 256                           | 32          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           | QFN-S                          |

| dsPIC33EP512GP502 | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP32GP503  | 512                            | 32                            | 4           | _                    | _             | _              | _      | _                  |                               | _                                  | _    |               | _                            |                     |      |     |          |           |                                |

| dsPIC33EP64GP503  | 1024                           | 64                            | 8           | 5                    | 4             | 4              | 2      | 2                  | 1                             | 3                                  | 2    | 1             | 8                            | 3/4                 | Yes  | Yes | 25       | 36        | VTLA                           |

| dsPIC33EP32GP504  | 512                            | 32                            | 4           |                      |               |                |        |                    |                               |                                    |      |               |                              | İ                   |      |     |          |           |                                |

| dsPIC33EP64GP504  | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           | VTLA <sup>(4)</sup> ,          |

| dsPIC33EP128GP504 | 1024                           | 128                           | 16          | 5                    | 4             | 4              | 2      | 2                  | 1                             | 3                                  | 2    | 1             | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,                  |

| dsPIC33EP256GP504 | 1024                           | 256                           | 32          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          | 40        | UQFN,<br>UQFN                  |

| dsPIC33EP512GP504 | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP64GP506  | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              | 1                   |      |     |          |           |                                |

| dsPIC33EP128GP506 | 1024                           | 128                           | 16          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           | TQFP,                          |

| dsPIC33EP256GP506 | 1024                           | 256                           | 32          | 5                    | 4             | 4              | 2      | 2                  | 1                             | 3                                  | 2    | 1             | 16                           | 3/4                 | Yes  | Yes | 53       | 64        | QFN                            |

| dsPIC33EP512GP506 | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           |                                |

|                   |                                | 1                             |             |                      |               | 1              | 1      | 1                  |                               |                                    | 1    | 1             | 1                            |                     |      |     |          |           |                                |

## TABLE 1: dsPIC33EPXXXGP50X and PIC24EPXXXGP20X GENERAL PURPOSE FAMILIES

Note 1: On 28-pin devices, Comparator 4 does not have external connections. Refer to Section 25.0 "Op Amp/Comparator Module" for details.

Only SPI2 is remappable.

INT0 is not remappable.

4: The SSOP and VTLA packages are not available for devices with 512 Kbytes of memory.

# Pin Diagrams (Continued)

# 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for digital signal processing. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

# 3.1 Registers

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can act as a data, address or address offset register. The 16th working register (W15) operates as a Software Stack Pointer for interrupts and calls.

# 3.2 Instruction Set

The instruction set for dsPIC33EPXXXGP50X and dsPIC33EPXXXMC20X/50X devices has two classes of instructions: the MCU class of instructions and the DSP class of instructions. The instruction set for PIC24EPXXXGP/MC20X devices has the MCU class of instructions only and does not support DSP instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

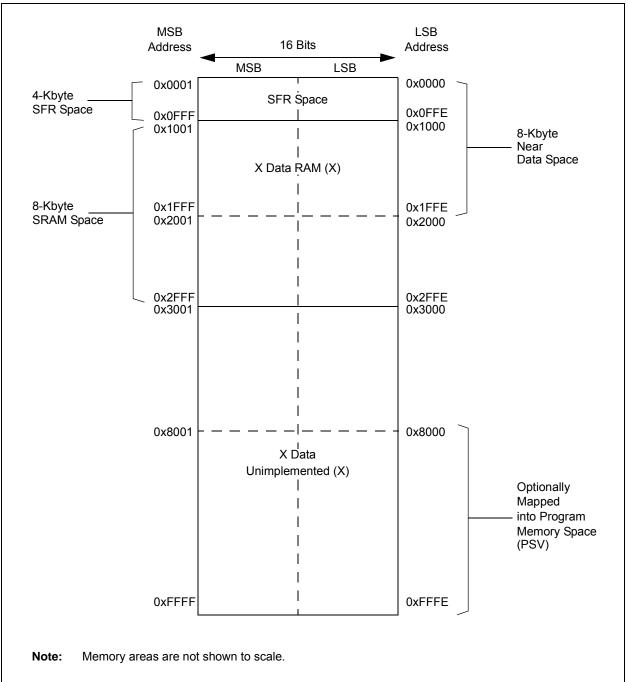

# 3.3 Data Space Addressing

The base Data Space can be addressed as 64 Kbytes (32K words).

The Data Space includes two ranges of memory, referred to as X and Y data memory. Each memory range is accessible through its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. On dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Spaces have memory locations that are device-specific, and are described further in the data memory maps in **Section 4.2 "Data Address Space"**.

The upper 32 Kbytes of the Data Space memory map can optionally be mapped into Program Space (PS) at any 32-Kbyte aligned program word boundary. The Program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Moreover, the Base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space (EDS) address. The EDS can be addressed as 8M words or 16 Mbytes. Refer to the "**Data Memory**" (DS70595) and "**Program Memory**" (DS70613) sections in the "*dsPIC33/PIC24 Family Reference Manual*" for more details on EDS, PSV and table accesses.

On the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data re-ordering for radix-2 FFT algorithms. PIC24EPXXXGP/MC20X devices do not support Modulo and Bit-Reversed Addressing.

# 3.4 Addressing Modes

The CPU supports these addressing modes:

- Inherent (no operand)

- Relative

- Literal

- · Memory Direct

- Register Direct

- Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

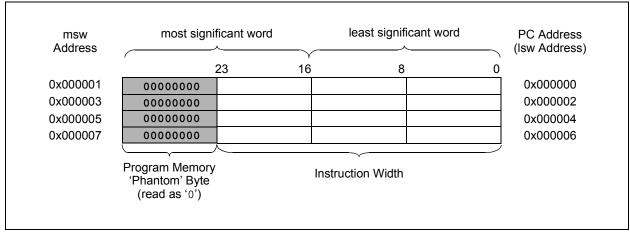

## 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-6).

Program memory addresses are always word-aligned on the lower word and addresses are incremented, or decremented by two, during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

# 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices reserve the addresses between 0x000000 and 0x000200 for hardcoded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of Flash memory, with the actual address for the start of code at address, 0x000002, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in **Section 7.1** "Interrupt Vector Table".

## FIGURE 4-6: PROGRAM MEMORY ORGANIZATION

## 4.2.5 X AND Y DATA SPACES

# The dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X core has two Data Spaces, X and Y. These Data Spaces can be considered either separate (for some DSP instructions) or as one unified linear address range (for MCU instructions). The Data Spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X Data Space is used by all instructions and supports all addressing modes. X Data Space has separate read and write data buses. The X read data bus is the read data path for all instructions that view Data Space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y Data Space is used in concert with the X Data Space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y Data Spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X Data Space. Modulo Addressing and Bit-Reversed Addressing are not present in PIC24EPXXXGP/MC20X devices.

All data memory writes, including in DSP instructions, view Data Space as combined X and Y address space. The boundary between the X and Y Data Spaces is device-dependent and is not user-programmable.

# 4.3 Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

## 4.3.1 KEY RESOURCES

- "Program Memory" (DS70613) in the "dsPIC33/ PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

# TABLE 4-39: PMD REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   |        |       |       | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  |        | _      | _      | -      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  |       |       | CRCMD  | _     | —     | —      |        | —      | I2C2MD |       | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      |       |       | _      | _     | —     | —      | REFOMD | CTMUMD |        |       | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      |        |       |       | _      |       | —     | —      |        | —      |        |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |       |       |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIND/        | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | —     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-40: PMD REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | _      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  | _      | —      | —      | —      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | —     | —     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      | —      |        | _      | _      | PWM3MD | PWM2MD | PWM1MD | —      |       |       | _      | —      |        | —      | -     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | —      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 95

## TABLE 4-42: OP AMP/COMPARATOR REGISTER MAP

| File Name                | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8 | Bit 7 | Bit 6  | Bit 5    | Bit 4 | Bit 3   | Bit 2  | Bit 1     | Bit 0 | All<br>Resets |

|--------------------------|-------|--------|--------|--------|--------|--------|---------|---------|-------|-------|--------|----------|-------|---------|--------|-----------|-------|---------------|

| CMSTAT                   | 0A80  | PSIDL  | _      | -      | —      | C4EVT  | C3EVT   | C2EVT   | C1EVT | _     | -      | —        | —     | C4OUT   | C3OUT  | C2OUT     | C10UT | 0000          |

| CVRCON                   | 0A82  |        | CVR2OE | _      | _      | _      | VREFSEL | _       | _     | CVREN | CVR10E | CVRR     | CVRSS |         | CVR<   | 3:0>      |       | 0000          |

| CM1CON                   | 0A84  | CON    | COE    | CPOL   | _      | _      | OPMODE  | CEVT    | COUT  | EVPOL | _<1:0> | _        | CREF  | _       | _      | CCH       | <1:0> | 0000          |

| CM1MSKSRC                | 0A86  |        | _      | _      | _      |        | SELSR   | CC<3:0> |       |       | SELSRC | B<3:0>   |       |         | SELSRC | A<3:0>    |       | 0000          |

| CM1MSKCON                | 0A88  | HLMS   | _      | OCEN   | OCNEN  | OBEN   | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN | ABEN    | ABNEN  | AAEN      | AANEN | 0000          |

| CM1FLTR                  | 0A8A  |        | _      | _      | _      | _      | _       | _       | _     | _     | C      | FSEL<2:0 | >     | CFLTREN | (      | CFDIV<2:0 | >     | 0000          |

| CM2CON                   | 0A8C  | CON    | COE    | CPOL   | _      | _      | OPMODE  | CEVT    | COUT  | EVPOL | _<1:0> | _        | CREF  | _       | _      | CCH       | <1:0> | 0000          |

| CM2MSKSRC                | 0A8E  |        | _      | _      | _      |        | SELSR   | CC<3:0> |       |       | SELSRC | B<3:0>   |       |         | SELSRC | A<3:0>    |       | 0000          |

| CM2MSKCON                | 0A90  | HLMS   | _      | OCEN   | OCNEN  | OBEN   | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN | ABEN    | ABNEN  | AAEN      | AANEN | 0000          |

| CM2FLTR                  | 0A92  | _      | _      | _      | _      | _      | _       | _       | _     |       | C      | FSEL<2:0 | >     | CFLTREN | (      | CFDIV<2:0 | >     | 0000          |

| CM3CON <sup>(1)</sup>    | 0A94  | CON    | COE    | CPOL   | _      | _      | OPMODE  | CEVT    | COUT  | EVPOL | _<1:0> | _        | CREF  | _       | _      | CCH       | <1:0> | 0000          |

| CM3MSKSRC(1)             | 0A96  | _      | _      | _      | _      |        | SELSR   | CC<3:0> |       |       | SELSRC | B<3:0>   |       |         | SELSRC | A<3:0>    |       | 0000          |

| CM3MSKCON <sup>(1)</sup> | 0A98  | HLMS   | _      | OCEN   | OCNEN  | OBEN   | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN | ABEN    | ABNEN  | AAEN      | AANEN | 0000          |

| CM3FLTR <sup>(1)</sup>   | 0A9A  | _      | _      | _      | _      | _      | _       | _       | _     |       | C      | FSEL<2:0 | >     | CFLTREN | (      | CFDIV<2:0 | >     | 0000          |

| CM4CON                   | 0A9C  | CON    | COE    | CPOL   | _      | _      | _       | CEVT    | COUT  | EVPOL | _<1:0> | _        | CREF  | _       | _      | CCH       | <1:0> | 0000          |

| CM4MSKSRC                | 0A9E  | _      | _      |        | _      |        | SELSR   | CC<3:0> | -     |       | SELSRC | B<3:0>   | •     |         | SELSRC | A<3:0>    |       | 0000          |

| CM4MSKCON                | 0AA0  | HLMS   | _      | OCEN   | OCNEN  | OBEN   | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN | ABEN    | ABNEN  | AAEN      | AANEN | 0000          |

| CM4FLTR                  | 0AA2  | _      | _      |        | _      | _      | _       | _       | _     | —     | C      | FSEL<2:0 | >     | CFLTREN | (      | CFDIV<2:0 | >     | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These registers are unavailable on dsPIC33EPXXXGP502/MC502/MC502/MC202 and PIC24EP256GP/MC202 (28-pin) devices.

## TABLE 4-43: CTMU REGISTER MAP

| File N | lame | Addr. | Bit 15  | Bit 14  | Bit 13   | Bit 12 | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7   | Bit 6   | Bit 5 | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------|------|-------|---------|---------|----------|--------|----------|----------|----------|----------|---------|---------|-------|-------|---------|-------|-------|-------|---------------|

| CTMUC  | CON1 | 033A  | CTMUEN  | —       | CTMUSIDL | TGEN   | EDGEN    | EDGSEQEN | IDISSEN  | CTTRIG   | _       | _       | _     | _     | _       | _     | _     | _     | 0000          |

| CTMUC  | CON2 | 033C  | EDG1MOD | EDG1POL |          | EDG1   | SEL<3:0> |          | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL |       | EDG2S | EL<3:0> |       | _     | -     | 0000          |

| CTMU   | ICON | 033E  |         |         | ITRIM<5  | 5:0>   |          |          | IRNG     | <1:0>    |         | _       | _     | _     | _       | _     | -     | _     | 0000          |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-44: JTAG INTERFACE REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7  | Bit 6  | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|--------|--------|--------|---------|-------|-------|-------|-------|-------|---------------|

| JDATAH    | 0FF0 | _      | —      | _      | _      |        |        |       |        |        | JDATAH | <27:16> |       |       |       |       |       | xxxx          |

| JDATAL    | 0FF2 |        |        |        |        |        |        |       | JDATAL | <15:0> |        |         |       |       |       |       |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 97

# 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions. which apply to dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

## 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

# 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

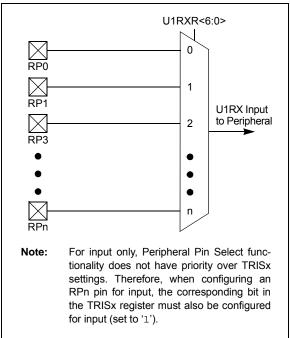

## 11.4.4 INPUT MAPPING

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-17). Each register contains sets of 7-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 7-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

For example, Figure 11-2 illustrates remappable pin selection for the U1RX input.

#### FIGURE 11-2: REMAPPABLE INPUT FOR U1RX

## 11.4.4.1 Virtual Connections

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices support virtual (internal) connections to the output of the op amp/ comparator module (see Figure 25-1 in Section 25.0 "Op Amp/Comparator Module"), and the PTG module (see Section 24.0 "Peripheral Trigger Generator (PTG) Module").

In addition, dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support virtual connections to the filtered QEI module inputs: FINDX1, FHOME1, FINDX2 and FHOME2 (see Figure 17-1 in Section 17.0 "Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)".

Virtual connections provide a simple way of interperipheral connection without utilizing a physical pin. For example, by setting the FLT1R<6:0> bits of the RPINR12 register to the value of `b0000001, the output of the analog comparator, C1OUT, will be connected to the PWM Fault 1 input, which allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

Virtual connection to the QEI module allows peripherals to be connected to the QEI digital filter input. To utilize this filter, the QEI module must be enabled and its inputs must be connected to a physical RPn pin. Example 11-2 illustrates how the input capture module can be connected to the QEI digital filter.

# EXAMPLE 11-2: CONNECTING IC1 TO THE HOME1 QEI1 DIGITAL FILTER INPUT ON PIN 43 OF THE dsPIC33EPXXXMC206 DEVICE

| RPINR15 = 0x2500; | /* Connect the QEI1 HOME1 input to RP37 (pin 43) */                   |

|-------------------|-----------------------------------------------------------------------|

| RPINR7 = 0x009;   | /* Connect the IC1 input to the digital filter on the FHOME1 input */ |

| QEI1IOC = 0x4000; | /* Enable the QEI digital filter */                                   |

| QEI1CON = 0x8000; | /* Enable the QEI module */                                           |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                         | U-0                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                            | U-0                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                               | R/W-0            | R/W-0             | R/W-0         |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------|-------------------|---------------|

| _                           | _                                                                                                                                                                                                          | _                                                                                                                                                                                                                                              | —                                                                                                                                                                                                                                                                                                                                                                                            | BLANKSEL3                                                                                           | BLANKSEL2        | BLANKSEL1         | BLANKSEL      |

| bit 15                      | •                                                                                                                                                                                                          | •                                                                                                                                                                                                                                              | •                                                                                                                                                                                                                                                                                                                                                                                            | •                                                                                                   |                  | •                 | bit 8         |

| U-0                         | U-0                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0                                                                                               | R/W-0            | R/W-0             | R/W-0         |

|                             |                                                                                                                                                                                                            | CHOPSEL3                                                                                                                                                                                                                                       | CHOPSEL2                                                                                                                                                                                                                                                                                                                                                                                     | CHOPSEL1                                                                                            | CHOPSEL0         | CHOPHEN           | CHOPLEN       |

| bit 7                       |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                     |                  | onornen           | bit           |

|                             |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                     |                  |                   |               |

| Legend:                     |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                     |                  | (0)               |               |

| R = Readab                  |                                                                                                                                                                                                            | W = Writable                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                              | -                                                                                                   | ented bit, read  |                   |               |

| -n = Value a                | at POR                                                                                                                                                                                                     | '1' = Bit is set                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                              | '0' = Bit is clea                                                                                   | red              | x = Bit is unkr   | nown          |

| bit 15-12                   | Unimplemen                                                                                                                                                                                                 | ted: Read as '                                                                                                                                                                                                                                 | D'                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                     |                  |                   |               |

| bit 11-8                    | -                                                                                                                                                                                                          |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                              | urce Select bits                                                                                    |                  |                   |               |

|                             | The selected                                                                                                                                                                                               | state blank sig                                                                                                                                                                                                                                | nal will block t                                                                                                                                                                                                                                                                                                                                                                             | he current-limit                                                                                    | and/or Fault inp | out signals (if e | nabled via th |

|                             | BCH and BCI                                                                                                                                                                                                | L bits in the LEI                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                     | ·                | 5 (               |               |

|                             | 1001 <b>= Rese</b>                                                                                                                                                                                         | rved                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                     |                  |                   |               |

|                             | •                                                                                                                                                                                                          |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                     |                  |                   |               |

|                             |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                     |                  |                   |               |

|                             | •                                                                                                                                                                                                          |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                     |                  |                   |               |

|                             | •<br>•<br>• 0100 = Rese                                                                                                                                                                                    | rved                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                     |                  |                   |               |

|                             | •<br>•<br>0100 = Rese<br>0011 = PWM                                                                                                                                                                        | rved<br>3H selected as                                                                                                                                                                                                                         | state blank so                                                                                                                                                                                                                                                                                                                                                                               | ource                                                                                               |                  |                   |               |

|                             | 0011 = PWM<br>0010 = PWM                                                                                                                                                                                   | 3H selected as 2H selected as                                                                                                                                                                                                                  | state blank so                                                                                                                                                                                                                                                                                                                                                                               | ource                                                                                               |                  |                   |               |

|                             | 0011 = PWM<br>0010 = PWM<br>0001 = PWM                                                                                                                                                                     | 3H selected as<br>2H selected as<br>1H selected as                                                                                                                                                                                             | state blank so                                                                                                                                                                                                                                                                                                                                                                               | ource                                                                                               |                  |                   |               |

| hit 7-6                     | 0011 = PWM<br>0010 = PWM<br>0001 = PWM<br>0000 = No st                                                                                                                                                     | 3H selected as<br>2H selected as<br>1H selected as<br>ate blanking                                                                                                                                                                             | state blank so<br>state blank so                                                                                                                                                                                                                                                                                                                                                             | ource                                                                                               |                  |                   |               |

|                             | 0011 = PWM<br>0010 = PWM<br>0001 = PWM<br>0000 = No st<br>Unimplemen                                                                                                                                       | 3H selected as<br>2H selected as<br>1H selected as<br>ate blanking<br>ted: Read as '                                                                                                                                                           | state blank so<br>state blank so<br>o'                                                                                                                                                                                                                                                                                                                                                       | burce<br>burce                                                                                      |                  |                   |               |

|                             | 0011 = PWM<br>0010 = PWM<br>0001 = PWM<br>0000 = No st<br>Unimplemen<br>CHOPSEL<3                                                                                                                          | 3H selected as<br>2H selected as<br>1H selected as<br>ate blanking<br>ted: Read as '(<br>:0>: PWMx Ch<br>signal will enab                                                                                                                      | state blank so<br>state blank so<br>o'<br>op Clock Sour                                                                                                                                                                                                                                                                                                                                      | burce<br>burce                                                                                      | elected PWMx o   | putputs.          |               |

|                             | 0011 = PWM<br>0010 = PWM<br>0001 = PWM<br>0000 = No st<br>Unimplemen<br>CHOPSEL<3<br>The selected                                                                                                          | 3H selected as<br>2H selected as<br>1H selected as<br>ate blanking<br>ted: Read as '(<br>:0>: PWMx Ch<br>signal will enab                                                                                                                      | state blank so<br>state blank so<br>o'<br>op Clock Sour                                                                                                                                                                                                                                                                                                                                      | burce<br>burce<br>rce Select bits                                                                   | elected PWMx o   | putputs.          |               |

|                             | 0011 = PWM<br>0010 = PWM<br>0001 = PWM<br>0000 = No st<br>Unimplemen<br>CHOPSEL<3<br>The selected                                                                                                          | 3H selected as<br>2H selected as<br>1H selected as<br>ate blanking<br>ted: Read as '(<br>:0>: PWMx Ch<br>signal will enab                                                                                                                      | state blank so<br>state blank so<br>o'<br>op Clock Sour                                                                                                                                                                                                                                                                                                                                      | burce<br>burce<br>rce Select bits                                                                   | elected PWMx o   | outputs.          |               |

|                             | 0011 = PWM<br>0010 = PWM<br>0001 = PWM<br>0000 = No st<br>Unimplemen<br>CHOPSEL<3<br>The selected                                                                                                          | 3H selected as<br>2H selected as<br>1H selected as<br>ate blanking<br>ted: Read as '(<br>:0>: PWMx Ch<br>signal will enab                                                                                                                      | state blank so<br>state blank so<br>o'<br>op Clock Sour                                                                                                                                                                                                                                                                                                                                      | burce<br>burce<br>rce Select bits                                                                   | elected PWMx o   | outputs.          |               |

|                             | 0011 = PWM<br>0010 = PWM<br>0001 = PWM<br>0000 = No st<br>Unimplemen<br>CHOPSEL<3<br>The selected<br>1001 = Rese                                                                                           | 3H selected as<br>2H selected as<br>1H selected as<br>ate blanking<br>ted: Read as '(<br>:0>: PWMx Ch<br>signal will enab<br>rved                                                                                                              | state blank so<br>state blank so<br>o'<br>op Clock Sour<br>ole and disable                                                                                                                                                                                                                                                                                                                   | ource<br>ource<br>rce Select bits<br>e (CHOP) the se                                                | elected PWMx o   | putputs.          |               |

|                             | 0011 = PWM<br>0010 = PWM<br>0001 = PWM<br>0000 = No st<br>Unimplemen<br>CHOPSEL<3<br>The selected<br>1001 = Rese                                                                                           | 3H selected as<br>2H selected as<br>1H selected as<br>ate blanking<br>ted: Read as '0<br>:0>: PWMx Ch<br>signal will enab<br>rved<br>rved<br>3H selected as                                                                                    | state blank so<br>state blank so<br>op Clock Sour<br>ole and disable                                                                                                                                                                                                                                                                                                                         | ource<br>ource<br>rce Select bits<br>e (CHOP) the se<br>source                                      | elected PWMx o   | outputs.          |               |

|                             | 0011 = PWM<br>0010 = PWM<br>0001 = PWM<br>0000 = No st<br>Unimplemen<br>CHOPSEL<3<br>The selected<br>1001 = Rese                                                                                           | 3H selected as<br>2H selected as<br>1H selected as<br>ate blanking<br>ted: Read as '(<br>:0>: PWMx Ch<br>signal will enab<br>rved<br>3H selected as<br>2H selected as                                                                          | state blank so<br>state blank so<br>op Clock Sour<br>ole and disable<br>CHOP clock                                                                                                                                                                                                                                                                                                           | source<br>source                                                                                    | elected PWMx o   | outputs.          |               |

|                             | 0011 = PWM<br>0010 = PWM<br>0001 = PWM<br>0000 = No st<br>Unimplemen<br>CHOPSEL<3<br>The selected<br>1001 = Rese<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | 3H selected as<br>2H selected as<br>1H selected as<br>ate blanking<br>ted: Read as '(<br>:0>: PWMx Ch<br>signal will enab<br>rved<br>3H selected as<br>2H selected as<br>1H selected as                                                        | state blank so<br>state blank so<br>op Clock Sour<br>ole and disable<br>CHOP clock s<br>CHOP clock s<br>CHOP clock s                                                                                                                                                                                                                                                                         | source<br>source                                                                                    |                  | outputs.          |               |

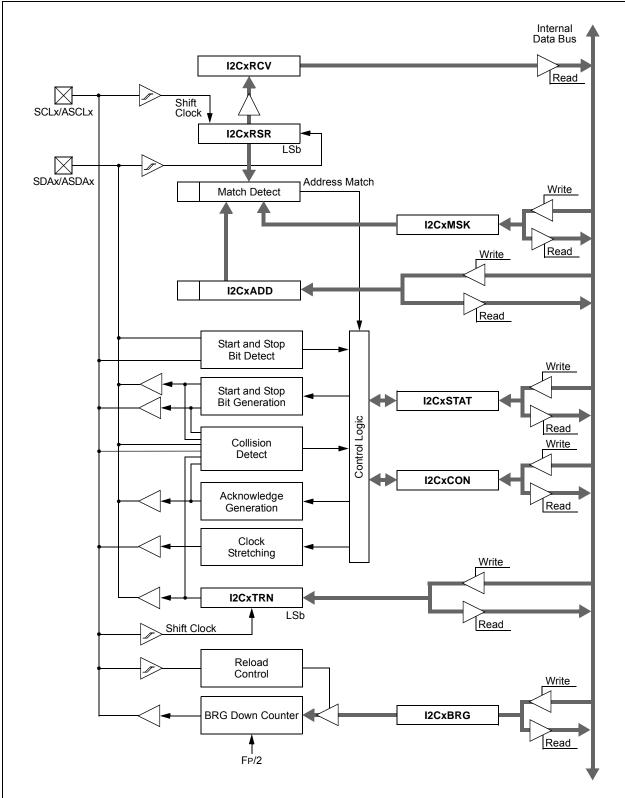

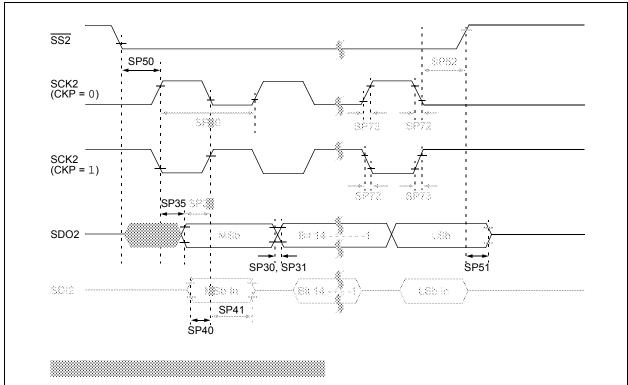

| bit 7-6<br>bit 5-2<br>bit 1 | 0011 = PWM<br>0010 = PWM<br>0001 = PWM<br>0000 = No st<br>Unimplemen<br>CHOPSEL<3<br>The selected<br>1001 = Rese<br>•<br>•<br>•<br>0100 = Rese<br>0011 = PWM<br>0010 = PWM<br>0001 = PWM                   | 3H selected as<br>2H selected as<br>1H selected as<br>ate blanking<br>ted: Read as '(<br>:0>: PWMx Ch<br>signal will enab<br>rved<br>3H selected as<br>2H selected as<br>1H selected as                                                        | state blank so<br>state blank so<br>op Clock Sour-<br>ole and disable<br>cHOP clock so<br>cHOP clock so<br>cHOP clock so<br>cHOP clock so                                                                                                                                                                                                                                                    | ource<br>ource<br>rce Select bits<br>e (CHOP) the se<br>source<br>source<br>source<br>CHOP clock so |                  | outputs.          |               |