Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                    |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · · · · · · · · · · · · · · · · · · ·                                           |

| RAM Size                   | 4K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

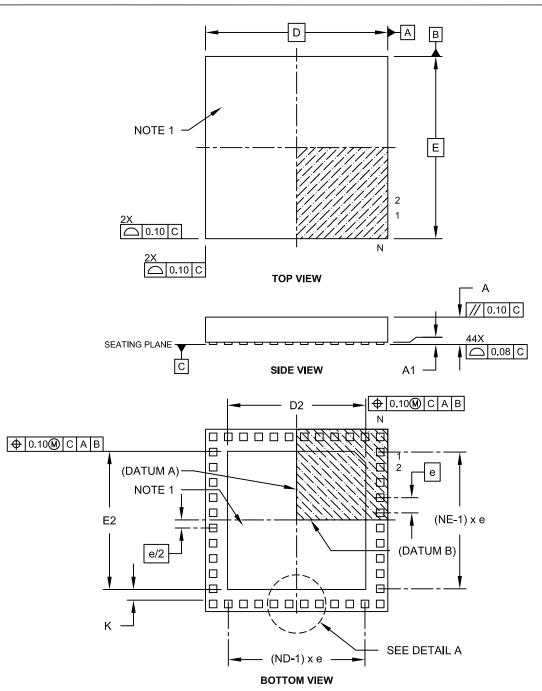

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc506-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 4                                                                        | -12:  | PWM RI   | EGISTE                                                                               | R MAP  | FOR de | sPIC33E | PXXXN  | AC20X/50 | DX AND F | PIC24EP | PXXXM | C20X [ | DEVICE | S ONI | _Y    |            |       |               |

|--------------------------------------------------------------------------------|-------|----------|--------------------------------------------------------------------------------------|--------|--------|---------|--------|----------|----------|---------|-------|--------|--------|-------|-------|------------|-------|---------------|

| File Name                                                                      | Addr. | Bit 15   | Bit 14                                                                               | Bit 13 | Bit 12 | Bit 11  | Bit 10 | Bit 9    | Bit 8    | Bit 7   | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1      | Bit 0 | All<br>Resets |

| PTCON                                                                          | 0C00  | PTEN     | PTEN - PTSIDL SESTAT SEIEN EIPU SYNCPOL SYNCOEN SYNCEN SYNCSRC<2:0> SEVTPS<3:0> 0000 |        |        |         |        |          |          |         | 0000  |        |        |       |       |            |       |               |

| PTCON2                                                                         | 0C02  | _        | —                                                                                    | _      | _      | _       | —      | _        | —        | —       | _     | —      | _      | —     |       | PCLKDIV<2: | 0>    | 0000          |

| PTPER                                                                          | 0C04  |          | PTPER<15:0> 00F8                                                                     |        |        |         |        |          |          |         | 00F8  |        |        |       |       |            |       |               |

| SEVTCMP                                                                        | 0C06  |          |                                                                                      |        |        |         |        |          | SEVTCMP< | 5:0>    |       |        |        |       |       |            |       | 0000          |

| MDC                                                                            | 0C0A  |          |                                                                                      |        |        |         |        |          | MDC<15:  | )>      |       |        |        |       |       |            |       | 0000          |

| CHOP                                                                           | 0C1A  | CHPCLKEN | IPCLKEN CHOPCLK<9:0> 0000                                                            |        |        |         |        |          |          |         |       |        |        |       |       |            |       |               |

| PWMKEY                                                                         | 0C1E  |          | PWMKEY<15:0> 0000                                                                    |        |        |         |        |          |          |         |       |        |        |       |       |            |       |               |

| Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |       |          |                                                                                      |        |        |         |        |          |          |         |       |        |        |       |       |            |       |               |

## TABLE 4-13: PWM GENERATOR 1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

|           | 10.   |         |        |         |                                                                                                                                                                                             |          | I OIT U |          |           |          |        | 1102-         |        |         |          |         |         |      |

|-----------|-------|---------|--------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|----------|-----------|----------|--------|---------------|--------|---------|----------|---------|---------|------|

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13  | I3         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0 |          |         |          |           |          | Bit 0  | All<br>Resets |        |         |          |         |         |      |

| PWMCON1   | 0C20  | FLTSTAT | CLSTAT | TRGSTAT | FLTIEN                                                                                                                                                                                      | CLIEN    | TRGIEN  | ITB      | MDCS      | DTC<     | :1:0>  | DTCP          | _      | MTBS    | CAM      | XPRES   | IUE     | 0000 |

| IOCON1    | 0C22  | PENH    | PENL   | POLH    | POLL                                                                                                                                                                                        | PMOD     | <1:0>   | OVRENH   | OVRENL    | OVRDA    | T<1:0> | FLTDA         | T<1:0> | CLDA    | T<1:0>   | SWAP    | OSYNC   | C000 |

| FCLCON1   | 0C24  | _       |        | (       | CLSRC<4:                                                                                                                                                                                    | 0>       |         | CLPOL    | CLMOD     |          | FL     | TSRC<4:       | )>     |         | FLTPOL   | FLTMO   | D<1:0>  | 0000 |

| PDC1      | 0C26  |         |        |         |                                                                                                                                                                                             |          |         |          | PDC1<15:0 | )>       |        |               |        |         |          |         |         | FFF8 |

| PHASE1    | 0C28  |         |        |         | PHASE1<15:0>                                                                                                                                                                                |          |         |          |           | 0000     |        |               |        |         |          |         |         |      |

| DTR1      | 0C2A  | _       | _      |         | DTR1<13:0>                                                                                                                                                                                  |          |         |          |           | 0000     |        |               |        |         |          |         |         |      |

| ALTDTR1   | 0C2C  | _       | _      |         |                                                                                                                                                                                             |          |         |          | А         | LTDTR1<1 | 3:0>   |               |        |         |          |         |         | 0000 |

| TRIG1     | 0C32  |         |        |         |                                                                                                                                                                                             |          |         |          | TRGCMP<18 | 5:0>     |        |               |        |         |          |         |         | 0000 |

| TRGCON1   | 0C34  |         | TRGDI  | V<3:0>  |                                                                                                                                                                                             | _        | _       | _        | _         | _        | _      |               |        | TRG     | STRT<5:0 | >       |         | 0000 |

| LEBCON1   | 0C3A  | PHR     | PHF    | PLR     | PLF                                                                                                                                                                                         | FLTLEBEN | CLLEBEN | _        | _         | _        | _      | BCH           | BCL    | BPHH    | BPHL     | BPLH    | BPLL    | 0000 |

| LEBDLY1   | 0C3C  | _       | _      | —       | —                                                                                                                                                                                           |          |         |          |           |          | LEB<11 | :0>           |        |         |          |         |         | 0000 |

| AUXCON1   | 0C3E  | —       | —      | _       |                                                                                                                                                                                             |          | BLANKS  | SEL<3:0> |           | _        | _      |               | CHOPS  | EL<3:0> |          | CHOPHEN | CHOPLEN | 0000 |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X CPU.

The interrupt controller has the following features:

- Up to eight processor exceptions and software traps

- Eight user-selectable priority levels

- Interrupt Vector Table (IVT) with a unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Fixed interrupt entry and return latencies

## 7.1 Interrupt Vector Table

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X Interrupt Vector Table (IVT), shown in Figure 7-1, resides in program memory starting at location, 000004h. The IVT contains seven non-maskable trap vectors and up to 246 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit-wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

## 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

| U-0             | U-0   | U-0              | U-0   | U-0              | U-0              | U-0             | U-0   |

|-----------------|-------|------------------|-------|------------------|------------------|-----------------|-------|

| —               | —     | —                | —     | —                | —                | _               | —     |

| bit 15          |       |                  |       |                  | •                |                 | bit 8 |

|                 |       |                  |       |                  |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | STB<  | 23:16>           |                  |                 |       |

| bit 7           |       |                  |       |                  |                  |                 | bit 0 |

|                 |       |                  |       |                  |                  |                 |       |

| Legend:         |       |                  |       |                  |                  |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimpler     | mented bit, read | l as '0'        |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | eared            | x = Bit is unkr | nown  |

|                 |       |                  |       |                  |                  |                 |       |

#### REGISTER 8-5: DMAXSTBH: DMA CHANNEL X START ADDRESS REGISTER B (HIGH)

bit 15-8 Unimplemented: Read as '0'

bit 7-0 STB<23:16>: Secondary Start Address bits (source or destination)

#### REGISTER 8-6: DMAXSTBL: DMA CHANNEL X START ADDRESS REGISTER B (LOW)

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | STB   | <15:8>            |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | STE   | 3<7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkı | nown  |

bit 15-0 **STB<15:0>:** Secondary Start Address bits (source or destination)

# 11.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS70598) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Many of the device pins are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

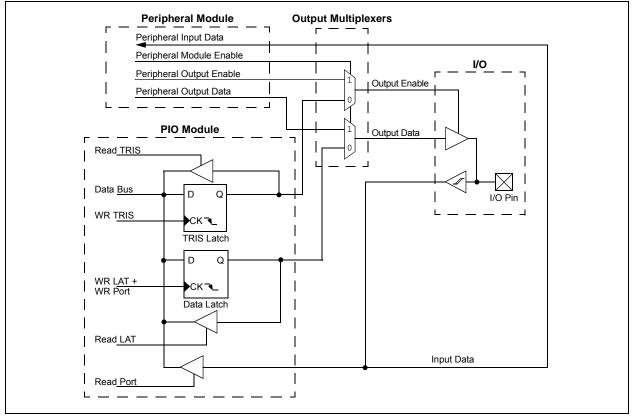

# 11.1 Parallel I/O (PIO) Ports

Generally, a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through," in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have eight registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Latch register (LATx) read the latch. Writes to the Latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device is disabled. This means the corresponding LATx and TRISx registers and the port pin are read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

| U-0     | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|------------|-------|-------|-------|

| —       | —     | —     | —     | —          | —     | —     | —     |

| bit 15  | •     |       |       |            | •     |       | bit 8 |

|         |       |       |       |            |       |       |       |

| U-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| _       |       |       |       | OCFAR<6:0> | >     |       |       |

| bit 7   | •     |       |       |            |       |       | bit 0 |

|         |       |       |       |            |       |       |       |

| Leaend: |       |       |       |            |       |       |       |

#### REGISTER 11-6: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0'

bit 6-0 OCFAR<6:0>: Assign Output Compare Fault A (OCFA) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121

> . 0000001 = Input tied to CMP1 0000000 = Input tied to Vss

# 14.2 Input Capture Registers

#### REGISTER 14-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0   |

|--------|-----|--------|---------|---------|---------|-----|-------|

| _      | —   | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 |     | —     |

| bit 15 |     |        |         |         |         |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/HC/HS-0 | R/HC/HS-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----------|-----------|-------|-------|-------|

| —     | ICI1  | ICI0  | ICOV      | ICBNE     | ICM2  | ICM1  | ICM0  |

| bit 7 |       |       |           |           |       |       | bit 0 |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable b  | bit                |

|-------------------|-----------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared      | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture Stop in Idle Control bit                                                                                                              |

|           | 1 = Input capture will Halt in CPU Idle mode                                                                                                                |

|           | 0 = Input capture will continue to operate in CPU Idle mode                                                                                                 |

| bit 12-10 | ICTSEL<2:0>: Input Capture Timer Select bits                                                                                                                |

|           | 111 = Peripheral clock (FP) is the clock source of the ICx                                                                                                  |

|           | 110 = Reserved                                                                                                                                              |

|           | 101 = Reserved                                                                                                                                              |

|           | 100 = T1CLK is the clock source of the ICx (only the synchronous clock is supported)<br>011 = T5CLK is the clock source of the ICx                          |

|           | 010 = T4CLK is the clock source of the ICx                                                                                                                  |

|           | 001 = T2CLK is the clock source of the ICx                                                                                                                  |

|           | 000 = T3CLK is the clock source of the ICx                                                                                                                  |

| bit 9-7   | Unimplemented: Read as '0'                                                                                                                                  |

| bit 6-5   | ICI<1:0>: Number of Captures per Interrupt Select bits (this field is not used if ICM<2:0> = 001 or 111)                                                    |

|           | 11 = Interrupt on every fourth capture event                                                                                                                |

|           | 10 = Interrupt on every third capture event                                                                                                                 |

|           | 01 = Interrupt on every second capture event<br>00 = Interrupt on every capture event                                                                       |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                    |

| bit 4     | 1 = Input capture buffer overflow occurred                                                                                                                  |

|           | 0 = No input capture buffer overflow occurred                                                                                                               |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                                |

|           | 1 = Input capture buffer is not empty, at least one more capture value can be read                                                                          |

|           | 0 = Input capture buffer is empty                                                                                                                           |

| bit 2-0   | ICM<2:0>: Input Capture Mode Select bits                                                                                                                    |

|           | 111 = Input capture functions as interrupt pin only in CPU Sleep and Idle modes (rising edge detect only, all other control bits are not applicable)        |

|           | 110 = Unused (module is disabled)                                                                                                                           |

|           | 101 = Capture mode, every 16th rising edge (Prescaler Capture mode)                                                                                         |

|           | <ul> <li>100 = Capture mode, every 4th rising edge (Prescaler Capture mode)</li> <li>011 = Capture mode, every rising edge (Simple Capture mode)</li> </ul> |

|           | 010 = Capture mode, every falling edge (Simple Capture mode)                                                                                                |

|           | 001 = Capture mode, every edge rising and falling (Edge Detect mode (ICI<1:0>) is not used in this mode)                                                    |

|           | 000 = Input capture module is turned off                                                                                                                    |

#### 17.2 QEI Control Registers

|  | REGISTER 17-1: | QEI1CON: QEI1 CONTROL REGISTER |

|--|----------------|--------------------------------|

|--|----------------|--------------------------------|

| U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         —       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   |                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------|---------------------|

| bit 15       bit 2         U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       -       intdividue       W= Writable bit       U = Unimplemented bit, read as '0'       bit 15       GEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to         bit 13       GEISDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD-2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       100 = Modulo Count mode for position counter         100 = Next index event after home event initializes position counter with contents of QEI1IC register       100 = Next index input event initializes position counter with contents of QEI1IC register       100 = Index input event dees not affect position coun                                                                                                                                                                                                  | R/W-0        | U-0                                                                                              | R/W-0                                                                                                          | R/W-0                                                                                        | R/W-0                                                                                          | R/W-0                                                      | R/W-0                             | R/W-0               |

| U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       bit 0       Dit 7       Dit 7       Dit 7       Dit 7       Dit 7         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       Dit 7         en value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN:       Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0         0 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to       Dit 13       QEISDL: QEI Stop in Idle Mode bit         1 = Discontinues module operation in Idle mode       0 = Continues module operation in Idle mode       Di Continues module operation on In Idle mode         Dit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         100 = Modulo Count mode for position counter       101 = Resets the position counter       101 = Resets the position counter with contents of QEI1IC register         101 = Resets the position counter when the position counter with contents of QEI1IC register       000 = Index input e                                                                                                                                                                                                                                          | QEIEN        | _                                                                                                | QEISIDL                                                                                                        | PIMOD2 <sup>(1)</sup>                                                                        | PIMOD1 <sup>(1)</sup>                                                                          | PIMOD0 <sup>(1)</sup>                                      | IMV1 <sup>(2)</sup>               | IMV0 <sup>(2)</sup> |

| -       INTDIV2 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       bit 7       bit 0         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       bit 0         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'       Bit is cleared       x = Bit is unknown         bit 13       QEISDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation unter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Modulo Count mode for position counter         10 = Resets the position counter when the position counter with contents of QEI1IC register       100 = Second index event after home event initializes position counter with contents of QEI1IC register         10 = Next index input event frees the position counter       111 = Reserved       112 = Rise index input event mees the position counter         11 = First index event after home event initializes position counter with contents of QEI1IC register       100 = Next index input event mees the position counter         10 = Next ind                                                                                                                                                   | bit 15       |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   | bit 8               |

| -       INTDIV2 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       bit 7       bit 0         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       bit 0         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'       Bit is cleared       x = Bit is unknown         bit 13       QEISDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation unter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Modulo Count mode for position counter         10 = Resets the position counter when the position counter with contents of QEI1IC register       100 = Second index event after home event initializes position counter with contents of QEI1IC register         10 = Next index input event frees the position counter       111 = Reserved       112 = Rise index input event mees the position counter         11 = First index event after home event initializes position counter with contents of QEI1IC register       100 = Next index input event mees the position counter         10 = Next ind                                                                                                                                                   |              |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   |                     |

| bit 7       bit 0         Legend:       W = Writable bit       U = Unimplemented bit, read as '0'         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Module counters are enabled         0 = Module counters are disabled, but SFRs can be read or written to       0 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'       0 = Continues module operation when device enters Idle mode         0 = Continues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD-2:0-: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Resets the position counter         101 = Resets the position counter when the position counter with contents of QEI1IC register         101 = Nexet input event after home event initializes position counter with contents of QEI1IC register         010 = Next index input event resets the position counter         011 = Every index input event resets the position counter         012 = Nease B match occurs when QEB = 1         0 = Phase B match occurs when QEB = 0         bit 8       IMV0: Index Match Value for Phase A bit <sup>(2)</sup> 1 = Phase A match occurs when QEA = 1 <t< td=""><td>U-0</td><td></td><td></td><td></td><td>R/W-0</td><td>R/W-0</td><td>R/W-0</td><td>R/W-0</td></t<>                                                                       | U-0          |                                                                                                  |                                                                                                                |                                                                                              | R/W-0                                                                                          | R/W-0                                                      | R/W-0                             | R/W-0               |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0         0 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to       0         bit 14       Unimplemented: Read as '0'       0         bit 13       QEISIDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         11 = Reserved       111 = Reserved         110 = Modulo Count mode for position counter       101 = Resets the position counter when the position counter equals QEI1GEC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       100 = Second index event after home event initializes position counter with contents of QEI1IC register         101 = First index vent after home event initializes position counter with contents of QEI1IC register       001 = Every index input event resets the position counter         010 = Next index input event does not affect position counter       001 = Every index input event after home event initializes position counter with contents of QEI1IC register                                                                                                                                |              | INTDIV2 <sup>(3)</sup>                                                                           | INTDIV1 <sup>(3)</sup>                                                                                         | INTDIV0 <sup>(3)</sup>                                                                       | CNTPOL                                                                                         | GATEN                                                      | CCM1                              |                     |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is cleared       x = Bit is unknown         bit 15       QEISIDL: QEI Stop in Idle Mode bit       1 = Module counters are disabled, but SFRs can be read or written to       bit 14         Unimplemented: Read as '0'       East as '0'       East as '0'       East as '0'         bit 13       QEISIDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       10 = Second index event after home event initializes position counter with contents of QEI1IC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter         101 = Reserved       III = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes position counter with contents of QEI1IC register         102 = Mext index input event does not affect position counter       01 = Phase                                                                                              | bit 7        |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   | bit 0               |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is cleared       x = Bit is unknown         bit 15       QEISIDL: QEI Stop in Idle Mode bit       1 = Module counters are disabled, but SFRs can be read or written to       bit 14         Unimplemented: Read as '0'       East as '0'       East as '0'       East as '0'         bit 13       QEISIDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       10 = Second index event after home event initializes position counter with contents of QEI1IC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter         101 = Reserved       III = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes position counter with contents of QEI1IC register         102 = Mext index input event does not affect position counter       01 = Phase                                                                                              | Logondy      |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   |                     |

| n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is unknown         bit 14       Unimplemented: Read as '0'       0'       0'       Bit is cleared       0 = Continues module operation when device enters ldle mode       0 = Continues module operation in ldle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       10 = Second index event after home event initializes position counter with contents of QEI11C register         100 = Second index event after home event initializes position counter with contents of QEI11C register       10 = Next index input event resets the position counter with contents of QEI11C register         101 = Every index input event resets the position counter       00 = Index input event does not affect position counter         001 = Every index input event genst bit <sup>(2)</sup> 1 = Phase B match occurs when QEB = 1         011 = Phase B match occurs when QEB = 1       0 = Phase B match occurs when QEA = 1         015 = Phase A match occurs when QEA = 1       0 = Phase A match occurs when QEA = 1         015 = Phase A match occurs when QEA =                                                                                                  |              | lo hit                                                                                           |                                                                                                                | hit                                                                                          | II – Unimplor                                                                                  | monted bit read                                            | ac '0'                            |                     |

| bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit         1 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'         bit 13       QEISIDL: QEI Stop in Idle Mode bit         1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         11 = Discontinues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       100 = Second index event after home event initializes position counter with contents of QEI1IC register         011 = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event resets the position counter         001 = Nevery index input eve                                                                                                  |              |                                                                                                  |                                                                                                                |                                                                                              | •                                                                                              |                                                            |                                   |                     |

| <ul> <li>1 = Module counters are enabled</li> <li>0 = Module counters are disabled, but SFRs can be read or written to</li> <li>bit 14</li> <li>Unimplemented: Read as '0'</li> <li>bit 13</li> <li>QEISIDL: QEI Stop in Idle Mode bit</li> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> <li>0 = Continues module operation in Idle mode</li> <li>0 = Continues module operation counter Initialization Mode Select bits<sup>(1)</sup></li> <li>111 = Reserved</li> <li>110 = Modulo Count mode for position counter</li> <li>101 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event initializes the position counter with contents of QEI1IC register</li> <li>010 = Next index input event resets the position counter with contents of QEI1IC register</li> <li>011 = Every index input event resets the position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index Match Value for Phase B bit<sup>(2)</sup></li> <li>1 = Phase B match occurs when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>bit 8</li> <li>IMV0: Index Match Value for Phase A bit<sup>(2)</sup></li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> </ul> | -n = value a | PUR                                                                                              | I = Bit is set                                                                                                 |                                                                                              | 0 = Bit is cle                                                                                 | ared                                                       | x = Bit is unkr                   | lown                |

| bit 13       QEISDL: QEI Stop in Idle Mode bit         1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Modulo Count mode for position counter         100 = Modulo Count mode for position counter       101 = Resets the position counter when the position counter equals QEI1GEC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter with contents of QEI1IC register         011 = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter with contents of QEI1IC register         011 = Every index input event resets the position counter       001 = Every index input event for position counter         001 = Index input event does not affect position counter       000 = Index input event does not affect position counter         001 = Phase B match occurs when QEB = 1       0 = Phase B match occurs when QEB = 0         0it 8       IMV0: Index Match Value for Phase A bit <sup>(2)</sup> 1 = Phase A match occurs when QEA = 1       0 = Phase A match occurs when QEA = 0         0it 7       Unimplemented: Read as '0'                                                                                                                                                                                   | bit 15       | 1 = Module co                                                                                    | ounters are ena                                                                                                | abled                                                                                        |                                                                                                |                                                            |                                   |                     |

| <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> <li>bit 12-10</li> <li>PIMOD&lt;2:0&gt;: Position Counter Initialization Mode Select bits<sup>(1)</sup></li> <li>111 = Reserved</li> <li>10 = Modulo Count mode for position counter</li> <li>10 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event resets the position counter with contents of QEI1IC register</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event operation when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>bit 8</li> <li>IMV0: Index Match Value for Phase A bit<sup>(2)</sup></li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                  | bit 14       | Unimplemen                                                                                       | ted: Read as '                                                                                                 | 0'                                                                                           |                                                                                                |                                                            |                                   |                     |

| <ul> <li>0 = Continues module operation in Idle mode</li> <li>bit 12-10</li> <li>PIMOD&lt;2:0&gt;: Position Counter Initialization Mode Select bits<sup>(1)</sup></li> <li>111 = Reserved</li> <li>10 = Modulo Count mode for position counter</li> <li>101 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event resets the position counter with contents of QEI1IC register</li> <li>001 = Every index input event resets the position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event QEB = 1</li> <li>0 = Phase B match occurs when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>bit 8</li> <li>IMV0: Index Match Value for Phase A bit<sup>(2)</sup></li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>bit 7</li> </ul>                                                                                                                                                                                                                                                                                                                                  | bit 13       | QEISIDL: QE                                                                                      | I Stop in Idle M                                                                                               | lode bit                                                                                     |                                                                                                |                                                            |                                   |                     |

| <ul> <li>111 = Reserved</li> <li>10 = Modulo Count mode for position counter</li> <li>101 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>011 = First index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event initializes the position counter with contents of QEI1IC register</li> <li>011 = Every index input event resets the position counter with contents of QEI1IC register</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>011 = Phase B match occurs when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>0 = Phase A match occurs when QEA = 0</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                | dle mode                                                   |                                   |                     |

| <ul> <li>110 = Modulo Count mode for position counter</li> <li>101 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>011 = First index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event initializes the position counter with contents of QEI1IC register</li> <li>001 = Every index input event resets the position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event for Phase B bit<sup>(2)</sup></li> <li>1 = Phase B match occurs when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>bit 8</li> <li>IMV0: Index Match Value for Phase A bit<sup>(2)</sup></li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 12-10    | PIMOD<2:0>                                                                                       | : Position Cour                                                                                                | nter Initializatio                                                                           | on Mode Selec                                                                                  | t bits <sup>(1)</sup>                                      |                                   |                     |

| 1 = Phase B match occurs when QEB = 1         0 = Phase B match occurs when QEB = 0         bit 8       IMV0: Index Match Value for Phase A bit <sup>(2)</sup> 1 = Phase A match occurs when QEA = 1         0 = Phase A match occurs when QEA = 0         bit 7       Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              | 110 = Modulo<br>101 = Resets<br>100 = Second<br>011 = First in<br>010 = Next in<br>001 = Every i | b Count mode f<br>the position co<br>d index event a<br>dex event after<br>idex input even<br>index input even | bunter when the<br>fter home event<br>home event in<br>t initializes the<br>put resets the p | e position cou<br>at initializes posi<br>nitializes positi<br>position coun<br>position counte | sition counter wit<br>on counter with<br>ter with contents | h contents of C<br>contents of QE | EI1IC register      |

| 0 = Phase B match occurs when QEB = 0         bit 8         IMV0: Index Match Value for Phase A bit <sup>(2)</sup> 1 = Phase A match occurs when QEA = 1         0 = Phase A match occurs when QEA = 0         bit 7         Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bit 9        |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   |                     |

| bit 8       IMV0: Index Match Value for Phase A bit <sup>(2)</sup> 1 = Phase A match occurs when QEA = 1         0 = Phase A match occurs when QEA = 0         bit 7       Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   |                     |

| 1 = Phase A match occurs when QEA = 10 = Phase A match occurs when QEA = 0bit 7Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   |                     |