Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 64KB (22K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 4K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

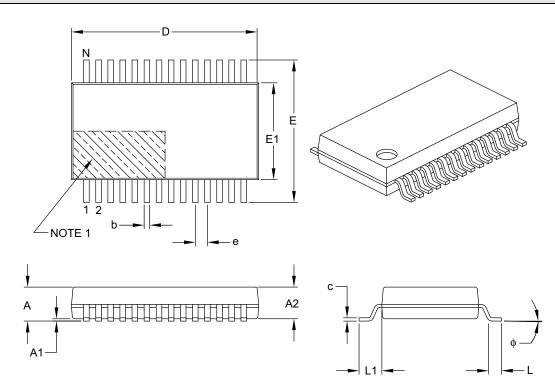

| Mounting Type              | Surface Mount                                                                    |

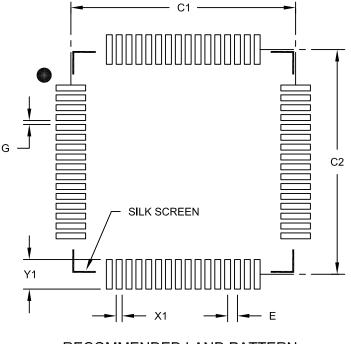

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc506t-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 2: dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X MOTOR CONTROL FAMILIES (CONTINUED)

|                   |                                |                               | (00          |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

|-------------------|--------------------------------|-------------------------------|--------------|----------------------|---------------|----------------|------------------------------------------------|------------------------------|--------|--------------------|------------------|------------------------------------|--------------------------------|----------------------|------------------------------|---------------------|------|-----|----------|-----------|-----------------------|

|                   | <i>•</i>                       | (se                           |              |                      | -             | Re             | mappa                                          | ble P                        | eriphe | erals              |                  |                                    |                                |                      | ~                            |                     |      |     |          |           |                       |

| Device            | Page Erase Size (Instructions) | Program Flash Memory (Kbytes) | RAM (Kbytes) | 16-Bit/32-Bit Timers | Input Capture | Output Compare | Motor Control PWM <sup>(4)</sup><br>(Channels) | Quadrature Encoder Interface | UART   | SPI <sup>(2)</sup> | ECAN™ Technology | External Interrupts <sup>(3)</sup> | I <sup>2</sup> C <sup>TM</sup> | <b>CRC Generator</b> | 10-Bit/12-Bit ADC (Channels) | Op Amps/Comparators | CTMU | ЪТG | I/O Pins | Pins      | Packages              |

| dsPIC33EP32MC504  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP64MC504  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           | VTLA <sup>(5)</sup> , |

| dsPIC33EP128MC504 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,         |

| dsPIC33EP256MC504 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          | 40        | UQFN                  |

| dsPIC33EP512MC504 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP64MC506  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP128MC506 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 16                           | 3/4                 | Voo  | Voo | 53       | 64        | TQFP,                 |

| dsPIC33EP256MC506 | 1024                           | 256                           | 32           | 3                    | 4             | 4              | 0                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 10                           | 3/4                 | Yes  | Yes | 55       | 04        | QFN                   |

| dsPIC33EP512MC506 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

Note 1:

On 28-pin devices, Comparator 4 does not have external connections. Refer to Section 25.0 "Op Amp/Comparator Module" for details.

2:

Only SPI2 is remappable.

3: INT0 is not remappable.

4: Only the PWM Faults are remappable.

5: The SSOP and VTLA packages are not available for devices with 512 Kbytes of memory.

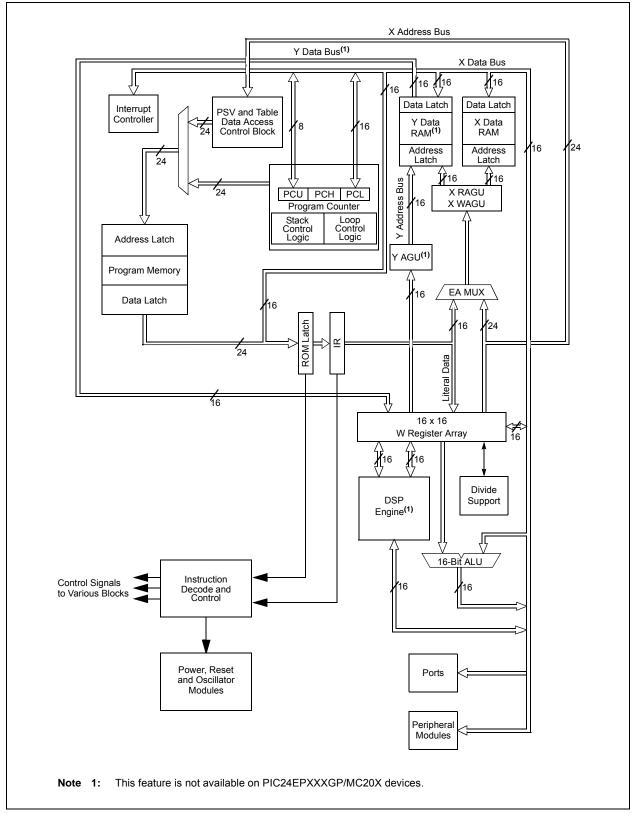

FIGURE 3-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X CPU BLOCK DIAGRAM

| IABLE 4   | -10.  | 001                         |                                     | JMPARE   |        |           | OUIFU  |       | ARE 4       | REGIS       |              | <u>٢</u> |        |          |           |          |       |               |

|-----------|-------|-----------------------------|-------------------------------------|----------|--------|-----------|--------|-------|-------------|-------------|--------------|----------|--------|----------|-----------|----------|-------|---------------|

| File Name | Addr. | Bit 15                      | Bit 14                              | Bit 13   | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8       | Bit 7       | Bit 6        | Bit 5    | Bit 4  | Bit 3    | Bit 2     | Bit 1    | Bit 0 | All<br>Resets |

| OC1CON1   | 0900  | —                           | -                                   | OCSIDL   | C      | CTSEL<2:0 | )>     | —     | ENFLTB      | ENFLTA      | —            | OCFLTB   | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC1CON2   | 0902  | FLTMD                       | FLTOUT                              | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS   |        | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC1RS     | 0904  |                             |                                     |          |        |           |        | Outp  | out Compare | e 1 Seconda | ary Register |          |        |          |           |          |       | xxxx          |

| OC1R      | 0906  |                             |                                     |          |        |           |        |       | Output Co   | mpare 1 Re  | gister       |          |        |          |           |          |       | xxxx          |

| OC1TMR    | 0908  |                             |                                     |          |        |           |        |       | Timer V     | alue 1 Regi | ster         |          |        |          |           |          |       | xxxx          |

| OC2CON1   | 090A  | _                           | —                                   | OCSIDL   | 0      | CTSEL<2:0 | )>     | _     | ENFLTB      | ENFLTA      | _            | OCFLTB   | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC2CON2   | 090C  | FLTMD                       | FLTOUT                              | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS   |        | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC2RS     | 090E  |                             | Output Compare 2 Secondary Register |          |        |           |        |       |             |             |              | xxxx     |        |          |           |          |       |               |

| OC2R      | 0910  |                             |                                     |          |        |           |        |       | Output Co   | mpare 2 Re  | gister       |          |        |          |           |          |       | xxxx          |

| OC2TMR    | 0912  |                             |                                     |          |        |           |        |       | Timer V     | alue 2 Regi | ster         |          |        |          |           |          |       | xxxx          |

| OC3CON1   | 0914  | _                           | —                                   | OCSIDL   | 0      | CTSEL<2:0 | )>     | _     | ENFLTB      | ENFLTA      | _            | OCFLTB   | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC3CON2   | 0916  | FLTMD                       | FLTOUT                              | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS   |        | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC3RS     | 0918  |                             |                                     |          |        |           |        | Outp  | out Compare | e 3 Seconda | ary Register |          |        |          |           |          |       | xxxx          |

| OC3R      | 091A  |                             |                                     |          |        |           |        |       | Output Co   | mpare 3 Re  | gister       |          |        |          |           |          |       | xxxx          |

| OC3TMR    | 091C  |                             |                                     |          |        |           |        |       | Timer V     | alue 3 Regi | ster         |          |        |          |           |          |       | xxxx          |

| OC4CON1   | 091E  | _                           | —                                   | OCSIDL   | 0      | CTSEL<2:0 | )>     | _     | ENFLTB      | ENFLTA      | _            | OCFLTB   | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC4CON2   | 0920  | FLTMD                       | FLTOUT                              | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS   |        | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC4RS     | 0922  |                             |                                     |          |        |           |        | Outp  | out Compare | e 4 Seconda | ary Register |          |        |          |           |          |       | xxxx          |

| OC4R      | 0924  |                             |                                     |          |        |           |        |       | Output Co   | mpare 4 Re  | gister       |          |        |          |           |          |       | xxxx          |

| OC4TMR    | 0926  | 26 Timer Value 4 Register x |                                     |          |        |           |        |       | xxxx        |             |              |          |        |          |           |          |       |               |

## TABLE 4-10: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 4 REGISTER MAP

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

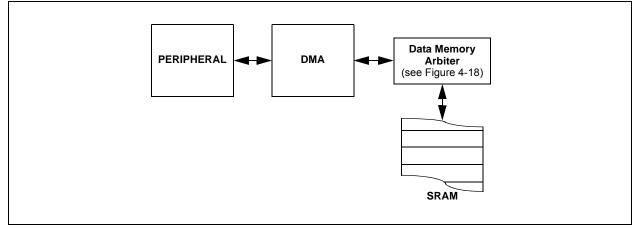

## 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM

In addition, DMA can access the entire data memory space. The Data Memory Bus Arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. Some of the peripherals supported by the DMA Controller include:

- ECAN<sup>™</sup>

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

## FIGURE 8-1: DMA CONTROLLER MODULE

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRIS setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRIS settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Pin Select registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Pin Select registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

#### 11.6 I/O Ports Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 11.6.1 KEY RESOURCES

- "I/O Ports" (DS70598) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 11-16: RPINR38: PERIPHERAL PIN SELECT INPUT REGISTER 38 (dsPIC33EPXXXMC20X AND PIC24EPXXXMC20X DEVICES ONLY)

|              | -                                 |                                      |       |                  |                   | -               |                |

|--------------|-----------------------------------|--------------------------------------|-------|------------------|-------------------|-----------------|----------------|

| U-0          | R/W-0                             | R/W-0                                | R/W-0 | R/W-0            | R/W-0             | R/W-0           | R/W-0          |

|              |                                   |                                      |       | DTCMP1R<6:       | 0>                |                 |                |

| bit 15       |                                   |                                      |       |                  |                   |                 | bit 8          |

|              |                                   |                                      |       |                  |                   |                 |                |

| U-0          | U-0                               | U-0                                  | U-0   | U-0              | U-0               | U-0             | U-0            |

| —            | —                                 | —                                    | _     |                  | _                 | —               | —              |

| bit 7        |                                   |                                      |       |                  |                   |                 | bit C          |

|              |                                   |                                      |       |                  |                   |                 |                |

| Legend:      |                                   |                                      |       |                  |                   |                 |                |

| R = Readal   | R = Readable bit W = Writable bit |                                      |       |                  | mented bit, read  | d as '0'        |                |

| -n = Value a | at POR                            | '1' = Bit is set                     | :     | '0' = Bit is cle | x = Bit is unkr   | nown            |                |

|              |                                   |                                      |       |                  |                   |                 |                |

| bit 15       | Unimpleme                         | nted: Read as '                      | 0'    |                  |                   |                 |                |

| bit 14-8     |                                   | 6:0>: Assign PV<br>1-2 for input pin |       | •                | on Input 1 to the | e Corresponding | g RPn Pin bits |

|              | 1111001 =                         | Input tied to RP                     | 1121  |                  |                   |                 |                |

|              | •                                 |                                      |       |                  |                   |                 |                |

|              | •                                 |                                      |       |                  |                   |                 |                |

|              |                                   | Input tied to CM                     | P1    |                  |                   |                 |                |

|              |                                   | Input tied to Vss                    |       |                  |                   |                 |                |

| bit 7-0      |                                   | nted: Read as '                      |       |                  |                   |                 |                |

|              |                                   |                                      | -     |                  |                   |                 |                |

## 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70569) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, ADC Converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family offers two SPI modules on a single device. These modules, which are designated as SPI1 and SPI2, are functionally identical. Each SPI module includes an eight-word FIFO buffer and allows DMA bus connections. When using the SPI module with DMA, FIFO operation can be disabled.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 and SPI2 modules.

The SPI1 module uses dedicated pins which allow for a higher speed when using SPI1. The SPI2 module takes advantage of the Peripheral Pin Select (PPS) feature to allow for greater flexibility in pin configuration of the SPI2 module, but results in a lower maximum speed for SPI2. See **Section 30.0** "**Electrical Characteristics**" for more information.

The SPIx serial interface consists of four pins, as follows:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx/FSYNCx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPIx module can be configured to operate with two, three or four pins. In 3-pin mode, SSx is not used. In 2-pin mode, neither SDOx nor SSx is used.

Figure 18-1 illustrates the block diagram of the SPIx module in Standard and Enhanced modes.

| R/W-0         | R/W-0                              | R/W-0                                  | U-0          | U-0              | U-0             | U-0               | U-0    |  |  |  |  |

|---------------|------------------------------------|----------------------------------------|--------------|------------------|-----------------|-------------------|--------|--|--|--|--|

| FRMEN         | SPIFSD                             | FRMPOL                                 | —            | —                | _               | —                 | _      |  |  |  |  |

| bit 15        |                                    |                                        |              |                  |                 |                   | bit 8  |  |  |  |  |

|               |                                    |                                        |              |                  |                 |                   |        |  |  |  |  |

| U-0           | U-0                                | U-0                                    | U-0          | U-0              | U-0             | R/W-0             | R/W-0  |  |  |  |  |

| _             | —                                  | —                                      | _            |                  | _               | FRMDLY            | SPIBEN |  |  |  |  |

| bit 7         |                                    |                                        |              |                  |                 |                   | bit 0  |  |  |  |  |

|               |                                    |                                        |              |                  |                 |                   |        |  |  |  |  |

| Legend:       |                                    |                                        |              |                  |                 |                   |        |  |  |  |  |

| R = Readable  | e bit                              | W = Writable b                         | pit          | U = Unimpler     | nented bit, rea | ad as '0'         |        |  |  |  |  |

| -n = Value at | POR                                | '1' = Bit is set                       |              | '0' = Bit is cle | ared            | x = Bit is unkr   | nown   |  |  |  |  |

|               |                                    |                                        |              |                  |                 |                   |        |  |  |  |  |

| bit 15        | FRMEN: Fra                         | med SPIx Suppo                         | ort bit      |                  |                 |                   |        |  |  |  |  |

|               |                                    | SPIx support is e<br>SPIx support is d |              | x pin is used as | Frame Sync      | oulse input/outpu | it)    |  |  |  |  |

| bit 14        | SPIFSD: Fra                        | me Sync Pulse [                        | Direction Co | ontrol bit       |                 |                   |        |  |  |  |  |

|               |                                    | ync pulse input (<br>ync pulse output  |              |                  |                 |                   |        |  |  |  |  |

| bit 13        | FRMPOL: Fr                         | ame Sync Pulse                         | Polarity bit | t                |                 |                   |        |  |  |  |  |

|               |                                    | ync pulse is activ                     | •            |                  |                 |                   |        |  |  |  |  |

|               |                                    | ync pulse is activ                     |              |                  |                 |                   |        |  |  |  |  |

| bit 12-2      | -                                  | nted: Read as '0                       |              |                  |                 |                   |        |  |  |  |  |

| bit 1         |                                    | ame Sync Pulse                         | -            |                  |                 |                   |        |  |  |  |  |

|               |                                    | ync pulse coincio<br>ync pulse preceo  |              |                  |                 |                   |        |  |  |  |  |

| bit 0         | SPIBEN: Enhanced Buffer Enable bit |                                        |              |                  |                 |                   |        |  |  |  |  |

|               |                                    | d buffer is enable                     |              |                  |                 |                   |        |  |  |  |  |

|               | 0 = Enhance                        | d buffer is disabl                     | ed (Standa   | rd mode)         |                 |                   |        |  |  |  |  |

|               |                                    |                                        |              |                  |                 |                   |        |  |  |  |  |

#### REGISTER 18-3: SPIXCON2: SPIX CONTROL REGISTER 2

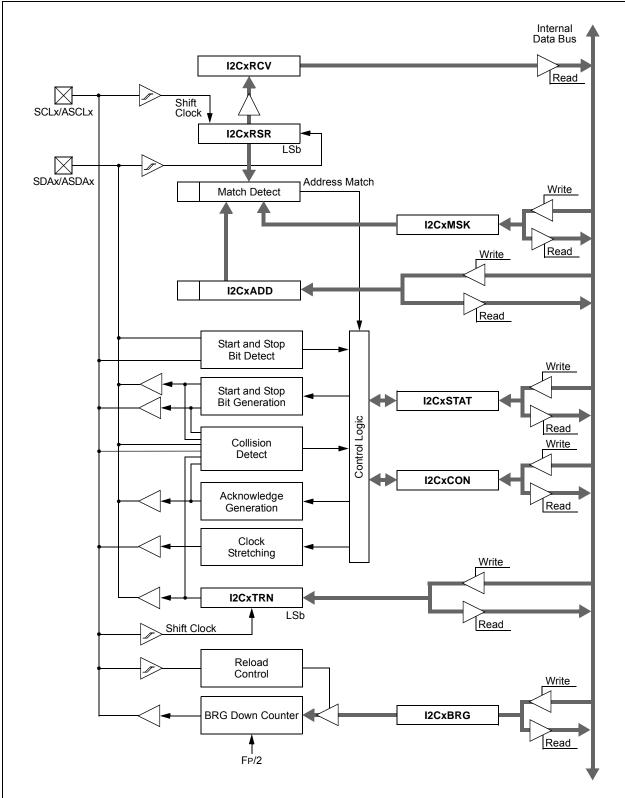

FIGURE 19-1: I2Cx BLOCK DIAGRAM (X = 1 OR 2)

#### 21.5 ECAN Message Buffers

ECAN Message Buffers are part of RAM memory. They are not ECAN Special Function Registers. The user application must directly write into the RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

#### BUFFER 21-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0           | U-0                       | U-0               | R/W-x         | R/W-x                                   | R/W-x            | R/W-x    | R/W-x |  |  |

|---------------|---------------------------|-------------------|---------------|-----------------------------------------|------------------|----------|-------|--|--|

|               | —                         | _                 | SID10         | SID9                                    | SID8             | SID7     | SID6  |  |  |

| bit 15        |                           |                   |               |                                         |                  |          | bit 8 |  |  |

| R/W-x         | R/W-x                     | R/W-x             | R/W-x         | R/W-x                                   | R/W-x            | R/W-x    | R/W-x |  |  |

| SID5          | SID4                      | SID3              | SID2          | SID1                                    | SID0             | SRR      | IDE   |  |  |

| bit 7         |                           |                   |               |                                         |                  |          | bit 0 |  |  |

| Legend:       |                           |                   |               |                                         |                  |          |       |  |  |

| R = Readabl   | e bit                     | W = Writable      | bit           | U = Unimpler                            | mented bit, read | l as '0' |       |  |  |

| -n = Value at | POR                       | '1' = Bit is set  |               | '0' = Bit is cleared x = Bit is unknown |                  |          |       |  |  |

|               |                           |                   |               |                                         |                  |          |       |  |  |

| bit 15-13     | Unimplemen                | ted: Read as '    | כי            |                                         |                  |          |       |  |  |

| bit 12-2      | <b>SID&lt;10:0&gt;:</b> S | Standard Identifi | ier bits      |                                         |                  |          |       |  |  |

| bit 1         | SRR: Substitu             | ute Remote Re     | quest bit     |                                         |                  |          |       |  |  |

|               | When IDE =                | 0:                |               |                                         |                  |          |       |  |  |

|               | 1 = Message               | will request rer  | note transmis | ssion                                   |                  |          |       |  |  |

|               | 0 = Normal m              | nessage           |               |                                         |                  |          |       |  |  |

|               | When IDE = 1              | <u>1:</u>         |               |                                         |                  |          |       |  |  |

|               | The SRR bit r             | must be set to '  | 1'.           |                                         |                  |          |       |  |  |

| bit 0         | IDE: Extende              | d Identifier bit  |               |                                         |                  |          |       |  |  |

|               | 1 = Message               | will transmit Ex  | tended Ident  | ifier                                   |                  |          |       |  |  |

|               | 0 = Message               | will transmit St  | andard Identi | fier                                    |                  |          |       |  |  |

|               |                           |                   |               |                                         |                  |          |       |  |  |

#### BUFFER 21-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0                                | U-0                               | U-0   | U-0   | R/W-x            | R/W-x                              | R/W-x           | R/W-x |  |  |  |

|------------------------------------|-----------------------------------|-------|-------|------------------|------------------------------------|-----------------|-------|--|--|--|

| —                                  | —                                 | —     | _     | EID17            | EID16                              | EID15           | EID14 |  |  |  |

| bit 15                             |                                   |       |       |                  |                                    |                 | bit 8 |  |  |  |

|                                    |                                   |       |       |                  |                                    |                 |       |  |  |  |

| R/W-x                              | R/W-x                             | R/W-x | R/W-x | R/W-x            | R/W-x                              | R/W-x           | R/W-x |  |  |  |

| EID13                              | EID12                             | EID11 | EID10 | EID9             | EID8                               | EID7            | EID6  |  |  |  |

| bit 7                              |                                   |       |       |                  |                                    |                 | bit 0 |  |  |  |

|                                    |                                   |       |       |                  |                                    |                 |       |  |  |  |

| Legend:                            |                                   |       |       |                  |                                    |                 |       |  |  |  |

| R = Readable                       | R = Readable bit W = Writable bit |       |       |                  | U = Unimplemented bit, read as '0' |                 |       |  |  |  |

| -n = Value at POR '1' = Bit is set |                                   |       |       | '0' = Bit is cle | ared                               | x = Bit is unkr | nown  |  |  |  |

|                                    |                                   |       |       |                  |                                    |                 |       |  |  |  |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

| U-0          | U-0                                                                                                | U-0                                                                                                                                                     | U-0                                                                                                       | U-0                                                                                                          | U-0                               | U-0      | R/W-0   |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------|----------|---------|--|--|--|

| —            | _                                                                                                  | —                                                                                                                                                       |                                                                                                           | —                                                                                                            | _                                 | —        | ADDMAEN |  |  |  |

| bit 15       |                                                                                                    |                                                                                                                                                         |                                                                                                           |                                                                                                              |                                   |          | bit 8   |  |  |  |

| U-0          | U-0                                                                                                | U-0                                                                                                                                                     | U-0                                                                                                       | U-0                                                                                                          | R/W-0                             | R/W-0    | R/W-0   |  |  |  |

| 0-0          | 0-0                                                                                                | 0-0                                                                                                                                                     | 0-0                                                                                                       | 0-0                                                                                                          |                                   |          | -       |  |  |  |

|              | —                                                                                                  | —                                                                                                                                                       | _                                                                                                         | —                                                                                                            | DMABL2                            | DMABL1   | DMABL0  |  |  |  |

| bit 7        |                                                                                                    |                                                                                                                                                         |                                                                                                           |                                                                                                              |                                   |          | bit 0   |  |  |  |

| Legend:      |                                                                                                    |                                                                                                                                                         |                                                                                                           |                                                                                                              |                                   |          |         |  |  |  |

| R = Readab   | le bit                                                                                             | W = Writable b                                                                                                                                          | bit                                                                                                       | U = Unimpler                                                                                                 | mented bit, read                  | 1 as '0' |         |  |  |  |

| -n = Value a | t POR                                                                                              | '1' = Bit is set                                                                                                                                        |                                                                                                           | 0' = Bit is cleared x = Bit is unknown                                                                       |                                   |          |         |  |  |  |

|              |                                                                                                    |                                                                                                                                                         |                                                                                                           |                                                                                                              |                                   |          |         |  |  |  |

| bit 15-9     | Unimplemen                                                                                         | ted: Read as '0                                                                                                                                         | 3                                                                                                         |                                                                                                              |                                   |          |         |  |  |  |

| bit 8        | ADDMAEN: A                                                                                         | ADC1 DMA Ena                                                                                                                                            | ıble bit                                                                                                  |                                                                                                              |                                   |          |         |  |  |  |

|              |                                                                                                    |                                                                                                                                                         |                                                                                                           | 0                                                                                                            | ster for transfer<br>ADC1BUFF reg | 0        |         |  |  |  |

| bit 7-3      | Unimplemen                                                                                         | ted: Read as '0                                                                                                                                         | ,                                                                                                         |                                                                                                              |                                   |          |         |  |  |  |

| bit 2-0      | DMABL<2:0>                                                                                         | Selects Numb                                                                                                                                            | per of DMA B                                                                                              | uffer Locations                                                                                              | per Analog Inpu                   | ut bits  |         |  |  |  |

|              | 110 = Allocat<br>101 = Allocat<br>100 = Allocat<br>011 = Allocat<br>010 = Allocat<br>001 = Allocat | es 128 words of<br>es 64 words of 1<br>es 32 words of 1<br>es 16 words of 1<br>es 8 words of b<br>es 4 words of b<br>es 2 words of b<br>es 1 word of bu | buffer to each<br>buffer to each<br>buffer to each<br>uffer to each<br>uffer to each a<br>uffer to each a | analog input<br>analog input<br>analog input<br>analog input<br>analog input<br>analog input<br>analog input |                                   |          |         |  |  |  |

## REGISTER 23-4: AD1CON4: ADC1 CONTROL REGISTER 4

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 24-12: PTGQPTR: PTG STEP QUEUE POINTER REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0   | U-0   | U-0         | U-0   | U-0   |

|--------|-----|-----|-------|-------|-------------|-------|-------|

| —      | —   | —   | —     | —     |             | _     | —     |

| bit 15 |     |     |       |       |             |       | bit 8 |

|        |     |     |       |       |             |       |       |

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 |

| _      |     |     |       |       | PTGQPTR<4:0 | >     |       |

| bit 7  |     |     |       |       |             |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 **PTGQPTR<4:0>:** PTG Step Queue Pointer Register bits This register points to the currently active Step command in the Step queue.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## **REGISTER 24-13: PTGQUEX: PTG STEP QUEUE REGISTER x (x = 0-7)**<sup>(1,3)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0     | R/W-0                | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-----------|----------------------|-------|-------|-------|

|        |       |       | STEP(2x + | - 1)<7:0> <b>(2)</b> |       |       |       |

| bit 15 |       |       |           |                      |       |       | bit 8 |

|        |       |       |           |                      |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0     | R/W-0                | R/W-0 | R/W-0 | R/W-0 |

| R/W-0                        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|------------------------------|-------|-------|-------|-------|-------|-------|-------|--|

| STEP(2x)<7:0> <sup>(2)</sup> |       |       |       |       |       |       |       |  |

| bit 7                        |       |       |       |       |       |       |       |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-8 | STEP(2x + 1)<7:0>: PTG Step Queue Pointer Register bits <sup>(2)</sup> |

|----------|------------------------------------------------------------------------|

|          | A queue location for storage of the STEP(2x + 1) command byte.         |

| bit 7-0  | STEP(2x)<7:0>: PTG Step Queue Pointer Register bits <sup>(2)</sup>     |

|          | A queue location for storage of the STEP(2x) command byte.             |

- **Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

- 2: Refer to Table 24-1 for the Step command encoding.

**3:** The Step registers maintain their values on any type of Reset.

| R/W-0         | R/W-0                                                      | R/W-0                                       | U-0                 | U-0              | R/W-0            | R/W-0               | R/W-0               |  |  |  |

|---------------|------------------------------------------------------------|---------------------------------------------|---------------------|------------------|------------------|---------------------|---------------------|--|--|--|

| CON           | COE <sup>(2)</sup>                                         | CPOL                                        | _                   | —                | OPMODE           | CEVT                | COUT                |  |  |  |

| bit 15        |                                                            |                                             |                     |                  |                  |                     | bit 8               |  |  |  |

|               |                                                            |                                             |                     |                  |                  |                     |                     |  |  |  |

| R/W-0         | R/W-0                                                      | U-0                                         | R/W-0               | U-0              | U-0              | R/W-0               | R/W-0               |  |  |  |

| EVPOL1        | EVPOL0                                                     | —                                           | CREF <sup>(1)</sup> | _                | —                | CCH1 <sup>(1)</sup> | CCH0 <sup>(1)</sup> |  |  |  |

| bit 7         |                                                            |                                             |                     |                  |                  |                     | bit (               |  |  |  |

| Legend:       |                                                            |                                             |                     |                  |                  |                     |                     |  |  |  |

| R = Readabl   | e bit                                                      | W = Writable                                | bit                 | U = Unimple      | mented bit, read | as '0'              |                     |  |  |  |

| -n = Value at | POR                                                        | '1' = Bit is set                            |                     | '0' = Bit is cle | eared            | x = Bit is unkr     | nown                |  |  |  |

|               |                                                            |                                             |                     |                  |                  |                     |                     |  |  |  |

| bit 15        | CON: Op Am                                                 | p/Comparator                                | Enable bit          |                  |                  |                     |                     |  |  |  |

|               |                                                            | comparator is e                             |                     |                  |                  |                     |                     |  |  |  |

|               |                                                            | comparator is d                             |                     |                  |                  |                     |                     |  |  |  |

| bit 14        |                                                            | arator Output Ei                            |                     |                  |                  |                     |                     |  |  |  |

|               |                                                            | tor output is pre                           |                     | CxOUT pin        |                  |                     |                     |  |  |  |

|               | -                                                          | tor output is int                           | -                   |                  |                  |                     |                     |  |  |  |

| bit 13        | •                                                          | CPOL: Comparator Output Polarity Select bit |                     |                  |                  |                     |                     |  |  |  |

|               |                                                            | 1 = Comparator output is inverted           |                     |                  |                  |                     |                     |  |  |  |

|               | -                                                          | tor output is no                            |                     |                  |                  |                     |                     |  |  |  |

| bit 12-11     | •                                                          | ted: Read as '                              |                     |                  |                  |                     |                     |  |  |  |

| bit 10        | <b>OPMODE:</b> Op Amp/Comparator Operation Mode Select bit |                                             |                     |                  |                  |                     |                     |  |  |  |

|               |                                                            | perates as an o<br>perates as a co          |                     |                  |                  |                     |                     |  |  |  |

| bit 9         | •                                                          | arator Event bi                             | •                   |                  |                  |                     |                     |  |  |  |

|               | 1 = Compara                                                |                                             | rding to the E      | VPOL<1:0> s      | ettings occurred | ; disables futur    | e triggers and      |  |  |  |

|               |                                                            | ator event did n                            |                     |                  |                  |                     |                     |  |  |  |

| bit 8         | COUT: Comp                                                 | parator Output b                            | oit                 |                  |                  |                     |                     |  |  |  |

|               | When CPOL = 0 (non-inverted polarity):                     |                                             |                     |                  |                  |                     |                     |  |  |  |

|               | 1 = VIN + > VIN-                                           |                                             |                     |                  |                  |                     |                     |  |  |  |

|               | 0 = VIN + < VI                                             |                                             |                     |                  |                  |                     |                     |  |  |  |

|               |                                                            | = 1 (inverted p                             | olarity):           |                  |                  |                     |                     |  |  |  |

|               | 1 = VIN + < VI                                             |                                             |                     |                  |                  |                     |                     |  |  |  |

|               | 0 = VIN + > VI                                             | N-                                          |                     |                  |                  |                     |                     |  |  |  |

#### **REGISTER 25-2:** CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2 OR 3)

- Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

- 2: This output is not available when OPMODE (CMxCON<10>) = 1.

## 27.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a То comprehensive reference source. complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual', which is available from the Microchip web site (www.microchip.com).

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

## 27.1 Configuration Bits

In dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices, the Configuration bytes are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored in at the top of the on-chip program memory space, known as the Flash Configuration bytes. Their specific locations are shown in Table 27-1. The configuration data is automatically loaded from the Flash Configuration bytes to the proper Configuration Shadow registers during device Resets.

| Note: | Configuration data is reloaded on all types |

|-------|---------------------------------------------|

|       | of device Resets.                           |

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration bytes for configuration data in their code for the compiler. This is to make certain that program code is not stored in this address when the code is compiled.

The upper 2 bytes of all Flash Configuration Words in program memory should always be '1111 1111 1111 1111 1111 1111'. This makes them appear to be NOP instructions in the remote event that their locations are ever executed by accident. Since Configuration bits are not implemented in the corresponding locations, writing '1's to these locations has no effect on device operation.

**Note:** Performing a page erase operation on the last page of program memory clears the Flash Configuration bytes, enabling code protection as a result. Therefore, users should avoid performing page erase operations on the last page of program memory.

The Configuration Flash bytes map is shown in Table 27-1.

| DC CHARACTERISTICS |                     |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |        |            |           |  |

|--------------------|---------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|-----------|--|

| Parameter<br>No.   | Тур.                | Max. | Units                                                                                                                                                                                                                                                                                   |        | Conditions |           |  |

| Idle Current (III  | dle) <sup>(1)</sup> |      |                                                                                                                                                                                                                                                                                         |        |            |           |  |

| DC40d              | 3                   | 8    | mA                                                                                                                                                                                                                                                                                      | -40°C  |            |           |  |

| DC40a              | 3                   | 8    | mA                                                                                                                                                                                                                                                                                      | +25°C  | - 3.3V     | 10 MIPS   |  |

| DC40b              | 3                   | 8    | mA                                                                                                                                                                                                                                                                                      | +85°C  | 3.3V       | 10 101195 |  |

| DC40c              | 3                   | 8    | mA                                                                                                                                                                                                                                                                                      | +125°C | ]          |           |  |

| DC42d              | 6                   | 12   | mA                                                                                                                                                                                                                                                                                      | -40°C  |            |           |  |

| DC42a              | 6                   | 12   | mA                                                                                                                                                                                                                                                                                      | +25°C  | 3.3V       | 20 MIPS   |  |

| DC42b              | 6                   | 12   | mA                                                                                                                                                                                                                                                                                      | +85°C  | 3.3V       | 20 1011 3 |  |

| DC42c              | 6                   | 12   | mA                                                                                                                                                                                                                                                                                      | +125°C |            |           |  |

| DC44d              | 11                  | 18   | mA                                                                                                                                                                                                                                                                                      | -40°C  |            | 40 MIPS   |  |

| DC44a              | 11                  | 18   | mA                                                                                                                                                                                                                                                                                      | +25°C  | 3.3V       |           |  |

| DC44b              | 11                  | 18   | mA                                                                                                                                                                                                                                                                                      | +85°C  | 5.50       | 40 1011-3 |  |

| DC44c              | 11                  | 18   | mA                                                                                                                                                                                                                                                                                      | +125°C |            |           |  |

| DC45d              | 17                  | 27   | mA                                                                                                                                                                                                                                                                                      | -40°C  |            |           |  |

| DC45a              | 17                  | 27   | mA                                                                                                                                                                                                                                                                                      | +25°C  | - 3.3V     | 60 MIPS   |  |

| DC45b              | 17                  | 27   | mA                                                                                                                                                                                                                                                                                      | +85°C  | 3.3V       |           |  |

| DC45c              | 17                  | 27   | mA                                                                                                                                                                                                                                                                                      | +125°C | ]          |           |  |

| DC46d              | 20                  | 35   | mA                                                                                                                                                                                                                                                                                      | -40°C  |            |           |  |

| DC46a              | 20                  | 35   | mA                                                                                                                                                                                                                                                                                      | +25°C  | 3.3V       | 70 MIPS   |  |

| DC46b              | 20                  | 35   | mA                                                                                                                                                                                                                                                                                      | +85°C  | ]          |           |  |

#### TABLE 30-7: DC CHARACTERISTICS: IDLE CURRENT (lidle)

**Note 1:** Base Idle current (IIDLE) is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- $\overline{\text{MCLR}}$  = VDD, WDT and FSCM are disabled

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- The NVMSIDL bit (NVMCON<12>) = 1 (i.e., Flash regulator is set to standby while the device is in Idle mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- JTAG is disabled

| АС СНА       | ARACTERIS | TICS                                  |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |               |       |                                                                               |

|--------------|-----------|---------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|-------|-------------------------------------------------------------------------------|

| Param<br>No. | Symbol    | Charao                                | cteristic <sup>(1)</sup>  | Min.                                                                                                                                                                                                                                                                                  | Тур. | Max.          | Units | Conditions                                                                    |

| TB10         | TtxH      | TxCK High<br>Time                     | Synchronous<br>mode       | Greater of:<br>20 or<br>(Tcy + 20)/N                                                                                                                                                                                                                                                  | _    | _             | ns    | Must also meet<br>Parameter TB15,<br>N = prescale<br>value<br>(1, 8, 64, 256) |

| TB11         | TtxL      | TxCK Low<br>Time                      | Synchronous<br>mode       | Greater of:<br>20 or<br>(Tcy + 20)/N                                                                                                                                                                                                                                                  | _    |               | ns    | Must also meet<br>Parameter TB15,<br>N = prescale<br>value<br>(1, 8, 64, 256) |

| TB15         | TtxP      | TxCK<br>Input<br>Period               | Synchronous<br>mode       | Greater of:<br>40 or<br>(2 Tcy + 40)/N                                                                                                                                                                                                                                                | —    | —             | ns    | N = prescale<br>value<br>(1, 8, 64, 256)                                      |

| TB20         | TCKEXTMRL | Delay from<br>Clock Edge<br>Increment | External TxCK<br>to Timer | 0.75 Tcy + 40                                                                                                                                                                                                                                                                         | —    | 1.75 Tcy + 40 | ns    |                                                                               |

| <b>TABLE 30-24</b> | TIMER2 AND TIM | IER4 (TYPE B TIMER | ER) EXTERNAL CLOCK TIMING REQUIREMENTS | j. |

|--------------------|----------------|--------------------|----------------------------------------|----|

|--------------------|----------------|--------------------|----------------------------------------|----|

Note 1: These parameters are characterized, but are not tested in manufacturing.

#### TABLE 30-25: TIMER3 AND TIMER5 (TYPE C TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS

| АС СНА       | RACTERIST | TICS                                                         |                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |               |       |                                          |

|--------------|-----------|--------------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|-------|------------------------------------------|

| Param<br>No. | Symbol    | Charac                                                       | teristic <sup>(1)</sup>     | Min.                                                                                                                                                                                                                                                                                | Тур. | Max.          | Units | Conditions                               |

| TC10         | TtxH      | TxCK High<br>Time                                            | Synchronous                 | Tcy + 20                                                                                                                                                                                                                                                                            |      |               | ns    | Must also meet<br>Parameter TC15         |