Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 64KB (22K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc506t-i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

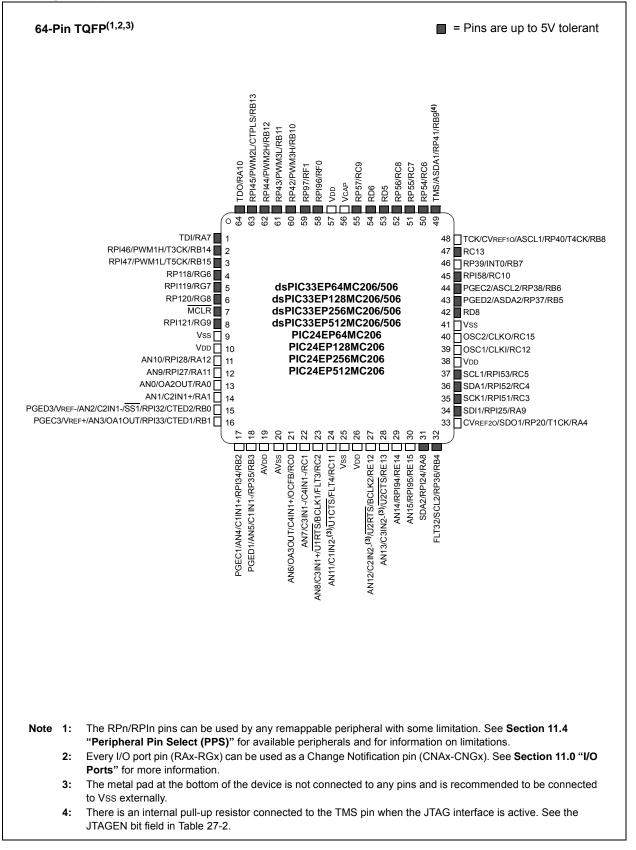

## Pin Diagrams (Continued)

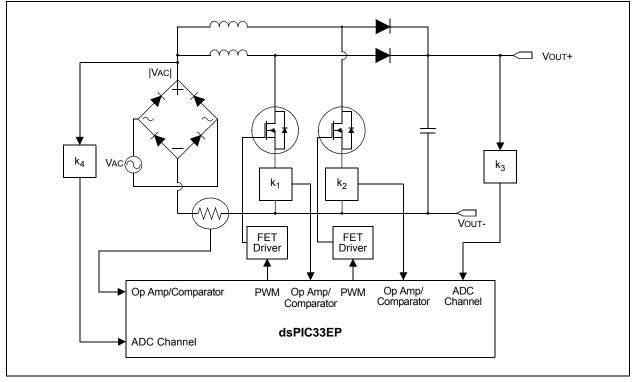

## FIGURE 2-7: INTERLEAVED PFC

## **REGISTER 3-1:** SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5       | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup><br>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled<br>110 = CPU Interrupt Priority Level is 6 (14)<br>101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)<br>011 = CPU Interrupt Priority Level is 3 (11)<br>010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)<br>000 = CPU Interrupt Priority Level is 0 (8) |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4         | RA: REPEAT Loop Active bit<br>1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 3         | N: MCU ALU Negative bit<br>1 = Result was negative<br>0 = Result was non-negative (zero or positive)                                                                                                                                                                                                                                                                                                                                                                                            |

| bit 2         | <ul> <li>OV: MCU ALU Overflow bit</li> <li>This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.</li> <li>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)</li> <li>0 = No overflow occurred</li> </ul>                                                                                                                                                                        |

| bit 1         | <ul> <li><b>Z:</b> MCU ALU Zero bit</li> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                                      |

| bit 0         | <b>C:</b> MCU ALU Carry/Borrow bit<br>1 = A carry-out from the Most Significant bit of the result occurred<br>0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                                                                                                                                                                             |

| Note 1:<br>2: | This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.<br>The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                                                                                                                                     |

- Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- 4: A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

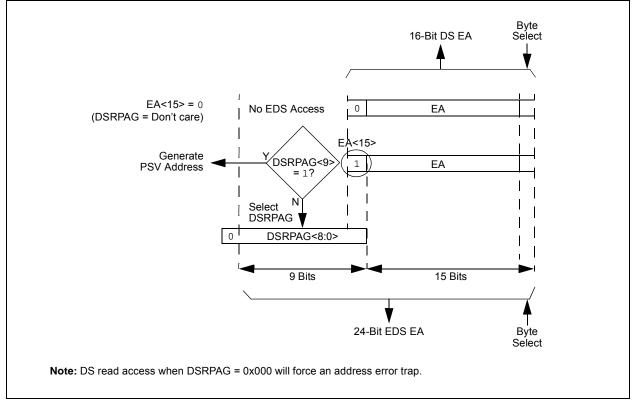

## 4.4.1 PAGED MEMORY SCHEME

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre-modified and post-modified Effective Addresses (EA). The upper half of the base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Read Page register (DSRPAG) or the 9-bit Write Page register (DSWPAG), to form an Extended Data Space (EDS) address or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

Construction of the EDS address is shown in Example 4-1. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when base address bit, EA<15> = 1, DSWPAG<8:0> are concatenated onto EA<14:0> to form the 24-bit EDS write address.

## **10.0 POWER-SAVING FEATURES**

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of peripherals being clocked constitutes lower consumed power.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices can manage power consumption in four ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- Software-Controlled Doze mode

- · Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

## EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

| PWRSAV | #SLEEP_MODE | ; | Put | the | device | into | Sleep mode |  |

|--------|-------------|---|-----|-----|--------|------|------------|--|

| PWRSAV | #IDLE_MODE  | ; | Put | the | device | into | Idle mode  |  |

## 10.1 Clock Frequency and Clock Switching

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or highprecision oscillators by simply changing the NOSCx bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0 "Oscillator Configuration"**.

## 10.2 Instruction-Based Power-Saving Modes

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 10-1.

**Note:** SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|                                                                      | REGISTER 10-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3 |          |                                         |     |       |        |       |  |  |

|----------------------------------------------------------------------|-------------------------------------------------------------------|----------|-----------------------------------------|-----|-------|--------|-------|--|--|

| U-0                                                                  | U-0                                                               | U-0      | U-0                                     | U-0 | R/W-0 | U-0    | U-0   |  |  |

| —                                                                    | _                                                                 | —        | —                                       | —   | CMPMD | —      | —     |  |  |

| bit 15                                                               |                                                                   |          |                                         |     |       |        | bit 8 |  |  |

|                                                                      |                                                                   |          |                                         |     |       |        |       |  |  |

| R/W-0                                                                | U-0                                                               | U-0      | U-0                                     | U-0 | U-0   | R/W-0  | U-0   |  |  |

| CRCMD                                                                | —                                                                 | —        | _                                       | —   | —     | I2C2MD | —     |  |  |

| bit 7                                                                |                                                                   |          |                                         |     |       |        | bit C |  |  |

|                                                                      |                                                                   |          |                                         |     |       |        |       |  |  |

| Legend:                                                              |                                                                   |          |                                         |     |       |        |       |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                   | l as '0' |                                         |     |       |        |       |  |  |

| -n = Value at POR '1' = Bit is set                                   |                                                                   |          | '0' = Bit is cleared x = Bit is unknown |     |       |        |       |  |  |

## REGISTER 10-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

| bit 10  | CMPMD: Comparator Module Disable bit |

|---------|--------------------------------------|

|         | 1 = Comparator module is disabled    |

|         | 0 = Comparator module is enabled     |

| bit 9-8 | Unimplemented: Read as '0'           |

| bit 7   | CRCMD: CRC Module Disable bit        |

|         | 1 = CRC module is disabled           |

|         | 0 = CRC module is enabled            |

| bit 6-2 | Unimplemented: Read as '0'           |

| bit 1   | I2C2MD: I2C2 Module Disable bit      |

|         | 1 = I2C2 module is disabled          |

|         | 0 = I2C2 module is enabled           |

| bit 0   | Unimplemented: Read as '0'           |

|         |                                      |

### REGISTER 10-4: PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

|        | -   |     |     |        |        |     |       |

|--------|-----|-----|-----|--------|--------|-----|-------|

| U-0    | U-0 | U-0 | U-0 | U-0    | U-0    | U-0 | U-0   |

| —      | —   |     |     |        | —      | —   | —     |

| bit 15 |     |     |     |        |        |     | bit 8 |

|        |     |     |     |        |        |     |       |

| U-0    | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | U-0 | U-0   |

| —      | —   | —   | —   | REFOMD | CTMUMD | —   | —     |

| bit 7  |     |     |     |        |        |     | bit 0 |

|        |     |     |     |        |        |     |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                                 |

|----------|------------------------------------------------------------|

| bit 3    | <b>REFOMD:</b> Reference Clock Module Disable bit          |

|          | <ol> <li>1 = Reference clock module is disabled</li> </ol> |

|          | 0 = Reference clock module is enabled                      |

| bit 2    | CTMUMD: CTMU Module Disable bit                            |

|          | 1 = CTMU module is disabled                                |

|          | 0 = CTMU module is enabled                                 |

| bit 1-0  | Unimplemented: Read as '0'                                 |

$\ensuremath{\textcircled{}^\circ}$  2011-2013 Microchip Technology Inc.

## 11.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS70598) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Many of the device pins are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

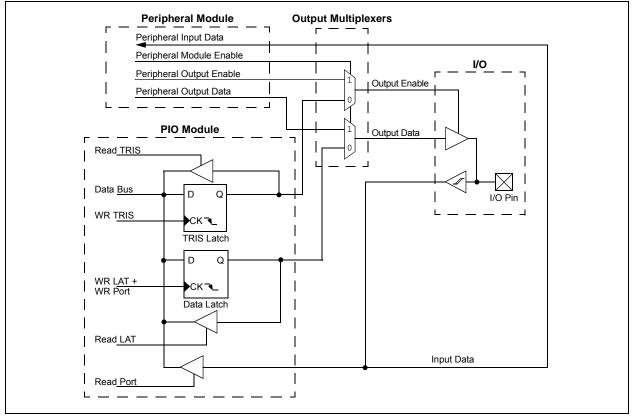

## 11.1 Parallel I/O (PIO) Ports

Generally, a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through," in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have eight registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Latch register (LATx) read the latch. Writes to the Latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device is disabled. This means the corresponding LATx and TRISx registers and the port pin are read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

NOTES:

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0      | R/W-0                                                                                                        | R/W-0                                                | R/W-0                           | U-0               | U-0              | U-0                    | R/W-0        |  |

|------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------|-------------------|------------------|------------------------|--------------|--|

| FLTMD      | FLTOUT                                                                                                       | FLTTRIEN                                             | OCINV                           | —                 | _                | —                      | OC32         |  |

| bit 15     | ·                                                                                                            |                                                      |                                 |                   | ·                |                        | bit          |  |

|            |                                                                                                              |                                                      |                                 |                   |                  |                        |              |  |

| R/W-0      | R/W-0, HS                                                                                                    | R/W-0                                                | R/W-0                           | R/W-1             | R/W-1            | R/W-0                  | R/W-0        |  |

| OCTRIG     | G TRIGSTAT                                                                                                   | OCTRIS                                               | SYNCSEL4                        | SYNCSEL3          | SYNCSEL2         | SYNCSEL1               | SYNCSEL      |  |

| bit 7      |                                                                                                              |                                                      |                                 |                   |                  |                        | bit          |  |

| Legend:    |                                                                                                              | HS = Hardwa                                          | re Settable bit                 |                   |                  |                        |              |  |

| R = Reada  | able bit                                                                                                     | W = Writable                                         | bit                             | U = Unimplem      | nented bit, read | l as '0'               |              |  |

| -n = Value | at POR                                                                                                       | '1' = Bit is set                                     |                                 | '0' = Bit is clea | ared             | x = Bit is unkn        | iown         |  |

|            |                                                                                                              |                                                      |                                 |                   |                  |                        |              |  |

| bit 15     | 1 = Fault mo<br>cleared i                                                                                    | t Mode Select b<br>ode is maintain<br>n software and | ed until the Fa<br>a new PWM pe | eriod starts      |                  |                        |              |  |

|            |                                                                                                              | de is maintaine                                      | d until the Faul                | t source is rem   | loved and a ne   | w PWM period           | starts       |  |

| bit 14     | FLTOUT: Fau                                                                                                  |                                                      | . –                             |                   |                  |                        |              |  |

|            |                                                                                                              | tput is driven hi<br>tput is driven lo               |                                 |                   |                  |                        |              |  |

| bit 13     | <ul> <li>0 = PWM output is driven low on a Fault</li> <li>FLTTRIEN: Fault Output State Select bit</li> </ul> |                                                      |                                 |                   |                  |                        |              |  |

|            |                                                                                                              | 1 = OCx pin is tri-stated on a Fault condition       |                                 |                   |                  |                        |              |  |

|            | •                                                                                                            | I/O state is defi                                    |                                 |                   | ault condition   |                        |              |  |

| bit 12     | OCINV: Outp                                                                                                  | OCINV: Output Compare x Invert bit                   |                                 |                   |                  |                        |              |  |

|            |                                                                                                              | out is inverted<br>out is not invert                 | ed                              |                   |                  |                        |              |  |

| bit 11-9   | Unimplemen                                                                                                   | ted: Read as '                                       | כי                              |                   |                  |                        |              |  |

| bit 8      | OC32: Casca                                                                                                  | ide Two OCx M                                        | odules Enable                   | bit (32-bit oper  | ration)          |                        |              |  |

|            |                                                                                                              | module operate module operate                        |                                 |                   |                  |                        |              |  |

| bit 7      |                                                                                                              | tput Compare x                                       |                                 | Select bit        |                  |                        |              |  |

|            |                                                                                                              | OCx from the s                                       |                                 |                   | CSELx bits       |                        |              |  |

|            |                                                                                                              | nizes OCx with                                       |                                 |                   |                  | S                      |              |  |

| bit 6      | TRIGSTAT: T                                                                                                  | imer Trigger St                                      | atus bit                        |                   |                  |                        |              |  |

|            |                                                                                                              | urce has been <sup>.</sup><br>urce has not be        |                                 |                   | d clear          |                        |              |  |

| bit 5      |                                                                                                              | put Compare x                                        |                                 | •                 |                  |                        |              |  |

|            | 1 = OCx is tr                                                                                                | • •                                                  | ·                               |                   |                  |                        |              |  |

|            | 0 = Output C                                                                                                 | ompare x mod                                         | ule drives the C                | OCx pin           |                  |                        |              |  |

| Note 1:    | Do not use the O                                                                                             | Cx module as i                                       | ts own Svnchro                  | nization or Tric  | aaer source.     |                        |              |  |

|            | When the OCy m                                                                                               |                                                      | -                               |                   |                  | module uses t          | he OCv       |  |

|            | module as a Trigg                                                                                            |                                                      |                                 |                   |                  |                        |              |  |

| 3:         | Each Output Con<br><b>"Peripheral Trig</b><br>PTGO0 = OC1<br>PTGO1 = OC2                                     |                                                      |                                 |                   |                  | n source. See <b>S</b> | Section 24.0 |  |

|            | PTGO2 = OC3 $PTGO3 = OC4$                                                                                    |                                                      |                                 |                   |                  |                        |              |  |

## REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

NOTES:

## 24.3 PTG Control Registers

### REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER

| R/W-0   | U-0     | R/W-0   | R/W-0   | U-0 | R/W-0                 | R/W-0                  | R/W-0                  |

|---------|---------|---------|---------|-----|-----------------------|------------------------|------------------------|

| PTGEN   | —       | PTGSIDL | PTGTOGL | —   | PTGSWT <sup>(2)</sup> | PTGSSEN <sup>(3)</sup> | PTGIVIS                |

| bit 15  |         |         |         |     |                       |                        | bit 8                  |

|         |         |         |         |     |                       |                        |                        |

| R/W-0   | HS-0    | U-0     | U-0     | U-0 | U-0                   | R/V                    | V-0                    |

| PTGSTRT | PTGWDTO | _       | _       | _   | _                     | PTGITM1 <sup>(1)</sup> | PTGITM0 <sup>(1)</sup> |

| bit 7 |

|-------|

|-------|

| Legend:           | HS = Hardware Settable bit |                                    |                    |  |  |  |

|-------------------|----------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 15  |       | PTGEN: Module Enable bit                                                                                                                                                                                                      |

|---------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |       | 1 = PTG module is enabled                                                                                                                                                                                                     |

|         |       | 0 = PTG module is disabled                                                                                                                                                                                                    |

| bit 14  |       | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| bit 13  |       | PTGSIDL: PTG Stop in Idle Mode bit                                                                                                                                                                                            |

|         |       | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                                       |

| bit 12  |       | PTGTOGL: PTG TRIG Output Toggle Mode bit                                                                                                                                                                                      |

|         |       | <ul> <li>1 = Toggle state of the PTGOx for each execution of the PTGTRIG command</li> <li>0 = Each execution of the PTGTRIG command will generate a single PTGOx pulse determined by the value in the PTGPWDx bits</li> </ul> |

| bit 11  |       | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| bit 10  |       | PTGSWT: PTG Software Trigger bit <sup>(2)</sup>                                                                                                                                                                               |

|         |       | 1 = Triggers the PTG module                                                                                                                                                                                                   |

|         |       | 0 = No action (clearing this bit will have no effect)                                                                                                                                                                         |

| bit 9   |       | PTGSSEN: PTG Enable Single-Step bit <sup>(3)</sup>                                                                                                                                                                            |

|         |       | 1 = Enables Single-Step mode                                                                                                                                                                                                  |

|         |       | 0 = Disables Single-Step mode                                                                                                                                                                                                 |

| bit 8   |       | PTGIVIS: PTG Counter/Timer Visibility Control bit                                                                                                                                                                             |

|         |       | 1 = Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the current values of their<br>corresponding counter/timer registers (PTGSD, PTGCx, PTGTx)                                                                   |

|         |       | <ul> <li>Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the value previously written<br/>to those limit registers</li> </ul>                                                                                    |

| bit 7   |       | PTGSTRT: PTG Start Sequencer bit                                                                                                                                                                                              |

|         |       | <ul><li>1 = Starts to sequentially execute commands (Continuous mode)</li><li>0 = Stops executing commands</li></ul>                                                                                                          |

| bit 6   |       | PTGWDTO: PTG Watchdog Timer Time-out Status bit                                                                                                                                                                               |

|         |       | 1 = PTG Watchdog Timer has timed out                                                                                                                                                                                          |

|         |       | 0 = PTG Watchdog Timer has not timed out.                                                                                                                                                                                     |

| bit 5-2 |       | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| Note    | 1: Th | nese bits apply to the PTGWHI and PTGWLO commands only.                                                                                                                                                                       |

|         | 2: Th | is bit is only used with the PTGCTRL step command software trigger option.                                                                                                                                                    |

3: Use of the PTG Single-Step mode is reserved for debugging tools only.

bit 0

## 27.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a То comprehensive reference source. complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual', which is available from the Microchip web site (www.microchip.com).

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

## 27.1 Configuration Bits

In dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices, the Configuration bytes are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored in at the top of the on-chip program memory space, known as the Flash Configuration bytes. Their specific locations are shown in Table 27-1. The configuration data is automatically loaded from the Flash Configuration bytes to the proper Configuration Shadow registers during device Resets.

| Note: | Configuration data is reloaded on all types |

|-------|---------------------------------------------|

|       | of device Resets.                           |

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration bytes for configuration data in their code for the compiler. This is to make certain that program code is not stored in this address when the code is compiled.

The upper 2 bytes of all Flash Configuration Words in program memory should always be '1111 1111 1111 1111 1111 1111'. This makes them appear to be NOP instructions in the remote event that their locations are ever executed by accident. Since Configuration bits are not implemented in the corresponding locations, writing '1's to these locations has no effect on device operation.

**Note:** Performing a page erase operation on the last page of program memory clears the Flash Configuration bytes, enabling code protection as a result. Therefore, users should avoid performing page erase operations on the last page of program memory.

The Configuration Flash bytes map is shown in Table 27-1.

| DC CH        | ARACTE | RISTICS                                 | (unless                         | d Operating<br>otherwise<br>g temperat | <b>stated)</b><br>ure -40° | C ≤ TA ≤ | <b>/ to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended                                                                                                                       |  |  |  |

|--------------|--------|-----------------------------------------|---------------------------------|----------------------------------------|----------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Param<br>No. | Symbol | Characteristic                          | Min. Typ. Max. Units Conditions |                                        |                            |          |                                                                                                                                                                                       |  |  |  |

|              | liL    | Input Leakage Current <sup>(1,2)</sup>  |                                 |                                        |                            |          |                                                                                                                                                                                       |  |  |  |

| DI50         |        | I/O Pins 5V Tolerant <sup>(3)</sup>     | -1                              | —                                      | +1                         | μA       | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in \ at \ high-impedance} \end{split}$                                                             |  |  |  |

| DI51         |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                              | _                                      | +1                         | μA       | $\label{eq:VSS} \begin{array}{l} Vss \leq V \text{PIN} \leq V \text{DD}, \\ \text{Pin at high-impedance}, \\ -40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C} \end{array}$ |  |  |  |

| DI51a        |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                              | _                                      | +1                         | μA       | Analog pins shared with external reference pins, $-40^{\circ}C \le TA \le +85^{\circ}C$                                                                                               |  |  |  |

| DI51b        |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                              | _                                      | +1                         | μA       | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance,<br>-40°C ≤ TA ≤ +125°C                                                                                                              |  |  |  |

| DI51c        |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                              | _                                      | +1                         | μA       | Analog pins shared with external reference pins, $-40^{\circ}C \le TA \le +125^{\circ}C$                                                                                              |  |  |  |

| DI55         |        | MCLR                                    | -5                              | —                                      | +5                         | μA       | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                                                                              |  |  |  |

| DI56         |        | OSC1                                    | -5                              | —                                      | +5                         | μΑ       | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &X{\sf T} \text{ and }H{\sf S} \text{ modes} \end{split}$                                                 |  |  |  |

## TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 2: Negative current is defined as current sourced by the pin.

- 3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 4: VIL source < (Vss 0.3). Characterized but not tested.

- **5:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

8: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

# FIGURE 30-11: TIMERQ (QEI MODULE) EXTERNAL CLOCK TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

## TABLE 30-30: QEI MODULE EXTERNAL CLOCK TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |           |                                                              |                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |      |       |                                  |

|--------------------|-----------|--------------------------------------------------------------|-----------------------------|-------------------------------------------------------|------|------|-------|----------------------------------|

| Param<br>No.       | Symbol    | Charao                                                       | cteristic <sup>(1)</sup>    | Min.                                                  | Тур. | Max. | Units | Conditions                       |

| TQ10               | TtQH      | TQCK High<br>Time                                            | Synchronous, with prescaler | Greater of 12.5 + 25<br>or<br>(0.5 Tcy/N) + 25        |      |      | ns    | Must also meet<br>Parameter TQ15 |

| TQ11               | TtQL      | TQCK Low<br>Time                                             | Synchronous, with prescaler | Greater of 12.5 + 25<br>or<br>(0.5 Tcy/N) + 25        | —    | _    | ns    | Must also meet<br>Parameter TQ15 |

| TQ15               | TtQP      | TQCP Input<br>Period                                         | Synchronous, with prescaler | Greater of 25 + 50<br>or<br>(1 Tcy/N) + 50            | —    | _    | ns    |                                  |

| TQ20               | TCKEXTMRL | Delay from External TQCK<br>Clock Edge to Timer<br>Increment |                             | _                                                     | 1    | Тсү  | —     |                                  |

Note 1: These parameters are characterized but not tested in manufacturing.

## FIGURE 30-29: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

## TABLE 30-54: OP AMP/COMPARATOR VOLTAGE REFERENCE SETTLING TIME SPECIFICATIONS

| AC CHARACTERISTICS |        |                | Standard Operating Conditions (see Note 2): 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |      |      |       |            |

|--------------------|--------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|

| Param.             | Symbol | Characteristic | Min.                                                                                                                                                                                                              | Тур. | Max. | Units | Conditions |

| VR310              | TSET   | Settling Time  | —                                                                                                                                                                                                                 | 1    | 10   | μS    | (Note 1)   |

**Note 1:** Settling time is measured while CVRR = 1 and CVR<3:0> bits transition from '0000' to '1111'.

2: Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

#### TABLE 30-55: OP AMP/COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| DC CHAF      | RACTERIS | TICS                                       | Standard O<br>(unless oth<br>Operating te | erwise st | <b>ated)</b><br>re -40°C ≤ T | A ≤ +85° | • <b>1): 3.0V to 3.6V</b><br>C for Industrial<br>°C for Extended |  |  |

|--------------|----------|--------------------------------------------|-------------------------------------------|-----------|------------------------------|----------|------------------------------------------------------------------|--|--|

| Param<br>No. | Symbol   | Characteristics                            | Min. Typ. Max. Units Conditions           |           |                              |          |                                                                  |  |  |

| VRD310       | CVRES    | Resolution                                 | CVRSRC/24                                 | _         | CVRSRC/32                    | LSb      |                                                                  |  |  |

| VRD311       | CVRAA    | Absolute Accuracy <sup>(2)</sup>           | —                                         | ±25       | _                            | mV       | CVRSRC = 3.3V                                                    |  |  |

| VRD313       | CVRSRC   | Input Reference Voltage                    | 0                                         | _         | AVDD + 0.3                   | V        |                                                                  |  |  |

| VRD314       | CVRout   | Buffer Output<br>Resistance <sup>(2)</sup> | _                                         | 1.5k      | _                            | Ω        |                                                                  |  |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

2: Parameter is characterized but not tested in manufacturing.

# 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units  |      |          | ETERS |

|----------------------------|--------|------|----------|-------|

| Dimensior                  | Limits | MIN  | NOM      | MAX   |

| Contact Pitch              | E      |      | 0.65 BSC |       |

| Optional Center Pad Width  | W2     |      |          | 4.70  |

| Optional Center Pad Length | T2     |      |          | 4.70  |

| Contact Pad Spacing        | C1     |      | 6.00     |       |

| Contact Pad Spacing        | C2     |      | 6.00     |       |

| Contact Pad Width (X28)    | X1     |      |          | 0.40  |

| Contact Pad Length (X28)   | Y1     |      |          | 0.85  |

| Distance Between Pads      | G      | 0.25 |          |       |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2124A

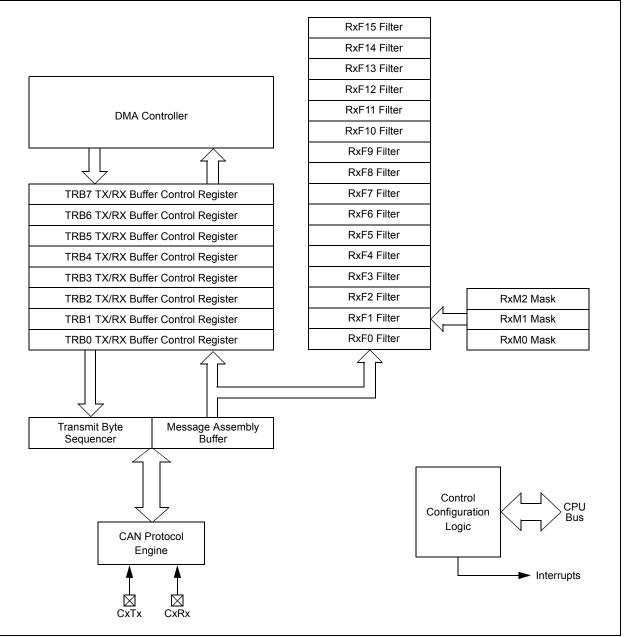

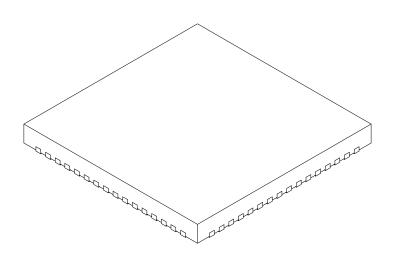

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | N      | MILLIMETERS |          |      |  |

|------------------------|--------|-------------|----------|------|--|

| Dimension              | Limits | MIN         | NOM      | MAX  |  |

| Number of Pins         | N      |             | 64       |      |  |

| Pitch                  | е      |             | 0.50 BSC |      |  |

| Overall Height         | A      | 0.80        | 0.90     | 1.00 |  |

| Standoff               | A1     | 0.00        | 0.02     | 0.05 |  |

| Contact Thickness      | A3     | 0.20 REF    |          |      |  |

| Overall Width          | E      | 9.00 BSC    |          |      |  |

| Exposed Pad Width      | E2     | 5.30        | 5.40     | 5.50 |  |

| Overall Length         | D      |             | 9.00 BSC |      |  |

| Exposed Pad Length     | D2     | 5.30        | 5.40     | 5.50 |  |

| Contact Width          | b      | 0.20        | 0.25     | 0.30 |  |

| Contact Length         | L      | 0.30        | 0.40     | 0.50 |  |

| Contact-to-Exposed Pad | K      | 0.20        | -        | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-154A Sheet 2 of 2

| Remappable Input for U1RX               |     |

|-----------------------------------------|-----|

| Reset System                            | 123 |

| Shared Port Structure                   |     |

| Single-Phase Synchronous Buck Converter |     |

| SPIx Module                             |     |

| Suggested Oscillator Circuit Placement  | 31  |

| Type B Timer (Timer2 and Timer4)        |     |

| Type B/Type C Timer Pair (32-Bit Timer) |     |

| Type C Timer (Timer3 and Timer5)        |     |

| UARTx Module                            |     |

| User-Programmable Blanking Function     |     |

| Watchdog Timer (WDT)                    |     |

| Brown-out Reset (BOR)                   |     |

## С

| C Compilers                              |          |

|------------------------------------------|----------|

| MPLAB XC Compilers                       |          |

| Charge Time Measurement Unit. See CTMU.  |          |

| Code Examples                            |          |

| IC1 Connection to QEI1 Input on          |          |

| Pin 43 of dsPIC33EPXXXMC206              |          |

| Port Write/Read                          |          |

| PWMx Write-Protected Register            |          |

| Unlock Sequence                          |          |

| PWRSAV Instruction Syntax                |          |

| Code Protection                          |          |

| CodeGuard Security                       | 379, 386 |

| Configuration Bits                       |          |

| Description                              |          |

| Configuration Byte Register Map          |          |

| Configuring Analog and Digital Port Pins |          |

| CPU                                      |          |

| Addressing Modes                         |          |

| Clocking System Options                  |          |

| Fast RC (FRC) Oscillator                 |          |

| FRC Oscillator with PLL                  |          |

| FRC Oscillator with Postscaler           |          |

| Low-Power RC (LPRC) Oscillator           |          |

| Primary (XT, HS, EC) Oscillator          |          |

| Primary Oscillator with PLL              |          |

| Control Registers                        |          |

| Data Space Addressing                    |          |

| Instruction Set                          |          |

| Resources                                |          |

| CTMU                                     |          |

| Control Registers                        |          |

| Resources                                |          |

| Customer Change Notification Service     |          |

| Customer Notification Service            |          |

| Customer Support                         |          |

|                                          |          |

# D

| Data Address Space                    | 51 |

|---------------------------------------|----|

| Memory Map for dsPIC33EP128MC20X/50X, |    |

| dsPIC33EP128GP50X Devices             | 54 |

| Memory Map for dsPIC33EP256MC20X/50X, |    |

| dsPIC33EP256GP50X Devices             | 55 |

| Memory Map for dsPIC33EP32MC20X/50X,  |    |

| dsPIC33EP32GP50X Devices              | 52 |

| Memory Map for dsPIC33EP512MC20X/50X, |    |

| dsPIC33EP512GP50X Devices             | 56 |

| Memory Map for dsPIC33EP64MC20X/50X,  |    |

| dsPIC33EP64GP50X Devices              | 53 |

| Memory Map for PIC24EP128GP/MC20X/50X |    |

| Devices                               | 59 |

|                                       |    |

| Memory Map for PIC24EP256GP/MC20X/50X   |       |

|-----------------------------------------|-------|

| Devices                                 | 60    |

| Memory Map for PIC24EP32GP/MC20X/50X    |       |

| Devices                                 | 57    |

| Memory Map for PIC24EP512GP/MC20X/50X   | 57    |

|                                         | ~ ~   |

| Devices                                 | 61    |

| Memory Map for PIC24EP64GP/MC20X/50X    |       |

| Devices                                 | 58    |

| Near Data Space                         | 51    |

| Organization, Alignment                 | 51    |

| SFR Space                               |       |

| Width                                   |       |

| Data Memory                             | 51    |

|                                         | 440   |

| Arbitration and Bus Master Priority     | . 110 |

| Data Space                              |       |

| Extended X                              | . 109 |

| Paged Memory Scheme                     | . 105 |

| DC and AC Characteristics               |       |

| Graphs                                  | 475   |

| DC Characteristics                      |       |

| BOR                                     | 111   |

|                                         |       |

| CTMU Current Source Requirements        |       |

| Doze Current (IDOZE) 407                |       |

| High Temperature                        |       |

| I/O Pin Input Specifications            | . 408 |

| I/O Pin Output Specifications           | 470   |

| Idle Current (IIDLE) 405                |       |

| Op Amp/Comparator Requirements          |       |

| Op Amp/Comparator Voltage Reference     | . 100 |

|                                         | 457   |

| Requirements                            |       |

| Operating Current (IDD) 404             |       |

| Operating MIPS vs. Voltage 402          |       |

| Power-Down Current (IPD) 406            | , 469 |

| Program Memory                          | . 412 |

| Temperature and Voltage                 | . 468 |

| Temperature and Voltage Specifications  |       |

| Thermal Operating Conditions            |       |

| Watchdog Timer Delta Current            |       |

|                                         | . 407 |

| Demo/Development Boards, Evaluation and | 400   |

| Starter Kits                            |       |

| Development Support                     |       |

| Third-Party Tools                       | . 400 |

| DMA Controller                          |       |

| Channel to Peripheral Associations      | . 140 |

| Control Registers                       |       |

| DMAxCNT                                 |       |

| DMAxCON                                 |       |

|                                         |       |

|                                         |       |

| DMAxREQ                                 |       |

| DMAxSTA                                 |       |

| DMAxSTB                                 |       |

| Resources                               |       |

| Supported Peripherals                   | . 139 |

| Doze Mode                               |       |

| DSP Engine                              |       |

| g                                       | ++    |

| E                                       |       |

# Ε

| 310 |

|-----|

| 311 |

| 311 |

| 312 |

| 312 |

| 313 |

| 313 |

|     |