#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128gp202-e-ss |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1: PINC                           |             | O DESC         | RIPT | IONS (CONTINUED)                                                                 |  |  |  |

|-------------------------------------------|-------------|----------------|------|----------------------------------------------------------------------------------|--|--|--|

| Pin Name <sup>(4)</sup>                   | Pin<br>Type | Buffer<br>Type | PPS  | Description                                                                      |  |  |  |

| U2CTS                                     | Ι           | ST             | No   | UART2 Clear-To-Send.                                                             |  |  |  |

| U2RTS                                     | 0           | —              | No   | UART2 Ready-To-Send.                                                             |  |  |  |

| U2RX                                      | Ι           | ST             | Yes  | UART2 receive.                                                                   |  |  |  |

| U2TX                                      | 0           | —              | Yes  | UART2 transmit.                                                                  |  |  |  |

| BCLK2                                     | 0           | ST             | No   | UART2 IrDA <sup>®</sup> baud clock output.                                       |  |  |  |

| SCK1                                      | I/O         | ST             | No   | Synchronous serial clock input/output for SPI1.                                  |  |  |  |

| SDI1                                      | I           | ST             | No   | SPI1 data in.                                                                    |  |  |  |

| SDO1                                      | 0           | —              | No   | SPI1 data out.                                                                   |  |  |  |

| SS1                                       | I/O         | ST             | No   | SPI1 slave synchronization or frame pulse I/O.                                   |  |  |  |

| SCK2                                      | I/O         | ST             | Yes  | Synchronous serial clock input/output for SPI2.                                  |  |  |  |

| SDI2                                      | I           | ST             | Yes  | SPI2 data in.                                                                    |  |  |  |

| SDO2                                      | 0           | _              | Yes  | SPI2 data out.                                                                   |  |  |  |

| SS2                                       | I/O         | ST             | Yes  | SPI2 slave synchronization or frame pulse I/O.                                   |  |  |  |

| SCL1                                      | I/O         | ST             | No   | Synchronous serial clock input/output for I2C1.                                  |  |  |  |

| SDA1                                      | I/O         | ST             | No   | Synchronous serial data input/output for I2C1.                                   |  |  |  |

| ASCL1                                     | I/O         | ST             | No   | Alternate synchronous serial clock input/output for I2C1.                        |  |  |  |

| ASDA1                                     | I/O         | ST             | No   | Alternate synchronous serial data input/output for I2C1.                         |  |  |  |

| SCL2                                      | I/O         | ST             | No   | Synchronous serial clock input/output for I2C2.                                  |  |  |  |

| SDA2                                      | I/O         | ST             | No   | Synchronous serial data input/output for I2C2.                                   |  |  |  |

| ASCL2                                     | I/O         | ST             | No   | Alternate synchronous serial clock input/output for I2C2.                        |  |  |  |

| ASDA2                                     | I/O         | ST             | No   | Alternate synchronous serial data input/output for I2C2.                         |  |  |  |

| TMS <sup>(5)</sup>                        | Ι           | ST             | No   | JTAG Test mode select pin.                                                       |  |  |  |

| TCK                                       | Ι           | ST             | No   | JTAG test clock input pin.                                                       |  |  |  |

| TDI                                       | I           | ST             | No   | JTAG test data input pin.                                                        |  |  |  |

| TDO                                       | 0           | _              | No   | JTAG test data output pin.                                                       |  |  |  |

| C1RX <sup>(2)</sup>                       | Ι           | ST             | Yes  | ECAN1 bus receive pin.                                                           |  |  |  |

| C1TX <sup>(2)</sup>                       | 0           | _              | Yes  | ECAN1 bus transmit pin.                                                          |  |  |  |

| FLT1 <sup>(1)</sup> , FLT2 <sup>(1)</sup> | Ι           | ST             | Yes  | PWM Fault Inputs 1 and 2.                                                        |  |  |  |

| FLT3 <sup>(1)</sup> , FLT4 <sup>(1)</sup> | Ι           | ST             | No   | PWM Fault Inputs 3 and 4.                                                        |  |  |  |

| FLT32 <sup>(1,3)</sup>                    | Ι           | ST             | No   | PWM Fault Input 32 (Class B Fault).                                              |  |  |  |

| DTCMP1-DTCMP3 <sup>(1)</sup>              | Ι           | ST             | Yes  | PWM Dead-Time Compensation Inputs 1 through 3.                                   |  |  |  |

| PWM1L-PWM3L <sup>(1)</sup>                | 0           | —              | No   | PWM Low Outputs 1 through 3.                                                     |  |  |  |

| PWM1H-PWM3H <sup>(1)</sup>                | 0           | —              | No   | PWM High Outputs 1 through 3.                                                    |  |  |  |

| SYNCI1 <sup>(1)</sup>                     | Ι           | ST             |      | PWM Synchronization Input 1.                                                     |  |  |  |

| SYNCO1 <sup>(1)</sup>                     | 0           |                | Yes  | PWM Synchronization Output 1.                                                    |  |  |  |

| INDX1 <sup>(1)</sup>                      | Ι           | ST             | Yes  | Quadrature Encoder Index1 pulse input.                                           |  |  |  |

| HOME1 <sup>(1)</sup>                      | Ι           | ST             | Yes  | Quadrature Encoder Home1 pulse input.                                            |  |  |  |

| QEA1 <sup>(1)</sup>                       | Ι           | ST             | Yes  | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer                   |  |  |  |

| QEB1 <sup>(1)</sup>                       | ,           | ст             | Vee  | external clock/gate input in Timer mode.                                         |  |  |  |

|                                           | Ι           | ST             | Yes  | Quadrature Encoder Phase B input in QEI1 mode. Auxiliary timer                   |  |  |  |

| CNTCMP1 <sup>(1)</sup>                    | 0           |                | Yes  | external clock/gate input in Timer mode.<br>Quadrature Encoder Compare Output 1. |  |  |  |

|                                           | 0           | <br>ompatible  | 162  |                                                                                  |  |  |  |

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend:

CMOS = CMOS compatible input or output

Analog = Analog input

ST = Schmitt Trigger input with CMOS levels

O = Output

PPS = Peripheral Pin Select

TTL = TTL input buffer

P = Power I = Input

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

5: There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

| Pin Name <sup>(4)</sup>       | Pin<br>Type | Buffer<br>Type | PPS     | Description                                                                                     |  |  |  |

|-------------------------------|-------------|----------------|---------|-------------------------------------------------------------------------------------------------|--|--|--|

| C1IN1-                        | I           | Analog         | No      | Op Amp/Comparator 1 Negative Input 1.                                                           |  |  |  |

| C1IN2-                        | I           | Analog         | No      | Comparator 1 Negative Input 2.                                                                  |  |  |  |

| C1IN1+                        | I           | Analog         | No      | Op Amp/Comparator 1 Positive Input 1.                                                           |  |  |  |

| OA1OUT                        | 0           | Analog         | No      | Op Amp 1 output.                                                                                |  |  |  |

| C1OUT                         | 0           | —              | Yes     | Comparator 1 output.                                                                            |  |  |  |

| C2IN1-                        | I           | Analog         | No      | Op Amp/Comparator 2 Negative Input 1.                                                           |  |  |  |

| C2IN2-                        | I           | Analog         | No      | Comparator 2 Negative Input 2.                                                                  |  |  |  |

| C2IN1+                        | I           | Analog         | No      | Op Amp/Comparator 2 Positive Input 1.                                                           |  |  |  |

| OA2OUT                        | 0           | Analog         | No      | Op Amp 2 output.                                                                                |  |  |  |

| C2OUT                         | 0           |                | Yes     | Comparator 2 output.                                                                            |  |  |  |

| C3IN1-                        | I           | Analog         | No      | Op Amp/Comparator 3 Negative Input 1.                                                           |  |  |  |

| C3IN2-                        | I           | Analog         | No      | Comparator 3 Negative Input 2.                                                                  |  |  |  |

| C3IN1+                        | I           | Analog         | No      | Op Amp/Comparator 3 Positive Input 1.                                                           |  |  |  |

| OA3OUT                        | 0           | Analog         | No      | Op Amp 3 output.                                                                                |  |  |  |

| C3OUT                         | 0           |                | Yes     | Comparator 3 output.                                                                            |  |  |  |

| C4IN1-                        | I.          | Analog         | No      | Comparator 4 Negative Input 1.                                                                  |  |  |  |

| C4IN1+                        | I.          | Analog         | No      | Comparator 4 Positive Input 1.                                                                  |  |  |  |

| C4OUT                         | 0           |                | Yes     | Comparator 4 output.                                                                            |  |  |  |

| CVREF10                       | 0           | Analog         | No      | Op amp/comparator voltage reference output.                                                     |  |  |  |

| CVREF20                       | 0           | Analog         | No      | Op amp/comparator voltage reference divided by 2 output.                                        |  |  |  |

| PGED1                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 1.                                 |  |  |  |

| PGEC1                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 1.                              |  |  |  |

| PGED2                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 2.                                 |  |  |  |

| PGEC2                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 2.                              |  |  |  |

| PGED3                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 3.                                 |  |  |  |

| PGEC3                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 3.                              |  |  |  |

| MCLR                          | I/P         | ST             | No      | Master Clear (Reset) input. This pin is an active-low Reset to the device.                      |  |  |  |

| AVDD                          | Р           | Р              | No      | Positive supply for analog modules. This pin must be connected at all times.                    |  |  |  |

| AVss                          | Р           | Р              | No      | Ground reference for analog modules. This pin must be connected at all times.                   |  |  |  |

| Vdd                           | Р           |                | No      | Positive supply for peripheral logic and I/O pins.                                              |  |  |  |

| VCAP                          | Р           |                | No      | CPU logic filter capacitor connection.                                                          |  |  |  |

| Vss                           | Р           |                | No      | Ground reference for logic and I/O pins.                                                        |  |  |  |

| VREF+                         | 1           | Analog         | No      | Analog voltage reference (high) input.                                                          |  |  |  |

| VREF-                         | Ι           | Analog         | No      | Analog voltage reference (low) input.                                                           |  |  |  |

| Legend: CMOS = C<br>ST = Schn | nitt Trigg  | jer input v    | with CI | or output     Analog = Analog input     P = Power       MOS levels     O = Output     I = Input |  |  |  |

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

PPS = Peripheral Pin Select

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

TTL = TTL input buffer

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

## 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz <  $F_{IN}$  < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

## 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

## 2.9 Application Examples

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- · Automotive HVAC, cooling fans, fuel pumps

- Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- Speech (playback, hands-free kits, answering machines, VoIP)

- Consumer audio

- Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- Data storage device management

- · Smart cards and smart card readers

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

## FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

#### **TABLE 4-3**: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| TADLL        | τу.   |        |        |            | VELEN  |        |        |                                  |        |             |            | DEVICE      |         |             |             |              |         |               |

|--------------|-------|--------|--------|------------|--------|--------|--------|----------------------------------|--------|-------------|------------|-------------|---------|-------------|-------------|--------------|---------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9                            | Bit 8  | Bit 7       | Bit 6      | Bit 5       | Bit 4   | Bit 3       | Bit 2       | Bit 1        | Bit 0   | All<br>Resets |

| IFS0         | 0800  |        | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF                          | T3IF   | T2IF        | OC2IF      | IC2IF       | DMA0IF  | T1IF        | OC1IF       | IC1IF        | INTOIF  | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF                            | DMA2IF | _           | _          | —           | INT1IF  | CNIF        | CMIF        | MI2C1IF      | SI2C1IF | 0000          |

| IFS2         | 0804  |        | _      | _          | -      |        | _      | —                                | _      | _           | IC4IF      | IC3IF       | DMA3IF  | _           | —           | SPI2IF       | SPI2EIF | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | _      | _      | _                                | _      | _           | _          | _           | _       | _           | MI2C2IF     | SI2C2IF      | _       | 0000          |

| IFS4         | 0808  | _      | _      | CTMUIF     | _      | _      | _      | _                                | _      | _           | _          | _           | _       | CRCIF       | U2EIF       | U1EIF        | _       | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  | _          | _      | _      | _      | —                                | —      | _           | _          | _           | _       | _           | —           | —            | —       | 0000          |

| IFS9         | 0812  | _      | _      | _          | _      | _      | _      | —                                | —      | _           | PTG3IF     | PTG2IF      | PTG1IF  | PTG0IF      | PTGWDTIF    | PTGSTEPIF    | _       | 0000          |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE                          | T3IE   | T2IE        | OC2IE      | IC2IE       | DMA0IE  | T1IE        | OC1IE       | IC1IE        | INT0IE  | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE                            | DMA2IE | _           | _          | _           | INT1IE  | CNIE        | CMIE        | MI2C1IE      | SI2C1IE | 0000          |

| IEC2         | 0824  | _      | _      | _          | _      | _      | _      | _                                | _      | _           | IC4IE      | IC3IE       | DMA3IE  | _           | _           | SPI2IE       | SPI2EIE | 0000          |

| IEC3         | 0826  | _      | _      | _          | _      | _      | _      | —                                | —      | _           | _          | _           | _       | _           | MI2C2IE     | SI2C2IE      | —       | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     | _      | _      | _      | _                                | _      | _           | _          | _           | _       | CRCIE       | U2EIE       | U1EIE        | _       | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | _      | _      | _      | _                                | _      | _           | _          | _           | _       | _           | _           | _            | _       | 0000          |

| IEC9         | 0832  | _      | _      | _          | _      | _      | _      | —                                | —      | _           | PTG3IE     | PTG2IE      | PTG1IE  | PTG0IE      | PTGWDTIE    | PTGSTEPIE    | _       | 0000          |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      | (      | OC1IP<2:0> — IC1IP<2:0> — INT0IP |        | INT0IP<2:0> |            | 4444        |         |             |             |              |         |               |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |        | _      | (      | OC2IP<2:0                        | >      | _           |            | IC2IP<2:0>  |         | _           | C           | 0MA0IP<2:0>  |         | 4444          |

| IPC2         | 0844  | _      | U      | J1RXIP<2:0 | >      | _      | ;      | SPI1IP<2:0                       | >      | _           |            | SPI1EIP<2:0 | >       | _           |             | T3IP<2:0>    |         | 4444          |

| IPC3         | 0846  | _      | _      | _          | _      | _      | D      | )MA1IP<2:                        | 0>     | _           | AD1IP<2:0> |             | _       | U1TXIP<2:0> |             | 0444         |         |               |

| IPC4         | 0848  |        |        | CNIP<2:0>  |        |        |        | CMIP<2:0                         | >      | _           |            | MI2C1IP<2:0 | >       | _           | S           | SI2C1IP<2:0> |         | 4444          |

| IPC5         | 084A  | _      | _      | _          | _      | _      | _      | _                                | _      | _           | _          | —           | _       | _           | I           | INT1IP<2:0>  |         | 0004          |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      | (      | OC4IP<2:0                        | >      | _           |            | OC3IP<2:0>  |         | _           | DMA2IP<2:0> |              | 4444    |               |

| IPC7         | 084E  |        | I      | U2TXIP<2:0 | >      |        | L      | J2RXIP<2:                        | )>     | _           |            | INT2IP<2:0> |         | _           |             | T5IP<2:0>    |         | 4444          |

| IPC8         | 0850  |        | _      | _          | _      |        | _      | —                                | —      | _           |            | SPI2IP<2:0> |         | _           | S           | SPI2EIP<2:0> |         | 0044          |

| IPC9         | 0852  |        | _      | _          | _      |        |        | IC4IP<2:0                        | >      | _           |            | IC3IP<2:0>  |         | _           | C           | 0MA3IP<2:0>  |         | 0444          |

| IPC12        | 0858  |        | _      | _          | _      |        | N      | 112C2IP<2:                       | 0>     | _           |            | SI2C2IP<2:0 | >       | _           | _           | _            | _       | 0440          |

| IPC16        | 0860  |        |        | CRCIP<2:0> | >      |        |        | U2EIP<2:0                        | >      | _           |            | U1EIP<2:0>  |         | _           | _           | _            | _       | 4440          |

| IPC19        | 0866  |        | _      | _          | _      | _      | _      | _                                | _      | _           |            | CTMUIP<2:0  | >       | _           | _           | _            | _       | 0040          |

| IPC35        | 0886  |        |        | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0                        | >      | _           | _          | _           | _       | _           | _           | _            | _       | 4400          |

| IPC36        | 0888  | _      |        | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<                          | 2:0>   | _           | P          | TGSTEPIP<2  | :0>     | _           | _           | —            | _       | 4440          |

| IPC37        | 088A  | _      | _      | _          | _      | _      | F      | PTG3IP<2:                        | )>     | _           |            | PTG2IP<2:0  | >       | _           | F           | PTG1IP<2:0>  |         | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | _      |        |        |                                  | —      | _           | DIV0ERR    | DMACERR     | MATHERR | ADDRERR     | STKERR      | OSCFAIL      |         | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      |        |        |                                  | _      | _           |            | —           | —       | _           | INT2EP      | INT1EP       | INT0EP  | 8000          |

| INTCON3      | 08C4  | _      | _      |            | _      |        |        | _                                | _      | _           | _          | DAE         | DOOVR   | _           | _           | —            |         | 0000          |

| INTCON4      | 08C6  |        | _      | _          | _      | _      | _      | —                                | _      | _           | _          | _           | _       | _           | _           |              | SGHT    | 0000          |

| INTTREG      | 08C8  | _      |        |            | _      |        | ILR<   | 3:0>                             |        |             |            |             | VECN    | UM<7:0>     |             |              |         | 0000          |

|              |       |        |        |            |        |        |        |                                  |        |             |            |             |         |             |             |              |         |               |

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

| R/W-1        | R/W-0                                                                                      | R/W-0                                                             | U-0          | U-0              | U-0              | U-0             | U-0    |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------|------------------|------------------|-----------------|--------|--|--|--|--|

| GIE          | DISI                                                                                       | SWTRAP                                                            |              |                  |                  | _               |        |  |  |  |  |

| bit 15       |                                                                                            |                                                                   |              |                  |                  |                 | bit 8  |  |  |  |  |

|              |                                                                                            |                                                                   |              |                  |                  |                 |        |  |  |  |  |

| U-0          | U-0                                                                                        | U-0                                                               | U-0          | U-0              | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

|              | —                                                                                          |                                                                   |              |                  | INT2EP           | INT1EP          | INT0EP |  |  |  |  |

| bit 7        |                                                                                            |                                                                   |              |                  |                  |                 | bit C  |  |  |  |  |

| Legend:      |                                                                                            |                                                                   |              |                  |                  |                 |        |  |  |  |  |

| R = Readab   | le bit                                                                                     | W = Writable                                                      | bit          | U = Unimpler     | mented bit, read | l as '0'        |        |  |  |  |  |

| -n = Value a |                                                                                            | '1' = Bit is set                                                  |              | '0' = Bit is cle |                  | x = Bit is unki | nown   |  |  |  |  |

|              |                                                                                            |                                                                   |              |                  |                  |                 |        |  |  |  |  |

| bit 15       | GIE: Global                                                                                | Interrupt Enable                                                  | e bit        |                  |                  |                 |        |  |  |  |  |

|              | 1 = Interrupt                                                                              | 1 = Interrupts and associated IE bits are enabled                 |              |                  |                  |                 |        |  |  |  |  |

|              |                                                                                            | s are disabled, I                                                 | •            | still enabled    |                  |                 |        |  |  |  |  |

| bit 14       | DISI: DISI                                                                                 | DISI: DISI Instruction Status bit                                 |              |                  |                  |                 |        |  |  |  |  |

|              | 1 = DISI instruction is active<br>0 = DISI instruction is not active                       |                                                                   |              |                  |                  |                 |        |  |  |  |  |

| bit 13       | SWTRAP: S                                                                                  | SWTRAP: Software Trap Status bit                                  |              |                  |                  |                 |        |  |  |  |  |

|              |                                                                                            | e trap is enabled<br>e trap is disabled                           |              |                  |                  |                 |        |  |  |  |  |

| bit 12-3     | Unimpleme                                                                                  | nted: Read as '                                                   | 0'           |                  |                  |                 |        |  |  |  |  |

| bit 2        | INT2EP: Ext                                                                                | ternal Interrupt 2                                                | 2 Edge Detec | t Polarity Selec | t bit            |                 |        |  |  |  |  |

|              | <ul> <li>1 = Interrupt on negative edge</li> <li>0 = Interrupt on positive edge</li> </ul> |                                                                   |              |                  |                  |                 |        |  |  |  |  |

| bit 1        | INT1EP: Ext                                                                                | <b>T1EP:</b> External Interrupt 1 Edge Detect Polarity Select bit |              |                  |                  |                 |        |  |  |  |  |

|              |                                                                                            | on negative edg                                                   |              |                  |                  |                 |        |  |  |  |  |

| bit 0        | INTOEP: Ext                                                                                | ternal Interrupt C                                                | Edge Detec   | t Polarity Selec | t bit            |                 |        |  |  |  |  |

|              |                                                                                            | on negative edg                                                   |              |                  |                  |                 |        |  |  |  |  |

### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

## 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

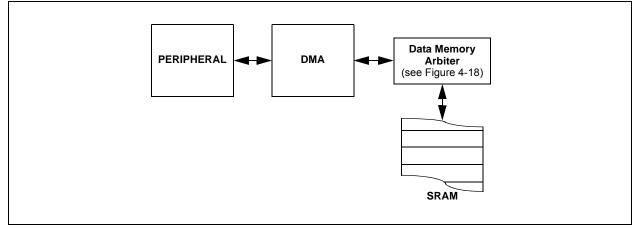

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM

In addition, DMA can access the entire data memory space. The Data Memory Bus Arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. Some of the peripherals supported by the DMA Controller include:

- ECAN<sup>™</sup>

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

## FIGURE 8-1: DMA CONTROLLER MODULE

In addition, DMA transfers can be triggered by timers as well as external interrupts. Each DMA channel is unidirectional. Two DMA channels must be allocated to read and write to a peripheral. If more than one channel receives a request to transfer data, a simple fixed priority scheme based on channel number, dictates which channel completes the transfer and which channel, or channels, are left pending. Each DMA channel moves a block of data, after which, it generates an interrupt to the CPU to indicate that the block is available for processing.

The DMA Controller provides these functional capabilities:

- Four DMA channels

- Register Indirect with Post-Increment Addressing mode

- Register Indirect without Post-Increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU interrupt after half or full block transfer complete

- Byte or word transfers

- · Fixed priority channel arbitration

- Manual (software) or automatic (peripheral DMA requests) transfer initiation

- One-Shot or Auto-Repeat Block Transfer modes

- Ping-Pong mode (automatic switch between two SRAM start addresses after each block transfer is complete)

- DMA request for each channel can be selected from any supported interrupt source

- Debug support features

The peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |

|-------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| INT0 – External Interrupt 0   | 00000000                             | _                                                       | _                                                      |

| IC1 – Input Capture 1         | 0000001                              | 0x0144 (IC1BUF)                                         | —                                                      |

| IC2 – Input Capture 2         | 00000101                             | 0x014C (IC2BUF)                                         | —                                                      |

| IC3 – Input Capture 3         | 00100101                             | 0x0154 (IC3BUF)                                         | —                                                      |

| IC4 – Input Capture 4         | 00100110                             | 0x015C (IC4BUF)                                         | —                                                      |

| OC1 – Output Compare 1        | 0000010                              | _                                                       | 0x0906 (OC1R)<br>0x0904 (OC1RS)                        |

| OC2 – Output Compare 2        | 00000110                             | _                                                       | 0x0910 (OC2R)<br>0x090E (OC2RS)                        |

| OC3 – Output Compare 3        | 00011001                             | _                                                       | 0x091A (OC3R)<br>0x0918 (OC3RS)                        |

| OC4 – Output Compare 4        | 00011010                             | _                                                       | 0x0924 (OC4R)<br>0x0922 (OC4RS)                        |

| TMR2 – Timer2                 | 00000111                             | —                                                       | _                                                      |

| TMR3 – Timer3                 | 00001000                             | —                                                       | _                                                      |

| TMR4 – Timer4                 | 00011011                             | —                                                       | _                                                      |

| TMR5 – Timer5                 | 00011100                             | —                                                       | —                                                      |

| SPI1 Transfer Done            | 00001010                             | 0x0248 (SPI1BUF)                                        | 0x0248 (SPI1BUF)                                       |

| SPI2 Transfer Done            | 00100001                             | 0x0268 (SPI2BUF)                                        | 0x0268 (SPI2BUF)                                       |

| UART1RX – UART1 Receiver      | 00001011                             | 0x0226 (U1RXREG)                                        | —                                                      |

| UART1TX – UART1 Transmitter   | 00001100                             | —                                                       | 0x0224 (U1TXREG)                                       |

| UART2RX – UART2 Receiver      | 00011110                             | 0x0236 (U2RXREG)                                        |                                                        |

| UART2TX – UART2 Transmitter   | 00011111                             | —                                                       | 0x0234 (U2TXREG)                                       |

| ECAN1 – RX Data Ready         | 00100010                             | 0x0440 (C1RXD)                                          | _                                                      |

| ECAN1 – TX Data Request       | 01000110                             | —                                                       | 0x0442 (C1TXD)                                         |

| ADC1 – ADC1 Convert Done      | 00001101                             | 0x0300 (ADC1BUF0)                                       | —                                                      |

### TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

## REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER (CONTINUED)

| bit 2 | <b>HOMIEN:</b> Home Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled            |

|-------|--------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IDXIRQ:</b> Status Flag for Index Event Status bit<br>1 = Index event has occurred<br>0 = No Index event has occurred |

| bit 0 | <b>IDXIEN:</b> Index Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled           |

Note 1: This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

## REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 6         | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)<br>Used in conjunction with the SCLREL bit.<br>1 = Enables software or receives clock stretching<br>0 = Disables software or receives clock stretching |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5         | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                                     |

|               | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                                       |

| bit 4         | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                   |

|               | <ul> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits ACKDT data bit. Hardware is clear at the end of the master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul>              |

| bit 3         | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                   |

|               | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware is clear at the end of the eighth bit of the master receive data byte.</li> <li>0 = Receive sequence is not in progress</li> </ul>                                             |

| bit 2         | <b>PEN:</b> Stop Condition Enable bit (when operating as $I^2C$ master)                                                                                                                                                                       |

| 511 2         | 1 = Initiates Stop condition on SDAx and SCLx pins. Hardware is clear at the end of the master Stop sequence.                                                                                                                                 |

| <b>h</b> :+ 4 | 0 = Stop condition is not in progress                                                                                                                                                                                                         |

| bit 1         | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                  |

|               | <ul> <li>1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware is clear at the end of the<br/>master Repeated Start sequence.</li> <li>0 = Repeated Start condition is not in progress</li> </ul>                            |

| bit 0         | <b>SEN:</b> Start Condition Enable bit (when operating as $l^2C$ master)                                                                                                                                                                      |

|               | <ul> <li>1 = Initiates Start condition on SDAx and SCLx pins. Hardware is clear at the end of the master Start sequence.</li> <li>0 = Start condition is not in progress</li> </ul>                                                           |

**Note 1:** When performing master operations, ensure that the IPMIEN bit is set to '0'.

| R-0, HSC          | R-0, HSC  | U-0             | U-0        | U-0               | R/C-0, HS        | R-0, HSC                              | R-0, HSC |  |

|-------------------|-----------|-----------------|------------|-------------------|------------------|---------------------------------------|----------|--|

| ACKSTAT           | TRSTAT    | _               | _          | —                 | BCL              | GCSTAT                                | ADD10    |  |

| bit 15            |           |                 |            |                   |                  |                                       | bit 8    |  |

|                   |           |                 |            |                   |                  |                                       |          |  |

| R/C-0, HS         | R/C-0, HS | R-0, HSC        | R/C-0, HSC | R/C-0, HSC        | R-0, HSC         | R-0, HSC                              | R-0, HSC |  |

| IWCOL             | I2COV     | D_A             | Р          | S                 | R_W              | RBF                                   | TBF      |  |

| bit 7             |           |                 |            |                   |                  |                                       | bit 0    |  |

|                   |           |                 |            |                   |                  |                                       |          |  |

| Legend:           |           | C = Clearab     | le bit     | HS = Hardwa       | re Settable bit  | HSC = Hardware Settable/Clearable bit |          |  |

| R = Readable bit  |           | W = Writable    | e bit      | U = Unimplem      | nented bit, read | as '0'                                |          |  |

| -n = Value at POR |           | '1' = Bit is se | et         | '0' = Bit is clea | ared             | x = Bit is unknown                    |          |  |

## REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER

| bit 15       | <b>ACKSTAT:</b> Acknowledge Status bit (when operating as $I^2C^{TM}$ master, applicable to master transmit operation)                         |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10       | 1 = NACK received from slave                                                                                                                   |

|              | 0 = ACK received from slave                                                                                                                    |

|              | Hardware is set or clear at the end of slave Acknowledge.                                                                                      |

| bit 14       | TRSTAT: Transmit Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                               |

|              | 1 = Master transmit is in progress (8 bits + ACK)                                                                                              |

|              | 0 = Master transmit is not in progress                                                                                                         |

|              | Hardware is set at the beginning of master transmission. Hardware is clear at the end of slave Acknowledge.                                    |

| bit 13-11    | Unimplemented: Read as '0'                                                                                                                     |

| bit 10       | BCL: Master Bus Collision Detect bit                                                                                                           |

|              | 1 = A bus collision has been detected during a master operation                                                                                |

|              | 0 = No bus collision detected<br>Hardware is set at detection of a bus collision.                                                              |

| <b>h</b> # 0 |                                                                                                                                                |

| bit 9        | GCSTAT: General Call Status bit                                                                                                                |

|              | 1 = General call address was received<br>0 = General call address was not received                                                             |

|              | Hardware is set when address matches general call address. Hardware is clear at Stop detection.                                                |

| bit 8        | ADD10: 10-Bit Address Status bit                                                                                                               |

|              | 1 = 10-bit address was matched                                                                                                                 |

|              | 0 = 10-bit address was not matched                                                                                                             |

|              | Hardware is set at the match of the 2nd byte of the matched 10-bit address. Hardware is clear at Stop                                          |

|              | detection.                                                                                                                                     |

| bit 7        | IWCOL: I2Cx Write Collision Detect bit                                                                                                         |

|              | <ul> <li>1 = An attempt to write to the I2CxTRN register failed because the I<sup>2</sup>C module is busy</li> <li>0 = No collision</li> </ul> |

|              | Hardware is set at the occurrence of a write to I2CxTRN while busy (cleared by software).                                                      |

| bit 6        | <b>I2COV:</b> I2Cx Receive Overflow Flag bit                                                                                                   |

|              | 1 = A byte was received while the I2CxRCV register was still holding the previous byte                                                         |

|              | 0 = No overflow                                                                                                                                |

|              | Hardware is set at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                            |

| bit 5        | <b>D_A:</b> Data/Address bit (when operating as I <sup>2</sup> C slave)                                                                        |

|              | 1 = Indicates that the last byte received was data                                                                                             |

|              | 0 = Indicates that the last byte received was a device address                                                                                 |

|              | Hardware is clear at a device address match. Hardware is set by reception of a slave byte.                                                     |

| bit 4        | P: Stop bit                                                                                                                                    |

|              | 1 = Indicates that a Stop bit has been detected last                                                                                           |

|              | 0 = Stop bit was not detected last<br>Hardware is set or clear when a Start, Repeated Start or Stop is detected.                               |

|              |                                                                                                                                                |

|              |                                                                                                                                                |

## 21.4 ECAN Control Registers

| U-0             | U-0                                                                                                                        | R/W-0                                                 | R/W-0                                                              | R/W-0                          | R/W-1            | R/W-0           | R/W-0  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------|--------------------------------|------------------|-----------------|--------|--|

| —               | —                                                                                                                          | CSIDL                                                 | ABAT                                                               | CANCKS                         | REQOP2           | REQOP1          | REQOP0 |  |

| bit 15          |                                                                                                                            |                                                       |                                                                    |                                |                  |                 | bit 8  |  |

| R-1             | R-0                                                                                                                        | R-0                                                   | U-0                                                                | R/W-0                          | U-0              | U-0             | R/W-0  |  |

| OPMODE2         | OPMODE1                                                                                                                    | OPMODE0                                               | _                                                                  | CANCAP                         |                  |                 | WIN    |  |

| bit 7           |                                                                                                                            |                                                       |                                                                    |                                |                  |                 | bit (  |  |

| Legend:         |                                                                                                                            |                                                       |                                                                    |                                |                  |                 |        |  |

| R = Readable    | bit                                                                                                                        | W = Writable I                                        | bit                                                                | U = Unimpler                   | mented bit, read | l as '0'        |        |  |

| -n = Value at F | POR                                                                                                                        | '1' = Bit is set                                      |                                                                    | '0' = Bit is cle               | ared             | x = Bit is unkr | nown   |  |

|                 |                                                                                                                            |                                                       |                                                                    |                                |                  |                 |        |  |

| bit 15-14       | -                                                                                                                          | ted: Read as '                                        |                                                                    |                                |                  |                 |        |  |

| bit 13          | 1 = Discontinu                                                                                                             | Ix Stop in Idle I<br>ues module ope<br>module opera   | eration when                                                       | device enters I                | dle mode         |                 |        |  |

| bit 12          |                                                                                                                            | All Pending Tra                                       |                                                                    |                                |                  |                 |        |  |

| Sit 12          | 1 = Signals al                                                                                                             | I transmit buffe                                      | rs to abort tra                                                    |                                | aborted          |                 |        |  |

| bit 11          | CANCKS: EC                                                                                                                 | ANx Module C                                          | lock (FCAN)                                                        | Source Select b                | oit              |                 |        |  |

|                 | 1 = FCAN is equal to 2 * FP<br>0 = FCAN is equal to FP                                                                     |                                                       |                                                                    |                                |                  |                 |        |  |

| bit 10-8        | 111 = Set Lis<br>110 = Reserv<br>101 = Reserv<br>100 = Set Co<br>011 = Set Lis<br>010 = Set Loc<br>001 = Set Dis           | ed<br>nfiguration mod<br>ten Only mode<br>opback mode | es mode<br>de                                                      | bits                           |                  |                 |        |  |

| bit 7-5         | OPMODE<2:(<br>111 = Module<br>110 = Reserv<br>101 = Reserv<br>100 = Module<br>011 = Module<br>010 = Module<br>001 = Module | <b>0&gt;</b> : Operation N<br>is in Listen All<br>ed  | Aode bits<br>Messages n<br>ation mode<br>ly mode<br>c mode<br>node |                                |                  |                 |        |  |

| bit 4           | Unimplemen                                                                                                                 | ted: Read as '                                        | )'                                                                 |                                |                  |                 |        |  |

| bit 3           |                                                                                                                            |                                                       |                                                                    | Capture Event<br>message recei |                  |                 |        |  |

|                 | 0 = Disables (                                                                                                             | •                                                     |                                                                    |                                |                  |                 |        |  |

| bit 2-1         | -                                                                                                                          | ted: Read as '0                                       |                                                                    |                                |                  |                 |        |  |

| bit 0           | WIN: SFR Ma                                                                                                                | p Window Sele                                         | ect bit                                                            |                                |                  |                 |        |  |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|               | 23-2: Al                                                                                                                              |                                        | CONTROL REG                              |                 |                   |                  |              |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------|-----------------|-------------------|------------------|--------------|--|--|--|

| R/W-0         | R/W-                                                                                                                                  | 0 R/W-0                                | U-0                                      | U-0             | R/W-0             | R/W-0            | R/W-0        |  |  |  |

| VCFG2         | VCFO                                                                                                                                  | G1 VCFG0                               | —                                        | _               | CSCNA             | CHPS1            | CHPS0        |  |  |  |

| bit 15        |                                                                                                                                       |                                        |                                          |                 |                   |                  | bit          |  |  |  |

| R-0           | R/W-                                                                                                                                  | 0 R/W-0                                | R/W-0                                    | R/W-0           | R/W-0             | R/W-0            | R/W-0        |  |  |  |

| BUFS          | SMPI                                                                                                                                  |                                        | SMPI2                                    | SMPI1           | SMPI0             | BUFM             | ALTS         |  |  |  |

| bit 7         | Sivil                                                                                                                                 |                                        |                                          |                 |                   | BOTW             | bit          |  |  |  |

| Logondi       |                                                                                                                                       |                                        |                                          |                 |                   |                  |              |  |  |  |

| Legend:       | hit                                                                                                                                   | M/ - Mritabla                          | hit U                                    | - Unimplo       | monted hit read   |                  |              |  |  |  |

| R = Readable  |                                                                                                                                       | W = Writable                           |                                          | •               | mented bit, read  |                  |              |  |  |  |

| -n = Value at | POR                                                                                                                                   | '1' = Bit is set                       | t 'U                                     | )' = Bit is cle | eared             | x = Bit is unkr  | nown         |  |  |  |

| bit 15-13     | VCFG<2                                                                                                                                | 2:0>: Converter Volt                   | age Reference Co                         | onfiguration    | bits              |                  |              |  |  |  |

|               | Value                                                                                                                                 | VREFH                                  | VREFL                                    |                 |                   |                  |              |  |  |  |

|               | 000                                                                                                                                   | Avdd                                   | Avss                                     |                 |                   |                  |              |  |  |  |

|               | 001                                                                                                                                   | External VREF+                         | Avss                                     |                 |                   |                  |              |  |  |  |

|               | 010                                                                                                                                   | Avdd                                   | External VREF-                           |                 |                   |                  |              |  |  |  |

|               | 011                                                                                                                                   | External VREF+                         | External VREF-                           |                 |                   |                  |              |  |  |  |

|               | 1xx                                                                                                                                   | Avdd                                   | Avss                                     |                 |                   |                  |              |  |  |  |

| bit 12-11     | Unimple                                                                                                                               | emented: Read as '                     | ʻ0'                                      |                 |                   |                  |              |  |  |  |

| bit 10        |                                                                                                                                       | : Input Scan Select                    |                                          |                 |                   |                  |              |  |  |  |

|               |                                                                                                                                       | ns inputs for CH0+ of                  |                                          | IXA             |                   |                  |              |  |  |  |

|               |                                                                                                                                       | s not scan inputs                      | gp                                       |                 |                   |                  |              |  |  |  |

| bit 9-8       | CHPS<1:0>: Channel Select bits                                                                                                        |                                        |                                          |                 |                   |                  |              |  |  |  |

|               | In 12-bit mode (AD21B = 1), the CHPS<1:0> bits are Unimplemented and are Read as '0':                                                 |                                        |                                          |                 |                   |                  |              |  |  |  |

|               |                                                                                                                                       | nverts CH0, CH1, C                     |                                          |                 |                   |                  |              |  |  |  |

|               |                                                                                                                                       | nverts CH0 and CH                      | 1                                        |                 |                   |                  |              |  |  |  |

| L:1 7         |                                                                                                                                       | nverts CH0                             | (                                        |                 |                   |                  |              |  |  |  |

| bit 7         | <b>BUFS:</b> Buffer Fill Status bit (only valid when BUFM = 1)                                                                        |                                        |                                          |                 |                   |                  |              |  |  |  |

|               | 1 = ADC is currently filling the second half of the buffer; the user application should access data in th<br>first half of the buffer |                                        |                                          |                 |                   |                  |              |  |  |  |

|               |                                                                                                                                       | C is currently filling                 | the first half of the                    | e buffer; the   | e user applicatio | on should acce   | ss data in t |  |  |  |

|               |                                                                                                                                       | ond half of the buffe                  |                                          | ,               |                   |                  |              |  |  |  |

| bit 6-2       | SMPI<4                                                                                                                                | :0>: Increment Rate                    | e bits                                   |                 |                   |                  |              |  |  |  |

|               | When Al                                                                                                                               | DDMAEN = 0:                            |                                          |                 |                   |                  |              |  |  |  |