#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 8K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128gp202-h-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

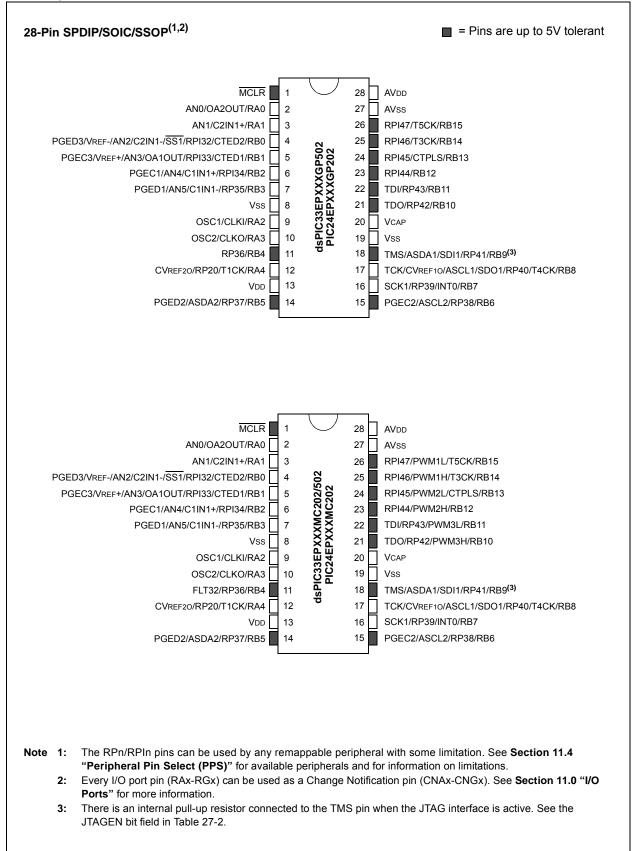

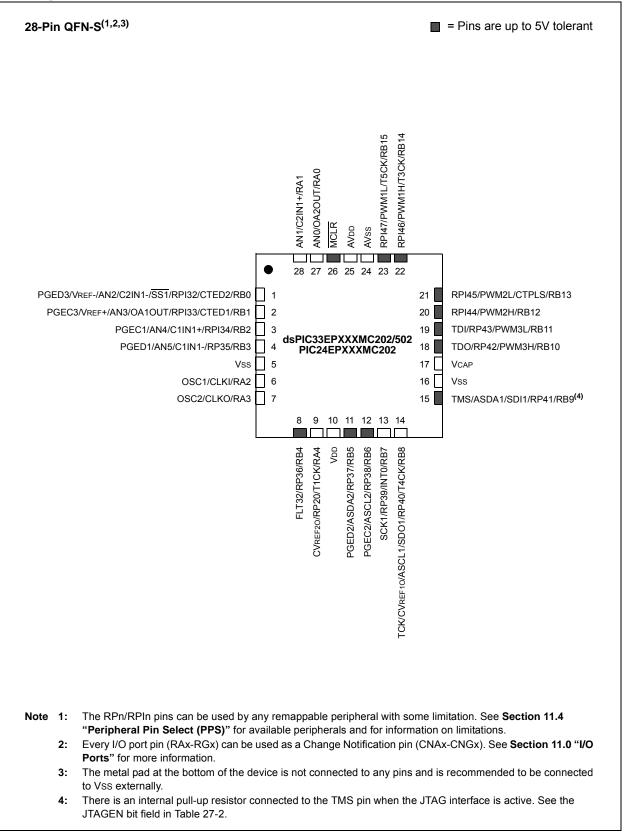

#### **Pin Diagrams**

#### Pin Diagrams (Continued)

## 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS AND MICROCONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual", which is available from the Microchip web site (www.microchip.com)

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

## 2.1 Basic Connection Requirements

Getting started with the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

(see Section 2.2 "Decoupling Capacitors")

• VCAP

(see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for the ADC module is implemented

Note: The AVDD and AVSS pins must be connected, independent of the ADC voltage reference source.

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, above tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of  $0.01 \ \mu\text{F}$  to  $0.001 \ \mu\text{F}$ . Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example,  $0.1 \ \mu\text{F}$  in parallel with  $0.001 \ \mu\text{F}$ .

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

#### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz <  $F_{IN}$  < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

## 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

#### 2.9 Application Examples

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- · Automotive HVAC, cooling fans, fuel pumps

- Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- Speech (playback, hands-free kits, answering machines, VoIP)

- Consumer audio

- Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- Data storage device management

- · Smart cards and smart card readers

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

#### FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6  | Bit 5          | Bit 4  | Bit 3  | Bit 2    | Bit 1       | Bit 0         | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|-------|--------|----------------|--------|--------|----------|-------------|---------------|---------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF  | IC2IF          | DMA0IF | T1IF   | OC1IF    | IC1IF       | <b>INTOIF</b> | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _      | _              | INT1IF | CNIF   | CMIF     | MI2C1IF     | SI2C1IF       | 0000          |

| IFS2         | 0804  | _      | _      | _          | _      | —      |        | _          | —      | _     | IC4IF  | IC3IF          | DMA3IF | C1IF   | C1RXIF   | SPI2IF      | SPI2EIF       | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | —      |        | _          | —      | _     | _      | _              | —      | _      | MI2C2IF  | SI2C2IF     | —             | 0000          |

| IFS4         | 0808  | _      | _      | CTMUIF     | _      | —      |        | _          | —      | _     | C1TXIF | _              | —      | CRCIF  | U2EIF    | U1EIF       | —             | 0000          |

| IFS6         | 080C  | _      | _      | _          | _      | —      |        | _          | —      | _     | _      | _              | —      | _      | —        | _           | PWM3IF        | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  | —          | _      | —      |        | _          | —      | _     | _      | _              | —      | _      | —        | _           | —             | 0000          |

| IFS9         | 0812  |        |        | _          | _      | _      | _      | _          | _      | _     | PTG3IF | PTG2IF         | PTG1IF | PTG0IF | PTGWDTIF | PTGSTEPIF   | _             | 0000          |

| IEC0         | 0820  |        | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE  | IC2IE          | DMA0IE | T1IE   | OC1IE    | IC1IE       | INT0IE        | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | _     | _      | _              | INT1IE | CNIE   | CMIE     | MI2C1IE     | SI2C1IE       | 0000          |

| IEC2         | 0824  |        |        | _          | _      | _      | _      | _          | _      | _     | IC4IE  | IC3IE          | DMA3IE | C1IE   | C1RXIE   | SPI2IE      | SPI2EIE       | 0000          |

| IEC3         | 0826  | _      | _      | —          | —      |        | _      |            | _      | _     | _      |                |        | —      | MI2C2IE  | SI2C2IE     | _             | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     | —      |        |        |            | _      | —     | C1TXIE |                |        | CRCIE  | U2EIE    | U1EIE       |               | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | —          | —      |        | _      |            | _      | _     | _      |                |        | —      | _        | _           | _             | 0000          |

| IEC9         | 0832  | _      | _      | —          | —      |        | _      |            | _      | _     | PTG3IE | PTG2IE         | PTG1IE | PTG0IE | PTGWDTIE | PTGSTEPIE   | _             | 0000          |

| IPC0         | 0840  |        |        | T1IP<2:0>  | >      | _      | (      | OC1IP<2:0  | >      | _     |        | IC1IP<2:0>     |        | _      |          | NT0IP<2:0>  |               | 4444          |

| IPC1         | 0842  |        |        | T2IP<2:0>  | >      | _      | (      | C2IP<2:0   | >      | _     |        | IC2IP<2:0>     |        | _      | D        | MA0IP<2:0>  |               | 4444          |

| IPC2         | 0844  |        | ι      | J1RXIP<2:0 | 0>     | _      | Ş      | SPI1IP<2:0 | )>     | _     |        | SPI1EIP<2:0    | >      | _      |          | T3IP<2:0>   |               | 4444          |

| IPC3         | 0846  |        |        | _          | _      | _      | C      | MA1IP<2:   | 0>     | _     |        | AD1IP<2:0>     |        | _      | U        | J1TXIP<2:0> |               | 0444          |

| IPC4         | 0848  |        |        | CNIP<2:0   | >      | _      |        | CMIP<2:0   | >      | _     | I      | WI2C1IP<2:0    | >      | _      | S        | I2C1IP<2:0> |               | 4444          |

| IPC5         | 084A  |        |        | _          | _      | _      | _      | _          | _      | _     | _      | _              | _      | _      |          | NT1IP<2:0>  |               | 0004          |

| IPC6         | 084C  |        |        | T4IP<2:0>  | >      | _      | (      | C4IP<2:0   | >      | _     |        | OC3IP<2:0>     |        | _      | D        | MA2IP<2:0>  |               | 4444          |

| IPC7         | 084E  |        | ι      | U2TXIP<2:0 | )>     | _      | L      | I2RXIP<2:  | 0>     | _     |        | INT2IP<2:0>    | •      | _      |          | T5IP<2:0>   |               | 4444          |

| IPC8         | 0850  |        |        | C1IP<2:0>  | >      | _      | C      | 1RXIP<2:   | 0>     | _     |        | SPI2IP<2:0>    | •      | _      | S        | PI2EIP<2:0> |               | 4444          |

| IPC9         | 0852  | _      | _      | _          | _      | _      |        | IC4IP<2:0  | >      | _     |        | IC3IP<2:0>     |        | _      | D        | MA3IP<2:0>  |               | 0444          |

| IPC11        | 0856  | _      | _      | _          | _      | _      |        | _          | —      | _     | _      | _              | —      | _      | _        | _           | _             | 0000          |

| IPC12        | 0858  | _      | _      | _          | _      | _      | N      | II2C2IP<2: | 0>     | _     |        | SI2C2IP<2:0    | >      | _      | _        | _           | _             | 0440          |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | )>     | _      |        | U2EIP<2:0  | >      | _     |        | U1EIP<2:0>     |        | _      | _        | _           | _             | 4440          |

| IPC17        | 0862  | _      | _      | _          | _      | _      | C      | 1TXIP<2:   | )>     | _     | _      | _              | —      | _      | _        | _           | _             | 0400          |

| IPC19        | 0866  | _      | _      | —          | _      | _      |        | _          | —      | _     |        | CTMUIP<2:0     | >      | _      | —        |             |               | 0040          |

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | )>     | _      |        | ICDIP<2:0  | >      | _     | _      | —              | _      | _      | —        | _           | _             | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:  | 0>     | _      | PT     | GWDTIP<    | 2:0>   | _     | PT     | PTGSTEPIP<2:0> |        | _      | _        | _           | _             | 4440          |

| IPC37        | 088A  | _      | _      | _          | _      | _      | F      | TG3IP<2:   | )>     | _     |        | PTG2IP<2:0     | >      | _      | Р        | TG1IP<2:0>  |               | 0444          |

#### TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4   | 4-9:  | INPUT  |                                     | JRE 1 T | HROUG  | H INPU    | Т САРТ | URE 4 | REGIST       | ER MA        | Р        |       |       |       |          |          |       |               |

|-----------|-------|--------|-------------------------------------|---------|--------|-----------|--------|-------|--------------|--------------|----------|-------|-------|-------|----------|----------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14                              | Bit 13  | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8        | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2    | Bit 1    | Bit 0 | All<br>Resets |

| IC1CON1   | 0140  | _      | —                                   | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | -            | —            | ICI<     | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC1CON2   | 0142  | _      | IC32 ICTRIG TRIGSTAT - SYNCSEL<4:0> |         |        |           |        |       |              |              | 000D     |       |       |       |          |          |       |               |

| IC1BUF    | 0144  |        |                                     |         |        |           |        | Inp   | ut Capture ' | 1 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC1TMR    | 0146  |        |                                     |         |        |           |        |       | Input Capt   | ture 1 Time  | r        |       |       |       |          |          |       | 0000          |

| IC2CON1   | 0148  |        | —                                   | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC2CON2   | 014A  |        | —                                   |         |        |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC2BUF    | 014C  |        |                                     |         |        |           |        | Inp   | ut Capture 2 | 2 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC2TMR    | 014E  |        |                                     |         |        |           |        |       | Input Capt   | ture 2 Time  | r        |       |       |       |          |          |       | 0000          |

| IC3CON1   | 0150  |        | —                                   | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC3CON2   | 0152  |        | —                                   |         |        |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC3BUF    | 0154  |        |                                     |         |        |           |        | Inp   | ut Capture 3 | 3 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC3TMR    | 0156  |        |                                     |         |        |           |        |       | Input Capt   | ture 3 Time  | r        |       |       |       |          |          |       | 0000          |

| IC4CON1   | 0158  |        | —                                   | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC4CON2   | 015A  | _      | _                                   |         | -      |           | -      | _     | IC32         | ICTRIG       | TRIGSTAT | -     |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC4BUF    | 015C  |        | Input Capture 4 Buffer Register     |         |        |           |        |       |              |              | xxxx     |       |       |       |          |          |       |               |

| IC4TMR    | 015E  |        |                                     |         |        |           |        |       | Input Capt   | ure 4 Time   | r        |       |       |       |          |          |       | 0000          |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-37: PMD REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | _     | _     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      |       | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  |        | _      | _      | —      | _      | CMPMD  | _     | -     | CRCMD  | _     |       |        |        | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  |        | _      | _      | —      | _      |        | _     | -     | —      | _     |       |        | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  |        | —      |        | —      | _      |        | _     |       | —      | _     |       |        |        | —      | —      |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  | _      |        |        | _      |        |        |       |       |        |       |       | DMA1MD | PTGMD  | _      |        |       | 0000          |

|              | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-38: PMD REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  |        | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      |        | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | —      | _      | _      |        |        | PWM3MD | PWM2MD | PWM1MD | _      | —     | —     | _      |        | —      | _      |       | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

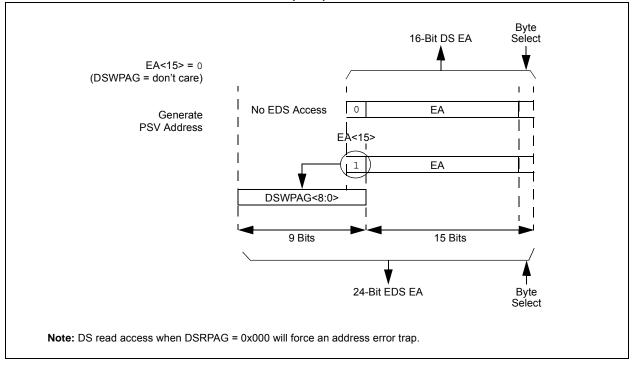

#### EXAMPLE 4-2: EXTENDED DATA SPACE (EDS) WRITE ADDRESS GENERATION

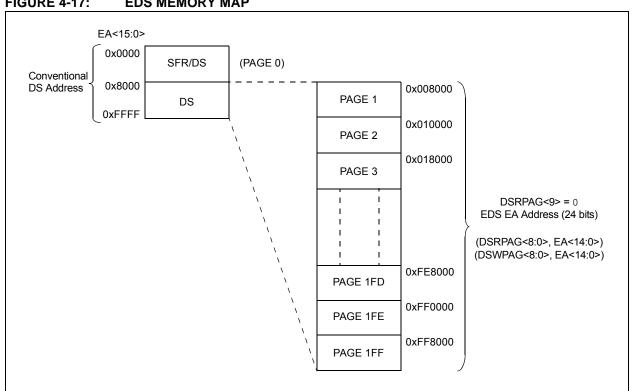

The paged memory scheme provides access to multiple 32-Kbyte windows in the EDS and PSV memory. The Data Space Page registers, DSxPAG, in combination with the upper half of the Data Space address, can provide up to 16 Mbytes of additional address space in the EDS and 8 Mbytes (DSRPAG only) of PSV address space. The paged data memory space is shown in Example 4-3.

The Program Space (PS) can be accessed with a DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG. Writes to PS are not supported, so DSWPAG is dedicated to DS, including EDS only. The Data Space and EDS can be read from, and written to, using DSRPAG and DSWPAG, respectively.

#### 4.4.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x7FFF, is always accessible regardless of the contents of the Data Space Page registers. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, DSRPAG and DSWPAG are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSxPAG in software has no effect.

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where base address bit, EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF, of the Data Space will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-17.

For more information on the PSV page access using Data Space Page registers, refer to the "**Program Space Visibility from Data Space**" section in "**Program Memory**" (DS70613) of the "*dsPIC33/ PIC24 Family Reference Manual*".

#### FIGURE 4-17: EDS MEMORY MAP

## 4.6 Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

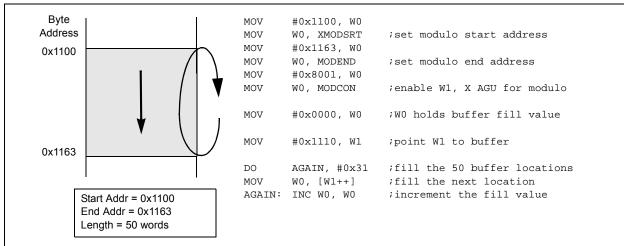

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

#### 4.6.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified, and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

| Note: | Y space Modulo Addressing EA calcula- |

|-------|---------------------------------------|

|       | tions assume word-sized data (LSb of  |

|       | every EA is always clear).            |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.6.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W register (YWM), to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit is set at MODCON<14>.

#### FIGURE 4-20: MODULO ADDRESSING OPERATION EXAMPLE

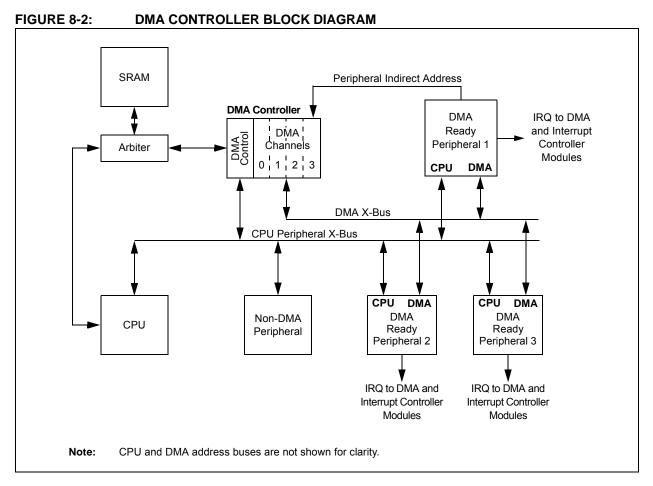

## 8.1 DMA Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 8.1.1 KEY RESOURCES

- Section 22. "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 8.2 DMAC Registers

Each DMAC Channel x (where x = 0 through 3) contains the following registers:

- 16-Bit DMA Channel Control register (DMAxCON)

- 16-Bit DMA Channel IRQ Select register (DMAxREQ)

- 32-Bit DMA RAM Primary Start Address register (DMAxSTA)

- 32-Bit DMA RAM Secondary Start Address register (DMAxSTB)

- 16-Bit DMA Peripheral Address register (DMAxPAD)

- 14-Bit DMA Transfer Count register (DMAxCNT)

Additional status registers (DMAPWC, DMARQC, DMAPPS, DMALCA and DSADR) are common to all DMAC channels. These status registers provide information on write and request collisions, as well as on last address and channel access information.

The interrupt flags (DMAxIF) are located in an IFSx register in the interrupt controller. The corresponding interrupt enable control bits (DMAxIE) are located in an IECx register in the interrupt controller, and the corresponding interrupt priority control bits (DMAxIP) are located in an IPCx register in the interrupt controller.

| R/W-0         | R/W-0        | R/W-0                                                 | R/W-0   | R/W-0             | R/W-0                 | R/W-0                | U-0   |

|---------------|--------------|-------------------------------------------------------|---------|-------------------|-----------------------|----------------------|-------|

| T5MD          | T4MD         | T3MD                                                  | T2MD    | T1MD              | QEI1MD <sup>(1)</sup> | PWMMD <sup>(1)</sup> |       |

| bit 15        |              |                                                       |         |                   |                       |                      | bit   |

|               |              |                                                       |         |                   |                       |                      |       |

| R/W-0         | R/W-0        | R/W-0                                                 | R/W-0   | R/W-0             | U-0                   | R/W-0                | R/W-0 |

| I2C1MD        | U2MD         | U1MD                                                  | SPI2MD  | SPI1MD            | —                     | C1MD <sup>(2)</sup>  | AD1MD |

| bit 7         |              |                                                       |         |                   |                       |                      | bit   |

| Legend:       |              |                                                       |         |                   |                       |                      |       |

| R = Readabl   | e bit        | W = Writable                                          | bit     | U = Unimplen      | nented bit, read      | d as '0'             |       |

| -n = Value at | POR          | '1' = Bit is set                                      |         | '0' = Bit is clea | ared                  | x = Bit is unkno     | own   |

| bit 15        | 1 = Timer5 m | 5 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 14        | 1 = Timer4 m | 4 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 13        | 1 = Timer3 m | 3 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 12        | 1 = Timer2 m | 2 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 11        | 1 = Timer1 m | 1 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 10        | 1 = QEI1 mod | 1 Module Disa<br>lule is disabled<br>lule is enabled  |         |                   |                       |                      |       |

| bit 9         | 1 = PWM mod  | /M Module Disa<br>dule is disabled<br>dule is enabled | 1       |                   |                       |                      |       |

| bit 8         | Unimplemen   | ted: Read as '                                        | כ'      |                   |                       |                      |       |

| bit 7         | 1 = I2C1 mod | 1 Module Disal<br>ule is disabled<br>ule is enabled   | ble bit |                   |                       |                      |       |

| bit 6         | 1 = UART2 m  | 2 Module Disa<br>odule is disabl<br>odule is enable   | ed      |                   |                       |                      |       |

| bit 5         | 1 = UART1 m  | 1 Module Disa<br>odule is disabl<br>odule is enable   | ed      |                   |                       |                      |       |

| bit 4         | 1 = SPI2 mod | 2 Module Disal<br>ule is disabled<br>ule is enabled   | ole bit |                   |                       |                      |       |

#### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This bit is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

#### REGISTER 11-7: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

|                   | R/W-0                                      | R/W-0                                                                      | R/W-0                                        | R/W-0                      | R/W-0           | R/W-0           | R/W-0           |

|-------------------|--------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------|----------------------------|-----------------|-----------------|-----------------|

| _                 |                                            |                                                                            |                                              | FLT2R<6:0>                 |                 |                 |                 |

| bit 15            |                                            |                                                                            |                                              |                            |                 |                 | bit 8           |

|                   | <b>D</b> 444 A                             | <b>D</b> 444 0                                                             | <b>D</b> 444 A                               | Date                       | <b>D</b> 444 0  | D M M A         | <b>D</b> # 44 0 |

| U-0               | R/W-0                                      | R/W-0                                                                      | R/W-0                                        | R/W-0                      | R/W-0           | R/W-0           | R/W-0           |

|                   |                                            |                                                                            |                                              | FLT1R<6:0>                 |                 |                 |                 |

| bit 7             |                                            |                                                                            |                                              |                            |                 |                 | bit C           |

| Legend:           |                                            |                                                                            |                                              |                            |                 |                 |                 |

| R = Readabl       | le bit                                     | W = Writable                                                               | bit                                          | U = Unimplen               | nented bit, rea | ad as '0'       |                 |

| -n = Value at     | t POR                                      | '1' = Bit is set                                                           |                                              | '0' = Bit is clea          | ared            | x = Bit is unkr | nown            |

| bit 14-8          | <b>FLT2R&lt;6:0&gt;</b><br>(see Table 11   | -2 for input pin                                                           | Fault 2 (FLT2)                               | ) to the Corresp<br>nbers) | onding RPn F    | Pin bits        |                 |

| bit 14-8          | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I                                                             | Fault 2 (FLT2)<br>selection nur<br>121       |                            | onding RPn F    | Pin bits        |                 |

| bit 14-8          | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I<br>I-2 for input pin<br>nput tied to RPI                    | Fault 2 (FLT2)<br>selection nur<br>121<br>P1 |                            | onding RPn F    | Pin bits        |                 |

| bit 14-8<br>bit 7 | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I<br>I-2 for input pin<br>nput tied to RPI<br>nput tied to CM | Fault 2 (FLT2<br>selection nur<br>121<br>P1  |                            | onding RPn F    | Pin bits        |                 |

#### REGISTER 11-15: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0                | R/W-0                                      | R/W-0                                           | R/W-0                                      | R/W-0                       | R/W-0            | R/W-0           | R/W-0 |

|--------------------|--------------------------------------------|-------------------------------------------------|--------------------------------------------|-----------------------------|------------------|-----------------|-------|

|                    |                                            |                                                 |                                            | SYNCI1R<6:03                | >                |                 |       |

| bit 15             |                                            |                                                 |                                            |                             |                  |                 | bit 8 |

|                    |                                            |                                                 |                                            |                             |                  |                 |       |

| U-0                | U-0                                        | U-0                                             | U-0                                        | U-0                         | U-0              | U-0             | U-0   |

| _                  |                                            |                                                 | —                                          |                             |                  | <u> </u>        | _     |

| bit 7              |                                            |                                                 |                                            |                             |                  |                 | bit 0 |

|                    |                                            |                                                 |                                            |                             |                  |                 |       |

| Legend:            |                                            |                                                 |                                            |                             |                  |                 |       |

| R = Readab         | ole bit                                    | W = Writable                                    | bit                                        | U = Unimplem                | nented bit, read | l as '0'        |       |

| -n = Value a       | it POR                                     | '1' = Bit is set                                |                                            | '0' = Bit is clea           | ared             | x = Bit is unkn | iown  |

|                    |                                            |                                                 |                                            |                             |                  |                 |       |

|                    |                                            |                                                 |                                            |                             |                  |                 |       |

| bit 15             | Unimplemer                                 | nted: Read as '                                 | 0'                                         |                             |                  |                 |       |

| bit 15<br>bit 14-8 | SYNCI1R<6:                                 |                                                 | M Synchroniz                               | zation Input 1 to<br>nbers) | the Correspon    | ding RPn Pin b  | its   |

|                    | SYNCI1R<6:<br>(see Table 11                | <b>0&gt;:</b> Assign PW                         | M Synchroniz selection nur                 |                             | the Correspon    | ding RPn Pin b  | its   |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                             | the Correspon    | ding RPn Pin b  | its   |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                             | the Correspon    | ding RPn Pin b  | its   |

|                    | SYNCI1R<6:<br>(see Table 11<br>1111001 = I | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz<br>selection nur<br>121<br>P1 |                             | the Correspon    | ding RPn Pin b  | its   |

## REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER (CONTINUED)

| bit 2 | <b>HOMIEN:</b> Home Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled            |

|-------|--------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IDXIRQ:</b> Status Flag for Index Event Status bit<br>1 = Index event has occurred<br>0 = No Index event has occurred |

| bit 0 | <b>IDXIEN:</b> Index Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled           |

Note 1: This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

## 21.4 ECAN Control Registers

| U-0               | U-0                                                                                                                                                                                                                                                                                                                    | R/W-0                                                 | R/W-0         | R/W-0            | R/W-1            | R/W-0              | R/W-0  |  |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------|------------------|------------------|--------------------|--------|--|--|--|--|

| —                 | —                                                                                                                                                                                                                                                                                                                      | CSIDL                                                 | ABAT          | CANCKS           | REQOP2           | REQOP1             | REQOP0 |  |  |  |  |

| bit 15            |                                                                                                                                                                                                                                                                                                                        |                                                       |               |                  |                  |                    | bit 8  |  |  |  |  |

| R-1               | R-0                                                                                                                                                                                                                                                                                                                    | R-0                                                   | U-0           | R/W-0            | U-0              | U-0                | R/W-0  |  |  |  |  |

| OPMODE2           | OPMODE1                                                                                                                                                                                                                                                                                                                | OPMODE0                                               | _             | CANCAP           |                  |                    | WIN    |  |  |  |  |

| bit 7             |                                                                                                                                                                                                                                                                                                                        |                                                       |               |                  |                  |                    | bit (  |  |  |  |  |

| Legend:           |                                                                                                                                                                                                                                                                                                                        |                                                       |               |                  |                  |                    |        |  |  |  |  |

| R = Readable      | bit                                                                                                                                                                                                                                                                                                                    | W = Writable I                                        | oit           | U = Unimpler     | mented bit, read | l as '0'           |        |  |  |  |  |

| -n = Value at POR |                                                                                                                                                                                                                                                                                                                        | '1' = Bit is set                                      |               | '0' = Bit is cle |                  | x = Bit is unknown |        |  |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                        |                                                       |               |                  |                  |                    |        |  |  |  |  |

| bit 15-14         | Unimplemen                                                                                                                                                                                                                                                                                                             | ted: Read as 'd                                       | )'            |                  |                  |                    |        |  |  |  |  |

| bit 13            | CSIDL: ECAN                                                                                                                                                                                                                                                                                                            | Nx Stop in Idle I                                     | Node bit      |                  |                  |                    |        |  |  |  |  |

|                   | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                                                                                                                                |                                                       |               |                  |                  |                    |        |  |  |  |  |

| bit 12            | ABAT: Abort All Pending Transmissions bit                                                                                                                                                                                                                                                                              |                                                       |               |                  |                  |                    |        |  |  |  |  |

|                   | <ul> <li>1 = Signals all transmit buffers to abort transmission</li> <li>0 = Module will clear this bit when all transmissions are aborted</li> </ul>                                                                                                                                                                  |                                                       |               |                  |                  |                    |        |  |  |  |  |

| bit 11            | CANCKS: ECANx Module Clock (FCAN) Source Select bit                                                                                                                                                                                                                                                                    |                                                       |               |                  |                  |                    |        |  |  |  |  |

|                   | 1 = FCAN is equal to 2 * FP<br>0 = FCAN is equal to FP                                                                                                                                                                                                                                                                 |                                                       |               |                  |                  |                    |        |  |  |  |  |

| bit 10-8          | 111 = Set Lis<br>110 = Reserv<br>101 = Reserv<br>100 = Set Co<br>011 = Set Lis<br>010 = Set Loc<br>001 = Set Dis                                                                                                                                                                                                       | ed<br>nfiguration mod<br>ten Only mode<br>opback mode | es mode<br>le | bits             |                  |                    |        |  |  |  |  |

| bit 7-5           | OPMODE<2:0>: Operation Mode bits<br>111 = Module is in Listen All Messages mode<br>110 = Reserved<br>101 = Reserved<br>100 = Module is in Configuration mode<br>011 = Module is in Listen Only mode<br>010 = Module is in Loopback mode<br>001 = Module is in Disable mode<br>000 = Module is in Normal Operation mode |                                                       |               |                  |                  |                    |        |  |  |  |  |

| bit 4             | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                             |                                                       |               |                  |                  |                    |        |  |  |  |  |

| bit 3             | <b>CANCAP:</b> CAN Message Receive Timer Capture Event Enable bit<br>1 = Enables input capture based on CAN message receive                                                                                                                                                                                            |                                                       |               |                  |                  |                    |        |  |  |  |  |

|                   | 0 = Disables (                                                                                                                                                                                                                                                                                                         | •                                                     | .1            |                  |                  |                    |        |  |  |  |  |

| bit 2-1           | -                                                                                                                                                                                                                                                                                                                      | ted: Read as '                                        |               |                  |                  |                    |        |  |  |  |  |

| bit 0             | <pre>WIN: SFR Ma 1 = Uses filter</pre>                                                                                                                                                                                                                                                                                 | ap Window Sele<br><sup>-</sup> window                 | ect bit       |                  |                  |                    |        |  |  |  |  |

#### 29.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 29.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 29.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 29.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

# TABLE 30-38:SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                 | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |                          |       |                             |  |

|--------------------|-----------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------|-------|-----------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                   | Min.                                                                                                                                                                                                                                                                                    | Typ. <sup>(2)</sup> | Max.                     | Units | Conditions                  |  |

| SP70               | FscP                  | Maximum SCK2 Input<br>Frequency                 | -                                                                                                                                                                                                                                                                                       | —                   | Lesser<br>of FP<br>or 11 | MHz   | (Note 3)                    |  |

| SP72               | TscF                  | SCK2 Input Fall Time                            |                                                                                                                                                                                                                                                                                         | _                   | —                        | ns    | See Parameter DO32 (Note 4) |  |

| SP73               | TscR                  | SCK2 Input Rise Time                            | _                                                                                                                                                                                                                                                                                       | _                   | —                        | ns    | See Parameter DO31 (Note 4) |  |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                      | _                                                                                                                                                                                                                                                                                       | —                   | —                        | ns    | See Parameter DO32 (Note 4) |  |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                      | —                                                                                                                                                                                                                                                                                       | —                   | —                        | ns    | See Parameter DO31 (Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge       | —                                                                                                                                                                                                                                                                                       | 6                   | 20                       | ns    |                             |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge    | 30                                                                                                                                                                                                                                                                                      | —                   | _                        | ns    |                             |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge      | 30                                                                                                                                                                                                                                                                                      | —                   | _                        | ns    |                             |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge       | 30                                                                                                                                                                                                                                                                                      | _                   | —                        | ns    |                             |  |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SS2}$ ↓ to SCK2 ↑ or SCK2 ↓<br>Input | 120                                                                                                                                                                                                                                                                                     | —                   | —                        | ns    |                             |  |

| SP51               | TssH2doZ              | SS2 ↑ to SDO2 Output<br>High-Impedance          | 10                                                                                                                                                                                                                                                                                      | _                   | 50                       | ns    | (Note 4)                    |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SS2 ↑ after SCK2 Edge                           | 1.5 TCY + 40                                                                                                                                                                                                                                                                            | —                   | —                        | ns    | (Note 4)                    |  |

| SP60               | TssL2doV              | SDO2 Data Output Valid after<br>SS2 Edge        | —                                                                                                                                                                                                                                                                                       | _                   | 50                       | ns    |                             |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 91 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI2 pins.

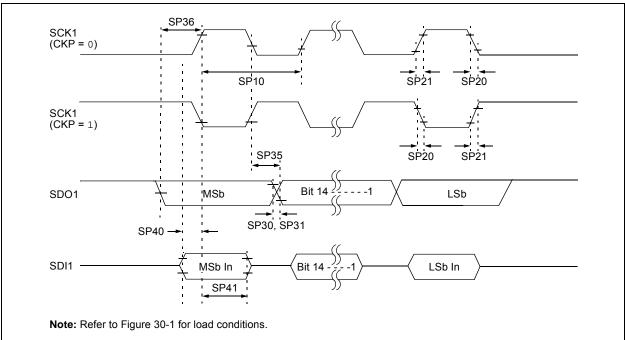

#### FIGURE 30-24: SPI1 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 30-43:SPI1 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |                             |  |

|--------------------|-----------------------|-----------------------------------------------|-------------------------------------------------------|---------------------|------|-------|-----------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                 | Min.                                                  | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |  |

| SP10               | FscP                  | Maximum SCK1 Frequency                        | _                                                     | —                   | 10   | MHz   | (Note 3)                    |  |

| SP20               | TscF                  | SCK1 Output Fall Time                         | —                                                     | —                   |      | ns    | See Parameter DO32 (Note 4) |  |

| SP21               | TscR                  | SCK1 Output Rise Time                         | —                                                     | —                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                    | —                                                     | —                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                    | —                                                     | _                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge     | —                                                     | 6                   | 20   | ns    |                             |  |

| SP36               | TdoV2sc,<br>TdoV2scL  | SDO1 Data Output Setup to<br>First SCK1 Edge  | 30                                                    | —                   | _    | ns    |                             |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data<br>Input to SCK1 Edge | 30                                                    | —                   | _    | ns    |                             |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge     | 30                                                    |                     |      | ns    |                             |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK1 is 100 ns. The clock generated in Master mode must not violate this specification.

- **4:** Assumes 50 pF load on all SPI1 pins.

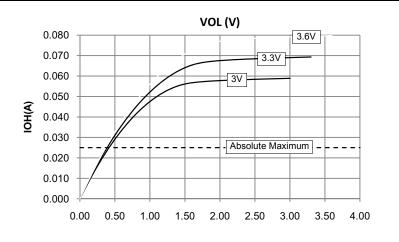

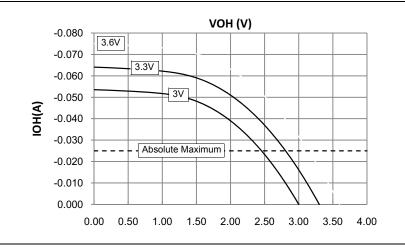

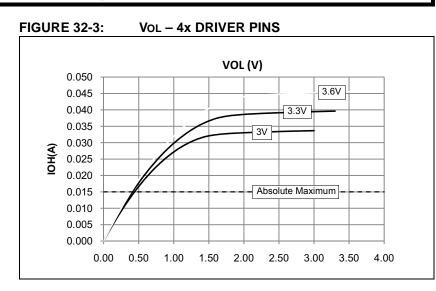

# 32.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

**Note:** The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

**FIGURE 32-1: VOH – 4x DRIVER PINS** VOH (V) -0.050 -0.045 3.6V -0.040 3.3V -0.035 3V -0.030 IOH(A) -0.025 -0.020 Absolute Maximum -0.015 -0.010 -0.005 0.000 0.50 1.00 2.00 2.50 3.00 3.50 0.00 1.50 4.00

#### FIGURE 32-2: VOH – 8x DRIVER PINS

## FIGURE 32-4: Vol – 8x DRIVER PINS