Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 28-SPDIP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128gp202-h-sp |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

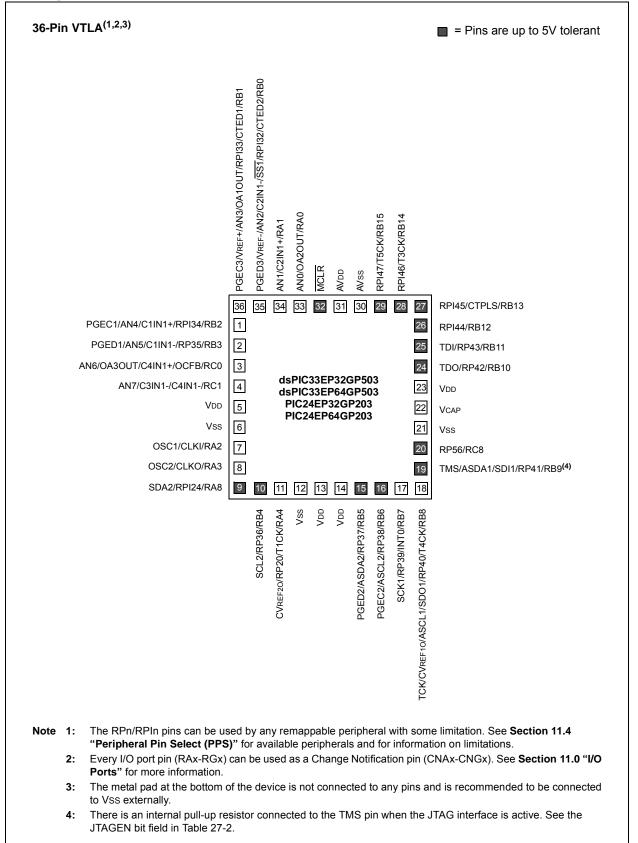

## **Pin Diagrams (Continued)**

# **Table of Contents**

| 1.0   | Device Overview                                                                                    |     |

|-------|----------------------------------------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-bit Digital Signal Controllers and Microcontrollers         | 29  |

| 3.0   | CPU                                                                                                | 35  |

| 4.0   | Memory Organization                                                                                | 45  |

| 5.0   | Flash Program Memory                                                                               | 119 |

| 6.0   | Resets                                                                                             |     |

| 7.0   | Interrupt Controller                                                                               | 127 |

| 8.0   | Direct Memory Access (DMA)                                                                         | 139 |

| 9.0   | Oscillator Configuration                                                                           |     |

| 10.0  | Power-Saving Features                                                                              | 163 |

| 11.0  | I/O Ports                                                                                          | 173 |

| 12.0  | Timer1                                                                                             | 203 |

| 13.0  | Timer2/3 and Timer4/5                                                                              | 207 |

| 14.0  | Input Capture                                                                                      | 213 |

|       | Output Compare                                                                                     |     |

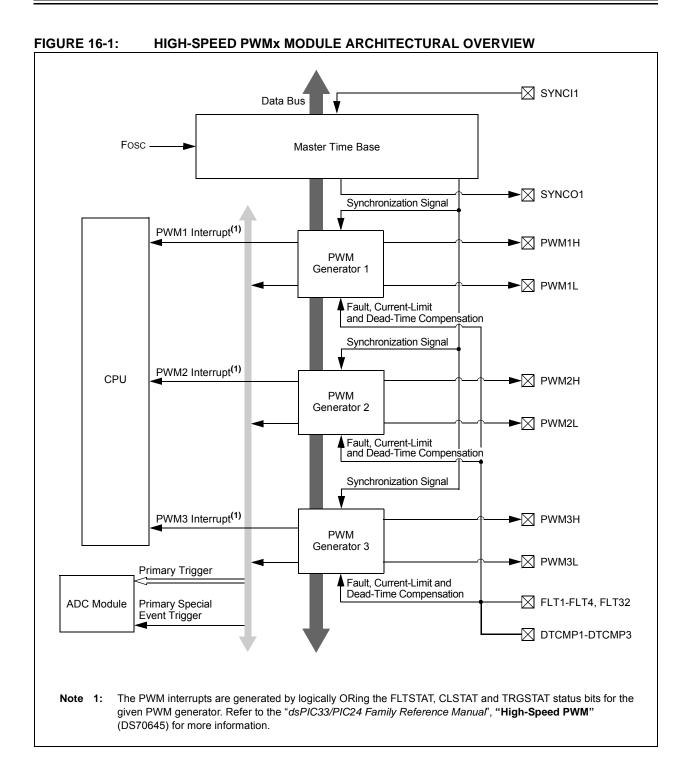

|       | High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)                     |     |

|       | Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only) |     |

|       | Serial Peripheral Interface (SPI)                                                                  |     |

|       | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                                                      |     |

|       | Universal Asynchronous Receiver Transmitter (UART)                                                 |     |

|       | Enhanced CAN (ECAN™) Module (dsPIC33EPXXXGP/MC50X Devices Only)                                    |     |

|       | Charge Time Measurement Unit (CTMU)                                                                |     |

|       | 10-Bit/12-Bit Analog-to-Digital Converter (ADC)                                                    |     |

|       | Peripheral Trigger Generator (PTG) Module                                                          |     |

| 25.0  | Op Amp/Comparator Module                                                                           |     |

|       | Programmable Cyclic Redundancy Check (CRC) Generator                                               |     |

| 27.0  |                                                                                                    |     |

|       |                                                                                                    |     |

| 29.0  | Development Support                                                                                |     |

|       | Electrical Characteristics                                                                         |     |

|       | High-Temperature Electrical Characteristics                                                        |     |

|       | DC and AC Device Characteristics Graphs                                                            |     |

|       | Packaging Information                                                                              |     |

|       | ndix A: Revision History                                                                           |     |

|       | (                                                                                                  |     |

|       | Vicrochip Web Site                                                                                 |     |

|       | omer Change Notification Service                                                                   |     |

|       | omer Support                                                                                       |     |

| Produ | uct Identification System                                                                          | 527 |

# 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section of the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

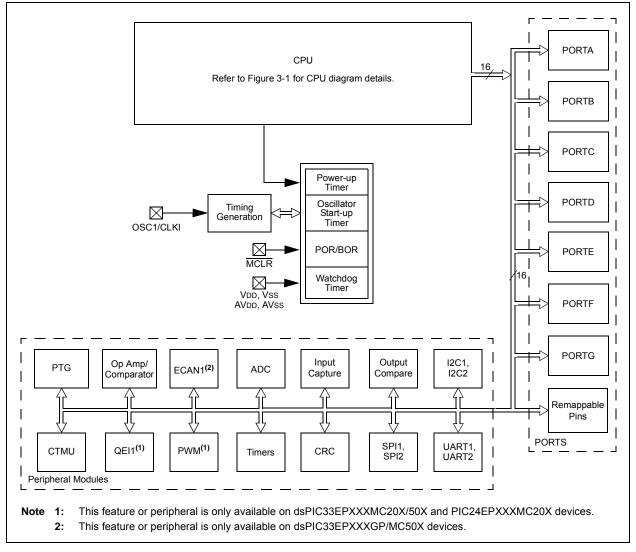

This document contains device-specific information for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X Digital Signal Controller (DSC) and Microcontroller (MCU) devices.

dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

Figure 1-1 shows a general block diagram of the core and peripheral modules. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

#### FIGURE 1-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X BLOCK DIAGRAM

## 3.5 **Programmer's Model**

The programmer's model for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X is shown in Figure 3-2. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions. Table 3-1 lists a description of each register.

In addition to the registers contained in the programmer's model, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/

MC20X devices contain control registers for Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only), Bit-Reversed Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only) and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory mapped, as shown in Table 4-1.

| Register(s) Name                                      | Description                                               |

|-------------------------------------------------------|-----------------------------------------------------------|

| W0 through W15                                        | Working Register Array                                    |

| ACCA, ACCB                                            | 40-Bit DSP Accumulators                                   |

| PC                                                    | 23-Bit Program Counter                                    |

| SR                                                    | ALU and DSP Engine STATUS Register                        |

| SPLIM                                                 | Stack Pointer Limit Value Register                        |

| TBLPAG                                                | Table Memory Page Address Register                        |

| DSRPAG                                                | Extended Data Space (EDS) Read Page Register              |

| DSWPAG                                                | Extended Data Space (EDS) Write Page Register             |

| RCOUNT                                                | REPEAT Loop Count Register                                |

| DCOUNT <sup>(1)</sup>                                 | DO Loop Count Register                                    |

| DOSTARTH <sup>(1,2)</sup> , DOSTARTL <sup>(1,2)</sup> | DO Loop Start Address Register (High and Low)             |

| DOENDH <sup>(1)</sup> , DOENDL <sup>(1)</sup>         | DO Loop End Address Register (High and Low)               |

| CORCON                                                | Contains DSP Engine, DO Loop Control and Trap Status bits |

## TABLE 3-1: PROGRAMMER'S MODEL REGISTER DESCRIPTIONS

Note 1: This register is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

2: The DOSTARTH and DOSTARTL registers are read-only.

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6                    | Bit 5       | Bit 4  | Bit 3  | Bit 2    | Bit 1        | Bit 0   | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|-------|--------------------------|-------------|--------|--------|----------|--------------|---------|---------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF                    | IC2IF       | DMA0IF | T1IF   | OC1IF    | IC1IF        | INTOIF  | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _                        | _           | INT1IF | CNIF   | CMIF     | MI2C1IF      | SI2C1IF | 0000          |

| IFS2         | 0804  | _      |        | _          | _      | _      |        | _          | _      |       | IC4IF                    | IC3IF       | DMA3IF | _      | —        | SPI2IF       | SPI2EIF | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | _      | QEI1IF | PSEMIF     | _      | _     | _                        | _           | _      | _      | MI2C2IF  | SI2C2IF      | —       | 0000          |

| IFS4         | 0808  | -      | _      | CTMUIF     | _      | _      |        | —          | _      | _     |                          | _           | _      | CRCIF  | U2EIF    | U1EIF        |         | 0000          |

| IFS5         | 080A  | PWM2IF | PWM1IF | _          | _      | _      |        | —          | _      | _     |                          | _           | _      | _      | _        | _            |         | 0000          |

| IFS6         | 080C  | _      | _      | _          | _      | _      |        | —          | _      | _     |                          | _           | _      | _      | _        | _            | PWM3IF  | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  | _          | _      | _      |        | —          | _      | _     |                          | _           | _      | _      | _        | _            | _       | 0000          |

| IFS9         | 0812  | _      | _      | _          | -      | _      |        | _          | —      | _     | PTG3IF                   | PTG2IF      | PTG1IF | PTG0IF | PTGWDTIF | PTGSTEPIF    |         | 0000          |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE                    | IC2IE       | DMA0IE | T1IE   | OC1IE    | IC1IE        | INTOIE  | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | —     | _                        | —           | INT1IE | CNIE   | CMIE     | MI2C1IE      | SI2C1IE | 0000          |

| IEC2         | 0824  | _      | _      | —          | -      | _      |        | —          | —      | _     | IC4IE                    | IC3IE       | DMA3IE |        | _        | SPI2IE       | SPI2EIE | 0000          |

| IEC3         | 0826  | _      | _      | _          | -      | _      | QEI1IE | PSEMIE     | —      | _     | _                        | —           | —      | -      | MI2C2IE  | SI2C2IE      | —       | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     | -      | _      |        | —          | —      | _     | _                        | —           | _      | CRCIE  | U2EIE    | U1EIE        |         | 0000          |

| IEC5         | 082A  | PWM2IE | PWM1IE | —          | -      | _      |        | _          | —      | _     | _                        | —           | _      |        | _        | —            |         | 0000          |

| IEC6         | 082C  | _      | _      | _          | -      | _      |        | _          | —      | _     | _                        | —           | _      | -      | _        | _            | PWM3IE  | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | -      | _      |        | _          | —      | _     | _                        | —           | _      | -      | _        | _            | —       | 0000          |

| IEC9         | 0832  | _      | _      | _          | -      | _      |        | _          | —      | _     | PTG3IE                   | PTG2IE      | PTG1IE | PTG0IE | PTGWDTIE | PTGSTEPIE    |         | 0000          |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      |        | OC1IP<2:0  | )>     | _     |                          | IC1IP<2:0>  |        |        |          | INT0IP<2:0>  |         | 4444          |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |        | _      |        | OC2IP<2:0  | )>     | _     |                          | IC2IP<2:0>  |        | -      | [        | DMA0IP<2:0>  |         | 4444          |

| IPC2         | 0844  | _      | -      | U1RXIP<2:0 | >      | _      | :      | SPI1IP<2:0 | )>     | _     |                          | SPI1EIP<2:0 | >      | -      |          | T3IP<2:0>    |         | 4444          |

| IPC3         | 0846  | _      | _      | —          | —      | _      | C      | MA1IP<2:   | 0>     | _     |                          | AD1IP<2:0>  |        | -      |          | U1TXIP<2:0>  |         | 0444          |

| IPC4         | 0848  | _      |        | CNIP<2:0>  |        | _      |        | CMIP<2:0   | >      | _     |                          | MI2C1IP<2:0 | >      | -      | 5        | SI2C1IP<2:0> |         | 4444          |

| IPC5         | 084A  | _      | _      | —          | —      | _      |        | —          | —      | _     | _                        | —           | —      | -      |          | INT1IP<2:0>  |         | 0004          |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      |        | OC4IP<2:0  | )>     |       |                          | OC3IP<2:0>  |        |        | [        | DMA2IP<2:0>  |         | 4444          |

| IPC7         | 084E  | _      |        | U2TXIP<2:0 | >      | _      | ι      | J2RXIP<2:  | 0>     |       |                          | INT2IP<2:0> | •      |        |          | T5IP<2:0>    |         | 4444          |

| IPC8         | 0850  | _      | _      | —          | —      | _      |        | —          | —      | _     |                          | SPI2IP<2:0> | •      | -      | 5        | SPI2EIP<2:0> |         | 0044          |

| IPC9         | 0852  | _      | _      | _          | -      | _      |        | IC4IP<2:0  | >      | _     | IC3IP<2:0> — DMA3IP<2:0> |             |        | 0444   |          |              |         |               |

| IPC12        | 0858  | _      | _      | _          | -      | _      | N      | 112C2IP<2: | 0>     | _     | SI2C2IP<2:0>             |             |        | 0440   |          |              |         |               |

| IPC14        | 085C  | _      | _      | _          | _      | _      | (      | QEI1IP<2:0 | )>     | _     | PSEMIP<2:0>              |             | _      | 0440   |          |              |         |               |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | >      | _      |        | U2EIP<2:0  | >      | _     |                          | U1EIP<2:0>  |        | _      | _        | _            | _       | 4440          |

| IPC19        | 0866  | _      | _      | —          | —      | _      | —      | —          | _      | _     |                          | CTMUIP<2:0  | >      | _      | _        | _            | _       | 0040          |

| IPC23        | 086E  | _      | F      | PWM2IP<2:0 | )>     | _      | P      | WM1IP<2:   | 0>     | _     | _                        | _           | —      | _      | _        | _            | _       | 4400          |

| IPC24        | 0870  | _      | _      |            |        | _      |        | _          |        |       | _                        | _           | _      | _      | F        | PWM3IP<2:0>  |         | 4004          |

# TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-41: PMD REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | —      | —      | _      | CMPMD  | _      | _      | CRCMD  | _     | —     | _      | —      | —      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      |        | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      | PWM3MD | PWM2MD | PWM1MD | _      | _     | _     | _      | _      | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| PIVID7       | 0760  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

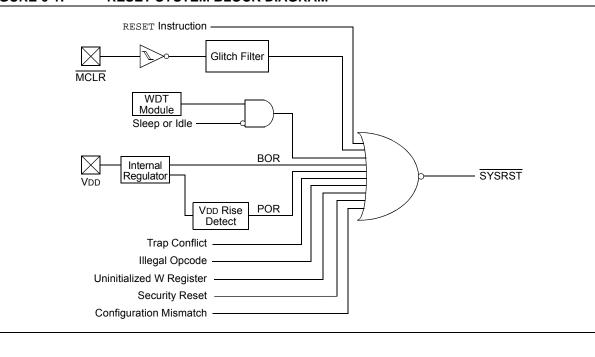

# 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- · BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Time-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 4.0 "Memory Organization" of this manual for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR and BOR bits (RCON<1:0>), that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

For all Resets, the default clock source is determined by the FNOSC<2:0> bits in the FOSCSEL Configuration register. The value of the FNOSC<2:0> bits is loaded into NOSC<2:0> (OSCCON<10:8>) on Reset, which in turn, initializes the system clock.

| U-0     | U-0 | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   |

|---------|-----|-------|-------|-------|-------|-------|-------|

| —       | —   | —     | —     | —     | —     | —     | —     |

| bit 15  |     |       |       |       |       |       | bit 8 |

|         |     |       |       |       |       |       |       |

| U-0     | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —       | —   | TUN5  | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7   |     |       |       |       |       |       | bit 0 |

|         |     |       |       |       |       |       |       |

| Logondi |     |       |       |       |       |       |       |

## REGISTER 9-4: OSCTUN: FRC OSCILLATOR TUNING REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **TUN<5:0>:** FRC Oscillator Tuning bits 011111 = Maximum frequency deviation of 1.453% (7.477 MHz) 011110 = Center frequency + 1.406% (7.474 MHz) •••• 000001 = Center frequency + 0.047% (7.373 MHz) 000000 = Center frequency (7.37 MHz nominal) 111111 = Center frequency - 0.047% (7.367 MHz) ••• 100001 = Center frequency - 1.453% (7.263 MHz) 100000 = Minimum frequency deviation of -1.5% (7.259 MHz)

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits<sup>(4)</sup>

- 11111 = No Sync or Trigger source for ICx

- 11110 = Reserved

- 11101 = Reserved

- 11100 = CTMU module synchronizes or triggers ICx

- 11011 = ADC1 module synchronizes or triggers  $ICx^{(5)}$

- 11010 = CMP3 module synchronizes or triggers  $ICx^{(5)}$

- $11001 = CMP2 \text{ module synchronizes or triggers ICx}^{(5)}$

- 11000 = CMP1 module synchronizes or triggers  $ICx^{(5)}$

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Reserved

- 10100 = Reserved

- 10011 = IC4 module synchronizes or triggers ICx

- 10010 = IC3 module synchronizes or triggers ICx

- 10001 = IC2 module synchronizes or triggers ICx

- 10000 = IC1 module synchronizes or triggers ICx

- 01111 = Timer5 synchronizes or triggers ICx

- 01110 = Timer4 synchronizes or triggers ICx

- 01101 = Timer3 synchronizes or triggers ICx (default)

- 01100 = Timer2 synchronizes or triggers ICx

- 01011 = Timer1 synchronizes or triggers ICx

- 01010 = PTGOx module synchronizes or triggers  $ICx^{(6)}$

- 01001 = Reserved

- 01000 = Reserved

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Reserved

- 00100 = OC4 module synchronizes or triggers ICx

- 00011 = OC3 module synchronizes or triggers ICx

- 00010 = OC2 module synchronizes or triggers ICx

- 00001 = OC1 module synchronizes or triggers ICx

- 00000 = No Sync or Trigger source for ICx

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1

PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4

| REGISTER 16-2: | PTCON2: PWMx PRIMARY MASTER CLOCK DIVIDER SELECT REGISTER 2 |

|----------------|-------------------------------------------------------------|

|----------------|-------------------------------------------------------------|

| U-0                                | U-0        | U-0            | U-0 | U-0              | U-0                     | U-0                     | U-0         |  |

|------------------------------------|------------|----------------|-----|------------------|-------------------------|-------------------------|-------------|--|

| —                                  | —          | —              | _   | —                | —                       | —                       | _           |  |

| bit 15                             |            |                |     |                  |                         |                         | bit 8       |  |

|                                    |            |                |     |                  |                         |                         |             |  |

| U-0                                | U-0        | U-0            | U-0 | U-0              | R/W-0                   | R/W-0                   | R/W-0       |  |

| —                                  | —          | —              | -   | —                | PCLKDIV2 <sup>(1)</sup> | PCLKDIV1 <sup>(1)</sup> | PCLKDIV0(1) |  |

| bit 7                              |            |                |     |                  |                         |                         | bit 0       |  |

|                                    |            |                |     |                  |                         |                         |             |  |

| Legend:                            |            |                |     |                  |                         |                         |             |  |

| R = Readable                       | bit        | W = Writable   | bit | U = Unimpler     | mented bit, read        | as '0'                  |             |  |

| -n = Value at POR '1' = Bit is set |            |                |     | '0' = Bit is cle | ared                    | x = Bit is unknown      |             |  |

|                                    |            |                |     |                  |                         |                         |             |  |

| bit 15-3                           | Unimplemen | ted: Read as ' | י'  |                  |                         |                         |             |  |

#### bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved 110 = Divide-by-64 101 = Divide-by-32

- 100 = Divide-by-32100 = Divide-by-16

- 011 = Divide-by-8

- 010 = Divide-by-4

- 001 = Divide-by-2

- 000 = Divide-by-1, maximum PWMx timing resolution (power-on default)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

# 19.0 INTER-INTEGRATED CIRCUIT<sup>™</sup> (I<sup>2</sup>C<sup>™</sup>)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70330) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

- 3: There are minimum bit rates of approximately FCY/512. As a result, high processor speeds may not support 100 Kbit/second operation. See timing specifications, IM10 and IM11, and the "Baud Rate Generator" in the "dsPIC33/PIC24 Family Reference Manual".

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices contains two Inter-Integrated Circuit (I<sup>2</sup>C) modules: I2C1 and I2C2.

The  $l^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $l^2C$  serial communication standard, with a 16-bit interface.

The  $I^2C$  module has a 2-pin interface:

- · The SCLx pin is clock

- The SDAx pin is data

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both Master and Slave modes of operation

- I<sup>2</sup>C Slave mode supports 7 and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7 and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation, detects bus collision and arbitrates accordingly

- Intelligent Platform Management Interface (IPMI)

support

- System Management Bus (SMBus) support

| R/W-0                                                                                                                                                              | R/W-0      | R/W-0            | R/W-0           | R/W-0             | R/W-0                              | R/W-0              | R/W-0  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------|-----------------|-------------------|------------------------------------|--------------------|--------|--|--|--|--|

|                                                                                                                                                                    | F15B       | P<3:0>           |                 | F14BP<3:0>        |                                    |                    |        |  |  |  |  |

| bit 15                                                                                                                                                             |            |                  |                 |                   |                                    |                    | bit 8  |  |  |  |  |

| R/W-0                                                                                                                                                              | R/W-0      | R/W-0            | R/W-0           | R/W-0             | R/W-0                              | R/W-0              | R/W-0  |  |  |  |  |

| 1010 0                                                                                                                                                             |            | P<3:0>           |                 |                   |                                    | P<3:0>             | 1010 0 |  |  |  |  |

| bit 7                                                                                                                                                              |            |                  |                 |                   |                                    |                    | bit 0  |  |  |  |  |

| Legend:                                                                                                                                                            |            |                  |                 |                   |                                    |                    |        |  |  |  |  |

| R = Readable bit W = Writable bit                                                                                                                                  |            |                  | bit             | U = Unimplen      | U = Unimplemented bit, read as '0' |                    |        |  |  |  |  |

| -n = Value at                                                                                                                                                      | t POR      | '1' = Bit is set | :               | '0' = Bit is clea | ared                               | x = Bit is unknown |        |  |  |  |  |

| <pre>bit 15-12 F15BP&lt;3:0&gt;: RX Buffer Mask for Filter 15 bits 1111 = Filter hits received in RX FIFO buffer 1110 = Filter hits received in RX Buffer 14</pre> |            |                  |                 |                   |                                    |                    |        |  |  |  |  |

| bit 11-8                                                                                                                                                           | F14BP<3:0; | RX Buffer Ma     | sk for Filter 1 | 4 bits (same val  | ues as bits<15                     | :12>)              |        |  |  |  |  |

| bit 7-4                                                                                                                                                            | F13BP<3:0; | RX Buffer Ma     | sk for Filter 1 | 3 bits (same val  | ues as bits<15                     | :12>)              |        |  |  |  |  |

| bit 3-0 <b>F12BP&lt;3:0&gt;:</b> RX Buffer Mask for Filter 12 bits (same values as bits<15:12>)                                                                    |            |                  |                 |                   |                                    |                    |        |  |  |  |  |

# REGISTER 21-15: CxBUFPNT4: ECANx FILTER 12-15 BUFFER POINTER REGISTER 4

NOTES:

## REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER (CONTINUED)

- PTGITM<1:0>: PTG Input Trigger Command Operating Mode bits<sup>(1)</sup>

- 11 = Single level detect with Step delay not executed on exit of command (regardless of the PTGCTRL command)

- 10 = Single level detect with Step delay executed on exit of command

- 01 = Continuous edge detect with Step delay not executed on exit of command (regardless of the PTGCTRL command)

- 00 = Continuous edge detect with Step delay executed on exit of command

- Note 1: These bits apply to the PTGWHI and PTGWLO commands only.

bit 1-0

- **2:** This bit is only used with the PTGCTRL step command software trigger option.

- **3:** Use of the PTG Single-Step mode is reserved for debugging tools only.

| R/W-0      | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                                                          | R/W-0          | R/W-0            | R/W-0                        | R/W-0           | R/W-0  |  |  |  |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|------------------------------|-----------------|--------|--|--|--|--|--|

| ADCTS4     | ADCTS3                                                                                                                                                                 | ADCTS2                                                                                                                                                         | ADCTS1         | IC4TSS           | IC3TSS                       | IC2TSS          | IC1TSS |  |  |  |  |  |

| bit 15     |                                                                                                                                                                        |                                                                                                                                                                |                |                  |                              |                 | bit 8  |  |  |  |  |  |

| R/W-0      | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                                                          | R/W-0          | R/W-0            | R/W-0                        | R/W-0           | R/W-0  |  |  |  |  |  |

| OC4CS      |                                                                                                                                                                        | OC2CS                                                                                                                                                          | OC1CS          | OC4TSS           | OC3TSS                       | OC2TSS          | OC1TSS |  |  |  |  |  |

| bit 7      |                                                                                                                                                                        |                                                                                                                                                                |                |                  |                              |                 | bit (  |  |  |  |  |  |

| Legend:    |                                                                                                                                                                        |                                                                                                                                                                |                |                  |                              |                 |        |  |  |  |  |  |

| R = Reada  | ble bit                                                                                                                                                                | W = Writable                                                                                                                                                   | bit            | U = Unimplei     | mented bit, read             | l as '0'        |        |  |  |  |  |  |

| -n = Value | at POR                                                                                                                                                                 | '1' = Bit is set                                                                                                                                               |                | '0' = Bit is cle |                              | x = Bit is unkr | nown   |  |  |  |  |  |

|            |                                                                                                                                                                        |                                                                                                                                                                |                |                  |                              |                 |        |  |  |  |  |  |

| bit 15     | ADCTS4: Sa                                                                                                                                                             | mple Trigger P                                                                                                                                                 | TGO15 for AE   | OC bit           |                              |                 |        |  |  |  |  |  |

|            | 1 = Generate                                                                                                                                                           | 1 = Generates Trigger when the broadcast command is executed                                                                                                   |                |                  |                              |                 |        |  |  |  |  |  |

|            | 0 = Does not                                                                                                                                                           | 0 = Does not generate Trigger when the broadcast command is executed                                                                                           |                |                  |                              |                 |        |  |  |  |  |  |

| bit 14     |                                                                                                                                                                        | mple Trigger P                                                                                                                                                 |                |                  |                              |                 |        |  |  |  |  |  |

|            |                                                                                                                                                                        | es Trigger wher                                                                                                                                                |                |                  |                              | al              |        |  |  |  |  |  |

| bit 13     |                                                                                                                                                                        |                                                                                                                                                                |                |                  | mand is execute              | a               |        |  |  |  |  |  |

| DIE 13     |                                                                                                                                                                        | mple Trigger P<br>es Trigger wher                                                                                                                              |                |                  | evecuted                     |                 |        |  |  |  |  |  |

|            |                                                                                                                                                                        |                                                                                                                                                                |                |                  | mand is execute              | ed              |        |  |  |  |  |  |

| bit 12     |                                                                                                                                                                        | ADCTS1: Sample Trigger PTGO12 for ADC bit                                                                                                                      |                |                  |                              |                 |        |  |  |  |  |  |

|            | 1 = Generate                                                                                                                                                           | <ul> <li>1 = Generates Trigger when the broadcast command is executed</li> <li>0 = Does not generate Trigger when the broadcast command is executed</li> </ul> |                |                  |                              |                 |        |  |  |  |  |  |

|            |                                                                                                                                                                        |                                                                                                                                                                |                |                  | mand is execute              | ed              |        |  |  |  |  |  |

| bit 11     | -                                                                                                                                                                      | C4TSS: Trigger/Synchronization Source for IC4 bit<br>= Generates Trigger/Synchronization when the broadcast command is executed                                |                |                  |                              |                 |        |  |  |  |  |  |

|            |                                                                                                                                                                        |                                                                                                                                                                |                |                  | ast command is broadcast con |                 | ited   |  |  |  |  |  |

| bit 10     | IC3TSS: Trig                                                                                                                                                           | SS: Trigger/Synchronization Source for IC3 bit                                                                                                                 |                |                  |                              |                 |        |  |  |  |  |  |

|            |                                                                                                                                                                        |                                                                                                                                                                |                |                  | ast command is broadcast con |                 | ited   |  |  |  |  |  |

| bit 9      | IC2TSS: Trig                                                                                                                                                           | SS: Trigger/Synchronization Source for IC2 bit                                                                                                                 |                |                  |                              |                 |        |  |  |  |  |  |

|            |                                                                                                                                                                        |                                                                                                                                                                |                |                  | ast command is broadcast con |                 | ited   |  |  |  |  |  |

| bit 8      |                                                                                                                                                                        | ger/Synchroniz                                                                                                                                                 |                |                  |                              |                 |        |  |  |  |  |  |

|            |                                                                                                                                                                        |                                                                                                                                                                |                |                  | ast command is broadcast con |                 | ited   |  |  |  |  |  |

| bit 7      |                                                                                                                                                                        | ck Source for C                                                                                                                                                | -              |                  |                              |                 |        |  |  |  |  |  |

|            | <ul> <li>1 = Generates clock pulse when the broadcast command is executed</li> <li>0 = Does not generate clock pulse when the broadcast command is executed</li> </ul> |                                                                                                                                                                |                |                  |                              |                 |        |  |  |  |  |  |

| bit 6      |                                                                                                                                                                        | ck Source for C                                                                                                                                                | -              |                  |                              |                 |        |  |  |  |  |  |

|            |                                                                                                                                                                        | es clock pulse v<br>aenerate clock                                                                                                                             |                |                  | d is executed command is exe | cuted           |        |  |  |  |  |  |

| bit 5      |                                                                                                                                                                        | ck Source for C                                                                                                                                                | -              |                  |                              |                 |        |  |  |  |  |  |

|            | 1 = Generate                                                                                                                                                           | es clock pulse v                                                                                                                                               | when the broad |                  | d is executed command is exe | cuted           |        |  |  |  |  |  |

|            | This register is rea<br>PTGSTRT = 1).                                                                                                                                  | -                                                                                                                                                              |                |                  |                              |                 | and    |  |  |  |  |  |

|            | This register is on                                                                                                                                                    | lv used with the                                                                                                                                               | PTGCTRI. OI    | PTION = 1111     | Step command                 | L               |        |  |  |  |  |  |

|            |                                                                                                                                                                        | .,                                                                                                                                                             |                |                  | c.op commune                 | •               |        |  |  |  |  |  |

# **REGISTER 24-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER**<sup>(1,2)</sup>

| REGISTER 25-5: | CMxMSKCON: COMPARATOR x MASK GATING |

|----------------|-------------------------------------|

|                | CONTROL REGISTER                    |

| R/W-0                            |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |                                         |                   |                    |              |  |  |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------|--------------------|--------------|--|--|

|                                  | U-0                                                                                                                                                                                                                                                                                                                       | R/W-0                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                        | R/W-0                                   | R/W-0             | R/W-0              | R/W-0        |  |  |

| HLMS                             | —                                                                                                                                                                                                                                                                                                                         | OCEN                                                                                                                                                                                                                                                                                                          | OCNEN                                                                                                                                                                                                                                                        | OBEN                                    | OBNEN             | OAEN               | OANEN        |  |  |

| bit 15                           |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |                                         |                   |                    | bit          |  |  |

| R/W-0                            | R/W-0                                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                        | R/W-0                                   | R/W-0             | R/W-0              | R/W-0        |  |  |

| NAGS                             | PAGS                                                                                                                                                                                                                                                                                                                      | ACEN                                                                                                                                                                                                                                                                                                          | ACNEN                                                                                                                                                                                                                                                        | ABEN                                    | ABNEN             | AAEN               | AANEN        |  |  |

| bit 7                            |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |                                         |                   |                    | bit          |  |  |

| Legend:                          |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |                                         |                   |                    |              |  |  |

| R = Readable bit                 |                                                                                                                                                                                                                                                                                                                           | W = Writable                                                                                                                                                                                                                                                                                                  | bit                                                                                                                                                                                                                                                          | U = Unimple                             | mented bit, read  | l as '0'           |              |  |  |

| -n = Value at POR                |                                                                                                                                                                                                                                                                                                                           | '1' = Bit is set                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                              | '0' = Bit is cle                        |                   | x = Bit is unknown |              |  |  |

|                                  |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |                                         |                   |                    |              |  |  |

| bit 15                           | HLMS: High                                                                                                                                                                                                                                                                                                                | or Low-Level N                                                                                                                                                                                                                                                                                                | Asking Select                                                                                                                                                                                                                                                | bits                                    |                   |                    |              |  |  |

|                                  | •                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                               | -                                                                                                                                                                                                                                                            |                                         | erted ('0') compa | rator signal from  | n propagatin |  |  |

|                                  |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |                                         | erted ('1') compa |                    |              |  |  |

| bit 14                           | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |                                         |                   |                    |              |  |  |

| bit 13                           | OCEN: OR G                                                                                                                                                                                                                                                                                                                | Sate C Input Er                                                                                                                                                                                                                                                                                               | able bit                                                                                                                                                                                                                                                     |                                         |                   |                    |              |  |  |

|                                  | 1 = MCI is co                                                                                                                                                                                                                                                                                                             | nnected to OR                                                                                                                                                                                                                                                                                                 | gate                                                                                                                                                                                                                                                         |                                         |                   |                    |              |  |  |

|                                  | 0 = MCI is no                                                                                                                                                                                                                                                                                                             | ot connected to                                                                                                                                                                                                                                                                                               | OR gate                                                                                                                                                                                                                                                      |                                         |                   |                    |              |  |  |

| bit 12                           | OCNEN: OR Gate C Input Inverted Enable bit                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |                                         |                   |                    |              |  |  |