#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betans                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128gp202-i-ss |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

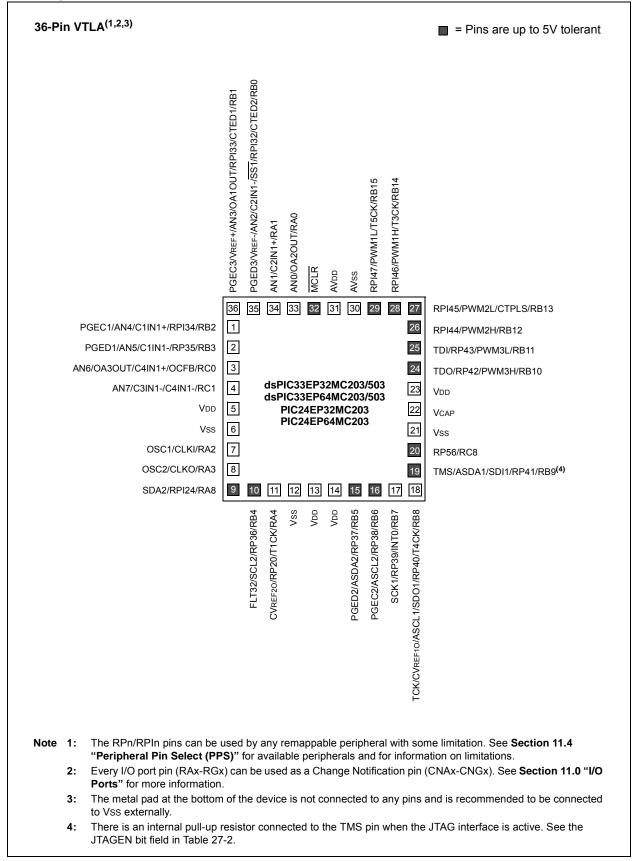

### Pin Diagrams (Continued)

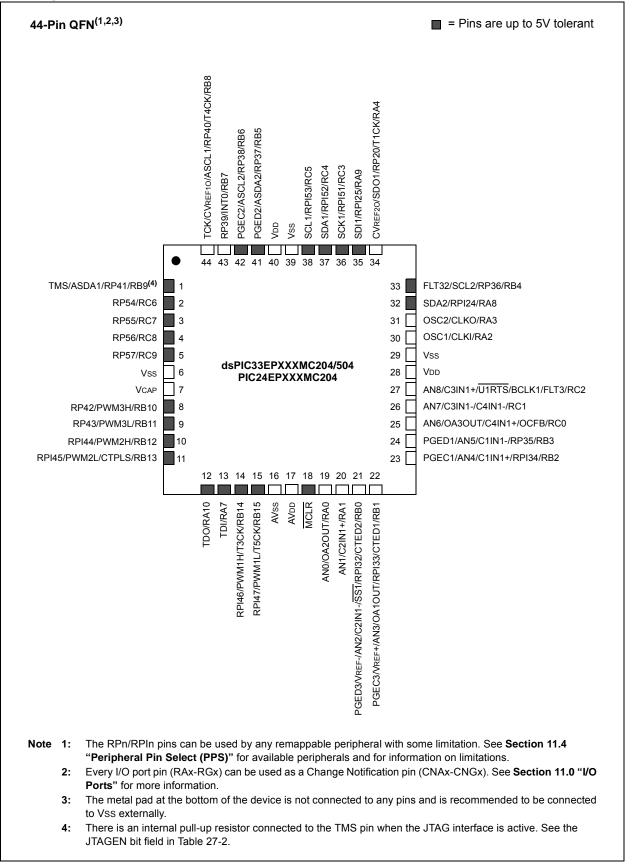

### Pin Diagrams (Continued)

### 3.5 **Programmer's Model**

The programmer's model for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X is shown in Figure 3-2. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions. Table 3-1 lists a description of each register.

In addition to the registers contained in the programmer's model, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/

MC20X devices contain control registers for Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only), Bit-Reversed Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only) and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory mapped, as shown in Table 4-1.

| Register(s) Name                                      | Description                                               |

|-------------------------------------------------------|-----------------------------------------------------------|

| W0 through W15                                        | Working Register Array                                    |

| ACCA, ACCB                                            | 40-Bit DSP Accumulators                                   |

| PC                                                    | 23-Bit Program Counter                                    |

| SR                                                    | ALU and DSP Engine STATUS Register                        |

| SPLIM                                                 | Stack Pointer Limit Value Register                        |

| TBLPAG                                                | Table Memory Page Address Register                        |

| DSRPAG                                                | Extended Data Space (EDS) Read Page Register              |

| DSWPAG                                                | Extended Data Space (EDS) Write Page Register             |

| RCOUNT                                                | REPEAT Loop Count Register                                |

| DCOUNT <sup>(1)</sup>                                 | DO Loop Count Register                                    |

| DOSTARTH <sup>(1,2)</sup> , DOSTARTL <sup>(1,2)</sup> | DO Loop Start Address Register (High and Low)             |

| DOENDH <sup>(1)</sup> , DOENDL <sup>(1)</sup>         | DO Loop End Address Register (High and Low)               |

| CORCON                                                | Contains DSP Engine, DO Loop Control and Trap Status bits |

### TABLE 3-1: PROGRAMMER'S MODEL REGISTER DESCRIPTIONS

Note 1: This register is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

2: The DOSTARTH and DOSTARTL registers are read-only.

| TABLE 4 | 4-31: | PER | IPHERA | L PIN S | ELECT | INPUT F | REGISTI | ER MAP | FOR de | sPIC33E | EPXXXG | P50X D | EVICES | SONLY |  |

|---------|-------|-----|--------|---------|-------|---------|---------|--------|--------|---------|--------|--------|--------|-------|--|

|         |       |     |        |         |       |         |         |        |        |         |        |        |        |       |  |

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6     | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|-----------|--------|------------|--------|-------|-------|-------|-----------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR0       | 06A0  | —      |        |           |        | INT1R<6:0> |        |       |       | _     | _         | —     | —     | —          | —     | —     | _     | 0000          |

| RPINR1       | 06A2  |        | _      | _         | _      | _          | _      | _     | _     | _     |           |       |       | INT2R<6:0> | •     |       |       | 0000          |

| RPINR3       | 06A6  |        | _      | _         | _      | _          | _      | _     | _     | _     |           |       | ٦     | [2CKR<6:0  | >     |       |       | 0000          |

| RPINR7       | 06AE  |        |        |           |        | IC2R<6:0>  |        |       |       | _     |           |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8       | 06B0  |        |        | IC4R<6:0> |        |            |        |       |       | _     | IC3R<6:0> |       |       |            |       |       |       | 0000          |

| RPINR11      | 06B6  |        | _      | _         | _      | _          | _      | _     | _     | _     |           |       | (     | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR18      | 06C4  |        | _      | _         | _      | _          | _      | _     | _     | _     |           |       | ι     | J1RXR<6:0  | >     |       |       | 0000          |

| RPINR19      | 06C6  |        | _      | _         | _      | _          | _      | _     | _     | _     |           |       | ι     | J2RXR<6:0  | >     |       |       | 0000          |

| RPINR22      | 06CC  |        |        |           | S      | CK2INR<6:0 | )>     |       |       | _     |           |       | :     | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23      | 06CE  | _      | _      | _         | —      | —          | _      | _     | —     | —     |           |       |       | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26      | 06D4  | —      | _      | _         | -      | _          | _      | —     |       | —     |           |       | (     | C1RXR<6:0  | >     |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **TABLE 4-32:** PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File Name | Addr. | Bit 15 | Bit 14       | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7      | Bit 6       | Bit 5 | Bit 4     | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------------|--------|--------|------------|--------|-------|-------|------------|-------------|-------|-----------|------------|-------|-------|-------|---------------|

| RPINR0    | 06A0  | _      |              |        |        | INT1R<6:0> |        |       |       | —          | —           | —     | —         | —          | —     | —     | _     | 0000          |

| RPINR1    | 06A2  |        | _            | _      | _      | _          | _      | _     | _     | _          | INT2R<6:0>  |       |           |            |       |       | 0000  |               |

| RPINR3    | 06A6  |        |              |        |        |            |        | _     | _     |            |             | -     | F2CKR<6:0 | >          |       |       | 0000  |               |

| RPINR7    | 06AE  |        |              |        |        | IC2R<6:0>  |        |       |       | _          | – IC1R<6:0> |       |           |            |       | 0000  |       |               |

| RPINR8    | 06B0  |        |              |        |        | IC4R<6:0>  |        |       |       | _          | IC3R<6:0>   |       |           |            | 0000  |       |       |               |

| RPINR11   | 06B6  |        | _            | _      | _      | _          | _      | _     | _     | _          |             |       | (         | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR12   | 06B8  |        | FLT2R<6:0>   |        |        |            |        |       | _     | FLT1R<6:0> |             |       |           |            | 0000  |       |       |               |

| RPINR14   | 06BC  |        |              |        | (      | QEB1R<6:0  | >      |       |       | _          |             |       | (         | QEA1R<6:0  | >     |       |       | 0000          |

| RPINR15   | 06BE  |        |              |        | Н      | OME1R<6:0  | )>     |       |       | _          |             |       | I         | NDX1R<6:0  | >     |       |       | 0000          |

| RPINR18   | 06C4  |        | _            | _      | _      | _          | _      | _     | _     | _          | U1RXR<6:0>  |       |           |            |       |       | 0000  |               |

| RPINR19   | 06C6  |        | _            | _      | _      | _          | _      | _     | _     | _          |             |       | ι         | J2RXR<6:0  | >     |       |       | 0000          |

| RPINR22   | 06CC  | _      |              |        | S      | CK2INR<6:( | )>     |       |       | —          |             |       |           | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23   | 06CE  | _      | —            | —      |        | —          | —      |       | —     | —          |             |       |           | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26   | 06D4  | _      | —            | —      |        | —          | —      |       | —     | —          |             |       | (         | C1RXR<6:0  | >     |       |       | 0000          |

| RPINR37   | 06EA  | _      | SYNCI1R<6:0> |        |        |            |        |       | —     | —          | —           | —     | —         |            |       |       | 0000  |               |

| RPINR38   | 06EC  | _      | DTCMP1R<6:0> |        |        |            |        |       | —     |            |             |       |           |            | _     | 0000  |       |               |

| RPINR39   | 06EE  | _      |              |        | D      | FCMP3R<6:  | 0>     |       |       | _          |             |       | D         | CMP2R<6:   | 0>    |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

### 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions. which apply to dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

### 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

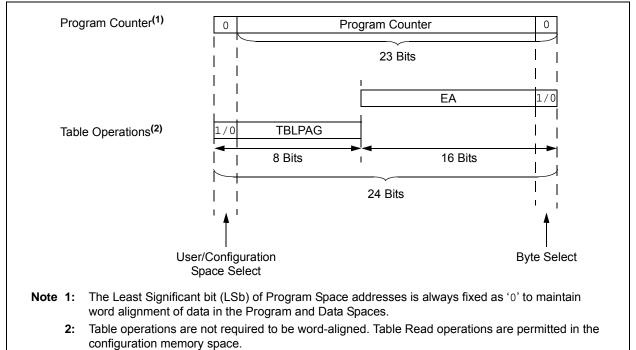

### 4.8 Interfacing Program and Data Memory Spaces

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture uses a 24-bit-wide Program Space (PS) and a 16-bit-wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

### TABLE 4-65: PROGRAM SPACE ADDRESS CONSTRUCTION

|                        | Access        | Program Space Address |               |          |             |     |  |  |  |  |

|------------------------|---------------|-----------------------|---------------|----------|-------------|-----|--|--|--|--|

| Access Type            | Space         | <23>                  | <22:16>       | <15>     | <14:1>      | <0> |  |  |  |  |

| Instruction Access     | User          | 0                     |               | PC<22:1> | 0           |     |  |  |  |  |

| (Code Execution)       |               |                       | 0xx xxxx x    | xxx xxx  | x xxxx xxx0 |     |  |  |  |  |

| TBLRD/TBLWT            | User          | TB                    | Data EA<15:0> |          |             |     |  |  |  |  |

| (Byte/Word Read/Write) |               | 0                     | xxx xxxx      | XXXX XXX |             |     |  |  |  |  |

|                        | Configuration | TBLPAG<7:0> Data EA<1 |               |          |             |     |  |  |  |  |

|                        |               | 1                     | xxx xxxx      | XXXX XX  | ***         |     |  |  |  |  |

### FIGURE 4-22: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

### **REGISTER 8-7:** DMAXPAD: DMA CHANNEL X PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | PAD   | <15:8>            |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | PAE   | )<7:0>            |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

|                 |       |                  |       |                   |                  |                 |       |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

#### bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

### REGISTER 8-8: DMAXCNT: DMA CHANNEL X TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0             | U-0   | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

| —               |       |                  |       | CNT<              | 13:8> <b>(2)</b> |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | CNT<  | <7:0> <b>(2)</b>  |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable b  | oit   | W = Writable b   | bit   | U = Unimplen      | nented bit, rea  | id as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

**2:** The number of DMA transfers = CNT<13:0> + 1.

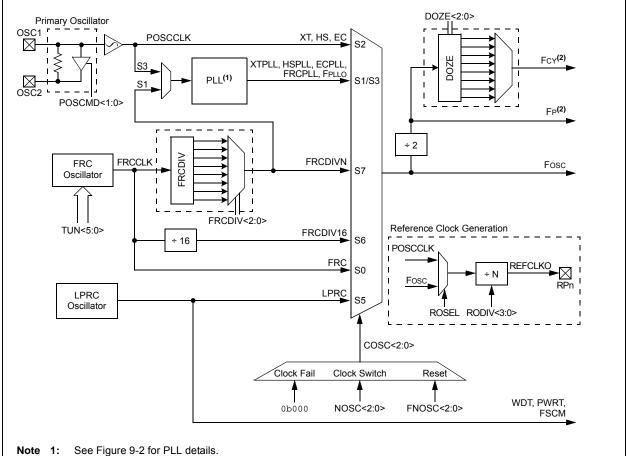

### 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator" (DS70580) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X oscillator system provides:

- On-chip Phase-Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources

- On-the-fly clock switching between various clock sources

- · Doze mode for system power savings

- Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Configuration bits for clock source selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

### FIGURE 9-1: OSCILLATOR SYSTEM DIAGRAM

2: The term, FP, refers to the clock source for all peripherals, while FCY refers to the clock source for the CPU. Throughout this document, FCY and FP are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used with a doze ratio of 1:2 or lower.

### 9.3 Oscillator Control Registers

### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0            | R-0                                                                | R-0                                                     | R-0                                | U-0                                | R/W-y                              | R/W-y                | R/W-y                |  |  |  |  |  |  |

|----------------|--------------------------------------------------------------------|---------------------------------------------------------|------------------------------------|------------------------------------|------------------------------------|----------------------|----------------------|--|--|--|--|--|--|

| _              | COSC2                                                              | COSC1                                                   | COSC0                              | —                                  | NOSC2 <sup>(2)</sup>               | NOSC1 <sup>(2)</sup> | NOSCO <sup>(2)</sup> |  |  |  |  |  |  |

| bit 15         |                                                                    |                                                         |                                    |                                    |                                    |                      | bit 8                |  |  |  |  |  |  |

| R/W-0          | R/W-0                                                              | R-0                                                     | U-0                                | R/W-0                              | U-0                                | U-0                  | R/W-0                |  |  |  |  |  |  |

| CLKLOC         | CK IOLOCK                                                          | LOCK                                                    |                                    | CF <sup>(3)</sup>                  |                                    |                      | OSWEN                |  |  |  |  |  |  |

| bit 7          |                                                                    |                                                         |                                    |                                    |                                    |                      | bit (                |  |  |  |  |  |  |

| Legend:        |                                                                    | y = Value set                                           | from Configur                      | ation bits on F                    | POR                                |                      |                      |  |  |  |  |  |  |

| R = Reada      | able bit                                                           | W = Writable                                            | -                                  |                                    | mented bit, read                   | l as '0'             |                      |  |  |  |  |  |  |

| -n = Value     | at POR                                                             | '1' = Bit is se                                         | t                                  | '0' = Bit is cle                   | eared                              | x = Bit is unkr      | nown                 |  |  |  |  |  |  |

| hit 1 <i>5</i> | Unimplemen                                                         | ted. Dood oo                                            | 0'                                 |                                    |                                    |                      |                      |  |  |  |  |  |  |

| bit 15         | -                                                                  | ted: Read as                                            |                                    |                                    |                                    |                      |                      |  |  |  |  |  |  |

| bit 14-12      |                                                                    | Current Oscill                                          |                                    |                                    | /)                                 |                      |                      |  |  |  |  |  |  |

|                |                                                                    | C Oscillator (F<br>C Oscillator (F                      |                                    |                                    |                                    |                      |                      |  |  |  |  |  |  |

|                |                                                                    | ower RC Oscil                                           |                                    |                                    |                                    |                      |                      |  |  |  |  |  |  |

|                | 100 = Reserv                                                       |                                                         | ()                                 |                                    |                                    |                      |                      |  |  |  |  |  |  |

|                |                                                                    | y Oscillator (X                                         |                                    | h PLL                              |                                    |                      |                      |  |  |  |  |  |  |

|                |                                                                    | y Oscillator (X                                         |                                    |                                    |                                    |                      |                      |  |  |  |  |  |  |

|                |                                                                    | C Oscillator (F<br>C Oscillator (F                      |                                    | le-by-N and Pl                     | LL (FRCPLL)                        |                      |                      |  |  |  |  |  |  |

| bit 11         |                                                                    | Unimplemented: Read as '0'                              |                                    |                                    |                                    |                      |                      |  |  |  |  |  |  |

| bit 10-8       | NOSC<2:0>:                                                         | NOSC<2:0>: New Oscillator Selection bits <sup>(2)</sup> |                                    |                                    |                                    |                      |                      |  |  |  |  |  |  |

|                | 111 = Fast R                                                       | C Oscillator (F                                         | RC) with Divid                     | le-by-n                            |                                    |                      |                      |  |  |  |  |  |  |

|                |                                                                    | C Oscillator (F                                         |                                    | le-by-16                           |                                    |                      |                      |  |  |  |  |  |  |

|                |                                                                    | ower RC Oscil                                           | ator (LPRC)                        |                                    |                                    |                      |                      |  |  |  |  |  |  |

|                | 100 = Reserv                                                       | /ed<br>y Oscillator (X                                  |                                    |                                    |                                    |                      |                      |  |  |  |  |  |  |

|                |                                                                    | y Oscillator (X                                         |                                    | IFLL                               |                                    |                      |                      |  |  |  |  |  |  |

|                |                                                                    | C Oscillator (F                                         |                                    | le-by-N and Pl                     | LL (FRCPLL)                        |                      |                      |  |  |  |  |  |  |

|                |                                                                    | C Oscillator (F                                         |                                    | ,                                  | ,                                  |                      |                      |  |  |  |  |  |  |

| bit 7          |                                                                    | Clock Lock Ena                                          |                                    |                                    |                                    |                      |                      |  |  |  |  |  |  |

|                |                                                                    |                                                         |                                    | configurations                     | are locked; if (F                  | =CKSM0 = 0), t       | then clock and       |  |  |  |  |  |  |

|                |                                                                    | figurations may<br>d PLL selectio                       |                                    | ked, configurat                    | ions may be mo                     | odified              |                      |  |  |  |  |  |  |

| bit 6          |                                                                    | Lock Enable b                                           |                                    | -                                  | -                                  |                      |                      |  |  |  |  |  |  |

|                | 1 = I/O lock is                                                    | s active                                                |                                    |                                    |                                    |                      |                      |  |  |  |  |  |  |

|                | 0 = I/O lock is                                                    | s not active                                            |                                    |                                    |                                    |                      |                      |  |  |  |  |  |  |

| bit 5          | LOCK: PLL L                                                        | ock Status bit                                          | (read-only)                        |                                    |                                    |                      |                      |  |  |  |  |  |  |

|                |                                                                    | s that PLL is in<br>s that PLL is ou                    |                                    |                                    | satisfied<br>progress or PLL       | is disabled          |                      |  |  |  |  |  |  |

| Note 1:        | Writes to this regis                                               |                                                         |                                    |                                    |                                    |                      | ʻdsPIC33/            |  |  |  |  |  |  |

| 2:             | Direct clock switch<br>This applies to cloo<br>mode as a transitio | es between ar<br>ck switches in                         | y primary osci<br>either directior | llator mode wi<br>n. In these inst | th PLL and FRC<br>ances, the appli | PLL mode are         |                      |  |  |  |  |  |  |

| 0              | This bit should only                                               |                                                         |                                    |                                    |                                    |                      |                      |  |  |  |  |  |  |

**3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

| R/W-0         | U-0                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| ROON          |                                                                                                                                                                                                                                              | ROSSLP                                                                                                                                                                                                                                                                                                                                                                                                   | ROSEL                                                                                                                                                                                                                 | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |

| bit 15        |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       | •                     | bit                   |

| U-0           | U-0                                                                                                                                                                                                                                          | U-0                                                                                                                                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                                                                                                   | U-0                   | U-0                   | U-0                   | U-0                   |

|               | _                                                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                       | _                     |                       | _                     |                       |

| bit 7         |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       |                       | bit                   |

| Legend:       |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       |                       |                       |

| R = Readable  | e bit                                                                                                                                                                                                                                        | W = Writable                                                                                                                                                                                                                                                                                                                                                                                             | bit                                                                                                                                                                                                                   | U = Unimpler          | nented bit, read      | l as '0'              |                       |

| -n = Value at |                                                                                                                                                                                                                                              | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                       | '0' = Bit is cle      |                       | x = Bit is unkr       | iown                  |

| bit 14        | 0 = Reference                                                                                                                                                                                                                                | e oscillator outp<br>e oscillator outp<br>i <b>ted:</b> Read as '                                                                                                                                                                                                                                                                                                                                        | out is disabled                                                                                                                                                                                                       |                       | .K pin <sup>(2)</sup> |                       |                       |

| bit 13        | -                                                                                                                                                                                                                                            | ference Oscilla                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       | en hit                |                       |                       |                       |

|               | 1 = Reference                                                                                                                                                                                                                                | e oscillator out<br>e oscillator out                                                                                                                                                                                                                                                                                                                                                                     | out continues                                                                                                                                                                                                         | to run in Sleep       |                       |                       |                       |

| bit 12        | 1 = Oscillator                                                                                                                                                                                                                               | erence Oscillato<br>crystal is used<br>lock is used as                                                                                                                                                                                                                                                                                                                                                   | as the refere                                                                                                                                                                                                         | nce clock             |                       |                       |                       |

| bit 11-8      | 1111 = Refer<br>1110 = Refer<br>1101 = Refer<br>1000 = Refer<br>1011 = Refer<br>1001 = Refer<br>1000 = Refer<br>0111 = Refer<br>0111 = Refer<br>0101 = Refer<br>0100 = Refer<br>0101 = Refer<br>0011 = Refer<br>0011 = Refer<br>0011 = Refer | Reference Os<br>rence clock divi<br>rence clock divi | ded by 32,763<br>ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048<br>ded by 1,024<br>ded by 512<br>ded by 512<br>ded by 256<br>ded by 128<br>ded by 64<br>ded by 32<br>ded by 16<br>ded by 8<br>ded by 4 | 8                     |                       |                       |                       |

|               | 0000 = Refer                                                                                                                                                                                                                                 | ence clock                                                                                                                                                                                                                                                                                                                                                                                               | -                                                                                                                                                                                                                     |                       |                       |                       |                       |

### REGISTER 9-5: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

### REGISTER 11-15: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0                | R/W-0                                      | R/W-0                                           | R/W-0                                      | R/W-0                       | R/W-0         | R/W-0              | R/W-0 |  |

|--------------------|--------------------------------------------|-------------------------------------------------|--------------------------------------------|-----------------------------|---------------|--------------------|-------|--|

|                    |                                            |                                                 |                                            | SYNCI1R<6:03                | >             |                    |       |  |

| bit 15             |                                            |                                                 |                                            |                             |               |                    | bit 8 |  |

|                    |                                            |                                                 |                                            |                             |               |                    |       |  |

| U-0                | U-0                                        | U-0                                             | U-0                                        | U-0                         | U-0           | U-0                | U-0   |  |

| _                  |                                            |                                                 | —                                          |                             |               | <u> </u>           | _     |  |

| bit 7              |                                            |                                                 |                                            |                             |               |                    | bit 0 |  |

|                    |                                            |                                                 |                                            |                             |               |                    |       |  |

| Legend:            |                                            |                                                 |                                            |                             |               |                    |       |  |

| R = Readab         | ole bit                                    | W = Writable                                    | bit                                        | U = Unimplem                | l as '0'      |                    |       |  |

| -n = Value a       | it POR                                     | '1' = Bit is set                                |                                            | '0' = Bit is clea           | ared          | x = Bit is unknown |       |  |

|                    |                                            |                                                 |                                            |                             |               |                    |       |  |

|                    |                                            |                                                 |                                            |                             |               |                    |       |  |

| bit 15             | Unimplemer                                 | nted: Read as '                                 | 0'                                         |                             |               |                    |       |  |

| bit 15<br>bit 14-8 | SYNCI1R<6:                                 |                                                 | M Synchroniz                               | zation Input 1 to<br>nbers) | the Correspon | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11                | <b>0&gt;:</b> Assign PW                         | M Synchroniz selection nur                 |                             | the Correspon | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                             | the Correspon | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                             | the Correspon | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11<br>1111001 = I | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz<br>selection nur<br>121<br>P1 |                             | the Correspon | ding RPn Pin b     | its   |  |

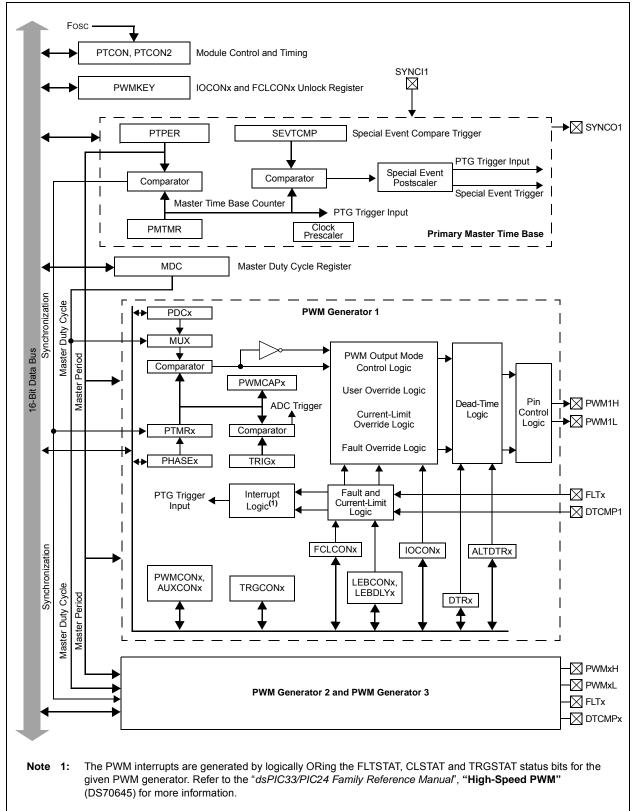

#### FIGURE 16-2: HIGH-SPEED PWMx MODULE REGISTER INTERCONNECTION DIAGRAM

### REGISTER 17-2: QEI1IOC: QEI1 I/O CONTROL REGISTER (CONTINUED)

- bit 2 INDEX: Status of INDXx Input Pin After Polarity Control

- 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

- bit 1 QEB: Status of QEBx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1' 0 = Pin is at logic '0'

- bit 0 **QEA:** Status of QEAx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

### REGISTER 24-12: PTGQPTR: PTG STEP QUEUE POINTER REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0   | U-0   | U-0         | U-0   | U-0   |

|--------|-----|-----|-------|-------|-------------|-------|-------|

| —      | —   | —   | —     | —     |             | _     | —     |

| bit 15 |     |     |       |       |             |       | bit 8 |

|        |     |     |       |       |             |       |       |

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 |

| _      |     |     |       |       | PTGQPTR<4:0 | >     |       |

| bit 7  |     |     |       |       |             |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 **PTGQPTR<4:0>:** PTG Step Queue Pointer Register bits This register points to the currently active Step command in the Step queue.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

### **REGISTER 24-13: PTGQUEX: PTG STEP QUEUE REGISTER x (x = 0-7)**<sup>(1,3)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0     | R/W-0                | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-----------|----------------------|-------|-------|-------|

|        |       |       | STEP(2x + | - 1)<7:0> <b>(2)</b> |       |       |       |

| bit 15 |       |       |           |                      |       |       | bit 8 |

|        |       |       |           |                      |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0     | R/W-0                | R/W-0 | R/W-0 | R/W-0 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0                  | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|---------|------------------------|-------|-------|-------|

|       |       |       | STEP(2x | ()<7:0> <sup>(2)</sup> |       |       |       |

| bit 7 |       |       |         |                        |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-8 | STEP(2x + 1)<7:0>: PTG Step Queue Pointer Register bits <sup>(2)</sup> |

|----------|------------------------------------------------------------------------|

|          | A queue location for storage of the STEP(2x + 1) command byte.         |

| bit 7-0  | STEP(2x)<7:0>: PTG Step Queue Pointer Register bits <sup>(2)</sup>     |

|          | A queue location for storage of the STEP(2x) command byte.             |

- **Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

- 2: Refer to Table 24-1 for the Step command encoding.

**3:** The Step registers maintain their values on any type of Reset.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

### REGISTER 26-3: CRCXORH: CRC XOR POLYNOMIAL HIGH REGISTER

| R/W-0                             | R/W-0                                                        | R/W-0                              | R/W-0           | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-----------------------------------|--------------------------------------------------------------|------------------------------------|-----------------|--------|-------|-------|-------|

|                                   |                                                              |                                    | X<3             | 31:24> |       |       |       |

| bit 15                            |                                                              |                                    |                 |        |       |       | bit 8 |

|                                   |                                                              |                                    |                 |        |       |       |       |

| R/W-0                             | R/W-0                                                        | R/W-0                              | R/W-0           | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|                                   |                                                              |                                    | X<2             | 23:16> |       |       |       |

| bit 7                             |                                                              |                                    |                 |        |       |       | bit 0 |

|                                   |                                                              |                                    |                 |        |       |       |       |

| Legend:                           |                                                              |                                    |                 |        |       |       |       |

| R = Readable bit W = Writable bit |                                                              | U = Unimplemented bit, read as '0' |                 |        |       |       |       |

| -n = Value at P                   | e at POR '1' = Bit is set '0' = Bit is cleared x = Bit is ur |                                    | x = Bit is unkr | nown   |       |       |       |

|                                   |                                                              |                                    |                 |        |       |       |       |

bit 15-0 X<31:16>: XOR of Polynomial Term X<sup>n</sup> Enable bits

#### REGISTER 26-4: CRCXORL: CRC XOR POLYNOMIAL LOW REGISTER

| R/W-0                             | R/W-0 | R/W-0                              | R/W-0  | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|-----------------------------------|-------|------------------------------------|--------|-----------------------------------------|-------|-------|-------|

|                                   |       |                                    | Х<     | 15:8>                                   |       |       |       |

| bit 15                            |       |                                    |        |                                         |       |       | bit 8 |

| R/W-0                             | R/W-0 | R/W-0                              | R/W-0  | R/W-0                                   | R/W-0 | R/W-0 | U-0   |

|                                   |       |                                    | X<7:1> |                                         |       |       | _     |

| bit 7                             |       |                                    |        |                                         |       |       | bit 0 |

| Legend:                           |       |                                    |        |                                         |       |       |       |

| R = Readable bit W = Writable bit |       | U = Unimplemented bit, read as '0' |        |                                         |       |       |       |

| -n = Value at P                   | OR    | '1' = Bit is set                   |        | '0' = Bit is cleared x = Bit is unknown |       | nown  |       |

bit 15-1X<15:1>: XOR of Polynomial Term X<sup>n</sup> Enable bitsbit 0Unimplemented: Read as '0'

### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| DC CHARACTERISTICS |                           |      | (unless othe | •      | <b>s: 3.0V to 3.6V</b><br>≤ Ta ≤ +85°C for Indi<br>≤ Ta ≤ +125°C for Ex |           |

|--------------------|---------------------------|------|--------------|--------|-------------------------------------------------------------------------|-----------|

| Parameter<br>No.   | Тур.                      | Max. | Units        |        | Conditions                                                              |           |

| Operating Cur      | rent (IDD) <sup>(1)</sup> |      |              |        |                                                                         |           |

| DC20d              | 9                         | 15   | mA           | -40°C  |                                                                         |           |

| DC20a              | 9                         | 15   | mA           | +25°C  | 3.3V                                                                    | 10 MIPS   |

| DC20b              | 9                         | 15   | mA           | +85°C  | 3.3V                                                                    | 10 1011-5 |

| DC20c              | 9                         | 15   | mA           | +125°C |                                                                         |           |

| DC22d              | 16                        | 25   | mA           | -40°C  |                                                                         |           |

| DC22a              | 16                        | 25   | mA           | +25°C  | 3.3∨                                                                    | 20 MIPS   |

| DC22b              | 16                        | 25   | mA           | +85°C  | 3.3V                                                                    | 20 MIF 3  |

| DC22c              | 16                        | 25   | mA           | +125°C |                                                                         |           |

| DC24d              | 27                        | 40   | mA           | -40°C  |                                                                         |           |

| DC24a              | 27                        | 40   | mA           | +25°C  | 3.3V                                                                    | 40 MIPS   |

| DC24b              | 27                        | 40   | mA           | +85°C  | 3.3V                                                                    | 40 1011-5 |

| DC24c              | 27                        | 40   | mA           | +125°C |                                                                         |           |

| DC25d              | 36                        | 55   | mA           | -40°C  |                                                                         |           |

| DC25a              | 36                        | 55   | mA           | +25°C  | 3.3V                                                                    | 60 MIPS   |

| DC25b              | 36                        | 55   | mA           | +85°C  | 3.3V                                                                    | OU IVIIPS |

| DC25c              | 36                        | 55   | mA           | +125°C | 7                                                                       |           |

| DC26d              | 41                        | 60   | mA           | -40°C  |                                                                         |           |

| DC26a              | 41                        | 60   | mA           | +25°C  | 3.3V                                                                    | 70 MIPS   |

| DC26b              | 41                        | 60   | mA           | +85°C  |                                                                         |           |

#### TABLE 30-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

**Note 1:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

• Oscillator is configured in EC mode with PLL, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU is executing while(1) {NOP(); } statement

- · JTAG is disabled

| DC CHARACTERISTICS |                               |               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                       |                 |  |  |

|--------------------|-------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|--|--|

| Parameter<br>No.   | Тур.                          | Max.          | Units                                                                                                                                                                                                                                                                                   | Condi                 | tions           |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> - | dsPIC33EP32GI | P50X, dsPIC33EF                                                                                                                                                                                                                                                                         | P32MC20X/50X and PIC2 | 4EP32GP/MC20X   |  |  |

| DC60d              | 30                            | 100           | μA                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |

| DC60a              | 35                            | 100           | μA                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |

| DC60b              | 150                           | 200           | μA                                                                                                                                                                                                                                                                                      | +85°C                 | 3.3V            |  |  |

| DC60c              | 250                           | 500           | μA                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP64GI | P50X, dsPIC33EF                                                                                                                                                                                                                                                                         | P64MC20X/50X and PIC2 | 4EP64GP/MC20X   |  |  |

| DC60d              | 25                            | 100           | μA                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |

| DC60a              | 30                            | 100           | μA                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |

| DC60b              | 150                           | 350           | μΑ                                                                                                                                                                                                                                                                                      | +85°C                 | 3.3V            |  |  |

| DC60c              | 350                           | 800           | μΑ                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP128G | P50X, dsPIC33E                                                                                                                                                                                                                                                                          | P128MC20X/50X and PIC | 24EP128GP/MC20X |  |  |

| DC60d              | 30                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |

| DC60a              | 35                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |

| DC60b              | 150                           | 350           | μΑ                                                                                                                                                                                                                                                                                      | +85°C                 | 5.50            |  |  |

| DC60c              | 550                           | 1000          | μΑ                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP256G | P50X, dsPIC33E                                                                                                                                                                                                                                                                          | P256MC20X/50X and PIC | 24EP256GP/MC20X |  |  |

| DC60d              | 35                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |