Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128gp204-e-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

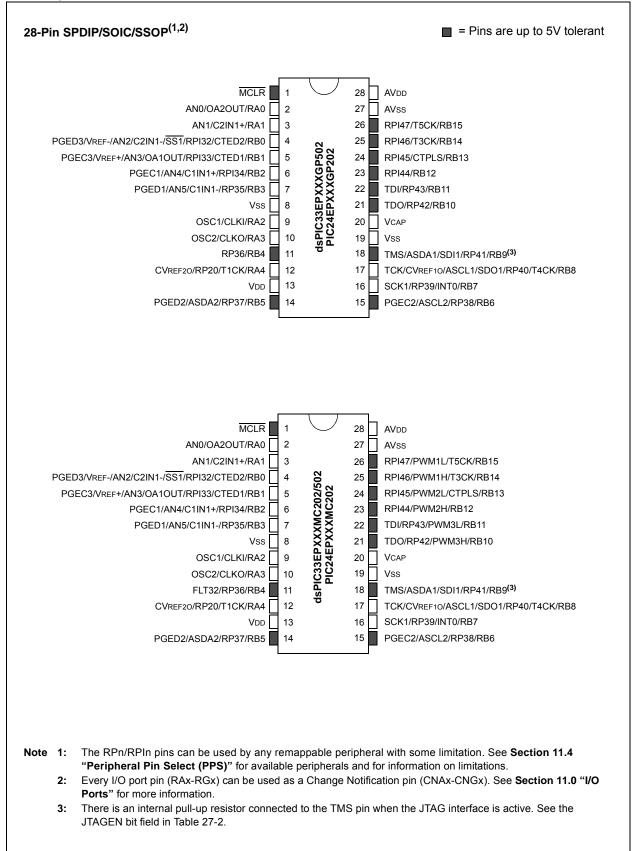

### **Pin Diagrams**

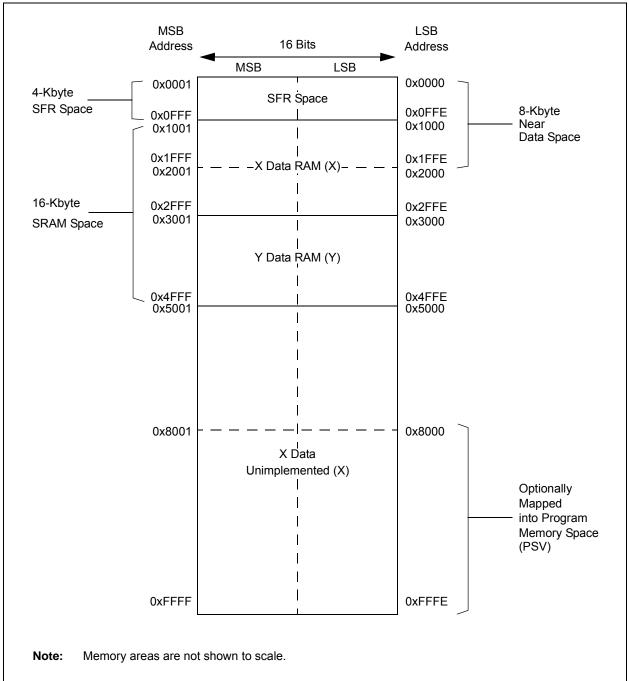

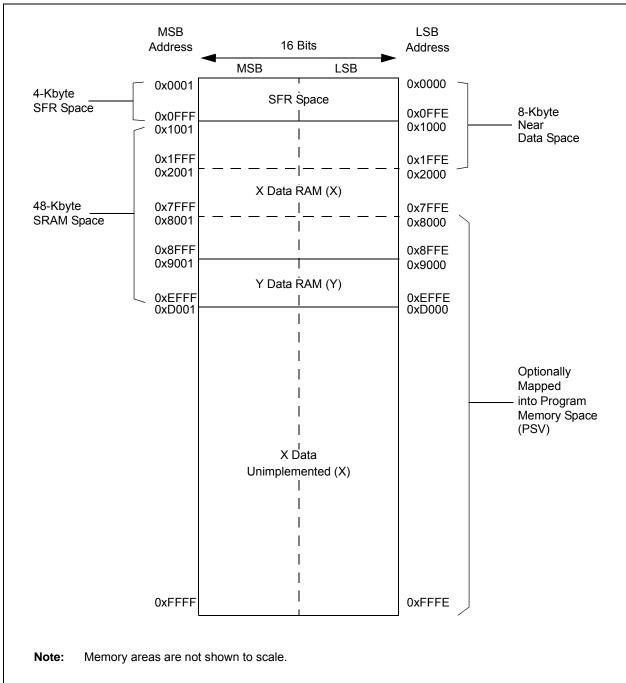

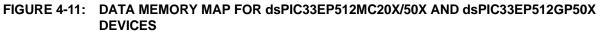

# FIGURE 4-9: DATA MEMORY MAP FOR dsPIC33EP128MC20X/50X AND dsPIC33EP128GP50X DEVICES

|                 |       |                |             |         |         |         |            |            |             |                                                       |        |       |       |       |       |       |        | All    |

|-----------------|-------|----------------|-------------|---------|---------|---------|------------|------------|-------------|-------------------------------------------------------|--------|-------|-------|-------|-------|-------|--------|--------|

| File Name       | Addr. | Bit 15         | Bit 14      | Bit 13  | Bit 12  | Bit 11  | Bit 10     | Bit 9      | Bit 8       | Bit 7                                                 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Resets |

| PTGCST          | 0AC0  | PTGEN          | —           | PTGSIDL | PTGTOGL |         | PTGSWT     | PTGSSEN    | PTGIVIS     | PTGSTRT                                               | PTGWTO | _     | _     | —     | —     | PTGIT | M<1:0> | 0000   |

| PTGCON          | 0AC2  | F              | PTGCLK<2    | :0>     |         | F       | PTGDIV<4:0 | >          |             | PTGPWD<3:0> — PTGWDT<2:0>                             |        |       |       |       |       | 0000  |        |        |

| PTGBTE          | 0AC4  |                | ADC         | TS<4:1> |         | IC4TSS  | IC3TSS     | IC2TSS     | IC1TSS      | 6 OC4CS OC3CS OC2CS OC1CS OC4TSS OC3TSS OC2TSS OC1TSS |        |       |       |       |       | 0000  |        |        |

| PTGHOLD         | 0AC6  |                |             |         |         |         |            |            | PTGHOLD     | D<15:0>                                               |        |       |       |       |       |       | 0000   |        |

| <b>PTGT0LIM</b> | 0AC8  |                |             |         |         |         |            |            | PTGT0LIM    | <15:0>                                                |        |       |       |       |       |       |        | 0000   |

| PTGT1LIM        | 0ACA  |                |             |         |         |         |            |            | PTGT1LIM    | <15:0>                                                |        |       |       |       |       |       |        | 0000   |

| PTGSDLIM        | 0ACC  |                |             |         |         |         |            |            | PTGSDLIN    | l<15:0>                                               |        |       |       |       |       |       |        | 0000   |

| <b>PTGC0LIM</b> | 0ACE  |                |             |         |         |         |            |            | PTGC0LIN    | <15:0>                                                |        |       |       |       |       |       |        | 0000   |

| PTGC1LIM        | 0AD0  | PTGC1LIM<15:0> |             |         |         |         |            |            |             |                                                       |        | 0000  |       |       |       |       |        |        |

| PTGADJ          | 0AD2  |                |             |         |         |         |            |            | PTGADJ<     | <15:0>                                                |        |       |       |       |       |       | 0000   |        |

| PTGL0           | 0AD4  |                |             |         |         |         |            |            | PTGL0<      | :15:0>                                                |        |       |       |       |       |       | 0000   |        |

| PTGQPTR         | 0AD6  | —              | —           | —       | —       | _       | —          | —          | _           | PTGQPTR<4:0>                                          |        |       |       |       |       | 0000  |        |        |

| PTGQUE0         | 0AD8  |                |             |         | STEP    | 1<7:0>  |            |            |             | STEP0<7:0>                                            |        |       |       |       |       |       | 0000   |        |

| PTGQUE1         | 0ADA  |                |             |         | STEP    | '3<7:0> |            |            |             | STEP2<7:0>                                            |        |       |       |       |       |       | 0000   |        |

| PTGQUE2         | 0ADC  |                |             |         | STEP    | 25<7:0> |            |            |             |                                                       |        |       | STEP4 | <7:0> |       |       |        | 0000   |

| PTGQUE3         | 0ADE  |                | STEP7<7:0>  |         |         |         |            |            |             | STEP6<7:0>                                            |        |       |       |       |       |       | 0000   |        |

| PTGQUE4         | 0AE0  | STEP9<7:0>     |             |         |         |         |            | STEP8<7:0> |             |                                                       |        |       |       |       | 0000  |       |        |        |

| PTGQUE5         | 0AE2  | STEP11<7:0>    |             |         |         |         |            |            | STEP10<7:0> |                                                       |        |       |       |       | 0000  |       |        |        |

| PTGQUE6         | 0AE4  | STEP13<7:0>    |             |         |         |         |            |            | STEP12<7:0> |                                                       |        |       |       |       | 0000  |       |        |        |

| PTGQUE7         | 0AE6  |                | STEP15<7:0> |         |         |         |            |            |             | STEP14<7:0>                                           |        |       |       |       |       | 0000  |        |        |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 78

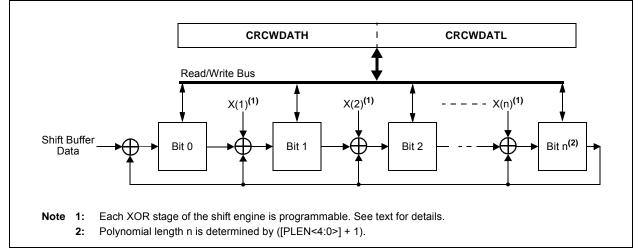

### TABLE 4-24: CRC REGISTER MAP

| File Name | Addr. | Bit 15 | 15   Bit 14   Bit 13   Bit 12   Bit 11   Bit 10   Bit 9   Bit 8   Bit 7   Bit 6   Bit 5   Bit 4   Bit 3   Bit 2   Bit 1   Bit 0 |                          |  |   |          |    |  |        |        | All<br>Resets |       |         |   |   |   |      |

|-----------|-------|--------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|---|----------|----|--|--------|--------|---------------|-------|---------|---|---|---|------|

| CRCCON1   | 0640  | CRCEN  | —                                                                                                                               | CSIDL                    |  | V | WORD<4:0 | )> |  | CRCFUL | CRCMPT | CRCISEL       | CRCGO | LENDIAN | _ | _ | — | 0000 |

| CRCCON2   | 0642  |        | _                                                                                                                               | DWIDTH<4:0> PLEN<4:0> 00 |  |   |          |    |  |        |        | 0000          |       |         |   |   |   |      |

| CRCXORL   | 0644  |        | X<15:1>0                                                                                                                        |                          |  |   |          |    |  |        | 0000   |               |       |         |   |   |   |      |

| CRCXORH   | 0646  |        | X<31:16>                                                                                                                        |                          |  |   |          |    |  |        | 0000   |               |       |         |   |   |   |      |

| CRCDATL   | 0648  |        | CRC Data Input Low Word                                                                                                         |                          |  |   |          |    |  | 0000   |        |               |       |         |   |   |   |      |

| CRCDATH   | 064A  |        | CRC Data Input High Word                                                                                                        |                          |  |   |          |    |  | 0000   |        |               |       |         |   |   |   |      |

| CRCWDATL  | 064C  |        | CRC Result Low Word                                                                                                             |                          |  |   |          |    |  | 0000   |        |               |       |         |   |   |   |      |

| CRCWDATH  | 064E  |        | CRC Result High Word                                                                                                            |                          |  |   |          |    |  | 0000   |        |               |       |         |   |   |   |      |

Legend: — = unimplemented, read as '0'. Shaded bits are not used in the operation of the programmable CRC module.

# TABLE 4-25: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC202/502 AND PIC24EPXXXGP/MC202 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5        | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|------------|--------|--------|-------|-------|-------|------------|--------------|------------|-------|-------|-------|-------|---------------|

| RPOR0        | 0680  | —      | —      |        | RP35R<5:0> |        |        |       |       | _     | _          | RP20R<5:0> 0 |            |       |       |       |       |               |

| RPOR1        | 0682  | _      | _      |        | RP37R<5:0> |        |        |       |       | _     | Ι          |              | RP36R<5:0> |       |       |       |       |               |

| RPOR2        | 0684  | _      | _      |        | RP39R<5:0> |        |        |       | _     | Ι     | RP38R<5:0> |              |            |       |       | 0000  |       |               |

| RPOR3        | 0686  | _      | _      |        | RP41R<5:0> |        |        |       | _     | Ι     | RP40R<5:0> |              |            |       |       | 0000  |       |               |

| RPOR4        | 0688  | _      | _      |        | RP43R<5:0> |        |        |       | —     | _     | RP42R<5:0> |              |            |       |       | 0000  |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-26: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC203/503 AND PIC24EPXXXGP/MC203 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5      | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|------------|--------|--------|-------|-------|-------|------------|------------|-------|--------|--------|-------|-------|---------------|

| RPOR0        | 0680  |        | —      |        |            | RP35F  | R<5:0> |       |       | _     | _          |            |       | RP20F  | २<5:0> |       |       | 0000          |

| RPOR1        | 0682  | _      | _      |        |            | RP37F  | ۲<5:0> |       |       | _     | _          |            |       | RP36F  | २<5:0> |       |       | 0000          |

| RPOR2        | 0684  | _      | _      |        | RP39R<5:0> |        |        |       | _     | —     |            |            | RP38F | R<5:0> |        |       | 0000  |               |

| RPOR3        | 0686  | _      | _      |        | RP41R<5:0> |        |        |       |       | _     | —          | RP40R<5:0> |       |        |        |       | 0000  |               |

| RPOR4        | 0688  | _      | _      |        | RP43R<5:0> |        |        |       |       | _     | _          | RP42R<5:0> |       |        |        | 0000  |       |               |

| RPOR5        | 068A  | _      | _      | _      | _          | _      | _      |       | _     | _     | _          | _          | _     | _      | —      |       |       | 0000          |

| RPOR6        | 068C  | _      | —      | —      |            |        |        |       | _     | —     | RP56R<5:0> |            |       |        |        | 0000  |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

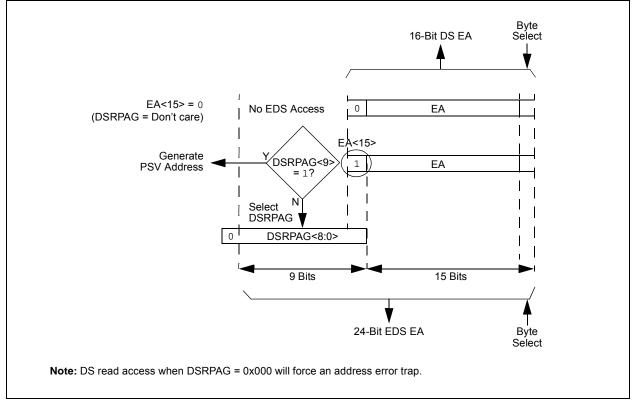

### 4.4.1 PAGED MEMORY SCHEME

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre-modified and post-modified Effective Addresses (EA). The upper half of the base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Read Page register (DSRPAG) or the 9-bit Write Page register (DSWPAG), to form an Extended Data Space (EDS) address or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

Construction of the EDS address is shown in Example 4-1. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when base address bit, EA<15> = 1, DSWPAG<8:0> are concatenated onto EA<14:0> to form the 24-bit EDS write address.

# 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions. which apply to dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

### 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

### 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                                          | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | U-0                              | U-0                                                                                              | U-0                               | U-0                      | U-0                         | U-0  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|-----------------------------|------|--|

|                                              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                | _                                                                                                | _                                 | _                        | _                           | _    |  |

| bit 15                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                  |                                                                                                  |                                   |                          |                             | bit  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                  |                                                                                                  |                                   |                          |                             |      |  |

| U-0                                          | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | U-0                              | R/W-0                                                                                            | R/W-0                             | U-0                      | U-0                         | U-0  |  |

| _                                            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                | DMA0MD <sup>(1)</sup><br>DMA1MD <sup>(1)</sup><br>DMA2MD <sup>(1)</sup><br>DMA3MD <sup>(1)</sup> | PTGMD                             | _                        | _                           | _    |  |

| bit 7                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                  |                                                                                                  |                                   |                          |                             | bit  |  |

| <b>Legend:</b><br>R = Readab<br>-n = Value a |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | W = Writable<br>'1' = Bit is set |                                                                                                  | U = Unimplen<br>'0' = Bit is clea | nented bit, read<br>ared | l as '0'<br>x = Bit is unkn | iown |  |

| bit 15-5<br>bit 4                            | Unimplemented: Read as '0'<br>DMA0MD: DMA0 Module Disable bit <sup>(1)</sup><br>1 = DMA0 module is disabled<br>0 = DMA0 module is enabled<br>DMA1MD: DMA1 Module Disable bit <sup>(1)</sup><br>1 = DMA1 module is disabled<br>0 = DMA1 module is enabled<br>DMA2MD: DMA2 Module Disable bit <sup>(1)</sup><br>1 = DMA2 module is disabled<br>0 = DMA2 module is enabled<br>DMA3MD: DMA3 Module Disable bit <sup>(1)</sup><br>1 = DMA3 module is disabled<br>0 = DMA3 module is disabled<br>0 = DMA3 module is disabled |                                  |                                                                                                  |                                   |                          |                             |      |  |

| bit 3                                        | <b>PTGMD:</b> PTG Module Disable bit<br>1 = PTG module is disabled<br>0 = PTG module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                        |                                  |                                                                                                  |                                   |                          |                             |      |  |

| bit 2-0                                      | Unimplement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ted: Read as '                   | 0'                                                                                               |                                   |                          |                             |      |  |

| Note 1: T                                    | his single bit ena                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ables and disal                  | oles all four DM                                                                                 | A channels.                       |                          |                             |      |  |

### REGISTER 10-6: PMD7: PERIPHERAL MODULE DISABLE CONTROL REGISTER 7

#### 11.7 **Peripheral Pin Select Registers**

### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|------------|-------|-------|-------|

| —      |       |       |       | INT1R<6:0> |       |       |       |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

| —      | —     | —     | —     | —          | _     | _     | —     |

| bit 7  |       | •     |       | •          |       |       | bit 0 |

|        |       |       |       |            |       |       |       |

| Legend: |

|---------|

|---------|

| Legena:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15 | Unimplemented: Read as '0' |

|--------|----------------------------|

|--------|----------------------------|

bit 14-8 INT1R<6:0>: Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 0000001 = Input tied to CMP1 0000000 = Input tied to Vss bit 7-0 Unimplemented: Read as '0'

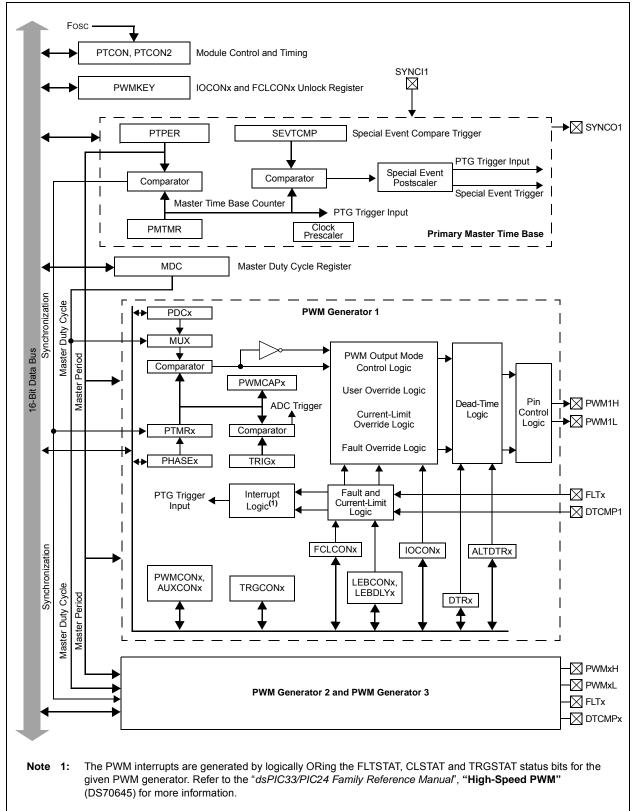

### FIGURE 16-2: HIGH-SPEED PWMx MODULE REGISTER INTERCONNECTION DIAGRAM

| U-0              | R/W-0                                    | R/W-0                              | R/W-0           | R/W-0                       | R/W-0                          | R/W-0                | R/W-0           |  |  |  |  |  |  |

|------------------|------------------------------------------|------------------------------------|-----------------|-----------------------------|--------------------------------|----------------------|-----------------|--|--|--|--|--|--|

| _                | CLSRC4                                   | CLSRC3                             | CLSRC2          | CLSRC1                      | CLSRC0                         | CLPOL <sup>(2)</sup> | CLMOD           |  |  |  |  |  |  |

| bit 15           |                                          |                                    | •               |                             |                                |                      | bit 8           |  |  |  |  |  |  |

|                  | <b>D</b> 4 4                             | D 0.01 4                           | <b>D</b> 444    |                             | DAMA                           | DAMA                 | DAMO            |  |  |  |  |  |  |

| R/W-1            | R/W-1                                    | R/W-1                              | R/W-1           | R/W-1                       | R/W-0<br>FLTPOL <sup>(2)</sup> | R/W-0                | R/W-0           |  |  |  |  |  |  |

| FLTSRC4<br>bit 7 | FLTSRC3                                  | FLTSRC2                            | FLTSRC1         | FLTSRC0                     | FLIPOL-                        | FLTMOD1              | FLTMOD0<br>bit  |  |  |  |  |  |  |

|                  |                                          |                                    |                 |                             |                                |                      | DI              |  |  |  |  |  |  |

| Legend:          |                                          |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

| R = Readable     | bit                                      | W = Writable                       | bit             | U = Unimpler                | mented bit, read               | l as '0'             |                 |  |  |  |  |  |  |

| -n = Value at I  | POR                                      | '1' = Bit is set                   |                 | '0' = Bit is cle            | ared                           | x = Bit is unkr      | nown            |  |  |  |  |  |  |

|                  |                                          |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

| bit 15           | Unimplemen                               | ted: Read as '                     | 0'              |                             |                                |                      |                 |  |  |  |  |  |  |

| bit 14-10        | CLSRC<4:0>                               | Current-Limit                      | Control Signa   | al Source Seleo             | ct for PWM Ger                 | nerator # bits       |                 |  |  |  |  |  |  |

|                  | 11111 = Fault 32                         |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | 11110 <b>= Res</b>                       | erved                              |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | •                                        |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | •                                        |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | •<br>01100 = Reserved                    |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | 01100 = Reserved<br>01011 = Comparator 4 |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  |                                          | Amp/Comparat                       | or 3            |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | •                                        | Amp/Comparat                       |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  |                                          | Amp/Comparat                       |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | 00111 = Res                              |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | 00110 <b>= Res</b>                       | erved                              |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | 00101 = Res                              | erved                              |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | 00100 <b>= Res</b>                       | erved                              |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | 00011 <b>= Fau</b>                       |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | 00010 <b>= Fau</b>                       |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | 00001 <b>= Fau</b>                       |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | 00000 <b>= Fau</b>                       | ( <i>j</i>                         |                 |                             | ~                              |                      |                 |  |  |  |  |  |  |

| bit 9            | CLPOL: Curr                              | ent-Limit Polar                    | ity for PWM G   | enerator # bit <sup>(</sup> | 2)                             |                      |                 |  |  |  |  |  |  |

|                  |                                          | cted current-lim                   |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | 0 = The selec                            | cted current-lim                   | it source is ac | tive-high                   |                                |                      |                 |  |  |  |  |  |  |

| bit 8            | CLMOD: Cur                               | rent-Limit Mode                    | e Enable for P  | WM Generator                | r # bit                        |                      |                 |  |  |  |  |  |  |

|                  |                                          | imit mode is er<br>imit mode is di |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | ne PWMLOCK                               |                                    |                 | <6>) is a '1', th           | e IOCONx regi                  | ster can only be     | e written aftei |  |  |  |  |  |  |

| the              | unlock sequen                            | ce has been ex                     | ecuted.         |                             |                                |                      |                 |  |  |  |  |  |  |

|                  |                                          |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

## REGISTER 16-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER<sup>(1)</sup>

2: These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

### 17.2 QEI Control Registers

|  | REGISTER 17-1: | QEI1CON: QEI1 CONTROL REGISTER |

|--|----------------|--------------------------------|

|--|----------------|--------------------------------|

| U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         —       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |                                                                                                  |                                                                                                                |                                                                                              |                                                                               |                                                            |                                   |                     |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------|---------------------|--|--|

| bit 15       bit 2         U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       -       intdividue       W= Writable bit       U = Unimplemented bit, read as '0'       bit 15       GEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to         bit 13       GEISDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD-2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       100 = Modulo Count mode for position counter         100 = Next index event after home event initializes position counter with contents of QEI1IC register       100 = Next index input event initializes position counter with contents of QEI1IC register       100 = Index input event dees not affect position coun                                                                                                                                                                                                  | R/W-0        | U-0                                                                                              | R/W-0                                                                                                          | R/W-0                                                                                        | R/W-0                                                                         | R/W-0                                                      | R/W-0                             | R/W-0               |  |  |

| U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       bit 0       Dit 7       Dit 7       Dit 7       Dit 7       Dit 7         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       Dit 7         en value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN:       Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0         0 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to       Dit 13       QEISDL: QEI Stop in Idle Mode bit         1 = Discontinues module operation in Idle mode       0 = Continues module operation in Idle mode       Di Continues module operation on In Idle mode         Dit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         100 = Modulo Count mode for position counter       101 = Resets the position counter       101 = Resets the position counter with contents of QEI1IC register         101 = Resets the position counter when the position counter with contents of QEI1IC register       000 = Index input e                                                                                                                                                                                                                                          | QEIEN        | _                                                                                                | QEISIDL                                                                                                        | PIMOD2 <sup>(1)</sup>                                                                        | PIMOD1 <sup>(1)</sup>                                                         | PIMOD0 <sup>(1)</sup>                                      | IMV1 <sup>(2)</sup>               | IMV0 <sup>(2)</sup> |  |  |

| -       INTDIV2 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       bit 7       bit 0         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       bit 0         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'       Bit is cleared       x = Bit is unknown         bit 13       QEISDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Modulo Count mode for position counter         10 = Resets the position counter when the position counter with contents of QEI1IC register       100 = Second index event after home event initializes position counter with contents of QEI1IC register         10 = Next index input event free home event initializes position counter with contents of QEI1IC register       00 = Index input event does not affect position counter         11 = Resets the position counter       110 = Next index input event me position counter       0 = Phase B match occurs when QEB = 1         0 = Phase B match occ                                                                                                                                                   | bit 15       |                                                                                                  |                                                                                                                |                                                                                              |                                                                               |                                                            |                                   | bit 8               |  |  |

| -       INTDIV2 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       bit 7       bit 0         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       bit 0         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'       Bit is cleared       x = Bit is unknown         bit 13       QEISDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Modulo Count mode for position counter         10 = Resets the position counter when the position counter with contents of QEI1IC register       100 = Second index event after home event initializes position counter with contents of QEI1IC register         10 = Next index input event free home event initializes position counter with contents of QEI1IC register       00 = Index input event does not affect position counter         11 = Resets the position counter       110 = Next index input event me position counter       0 = Phase B match occurs when QEB = 1         0 = Phase B match occ                                                                                                                                                   |              |                                                                                                  |                                                                                                                |                                                                                              |                                                                               |                                                            |                                   |                     |  |  |

| bit 7       bit 0         Legend:       W = Writable bit       U = Unimplemented bit, read as '0'         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Module counters are enabled         0 = Module counters are disabled, but SFRs can be read or written to       0 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'       0 = Continues module operation when device enters Idle mode         0 = Continues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD-2:0-: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Resets the position counter         101 = Resets the position counter when the position counter with contents of QEI1IC register         101 = Nexet input event after home event initializes position counter with contents of QEI1IC register         010 = Next index input event resets the position counter         011 = Every index input event resets the position counter         012 = Nease B match occurs when QEB = 1         0 = Phase B match occurs when QEB = 0         bit 8       IMV0: Index Match Value for Phase A bit <sup>(2)</sup> 1 = Phase A match occurs when QEA = 1 <t< td=""><td>U-0</td><td></td><td></td><td></td><td>R/W-0</td><td>R/W-0</td><td>R/W-0</td><td>R/W-0</td></t<>                                                                       | U-0          |                                                                                                  |                                                                                                                |                                                                                              | R/W-0                                                                         | R/W-0                                                      | R/W-0                             | R/W-0               |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0         0 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to       0         bit 14       Unimplemented: Read as '0'       0         bit 13       QEISIDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         11 = Reserved       111 = Reserved         110 = Modulo Count mode for position counter       101 = Resets the position counter when the position counter equals QEI1GEC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       100 = Second index event after home event initializes position counter with contents of QEI1IC register         101 = First index vent after home event initializes position counter with contents of QEI1IC register       001 = Every index input event resets the position counter         010 = Next index input event does not affect position counter       001 = Every index input event after home event initializes position counter with contents of QEI1IC register                                                                                                                                |              | INTDIV2 <sup>(3)</sup>                                                                           | INTDIV1 <sup>(3)</sup>                                                                                         | INTDIV0 <sup>(3)</sup>                                                                       | CNTPOL                                                                        | GATEN                                                      | CCM1                              |                     |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is cleared       x = Bit is unknown         bit 15       QEISIDL: QEI Stop in Idle Mode bit       1 = Module counters are disabled, but SFRs can be read or written to       bit 14         Unimplemented: Read as '0'       East as '0'       East as '0'       East as '0'         bit 13       QEISIDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       10 = Second index event after home event initializes position counter with contents of QEI1IC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter         101 = Reserved       III = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes position counter with contents of QEI1IC register         102 = Mext index input event does not affect position counter       01 = Phase                                                                                              | bit 7        |                                                                                                  |                                                                                                                |                                                                                              |                                                                               |                                                            |                                   | bit 0               |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is cleared       x = Bit is unknown         bit 15       QEISIDL: QEI Stop in Idle Mode bit       1 = Module counters are disabled, but SFRs can be read or written to       bit 14         Unimplemented: Read as '0'       East as '0'       East as '0'       East as '0'         bit 13       QEISIDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       10 = Second index event after home event initializes position counter with contents of QEI1IC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter         101 = Reserved       III = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes position counter with contents of QEI1IC register         102 = Mext index input event does not affect position counter       01 = Phase                                                                                              | Logondy      |                                                                                                  |                                                                                                                |                                                                                              |                                                                               |                                                            |                                   |                     |  |  |

| n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is unknown         bit 14       Unimplemented: Read as '0'       0'       0'       Bit is cleared       0 = Continues module operation when device enters ldle mode       0 = Continues module operation in ldle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       10 = Second index event after home event initializes position counter with contents of QEI11C register         100 = Second index event after home event initializes position counter with contents of QEI11C register       10 = Next index input event resets the position counter with contents of QEI11C register         101 = Every index input event resets the position counter       00 = Index input event does not affect position counter         001 = Every index input event genst bit <sup>(2)</sup> 1 = Phase B match occurs when QEB = 1         011 = Phase B match occurs when QEB = 1       0 = Phase B match occurs when QEA = 1         015 = Phase A match occurs when QEA = 1       0 = Phase A match occurs when QEA = 1         015 = Phase A match occurs when QEA =                                                                                                  |              | le hit                                                                                           | M = M/ritable                                                                                                  | hit                                                                                          | =   Inimpler                                                                  | mented hit read                                            | ae '0'                            |                     |  |  |

| bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit         1 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'         bit 13       QEISIDL: QEI Stop in Idle Mode bit         1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         11 = Discontinues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       100 = Second index event after home event initializes position counter with contents of QEI1IC register         011 = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event resets the position counter         001 = Nevery index input eve                                                                                                  |              |                                                                                                  |                                                                                                                |                                                                                              | •                                                                             |                                                            |                                   |                     |  |  |

| <ul> <li>1 = Module counters are enabled</li> <li>0 = Module counters are disabled, but SFRs can be read or written to</li> <li>bit 14</li> <li>Unimplemented: Read as '0'</li> <li>bit 13</li> <li>QEISIDL: QEI Stop in Idle Mode bit</li> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> <li>0 = Continues module operation in Idle mode</li> <li>0 = Continues module operation counter Initialization Mode Select bits<sup>(1)</sup></li> <li>111 = Reserved</li> <li>110 = Modulo Count mode for position counter</li> <li>101 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event initializes the position counter with contents of QEI1IC register</li> <li>010 = Next index input event resets the position counter with contents of QEI1IC register</li> <li>011 = Every index input event resets the position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index Match Value for Phase B bit<sup>(2)</sup></li> <li>1 = Phase B match occurs when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>bit 8</li> <li>IMV0: Index Match Value for Phase A bit<sup>(2)</sup></li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> </ul> | -n = value a | PUR                                                                                              | I = Bit is set                                                                                                 |                                                                                              | 0 = Bit is cie                                                                | ared                                                       | x = Bit is unkr                   | lown                |  |  |

| bit 13       QEISDL: QEI Stop in Idle Mode bit         1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Modulo Count mode for position counter         100 = Modulo Count mode for position counter       101 = Resets the position counter when the position counter equals QEI1GEC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter with contents of QEI1IC register         011 = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter with contents of QEI1IC register         011 = Every index input event resets the position counter       001 = Every index input event for position counter         001 = Index input event does not affect position counter       000 = Index input event does not affect position counter         001 = Phase B match occurs when QEB = 1       0 = Phase B match occurs when QEB = 0         0it 8       IMV0: Index Match Value for Phase A bit <sup>(2)</sup> 1 = Phase A match occurs when QEA = 1       0 = Phase A match occurs when QEA = 0         0it 7       Unimplemented: Read as '0'                                                                                                                                                                                   | bit 15       | 1 = Module co                                                                                    | ounters are ena                                                                                                | abled                                                                                        |                                                                               |                                                            |                                   |                     |  |  |

| <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> <li>bit 12-10</li> <li>PIMOD&lt;2:0&gt;: Position Counter Initialization Mode Select bits<sup>(1)</sup></li> <li>111 = Reserved</li> <li>10 = Modulo Count mode for position counter</li> <li>10 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event resets the position counter with contents of QEI1IC register</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event operation when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>bit 8</li> <li>IMV0: Index Match Value for Phase A bit<sup>(2)</sup></li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                  | bit 14       | Unimplemen                                                                                       | ted: Read as '                                                                                                 | 0'                                                                                           |                                                                               |                                                            |                                   |                     |  |  |

| <ul> <li>0 = Continues module operation in Idle mode</li> <li>bit 12-10</li> <li>PIMOD&lt;2:0&gt;: Position Counter Initialization Mode Select bits<sup>(1)</sup></li> <li>111 = Reserved</li> <li>10 = Modulo Count mode for position counter</li> <li>101 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event resets the position counter with contents of QEI1IC register</li> <li>001 = Every index input event resets the position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event QEB = 1</li> <li>0 = Phase B match occurs when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>bit 8</li> <li>IMV0: Index Match Value for Phase A bit<sup>(2)</sup></li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> </ul>                                                                                                                                                                                                                                                                                              | bit 13       | QEISIDL: QE                                                                                      | I Stop in Idle M                                                                                               | lode bit                                                                                     |                                                                               |                                                            |                                   |                     |  |  |

| <ul> <li>111 = Reserved</li> <li>10 = Modulo Count mode for position counter</li> <li>101 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>011 = First index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event initializes the position counter with contents of QEI1IC register</li> <li>011 = Every index input event resets the position counter with contents of QEI1IC register</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>011 = Phase B match occurs when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>0 = Phase A match occurs when QEA = 0</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |                                                                                                  |                                                                                                                |                                                                                              |                                                                               | dle mode                                                   |                                   |                     |  |  |