Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                |

|---------------------------|--------------------------------------------------------------------------------|

| Product Status            | Active                                                                         |

| Core Processor            | PIC                                                                            |

| Core Size                 | 16-Bit                                                                         |

| Speed                     | 70 MIPs                                                                        |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals               | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O             | 35                                                                             |

| Program Memory Size       | 128KB (43K x 24)                                                               |

| rogram Memory Type        | FLASH                                                                          |

| EPROM Size                | -                                                                              |

| RAM Size                  | 8K x 16                                                                        |

| oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Oata Converters           | A/D 9x10b/12b                                                                  |

| Oscillator Type           | Internal                                                                       |

| perating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Nounting Type             | Surface Mount                                                                  |

| Package / Case            | 48-UFQFN Exposed Pad                                                           |

| Supplier Device Package   | 48-UQFN (6x6)                                                                  |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128gp204-i-mv |

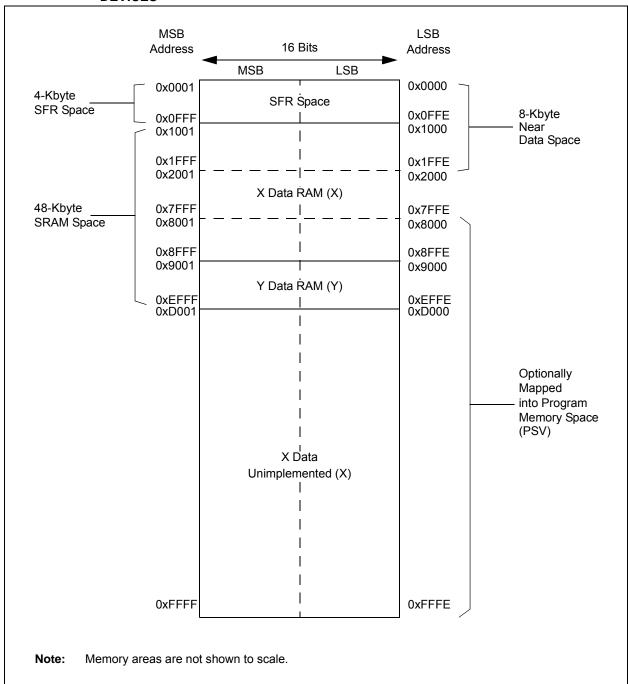

FIGURE 4-11: DATA MEMORY MAP FOR dsPIC33EP512MC20X/50X AND dsPIC33EP512GP50X DEVICES

#### TABLE 4-14: PWM GENERATOR 2 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12       | Bit 11                                           | Bit 10 | Bit 9  | Bit 8      | Bit 7     | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2     | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|---------|--------|---------|--------------|--------------------------------------------------|--------|--------|------------|-----------|--------|--------|--------|-------|-----------|-------|-------|---------------|

| PWMCON2   | 0C40  | FLTSTAT | CLSTAT | TRGSTAT | FLTIEN       | CLIEN                                            | TRGIEN | ITB    | MDCS       | DTC<      | :1:0>  | DTCP   | _      | MTBS  | CAM       | XPRES | IUE   | 0000          |

| IOCON2    | 0C42  | PENH    | PENL   | POLH    | POLL         | PMOD                                             | <1:0>  | OVRENH | OVRENL     | OVRDA     | T<1:0> | FLTDA  | T<1:0> | CLDA  | \T<1:0>   | SWAP  | OSYNC | C000          |

| FCLCON2   | 0C44  | _       |        | C       | LSRC<4:0     | > CLPOL CLMOD FLTSRC<4:0> FLTPOL FLTMOD<1:0>     |        |        |            |           |        | D<1:0> | 00F8   |       |           |       |       |               |

| PDC2      | 0C46  |         |        |         | PDC2<15:0>   |                                                  |        |        |            |           |        | 0000   |        |       |           |       |       |               |

| PHASE2    | 0C48  |         |        |         | PHASE2<15:0> |                                                  |        |        |            |           |        |        |        | 0000  |           |       |       |               |

| DTR2      | 0C4A  | _       | _      |         |              |                                                  |        |        |            | TR2<13:0> | •      |        |        |       |           |       |       | 0000          |

| ALTDTR2   | 0C4C  | _       | _      |         |              |                                                  |        |        | AL         | TDTR2<13: | 0>     |        |        |       |           |       |       | 0000          |

| TRIG2     | 0C52  |         |        |         |              |                                                  |        | TF     | RGCMP<15:0 | >         |        |        |        |       |           |       |       | 0000          |

| TRGCON2   | 0C54  |         | TRGDI  | /<3:0>  |              | _                                                | _      | _      | _          | _         | _      |        |        | TRO   | GSTRT<5:0 | )>    |       | 0000          |

| LEBCON2   | 0C5A  | PHR     | PHF    | PLR     | PLF          | FLTLEBEN CLLEBEN BCH BCL BPHH BPHL BPLH BPLL     |        |        |            |           |        |        | 0000   |       |           |       |       |               |

| LEBDLY2   | 0C5C  | _       | _      | _       | _            | LEB<11:0> 0                                      |        |        |            |           |        |        | 0000   |       |           |       |       |               |

| AUXCON2   | 0C5E  | _       | _      | _       | _            | BLANKSEL<3:0> — — CHOPSEL<3:0> CHOPHEN CHOPLEN 0 |        |        |            |           | 0000   |        |        |       |           |       |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-15: PWM GENERATOR 3 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13       | Bit 12     | Bit 11                                         | Bit 10                                     | Bit 9  | Bit 8      | Bit 7     | Bit 6  | Bit 5 | Bit 4   | Bit 3 | Bit 2     | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|---------|--------|--------------|------------|------------------------------------------------|--------------------------------------------|--------|------------|-----------|--------|-------|---------|-------|-----------|-------|-------|---------------|

| PWMCON3   | 0C60  | FLTSTAT | CLSTAT | TRGSTAT      | FLTIEN     | CLIEN                                          | TRGIEN                                     | ITB    | MDCS       | DTC<      | 1:0>   | DTCP  | _       | MTBS  | CAM       | XPRES | IUE   | 0000          |

| IOCON3    | 0C62  | PENH    | PENL   | POLH         | POLL       | PMOD                                           | <1:0>                                      | OVRENH | OVRENL     | OVRDA     | T<1:0> | FLTDA | \T<1:0> | CLD   | AT<1:0>   | SWAP  | OSYNC | C000          |

| FCLCON3   | 0C64  | _       |        | C            | CLSRC<4:0  | <b> &gt;</b>                                   | CLPOL CLMOD FLTSRC<4:0> FLTPOL FLTMOD<1:0> |        |            |           |        |       | D<1:0>  | 00F8  |           |       |       |               |

| PDC3      | 0C66  |         |        |              | PDC3<15:0> |                                                |                                            |        |            |           | 0000   |       |         |       |           |       |       |               |

| PHASE3    | 0C68  |         |        | PHASE3<15:0> |            |                                                |                                            |        |            |           |        |       | 0000    |       |           |       |       |               |

| DTR3      | 0C6A  | _       | _      |              |            |                                                |                                            |        |            | TR3<13:0  | >      |       |         |       |           |       |       | 0000          |

| ALTDTR3   | 0C6C  | _       | _      |              |            |                                                |                                            |        | AL         | TDTR3<13: | :0>    |       |         |       |           |       |       | 0000          |

| TRIG3     | 0C72  |         |        |              |            |                                                |                                            | T      | RGCMP<15:0 | )>        |        |       |         |       |           |       |       | 0000          |

| TRGCON3   | 0C74  |         | TRGDI  | V<3:0>       |            | _                                              | _                                          | _      | _          | _         | _      |       |         | TRO   | GSTRT<5:0 | )>    |       | 0000          |

| LEBCON3   | 0C7A  | PHR     | PHF    | PLR          | PLF        | FLTLEBEN                                       | CLLEBEN                                    | _      | _          | _         | _      | ВСН   | BCL     | врнн  | BPHL      | BPLH  | BPLL  | 0000          |

| LEBDLY3   | 0C7C  | _       | _      | _            | LEB<11:0>  |                                                |                                            |        |            |           |        |       | 0000    |       |           |       |       |               |

| AUXCON3   | 0C7E  | _       | _      | _            | _          | BLANKSEL<3:0> — — CHOPSEL<3:0> CHOPHEN CHOPLEN |                                            |        |            |           | 0000   |       |         |       |           |       |       |               |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| dsPIC33EPXXXGP | 250X, dsPIC33EPXX | XMC20X/50X AND | PIC24EPXXXG | P/MC20X |

|----------------|-------------------|----------------|-------------|---------|

| NOTES:         |                   |                |             |         |

|                |                   |                |             |         |

|                |                   |                |             |         |

|                |                   |                |             |         |

|                |                   |                |             |         |

|                |                   |                |             |         |

|                |                   |                |             |         |

|                |                   |                |             |         |

|                |                   |                |             |         |

|                |                   |                |             |         |

|                |                   |                |             |         |

|                |                   |                |             |         |

|                |                   |                |             |         |

|                |                   |                |             |         |

#### REGISTER 10-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 |

|--------|-----|-----|-----|-----|-----------------------|-----------------------|-----------------------|

| _      | _   | _   | _   | _   | PWM3MD <sup>(1)</sup> | PWM2MD <sup>(1)</sup> | PWM1MD <sup>(1)</sup> |

| bit 15 |     |     |     |     |                       |                       | bit 8                 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-11 **Unimplemented:** Read as '0'

bit 10 **PWM3MD:** PWM3 Module Disable bit<sup>(1)</sup>

1 = PWM3 module is disabled 0 = PWM3 module is enabled

bit 9 **PWM2MD:** PWM2 Module Disable bit<sup>(1)</sup>

1 = PWM2 module is disabled 0 = PWM2 module is enabled

bit 8 **PWM1MD:** PWM1 Module Disable bit<sup>(1)</sup>

1 = PWM1 module is disabled0 = PWM1 module is enabled

bit 7-0 **Unimplemented:** Read as '0'

Note 1: This bit is available on dsPIC33EPXXXMC50X/20X and PIC24EPXXXMC20X devices only.

TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES (CONTINUED)

| Peripheral Pin                 |                  |                | ] | Peripheral Pin                 | 1                | , , , , , , , , , , , , , , , , , , , |

|--------------------------------|------------------|----------------|---|--------------------------------|------------------|---------------------------------------|

| Select Input<br>Register Value | Input/<br>Output | Pin Assignment |   | Select Input<br>Register Value | Input/<br>Output | Pin Assignme                          |

| 010 1000                       | I/O              | RP40           |   | 101 0101                       | _                | _                                     |

| 010 1001                       | I/O              | RP41           |   | 101 0110                       | _                | _                                     |

| 010 1010                       | I/O              | RP42           |   | 101 0111                       | _                | _                                     |

| 010 1011                       | I/O              | RP43           |   | 101 1000                       | _                | _                                     |

| 010 1100                       | I                | RPI44          |   | 101 1001                       | _                | _                                     |

| 101 1010                       | _                | _              |   | 110 1101                       | _                | _                                     |

| 101 1011                       | _                | _              |   | 110 1110                       | _                |                                       |

| 101 1100                       | _                | _              |   | 110 1111                       | _                | _                                     |

| 101 1101                       | _                | _              |   | 111 0000                       | _                | _                                     |

| 101 1110                       | I                | RPI94          |   | 111 0001                       | _                |                                       |

| 101 1111                       | I                | RPI95          |   | 111 0010                       | _                | _                                     |

| 110 0000                       | I                | RPI96          |   | 111 0011                       | _                | _                                     |

| 110 0001                       | I/O              | RP97           |   | 111 0100                       | _                | _                                     |

| 110 0010                       | _                | _              |   | 111 0101                       | _                | _                                     |

| 110 0011                       | _                | _              |   | 111 0110                       | I/O              | RP118                                 |

| 110 0100                       | _                | _              |   | 111 0111                       | I                | RPI119                                |

| 110 0101                       | _                | _              |   | 111 1000                       | I/O              | RP120                                 |

| 110 0110                       | _                | _              |   | 111 1001                       | I                | RPI121                                |

| 110 0111                       | _                | _              |   | 111 1010                       | _                | _                                     |

| 110 1000                       | _                | _              |   | 111 1011                       | _                | _                                     |

| 110 1001                       | _                | _              |   | 111 1100                       | _                | _                                     |

| 110 1010                       | _                | _              |   | 111 1101                       | _                | _                                     |

| 110 1011                       | _                | _              |   | 111 1110                       |                  | _                                     |

| 110 1100                       | _                | <del>-</del>   |   | 111 1111                       |                  | _                                     |

**Legend:** Shaded rows indicate PPS Input register values that are unimplemented.

Note 1: See Section 11.4.4.1 "Virtual Connections" for more information on selecting this pin assignment.

**2:** These inputs are available on dsPIC33EPXXXGP/MC50X devices only.

## REGISTER 11-8: RPINR14: PERIPHERAL PIN SELECT INPUT REGISTER 14 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|------------|-------|-------|-------|

| _      |       |       |       | QEB1R<6:0> | >     |       |       |

| bit 15 |       |       |       |            |       |       | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|------------|-------|-------|-------|

| _     |       |       |       | QEA1R<6:0> | >     |       |       |

| bit 7 |       |       |       |            |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-8 QEB1R<6:0>: Assign B (QEB) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

•

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

bit 7 **Unimplemented:** Read as '0'

bit 6-0 **QEA1R<6:0>:** Assign A (QEA) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

.

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

## REGISTER 11-15: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------------|-------|-------|-------|

| _      |       |       |       | SYNCI1R<6:0 | )>    |       |       |

| bit 15 |       |       |       |             |       |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-8 SYNCI1R<6:0>: Assign PWM Synchronization Input 1 to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

.

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

bit 7-0 **Unimplemented:** Read as '0'

#### 14.2 Input Capture Registers

#### REGISTER 14-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0   |

|--------|-----|--------|---------|---------|---------|-----|-------|

| _      | _   | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _   | _     |

| bit 15 | _   |        |         |         | _       |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/HC/HS-0 | R/HC/HS-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----------|-----------|-------|-------|-------|

| _     | ICI1  | ICI0  | ICOV      | ICBNE     | ICM2  | ICM1  | ICM0  |

| bit 7 |       |       |           |           |       |       | bit 0 |

| Legend: HC = Hardware Clearable bit HS = Hardware Settable bit |                  |                            | į –                |

|----------------------------------------------------------------|------------------|----------------------------|--------------------|

| R = Readable bit                                               | W = Writable bit | U = Unimplemented bit, rea | nd as '0'          |

| -n = Value at POR                                              | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13 ICSIDL: Input Capture Stop in Idle Control bit

1 = Input capture will Halt in CPU Idle mode

0 = Input capture will continue to operate in CPU Idle mode

bit 12-10 ICTSEL<2:0>: Input Capture Timer Select bits

111 = Peripheral clock (FP) is the clock source of the ICx

110 = Reserved 101 = Reserved

100 = T1CLK is the clock source of the ICx (only the synchronous clock is supported)

011 = T5CLK is the clock source of the ICx 010 = T4CLK is the clock source of the ICx

001 = T2CLK is the clock source of the ICx

000 = T3CLK is the clock source of the ICx

bit 9-7 Unimplemented: Read as '0'

bit 6-5 ICI<1:0>: Number of Captures per Interrupt Select bits (this field is not used if ICM<2:0> = 001 or 111)

11 = Interrupt on every fourth capture event

10 = Interrupt on every third capture event

01 = Interrupt on every second capture event

00 = Interrupt on every capture event

bit 4 ICOV: Input Capture Overflow Status Flag bit (read-only)

1 = Input capture buffer overflow occurred0 = No input capture buffer overflow occurred

bit 3 **ICBNE:** Input Capture Buffer Not Empty Status bit (read-only)

1 = Input capture buffer is not empty, at least one more capture value can be read

0 = Input capture buffer is empty

bit 2-0 ICM<2:0>: Input Capture Mode Select bits

111 = Input capture functions as interrupt pin only in CPU Sleep and Idle modes (rising edge detect only, all other control bits are not applicable)

110 = Unused (module is disabled)

101 = Capture mode, every 16th rising edge (Prescaler Capture mode)

100 = Capture mode, every 4th rising edge (Prescaler Capture mode)

011 = Capture mode, every rising edge (Simple Capture mode)

010 = Capture mode, every falling edge (Simple Capture mode)

001 = Capture mode, every edge rising and falling (Edge Detect mode (ICI<1:0>) is not used in this mode)

000 = Input capture module is turned off

#### 17.1 QEI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note:

In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en555464

#### 17.1.1 KEY RESOURCES

- "Quadrature Encoder Interface" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

#### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

bit 6 STREN: SCLx Clock Stretch Enable bit (when operating as I<sup>2</sup>C slave)

Used in conjunction with the SCLREL bit.

- 1 = Enables software or receives clock stretching

- 0 = Disables software or receives clock stretching

- bit 5 ACKDT: Acknowledge Data bit (when operating as I<sup>2</sup>C master, applicable during master receive)

Value that is transmitted when the software initiates an Acknowledge sequence.

- 1 = Sends NACK during Acknowledge

- 0 = Sends ACK during Acknowledge

- bit 4 ACKEN: Acknowledge Sequence Enable bit

(when operating as I<sup>2</sup>C master, applicable during master receive)

- 1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits ACKDT data bit. Hardware is clear at the end of the master Acknowledge sequence.

- 0 = Acknowledge sequence is not in progress

- bit 3 **RCEN:** Receive Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Enables Receive mode for I<sup>2</sup>C. Hardware is clear at the end of the eighth bit of the master receive data byte.

- 0 = Receive sequence is not in progress

- bit 2 **PEN:** Stop Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiates Stop condition on SDAx and SCLx pins. Hardware is clear at the end of the master Stop sequence.

- 0 = Stop condition is not in progress

- bit 1 **RSEN:** Repeated Start Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware is clear at the end of the master Repeated Start sequence.

- 0 = Repeated Start condition is not in progress

- bit 0 **SEN:** Start Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiates Start condition on SDAx and SCLx pins. Hardware is clear at the end of the master Start sequence.

- 0 = Start condition is not in progress

- Note 1: When performing master operations, ensure that the IPMIEN bit is set to '0'.

## REGISTER 21-20: CxRXMnSID: ECANx ACCEPTANCE FILTER MASK n STANDARD IDENTIFIER REGISTER (n = 0-2)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| SID10  | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-x | R/W-x | R/W-x | U-0 | R/W-x | U-0 | R/W-x | R/W-x |

|-------|-------|-------|-----|-------|-----|-------|-------|

| SID2  | SID1  | SID0  | _   | MIDE  | _   | EID17 | EID16 |

| bit 7 |       |       |     |       |     |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-5 SID<10:0>: Standard Identifier bits

1 = Includes bit, SIDx, in filter comparison0 = SIDx bit is a don't care in filter comparison

bit 4 Unimplemented: Read as '0'

bit 3 MIDE: Identifier Receive Mode bit

1 = Matches only message types (standard or extended address) that correspond to EXIDE bit in the filter

0 = Matches either standard or extended address message if filters match (i.e., if (Filter SID) = (Message

SID) or if (Filter SID/EID) = (Message SID/EID))

bit 2 Unimplemented: Read as '0'

bit 1-0 EID<17:16>: Extended Identifier bits

1 = Includes bit, EIDx, in filter comparison

0 = EIDx bit is a don't care in filter comparison

## REGISTER 21-21: CxRXMnEID: ECANx ACCEPTANCE FILTER MASK n EXTENDED IDENTIFIER REGISTER (n = 0-2)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| EID15  | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 EID<15:0>: Extended Identifier bits

1 = Includes bit, EIDx, in filter comparison

0 = EIDx bit is a don't care in filter comparison

#### REGISTER 23-2: AD1CON2: ADC1 CONTROL REGISTER 2

| R/W-0  | R/W-0 | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-----|-----|-------|-------|-------|

| VCFG2  | VCFG1 | VCFG0 | _   | _   | CSCNA | CHPS1 | CHPS0 |

| bit 15 |       |       |     |     |       |       | bit 8 |

| R-0   | R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| BUFS  | SMPI4 | SMPI3 | SMPI2 | SMPI1 | SMPI0 | BUFM  | ALTS  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-13 VCFG<2:0>: Converter Voltage Reference Configuration bits

| Value | VREFH          | VREFL          |

|-------|----------------|----------------|

| 000   | Avdd           | Avss           |

| 001   | External VREF+ | Avss           |

| 010   | Avdd           | External VREF- |

| 011   | External VREF+ | External VREF- |

| 1xx   | Avdd           | Avss           |

bit 12-11 **Unimplemented:** Read as '0'

bit 10 CSCNA: Input Scan Select bit

1 = Scans inputs for CH0+ during Sample MUXA

0 = Does not scan inputs

bit 9-8 CHPS<1:0>: Channel Select bits

In 12-bit mode (AD21B = 1), the CHPS<1:0> bits are Unimplemented and are Read as '0':

1x = Converts CH0, CH1, CH2 and CH3

01 = Converts CH0 and CH1

00 = Converts CH0

bit 7 **BUFS:** Buffer Fill Status bit (only valid when BUFM = 1)

- 1 = ADC is currently filling the second half of the buffer; the user application should access data in the first half of the buffer

- 0 = ADC is currently filling the first half of the buffer; the user application should access data in the second half of the buffer

#### bit 6-2 **SMPI<4:0>:** Increment Rate bits

#### When ADDMAEN = 0:

x1111 = Generates interrupt after completion of every 16th sample/conversion operation x1110 = Generates interrupt after completion of every 15th sample/conversion operation

•

•

x0001 = Generates interrupt after completion of every 2nd sample/conversion operation

x0000 = Generates interrupt after completion of every sample/conversion operation

#### When ADDMAEN = 1:

11111 = Increments the DMA address after completion of every 32nd sample/conversion operation 11110 = Increments the DMA address after completion of every 31st sample/conversion operation

•

•

00001 = Increments the DMA address after completion of every 2nd sample/conversion operation

00000 = Increments the DMA address after completion of every sample/conversion operation

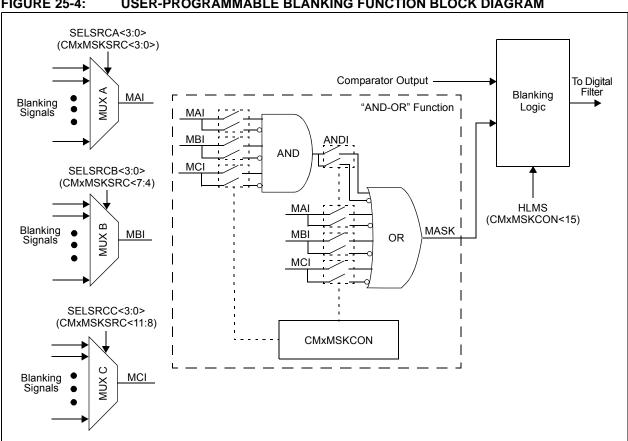

**FIGURE 25-4: USER-PROGRAMMABLE BLANKING FUNCTION BLOCK DIAGRAM**

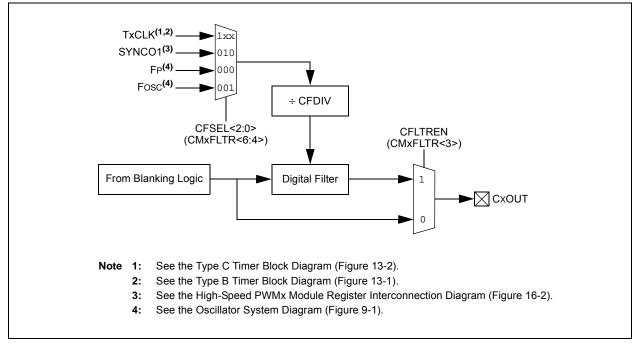

#### **FIGURE 25-5:** DIGITAL FILTER INTERCONNECT BLOCK DIAGRAM

#### 27.2 User ID Words

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices contain four User ID Words, located at addresses, 0x800FF8 through 0x800FFE. The User ID Words can be used for storing product information such as serial numbers, system manufacturing dates, manufacturing lot numbers and other application-specific information.

The User ID Words register map is shown in Table 27-3.

TABLE 27-3: USER ID WORDS REGISTER MAP

| File Name | Address  | Bits 23-16 | Bits 15-0 |

|-----------|----------|------------|-----------|

| FUID0     | 0x800FF8 | _          | UID0      |

| FUID1     | 0x800FFA | _          | UID1      |

| FUID2     | 0x800FFC | _          | UID2      |

| FUID3     | 0x800FFE | _          | UID3      |

**Legend:** — = unimplemented, read as '1'.

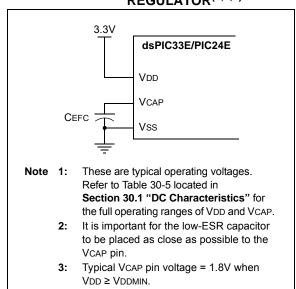

#### 27.3 On-Chip Voltage Regulator

All of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices power their core digital logic at a nominal 1.8V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family incorporate an onchip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. A low-ESR (less than 1 Ohm) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 30-5 located in **Section 30.0 "Electrical Characteristics"**.

**Note:** It is important for the low-ESR capacitor to be placed as close as possible to the VCAP pin.

FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

### 27.4 Brown-out Reset (BOR)

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated supply voltage, VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT Time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM is applied. The total delay in this case is TFSCM. Refer to Parameter SY35 in Table 30-22 of **Section 30.0 "Electrical Characteristics"** for specific TFSCM values.

The BOR status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

# 29.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM™ and dsPICDEM™ demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELoq® security ICs, CAN, IrDA®, PowerSmart battery management, SEEVAL® evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

#### 29.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

TABLE 30-37: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING REQUIREMENTS

| AC CHA | ARACTERIS             | псѕ                                        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)   Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                     |                          |       |                             |  |

|--------|-----------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------|-------|-----------------------------|--|

| Param. | Symbol                | Characteristic <sup>(1)</sup>              | Min.                                                                                                                                                                                                                                               | Typ. <sup>(2)</sup> | Max.                     | Units | Conditions                  |  |

| SP70   | FscP                  | Maximum SCK2 Input<br>Frequency            | _                                                                                                                                                                                                                                                  | _                   | Lesser<br>of FP<br>or 15 | MHz   | (Note 3)                    |  |

| SP72   | TscF                  | SCK2 Input Fall Time                       | _                                                                                                                                                                                                                                                  | _                   | _                        | ns    | See Parameter DO32 (Note 4) |  |

| SP73   | TscR                  | SCK2 Input Rise Time                       | _                                                                                                                                                                                                                                                  | _                   | _                        | ns    | See Parameter DO31 (Note 4) |  |

| SP30   | TdoF                  | SDO2 Data Output Fall Time                 | _                                                                                                                                                                                                                                                  | _                   | _                        | ns    | See Parameter DO32 (Note 4) |  |

| SP31   | TdoR                  | SDO2 Data Output Rise Time                 | _                                                                                                                                                                                                                                                  | _                   | _                        | ns    | See Parameter DO31 (Note 4) |  |

| SP35   | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after SCK2 Edge     | _                                                                                                                                                                                                                                                  | 6                   | 20                       | ns    |                             |  |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to First SCK2 Edge  | 30                                                                                                                                                                                                                                                 | _                   | _                        | ns    |                             |  |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge | 30                                                                                                                                                                                                                                                 | _                   | _                        | ns    |                             |  |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge  | 30                                                                                                                                                                                                                                                 | _                   | _                        | ns    |                             |  |

| SP50   | TssL2scH,<br>TssL2scL | SS2 ↓ to SCK2 ↑ or SCK2 ↓ Input            | 120                                                                                                                                                                                                                                                | _                   | _                        | ns    |                             |  |

| SP51   | TssH2doZ              | SS2 ↑ to SDO2 Output<br>High-Impedance     | 10                                                                                                                                                                                                                                                 | _                   | 50                       | ns    | (Note 4)                    |  |

| SP52   | TscH2ssH<br>TscL2ssH  | SS2 ↑ after SCK2 Edge                      | 1.5 Tcy + 40                                                                                                                                                                                                                                       | _                   | _                        | ns    | (Note 4)                    |  |

| SP60   | TssL2doV              | SDO2 Data Output Valid after<br>SS2 Edge   | _                                                                                                                                                                                                                                                  | _                   | 50                       | ns    |                             |  |

- Note 1: These parameters are characterized, but are not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK2 is 66.7 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

- 4: Assumes 50 pF load on all SPI2 pins.

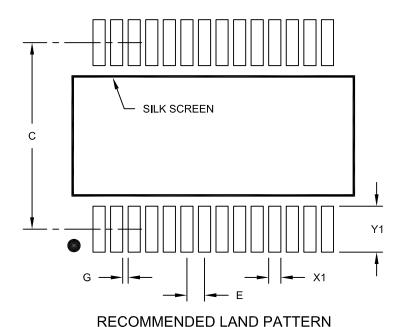

### 28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**ote:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Units **MILLIMETERS Dimension Limits** MIN MOM MAX Contact Pitch Ε 0.65 BSC Contact Pad Spacing С 7.20 Contact Pad Width (X28) X1 0.45 Contact Pad Length (X28) 1.75 Υ1

G

0.20

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

Distance Between Pads

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

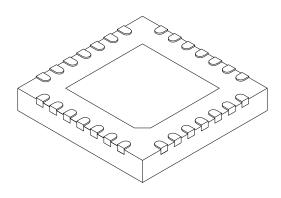

## 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units            | MILLIMETERS |          |      |  |

|-------------------------|------------------|-------------|----------|------|--|

| Dimension               | Dimension Limits |             |          | MAX  |  |

| Number of Pins          | N                |             | 28       |      |  |

| Pitch                   | е                |             | 0.65 BSC |      |  |

| Overall Height          | Α                | 0.80        | 0.90     | 1.00 |  |

| Standoff                | A1               | 0.00        | 0.02     | 0.05 |  |

| Terminal Thickness      | A3               | 0.20 REF    |          |      |  |

| Overall Width           | Е                |             | 6.00 BSC |      |  |

| Exposed Pad Width       | E2               | 3.65        | 3.70     | 4.70 |  |

| Overall Length          | D                |             | 6.00 BSC |      |  |

| Exposed Pad Length      | D2               | 3.65        | 3.70     | 4.70 |  |

| Terminal Width          | р                | 0.23        | 0.30     | 0.35 |  |

| Terminal Length         | Ĺ                | 0.30        | 0.40     | 0.50 |  |

| Terminal-to-Exposed Pad | K                | 0.20        | -        | -    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-124C Sheet 2 of 2

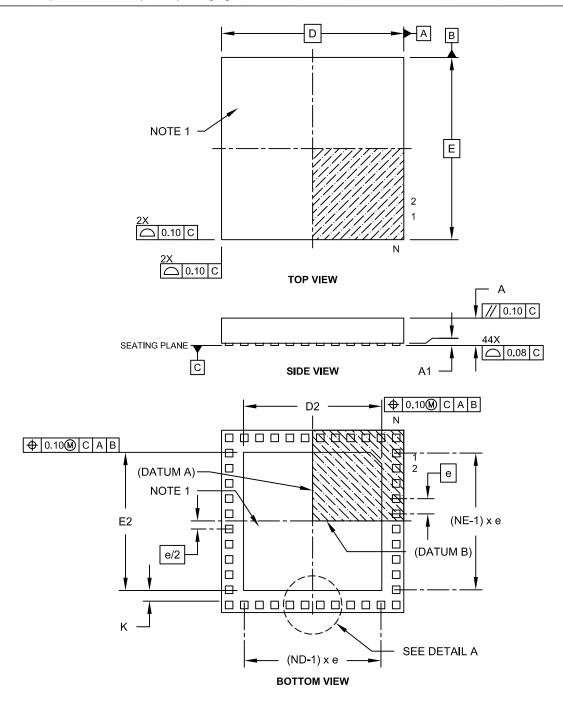

## 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-157C Sheet 1 of 2

| ECAN Module                                  |         | Instruction Set                             |     |

|----------------------------------------------|---------|---------------------------------------------|-----|

| Control Registers                            | 290     | Overview                                    | 390 |

| Modes of Operation                           | 289     | Summary                                     |     |

| Overview                                     | 287     | Symbols Used in Opcode Descriptions         | 388 |

| Resources                                    | 289     | Inter-Integrated Circuit (I <sup>2</sup> C) |     |

| Electrical Characteristics                   | 401     | Control Registers                           | 276 |

| AC4                                          |         | Resources                                   | 275 |

| Enhanced CAN (ECAN) Module                   | 287     | Internal RC Oscillator                      |     |

| Equations                                    |         | Use with WDT                                | 385 |

| Device Operating Frequency                   | 154     | Internet Address                            | 524 |

| FPLLO Calculation                            | 154     | Interrupt Controller                        |     |

| Fvco Calculation                             | 154     | Control and Status Registers                | 131 |

| Errata                                       | 23      | INTCON1                                     | 131 |

| -                                            |         | INTCON2                                     | 131 |

| F                                            |         | INTCON3                                     | 131 |

| Filter Capacitor (CEFC) Specifications       | 403     | INTCON4                                     | 131 |

| Flash Program Memory                         | 119     | INTTREG                                     | 131 |

| Control Registers                            | 120     | Interrupt Vector Details                    | 129 |

| Programming Operations                       | 120     | Interrupt Vector Table (IVT)                |     |

| Resources                                    | 120     | Reset Sequence                              |     |

| RTSP Operation                               | 120     | Resources                                   |     |

| Table Instructions                           | 119     |                                             |     |

| Flexible Configuration                       | 379     | J                                           |     |

| •                                            |         | JTAG Boundary Scan Interface                | 379 |

| G                                            |         | JTAG Interface                              | 386 |

| Guidelines for Getting Started               |         | M                                           |     |

| Application Examples                         |         | M                                           |     |

| Basic Connection Requirements                |         | Memory Maps                                 |     |

| CPU Logic Filter Capacitor Connection (VCAP) | 30      | Extended Data Space                         |     |

| Decoupling Capacitors                        |         | Memory Organization                         | 45  |

| External Oscillator Pins                     | 31      | Resources                                   |     |

| ICSP Pins                                    | 31      | Microchip Internet Web Site                 | 524 |

| Master Clear (MCLR) Pin                      |         | Modulo Addressing                           |     |

| Oscillator Value Conditions on Start-up      | 32      | Applicability                               | 115 |

| Unused I/Os                                  | 32      | Operation Example                           | 114 |

| н                                            |         | Start and End Address                       | 114 |

|                                              |         | W Address Register Selection                |     |

| High-Speed PWM                               |         | MPLAB Assembler, Linker, Librarian          | 398 |

| Control Registers                            |         | MPLAB ICD 3 In-Circuit Debugger             |     |

| Faults                                       |         | MPLAB PM3 Device Programmer                 | 399 |

| Resources                                    |         | MPLAB REAL ICE In-Circuit Emulator System   | 399 |

| High-Temperature Electrical Characteristics  |         | MPLAB X Integrated Development              |     |

| Absolute Maximum Ratings                     | 467     | Environment Software                        |     |

| I                                            |         | MPLAB X SIM Software Simulator              | 399 |

|                                              |         | MPLIB Object Librarian                      | 398 |

| I/O Ports                                    |         | MPLINK Object Linker                        | 398 |

| Helpful Tips                                 |         | 0                                           |     |

| Parallel I/O (PIO)                           |         | 0                                           |     |

| Resources                                    |         | Op Amp                                      |     |

| Write/Read Timing                            |         | Application Considerations                  | 358 |

| In-Circuit Debugger                          |         | Configuration A                             | 358 |

| In-Circuit Emulation                         |         | Configuration B                             | 359 |

| In-Circuit Serial Programming (ICSP)3        | 79, 386 | Op Amp/Comparator                           | 355 |

| Input Capture                                |         | Control Registers                           | 360 |

| Control Registers                            |         | Resources                                   | 359 |

| Resources                                    |         | Open-Drain Configuration                    | 174 |

| Input Change Notification (ICN)              |         | Oscillator                                  |     |

| Instruction Addressing Modes                 |         | Control Registers                           | 156 |

| File Register Instructions                   |         | Resources                                   | 155 |

| Fundamental Modes Supported                  |         | Output Compare                              | 219 |

| MAC Instructions                             | 113     | Control Registers                           |     |

| MCU Instructions                             |         | Resources                                   | 220 |

| Move and Accumulator Instructions            |         |                                             |     |

| Other Instructions                           | 113     |                                             |     |