Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128gp204-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

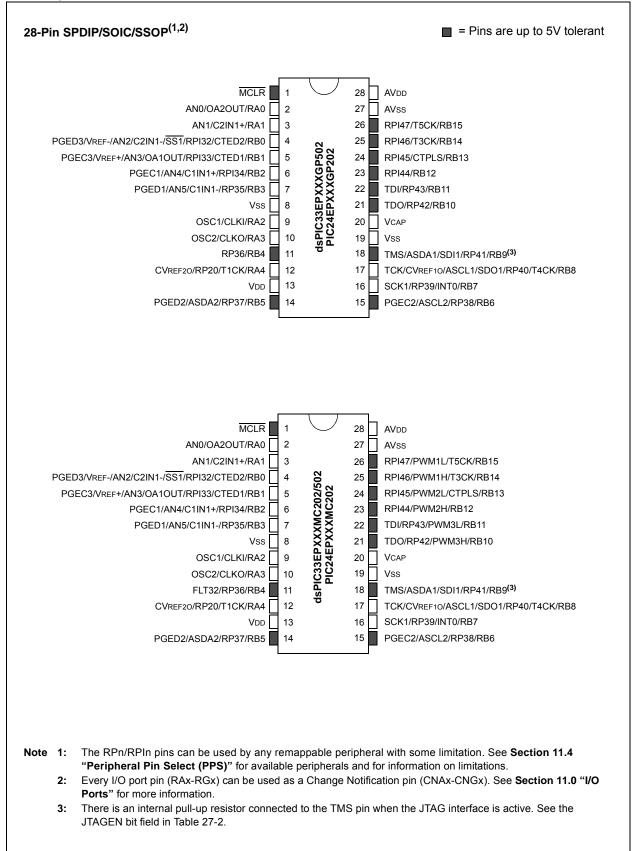

### **Pin Diagrams**

### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz <  $F_{IN}$  < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

## 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

### 2.9 Application Examples

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- · Automotive HVAC, cooling fans, fuel pumps

- Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- Speech (playback, hands-free kits, answering machines, VoIP)

- Consumer audio

- Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- Data storage device management

- · Smart cards and smart card readers

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

### FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

### TABLE 4-41: PMD REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr.       | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3    | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|----------|--------|--------|-------|---------------|

| PMD1         | 0760        | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD   | _      | _      | AD1MD | 0000          |

| PMD2         | 0762        | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | _     | _     | _      | OC4MD    | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764        | _      | _      | —      | —      | _      | CMPMD  | _      | _      | CRCMD  | _     | —     | _      | —        | —      | I2C2MD | _     | 0000          |

| PMD4         | 0766        | _      |        | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD   | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A        | _      |        | _      | _      | _      | PWM3MD | PWM2MD | PWM1MD | _      | _     | _     | _      | _        | _      | _      | _     | 0000          |

|              |             |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |          |        |        |       |               |

|              | 0760        |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD    |        |        |       | 0000          |

| PIVID7       | PMD7 076C — | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | 1D PIGMD | _      | _      | _     | 0000          |

|              |             |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |          |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

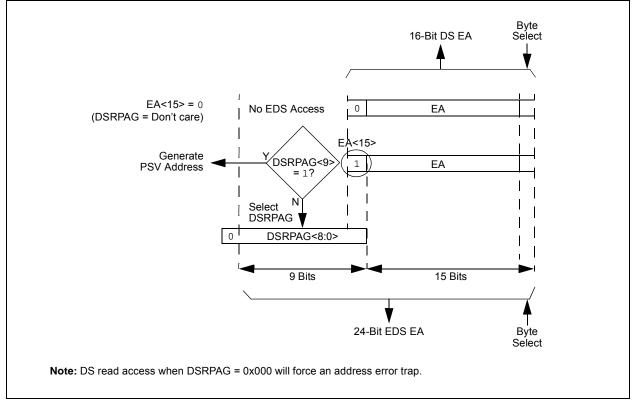

### 4.4.1 PAGED MEMORY SCHEME

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre-modified and post-modified Effective Addresses (EA). The upper half of the base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Read Page register (DSRPAG) or the 9-bit Write Page register (DSWPAG), to form an Extended Data Space (EDS) address or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

Construction of the EDS address is shown in Example 4-1. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when base address bit, EA<15> = 1, DSWPAG<8:0> are concatenated onto EA<14:0> to form the 24-bit EDS write address.

# 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions. which apply to dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

### 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

### 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/S-0                | U-0                                                                                 | U-0              | U-0                   | U-0              | U-0              | U-0             | U-0     |  |  |  |  |

|----------------------|-------------------------------------------------------------------------------------|------------------|-----------------------|------------------|------------------|-----------------|---------|--|--|--|--|

| FORCE <sup>(1)</sup> |                                                                                     | _                | _                     | —                |                  | _               |         |  |  |  |  |

| bit 15               |                                                                                     |                  |                       |                  |                  |                 | bit 8   |  |  |  |  |

|                      |                                                                                     |                  |                       |                  |                  |                 |         |  |  |  |  |

| R/W-0                | R/W-0                                                                               | R/W-0            | R/W-0                 | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |

| IRQSEL7              | IRQSEL6                                                                             | IRQSEL5          | IRQSEL4               | IRQSEL3          | IRQSEL2          | IRQSEL1         | IRQSEL0 |  |  |  |  |

| bit 7                |                                                                                     |                  |                       |                  |                  |                 | bit     |  |  |  |  |

| Legend:              |                                                                                     | S = Settable b   | oit                   |                  |                  |                 |         |  |  |  |  |

| R = Readable         | bit                                                                                 | W = Writable     | bit                   | U = Unimpler     | mented bit, read | d as '0'        |         |  |  |  |  |

| -n = Value at F      | POR                                                                                 | '1' = Bit is set |                       | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |  |

|                      |                                                                                     |                  |                       |                  |                  |                 |         |  |  |  |  |

| bit 15               | FORCE: Force                                                                        | e DMA Transfe    | er bit <sup>(1)</sup> |                  |                  |                 |         |  |  |  |  |

|                      | 1 = Forces a single DMA transfer (Manual mode)                                      |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 0 = Automatic DMA transfer initiation by DMA request                                |                  |                       |                  |                  |                 |         |  |  |  |  |

| bit 14-8             | Unimplemen                                                                          | ted: Read as 'd  | )'                    |                  |                  |                 |         |  |  |  |  |

| bit 7-0              | IRQSEL<7:0>: DMA Peripheral IRQ Number Select bits                                  |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 01000110 = ECAN1 – TX Data Request <sup>(2)</sup>                                   |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      |                                                                                     | IC4 – Input Ca   |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00100101 = IC3 – Input Capture 3<br>00100010 = ECAN1 – RX Data Ready <sup>(2)</sup> |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      |                                                                                     | SPI2 Transfer I  | -                     |                  |                  |                 |         |  |  |  |  |

|                      |                                                                                     |                  |                       | itter            |                  |                 |         |  |  |  |  |

|                      | 00011111 = UART2TX – UART2 Transmitter<br>00011110 = UART2RX – UART2 Receiver       |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00011100 = TMR5 – Timer5                                                            |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00011011 = TMR4 – Timer4                                                            |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00011010 = OC4 – Output Compare 4                                                   |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00011001 = OC3 – Output Compare 3                                                   |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00001101 = ADC1 – ADC1 Convert done                                                 |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00001100 = UART1TX – UART1 Transmitter                                              |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00001011 = UART1RX – UART1 Receiver                                                 |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00001010 = SPI1 – Transfer Done<br>00001000 = TMR3 – Timer3                         |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      |                                                                                     | TMR2 – Timer2    |                       |                  |                  |                 |         |  |  |  |  |

|                      |                                                                                     | OC2 – Output (   |                       |                  |                  |                 |         |  |  |  |  |

|                      |                                                                                     | IC2 – Input Ca   |                       |                  |                  |                 |         |  |  |  |  |

|                      | 0000010 =                                                                           | OC1 – Output (   | Compare 1             |                  |                  |                 |         |  |  |  |  |

|                      |                                                                                     | IC1 – Input Ca   |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00000000 =                                                                          | INT0 – Externa   | I Interrupt 0         |                  |                  |                 |         |  |  |  |  |

### REGISTER 8-2: DMAXREQ: DMA CHANNEL x IRQ SELECT REGISTER

- **Note 1:** The FORCE bit cannot be cleared by user software. The FORCE bit is cleared by hardware when the forced DMA transfer is complete or the channel is disabled (CHEN = 0).

- 2: This selection is available in dsPIC33EPXXXGP/MC50X devices only.

| Input Name <sup>(1)</sup>                   | Function Name | Register | Configuration Bits |

|---------------------------------------------|---------------|----------|--------------------|

| External Interrupt 1                        | INT1          | RPINR0   | INT1R<6:0>         |

| External Interrupt 2                        | INT2          | RPINR1   | INT2R<6:0>         |

| Timer2 External Clock                       | T2CK          | RPINR3   | T2CKR<6:0>         |

| Input Capture 1                             | IC1           | RPINR7   | IC1R<6:0>          |

| Input Capture 2                             | IC2           | RPINR7   | IC2R<6:0>          |

| Input Capture 3                             | IC3           | RPINR8   | IC3R<6:0>          |

| Input Capture 4                             | IC4           | RPINR8   | IC4R<6:0>          |

| Output Compare Fault A                      | OCFA          | RPINR11  | OCFAR<6:0>         |

| PWM Fault 1 <sup>(3)</sup>                  | FLT1          | RPINR12  | FLT1R<6:0>         |

| PWM Fault 2 <sup>(3)</sup>                  | FLT2          | RPINR12  | FLT2R<6:0>         |

| QEI1 Phase A <sup>(3)</sup>                 | QEA1          | RPINR14  | QEA1R<6:0>         |

| QEI1 Phase B <sup>(3)</sup>                 | QEB1          | RPINR14  | QEB1R<6:0>         |

| QEI1 Index <sup>(3)</sup>                   | INDX1         | RPINR15  | INDX1R<6:0>        |

| QEI1 Home <sup>(3)</sup>                    | HOME1         | RPINR15  | HOM1R<6:0>         |

| UART1 Receive                               | U1RX          | RPINR18  | U1RXR<6:0>         |

| UART2 Receive                               | U2RX          | RPINR19  | U2RXR<6:0>         |

| SPI2 Data Input                             | SDI2          | RPINR22  | SDI2R<6:0>         |

| SPI2 Clock Input                            | SCK2          | RPINR22  | SCK2R<6:0>         |

| SPI2 Slave Select                           | SS2           | RPINR23  | SS2R<6:0>          |

| CAN1 Receive <sup>(2)</sup>                 | C1RX          | RPINR26  | C1RXR<6:0>         |

| PWM Sync Input 1 <sup>(3)</sup>             | SYNCI1        | RPINR37  | SYNCI1R<6:0>       |

| PWM Dead-Time Compensation 1 <sup>(3)</sup> | DTCMP1        | RPINR38  | DTCMP1R<6:0>       |

| PWM Dead-Time Compensation 2 <sup>(3)</sup> | DTCMP2        | RPINR39  | DTCMP2R<6:0>       |

| PWM Dead-Time Compensation 3 <sup>(3)</sup> | DTCMP3        | RPINR39  | DTCMP3R<6:0>       |

### TABLE 11-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)

**Note 1:** Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

2: This input source is available on dsPIC33EPXXXGP/MC50X devices only.

3: This input source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

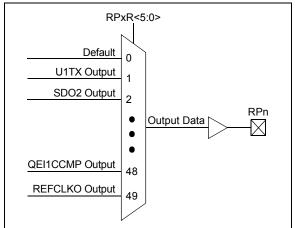

### 11.4.4.2 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 11-18 through Register 11-27). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-3 and Figure 11-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 11-3: MULTIPLEXING REMAPPABLE OUTPUT FOR RPn

### 11.4.4.3 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn pins is possible. This includes both many-toone and one-to-many mappings of peripheral inputs and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

### TABLE 11-3: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

| Function                | RPxR<5:0> | Output Name                                   |

|-------------------------|-----------|-----------------------------------------------|

| Default PORT            | 000000    | RPn tied to Default Pin                       |

| U1TX                    | 000001    | RPn tied to UART1 Transmit                    |

| U2TX                    | 000011    | RPn tied to UART2 Transmit                    |

| SDO2                    | 001000    | RPn tied to SPI2 Data Output                  |

| SCK2                    | 001001    | RPn tied to SPI2 Clock Output                 |

| SS2                     | 001010    | RPn tied to SPI2 Slave Select                 |

| C1TX <sup>(2)</sup>     | 001110    | RPn tied to CAN1 Transmit                     |

| OC1                     | 010000    | RPn tied to Output Compare 1 Output           |

| OC2                     | 010001    | RPn tied to Output Compare 2 Output           |

| OC3                     | 010010    | RPn tied to Output Compare 3 Output           |

| OC4                     | 010011    | RPn tied to Output Compare 4 Output           |

| C1OUT                   | 011000    | RPn tied to Comparator Output 1               |

| C2OUT                   | 011001    | RPn tied to Comparator Output 2               |

| C3OUT                   | 011010    | RPn tied to Comparator Output 3               |

| SYNCO1 <sup>(1)</sup>   | 101101    | RPn tied to PWM Primary Time Base Sync Output |

| QEI1CCMP <sup>(1)</sup> | 101111    | RPn tied to QEI 1 Counter Comparator Output   |

| REFCLKO                 | 110001    | RPn tied to Reference Clock Output            |

| C4OUT                   | 110010    | RPn tied to Comparator Output 4               |

Note 1: This function is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This function is available in dsPIC33EPXXXGP/MC50X devices only.

### REGISTER 11-9: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0                | R/W-0           | R/W-0           | R/W-0  |

|--------------|--------------|--------------------------------------------------------|---------------|----------------------|-----------------|-----------------|--------|

| _            |              |                                                        |               | HOME1R<6:0           | >               |                 |        |

| bit 15       |              |                                                        |               |                      |                 |                 | bit 8  |

|              |              | <b>D</b> # 4 4 0                                       | 54446         | 5444.0               | 5444.0          |                 | 5444.6 |

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0                | R/W-0           | R/W-0           | R/W-0  |

|              |              |                                                        |               | INDX1R<6:0>          | >               |                 |        |

| bit 7        |              |                                                        |               |                      |                 |                 | bit C  |

| Legend:      |              |                                                        |               |                      |                 |                 |        |

| R = Readab   | le bit       | W = Writable                                           | bit           | U = Unimplen         | nented bit, rea | ad as '0'       |        |

| -n = Value a | t POR        | '1' = Bit is set                                       |               | '0' = Bit is cleared |                 | x = Bit is unkr | nown   |

|              |              | nput tied to RPI                                       |               |                      |                 |                 |        |

|              |              | nput tied to CM<br>nput tied to Vss                    |               |                      |                 |                 |        |

| bit 7        |              | nted: Read as '                                        |               |                      |                 |                 |        |

| bit 6-0      | (see Table 1 | : Assign QEI1<br>1-2 for input pin<br>nput tied to RPI | selection nun | ,                    | responding RI   | Pn Pin bits     |        |

|              |              | nput tied to CM                                        |               |                      |                 |                 |        |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0      | U-0   | U-0   | U-0   | U-0       | U-0   | U-0   | U-0   |

|----------|-------|-------|-------|-----------|-------|-------|-------|

| —        | —     | —     | —     | —         | —     | —     | —     |

| bit 15   |       |       |       |           |       |       | bit 8 |

|          |       |       |       |           |       |       |       |

| U-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

| —        |       |       |       | SS2R<6:0> |       |       |       |

| bit 7    |       |       |       |           |       |       | bit 0 |

|          |       |       |       |           |       |       |       |

| l egend: |       |       |       |           |       |       |       |

### REGISTER 11-13: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0  | <b>SS2R&lt;6:0&gt;:</b> Assign SPI2 Slave Select (SS2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111001 = Input tied to RPI121                                                                                                            |

|          |                                                                                                                                           |

|          | •                                                                                                                                         |

|          | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss                                                                               |

### REGISTER 11-14: RPINR26: PERIPHERAL PIN SELECT INPUT REGISTER 26 (dsPIC33EPXXXGP/MC50X DEVICES ONLY)

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|------------|-------|-------|-------|

| _      | —     | —     | _     | _          | _     | —     | —     |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|        |       |       |       | C1RXR<6:0> | >     |       |       |

| bit 7  |       |       |       |            |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                              |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0  | <b>C1RXR&lt;6:0&gt;:</b> Assign CAN1 RX Input (CRX1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111001 = Input tied to RPI121                                                                                                          |

|          | •                                                                                                                                       |

|          |                                                                                                                                         |

|          | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss                                                                             |

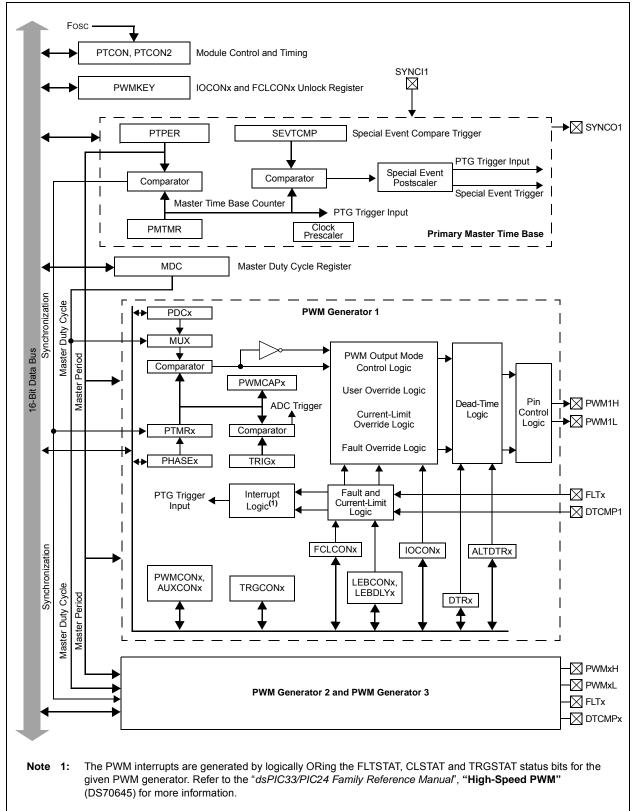

### FIGURE 16-2: HIGH-SPEED PWMx MODULE REGISTER INTERCONNECTION DIAGRAM

### REGISTER 17-1: QEI1CON: QEI1 CONTROL REGISTER (CONTINUED)

| bit 6-4 | <b>INTDIV&lt;2:0&gt;:</b> Timer Input Clock Prescale Select bits (interval timer, main timer (position counter), velocity counter and index counter internal clock divider select) <sup>(3)</sup>                                                                                                                            |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = 1:128 prescale value<br/>110 = 1:64 prescale value<br/>101 = 1:32 prescale value<br/>100 = 1:16 prescale value<br/>011 = 1:8 prescale value<br/>010 = 1:4 prescale value<br/>001 = 1:2 prescale value<br/>000 = 1:1 prescale value</pre>                                                                          |

| bit 3   | <b>CNTPOL:</b> Position and Index Counter/Timer Direction Select bit<br>1 = Counter direction is negative unless modified by external up/down signal                                                                                                                                                                         |

|         | <ul> <li>0 = Counter direction is positive unless modified by external up/down signal</li> </ul>                                                                                                                                                                                                                             |

| bit 2   | GATEN: External Count Gate Enable bit                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = External gate signal controls position counter operation</li> <li>0 = External gate signal does not affect position counter/timer operation</li> </ul>                                                                                                                                                          |

| bit 1-0 | CCM<1:0>: Counter Control Mode Selection bits                                                                                                                                                                                                                                                                                |

|         | <ul> <li>11 = Internal Timer mode with optional external count is selected</li> <li>10 = External clock count with optional external count is selected</li> <li>01 = External clock count with external up/down direction is selected</li> <li>00 = Quadrature Encoder Interface (x4 mode) Count mode is selected</li> </ul> |

| Note 1: | When CCM<1:0> = 10 or 11, all of the QEI counters operate as timers and the PIMOD<2:0> bits are ignored.                                                                                                                                                                                                                     |

- 2: When CCM<1:0> = 00, and QEA and QEB values match the Index Match Value (IMV), the POSCNTH and POSCNTL registers are reset. QEA/QEB signals used for the index match have swap and polarity values applied, as determined by the SWPAB and QEAPOL/QEBPOL bits.

- 3: The selected clock rate should be at least twice the expected maximum quadrature count rate.

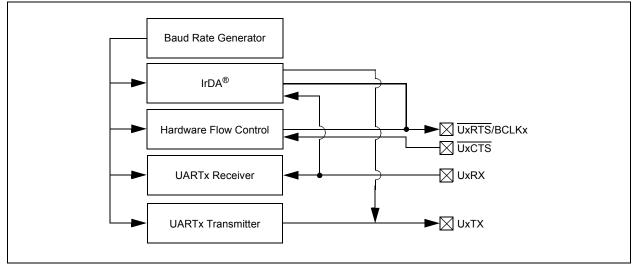

# 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "UART" (DS70582) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices contains two UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

Note: <u>Hardware</u> flow control using UxRTS and UxCTS is not available on all pin count devices. See the "**Pin Diagrams**" section for availability.

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UARTx Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 20-1. The UARTx module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

### FIGURE 20-1: UARTx SIMPLIFIED BLOCK DIAGRAM

© 2011-2013 Microchip Technology Inc.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0         | R/W-0                                                                      | R/W-0                                                                                                                      | R/W-0                                          | R/W-0            | R/W-0                | R/W-0    | R/W-0              |  |

|---------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------|----------------------|----------|--------------------|--|

|               | F15B                                                                       | P<3:0>                                                                                                                     |                                                | F14BP<3:0>       |                      |          |                    |  |

| bit 15        |                                                                            |                                                                                                                            |                                                |                  |                      |          | bit 8              |  |

| R/W-0         | R/W-0                                                                      | R/W-0                                                                                                                      | R/W-0                                          | R/W-0            | R/W-0                | R/W-0    | R/W-0              |  |

| 1011 0        |                                                                            | P<3:0>                                                                                                                     | 10110                                          |                  |                      | P<3:0>   | 1010 0             |  |

| bit 7         |                                                                            |                                                                                                                            |                                                |                  |                      |          | bit 0              |  |

| Legend:       |                                                                            |                                                                                                                            |                                                |                  |                      |          |                    |  |

| R = Readabl   | e bit                                                                      | W = Writable                                                                                                               | bit                                            | U = Unimplen     | nented bit, read     | d as '0' |                    |  |

| -n = Value at | t POR                                                                      | '1' = Bit is set                                                                                                           | '1' = Bit is set                               |                  | '0' = Bit is cleared |          | x = Bit is unknown |  |

| bit 15-12     | 1111 = Filte<br>1110 = Filte                                               | RX Buffer Ma<br>r hits received in<br>r hits received in<br>r hits received in<br>r hits received in<br>r hits received in | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | ıffer<br>4       |                      |          |                    |  |

| bit 11-8      | F14BP<3:0;                                                                 | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 4 bits (same val | ues as bits<15       | :12>)    |                    |  |

| bit 7-4       | F13BP<3:0>: RX Buffer Mask for Filter 13 bits (same values as bits<15:12>) |                                                                                                                            |                                                |                  |                      |          |                    |  |

| bit 3-0       | F12BP<3:0>: RX Buffer Mask for Filter 12 bits (same values as bits<15:12>) |                                                                                                                            |                                                |                  |                      |          |                    |  |

### REGISTER 21-15: CxBUFPNT4: ECANx FILTER 12-15 BUFFER POINTER REGISTER 4

### REGISTER 25-3: CM4CON: COMPARATOR 4 CONTROL REGISTER (CONTINUED)

- bit 5 Unimplemented: Read as '0'

- bit 4 **CREF:** Comparator Reference Select bit (VIN+ input)<sup>(1)</sup>

- 1 = VIN+ input connects to internal CVREFIN voltage

- 0 = VIN+ input connects to C4IN1+ pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Channel Select bits<sup>(1)</sup>

- 11 = VIN- input of comparator connects to OA3/AN6

- 10 = VIN- input of comparator connects to OA2/AN0

- 01 = VIN- input of comparator connects to OA1/AN3

- 00 = VIN- input of comparator connects to C4IN1-

- Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

# 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

### 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- · Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

| AC CHARACTERISTICS |           |                                                              |                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |               |       |                                                                               |

|--------------------|-----------|--------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|-------|-------------------------------------------------------------------------------|

| Param<br>No.       | Symbol    | Characteristic <sup>(1)</sup>                                |                     | Min.                                                                                                                                                                                                                                                                                  | Тур. | Max.          | Units | Conditions                                                                    |

| TB10               | TtxH      | TxCK High<br>Time                                            | Synchronous<br>mode | Greater of:<br>20 or<br>(Tcy + 20)/N                                                                                                                                                                                                                                                  | _    | _             | ns    | Must also meet<br>Parameter TB15,<br>N = prescale<br>value<br>(1, 8, 64, 256) |

| TB11               | TtxL      | TxCK Low<br>Time                                             | Synchronous<br>mode | Greater of:<br>20 or<br>(Tcy + 20)/N                                                                                                                                                                                                                                                  | _    |               | ns    | Must also meet<br>Parameter TB15,<br>N = prescale<br>value<br>(1, 8, 64, 256) |

| TB15               | TtxP      | TxCK<br>Input<br>Period                                      | Synchronous<br>mode | Greater of:<br>40 or<br>(2 Tcy + 40)/N                                                                                                                                                                                                                                                | —    | —             | ns    | N = prescale<br>value<br>(1, 8, 64, 256)                                      |

| TB20               | TCKEXTMRL | Delay from External TxCK<br>Clock Edge to Timer<br>Increment |                     | 0.75 Tcy + 40                                                                                                                                                                                                                                                                         | —    | 1.75 Tcy + 40 | ns    |                                                                               |

| TABLE 30-24: | TIMER2 AND TIM | IER4 (TYPE B TIMER | R) EXTERNAL CLOCK TIMING REQ | UIREMENTS |

|--------------|----------------|--------------------|------------------------------|-----------|

|--------------|----------------|--------------------|------------------------------|-----------|

Note 1: These parameters are characterized, but are not tested in manufacturing.

### TABLE 30-25: TIMER3 AND TIMER5 (TYPE C TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |                                    |                                                              |                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |               |       |                                          |

|--------------------|------------------------------------|--------------------------------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|-------|------------------------------------------|

| Param<br>No.       | Symbol Characteristic <sup>1</sup> |                                                              |                             | Min.                                                                                                                                                                                                                                                                              | Тур. | Max.          | Units | Conditions                               |

| TC10               | TtxH                               | TxCK High<br>Time                                            | Synchronous                 | Tcy + 20                                                                                                                                                                                                                                                                          |      |               | ns    | Must also meet<br>Parameter TC15         |

| TC11               | TtxL                               | TxCK Low<br>Time                                             | Synchronous                 | Тсү + 20                                                                                                                                                                                                                                                                          | _    | —             | ns    | Must also meet<br>Parameter TC15         |

| TC15               | TtxP                               | TxCK Input<br>Period                                         | Synchronous, with prescaler | 2 Tcy + 40                                                                                                                                                                                                                                                                        | —    | _             | ns    | N = prescale<br>value<br>(1, 8, 64, 256) |

| TC20               | TCKEXTMRL                          | Delay from External TxCK<br>Clock Edge to Timer<br>Increment |                             | 0.75 Tcy + 40                                                                                                                                                                                                                                                                     | _    | 1.75 Tcy + 40 | ns    |                                          |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

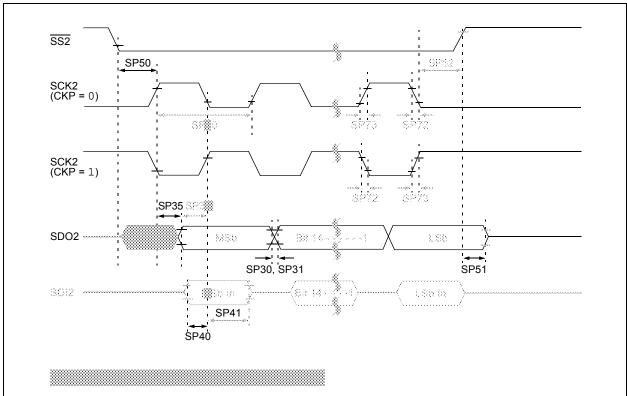

### FIGURE 30-20: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

NOTES:

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney Tel: 61-2-9868-6733

Fax: 61-2-9868-6755 China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Hangzhou Tel: 86-571-2819-3187

Fax: 86-571-2819-3189 China - Hong Kong SAR

Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

11/29/12