Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                             |

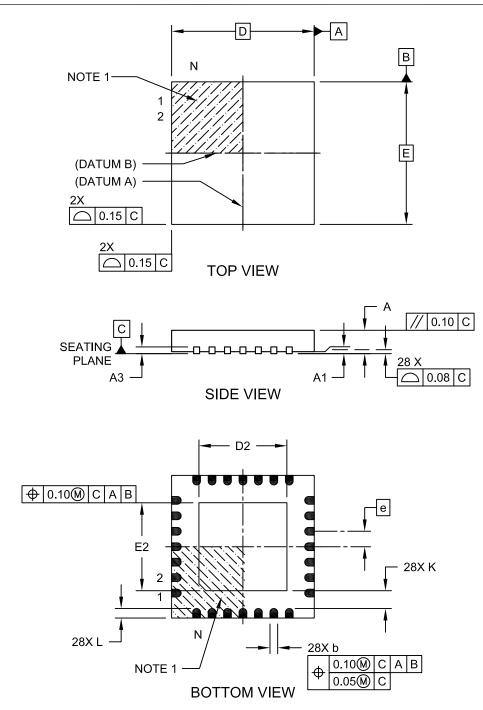

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128gp206-h-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.5 **Programmer's Model**

The programmer's model for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X is shown in Figure 3-2. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions. Table 3-1 lists a description of each register.

In addition to the registers contained in the programmer's model, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/

MC20X devices contain control registers for Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only), Bit-Reversed Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only) and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory mapped, as shown in Table 4-1.

| Register(s) Name                                      | Description                                               |

|-------------------------------------------------------|-----------------------------------------------------------|

| W0 through W15                                        | Working Register Array                                    |

| ACCA, ACCB                                            | 40-Bit DSP Accumulators                                   |

| PC                                                    | 23-Bit Program Counter                                    |

| SR                                                    | ALU and DSP Engine STATUS Register                        |

| SPLIM                                                 | Stack Pointer Limit Value Register                        |

| TBLPAG                                                | Table Memory Page Address Register                        |

| DSRPAG                                                | Extended Data Space (EDS) Read Page Register              |

| DSWPAG                                                | Extended Data Space (EDS) Write Page Register             |

| RCOUNT                                                | REPEAT Loop Count Register                                |

| DCOUNT <sup>(1)</sup>                                 | DO Loop Count Register                                    |

| DOSTARTH <sup>(1,2)</sup> , DOSTARTL <sup>(1,2)</sup> | DO Loop Start Address Register (High and Low)             |

| DOENDH <sup>(1)</sup> , DOENDL <sup>(1)</sup>         | DO Loop End Address Register (High and Low)               |

| CORCON                                                | Contains DSP Engine, DO Loop Control and Trap Status bits |

### TABLE 3-1: PROGRAMMER'S MODEL REGISTER DESCRIPTIONS

Note 1: This register is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

2: The DOSTARTH and DOSTARTL registers are read-only.

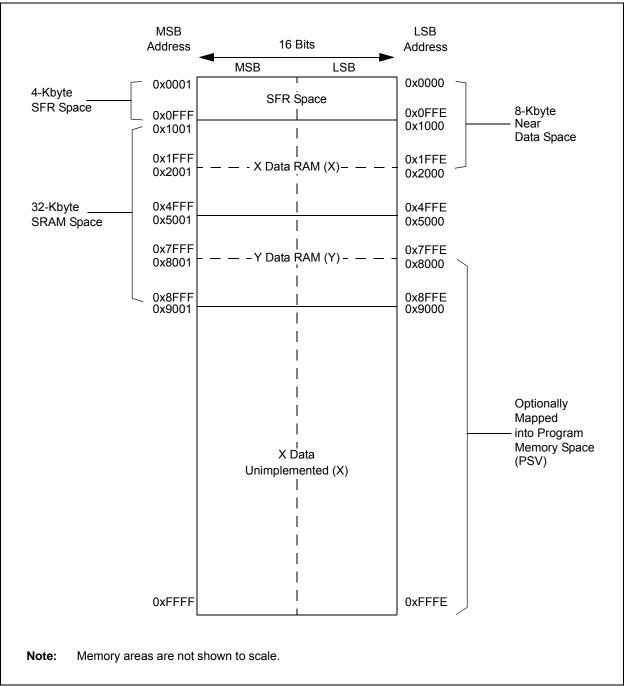

# FIGURE 4-10: DATA MEMORY MAP FOR dsPIC33EP256MC20X/50X AND dsPIC33EP256GP50X DEVICES

|                 |       |             |                                     |         |         |         |            |         |          |               |        |       |       |        |          |          |        | All    |

|-----------------|-------|-------------|-------------------------------------|---------|---------|---------|------------|---------|----------|---------------|--------|-------|-------|--------|----------|----------|--------|--------|

| File Name       | Addr. | Bit 15      | Bit 14                              | Bit 13  | Bit 12  | Bit 11  | Bit 10     | Bit 9   | Bit 8    | Bit 7         | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1    | Bit 0  | Resets |

| PTGCST          | 0AC0  | PTGEN       | —                                   | PTGSIDL | PTGTOGL |         | PTGSWT     | PTGSSEN | PTGIVIS  | PTGSTRT       | PTGWTO | _     | _     | —      | —        | PTGIT    | M<1:0> | 0000   |

| PTGCON          | 0AC2  | F           | PTGCLK<2                            | :0>     |         | F       | PTGDIV<4:0 | >       |          |               | PTGPWD | <3:0> |       | _      | P        | TGWDT<2: | 0>     | 0000   |

| PTGBTE          | 0AC4  |             | ADCTS<4:1> IC4TSS IC3TSS IC2TSS IC1 |         |         |         |            |         |          | OC4CS         | OC3CS  | OC2CS | OC1CS | OC4TSS | OC3TSS   | OC2TSS   | OC1TSS | 0000   |

| PTGHOLD         | 0AC6  |             |                                     |         |         |         |            |         | PTGHOLD  | <15:0>        |        |       |       |        |          |          |        | 0000   |

| <b>PTGT0LIM</b> | 0AC8  |             |                                     |         |         |         |            |         | PTGT0LIM | <15:0>        |        |       |       |        |          |          |        | 0000   |

| PTGT1LIM        | 0ACA  |             |                                     |         |         |         |            |         | PTGT1LIM | <15:0>        |        |       |       |        |          |          |        | 0000   |

| PTGSDLIM        | 0ACC  |             | PTGSDLIM<15:0> C                    |         |         |         |            |         |          |               |        |       | 0000  |        |          |          |        |        |

| <b>PTGC0LIM</b> | 0ACE  |             | PTGC0LIM<15:0>                      |         |         |         |            |         |          |               |        |       | 0000  |        |          |          |        |        |

| PTGC1LIM        | 0AD0  |             | PTGC1LIM<15:0>                      |         |         |         |            |         |          |               |        |       |       | 0000   |          |          |        |        |

| PTGADJ          | 0AD2  |             |                                     |         |         |         |            |         | PTGADJ<  | :15:0>        |        |       |       |        |          |          |        | 0000   |

| PTGL0           | 0AD4  |             |                                     |         |         |         |            |         | PTGL0<   | 15:0>         |        |       |       |        |          |          |        | 0000   |

| PTGQPTR         | 0AD6  | —           | —                                   | —       | —       | _       | —          | —       | _        | —             | —      | -     |       | P      | TGQPTR<4 | 4:0>     |        | 0000   |

| PTGQUE0         | 0AD8  |             |                                     |         | STEP    | 1<7:0>  |            |         |          | STEP0<7:0>    |        |       |       |        |          | 0000     |        |        |

| PTGQUE1         | 0ADA  |             |                                     |         | STEP    | '3<7:0> |            |         |          |               |        |       | STEP2 | 2<7:0> |          |          |        | 0000   |

| PTGQUE2         | 0ADC  |             |                                     |         | STEP    | 25<7:0> |            |         |          |               |        |       | STEP4 | <7:0>  |          |          |        | 0000   |

| PTGQUE3         | 0ADE  |             | STEP7<7:0>                          |         |         |         |            |         |          |               |        |       | STEP6 | 6<7:0> |          |          |        | 0000   |

| PTGQUE4         | 0AE0  | STEP9<7:0>  |                                     |         |         |         |            |         |          | STEP8<7:0>    |        |       |       |        |          | 0000     |        |        |

| PTGQUE5         | 0AE2  |             |                                     |         | STEP    | 11<7:0> |            |         |          | STEP10<7:0>   |        |       |       |        |          | 0000     |        |        |

| PTGQUE6         | 0AE4  |             |                                     |         | STEP    | 13<7:0> |            |         |          | STEP12<7:0>   |        |       |       |        |          | 0000     |        |        |

| PTGQUE7         | 0AE6  | STEP15<7:0> |                                     |         |         |         |            |         |          | STEP14<7:0> 0 |        |       |       |        | 0000     |          |        |        |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 78

### TABLE 4-53: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|---------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | _      | _      | _      | _      | TRISA10 | TRISA9 | TRISA8 | TRISA7 | -     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 079F          |

| PORTA        | 0E02  |        | _      | _      | -      | _      | RA10    | RA9    | RA8    | RA7    | -     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | LATA10  | LATA9  | LATA8  | LATA7  | -     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | —      | —      | _      |        | ODCA10  | ODCA9  | ODCA8  | ODCA7  | —     | —     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | —      | —      | _      |        | CNIEA10 | CNIEA9 | CNIEA8 | CNIEA7 | —     | —     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | —      | —      | _      |        | CNPUA10 | CNPUA9 | CNPUA8 | CNPUA7 | —     | —     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | —      | —      | _      |        | CNPDA10 | CNPDA9 | CNPDA8 | CNPDA7 | —     | —     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | _      | _      | —       | _      | —      | _      | _     | —     | ANSA4  | _      | _      | ANSA1  | ANSA0  | 0013          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-54: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | -       | -      | ANSB8  | _      | _      | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-55: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISC        | 0E20  | —      | _      | _      |        | —      | _      | TRISC9 | TRISC8 | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 03FF          |

| PORTC        | 0E22  | _      | _      | -      | _      | _      | —      | RC9    | RC8    | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xxxx          |

| LATC         | 0E24  | —      | —      | _      | _      |        | —      | LATC9  | LATC8  | LATC7  | LATC6  | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  | —      | —      | _      | _      |        | —      | ODCC9  | ODCC8  | ODCC7  | ODCC6  | ODCC5  | ODCC4  | ODCC3  | ODCC2  | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | —      | —      | _      | _      |        | —      | CNIEC9 | CNIEC8 | CNIEC7 | CNIEC6 | CNIEC5 | CNIEC4 | CNIEC3 | CNIEC2 | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  | —      | —      | _      | _      |        | —      | CNPUC9 | CNPUC8 | CNPUC7 | CNPUC6 | CNPUC5 | CNPUC4 | CNPUC3 | CNPUC2 | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  | —      | —      | _      | _      |        | —      | CNPDC9 | CNPDC8 | CNPDC7 | CNPDC6 | CNPDC5 | CNPDC4 | CNPDC3 | CNPDC2 | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | —      | —      | _      | _      |        | —      | _      |        |        |        | —      |        | _      | ANSC2  | ANSC1  | ANSC0  | 0007          |

Legend: x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2013 Microchip Technology Inc.

### 7.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

### 7.3.1 KEY RESOURCES

- "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

### 7.4 Interrupt Control and Status Registers

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- INTTREG

### 7.4.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior and also contains the Global Interrupt Enable bit (GIE).

INTCON3 contains the status flags for the DMA and DO stack overflow status trap sources.

The INTCON4 register contains the software generated hard trap status bit (SGHT).

### 7.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

### 7.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

### 7.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

### 7.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number bits (VECNUM<7:0>) and Interrupt Priority Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

### 7.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers refer to "**CPU**" (DS70359) in the "*dsPIC33/PIC24 Family Reference Manual*".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

## 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator" (DS70580) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

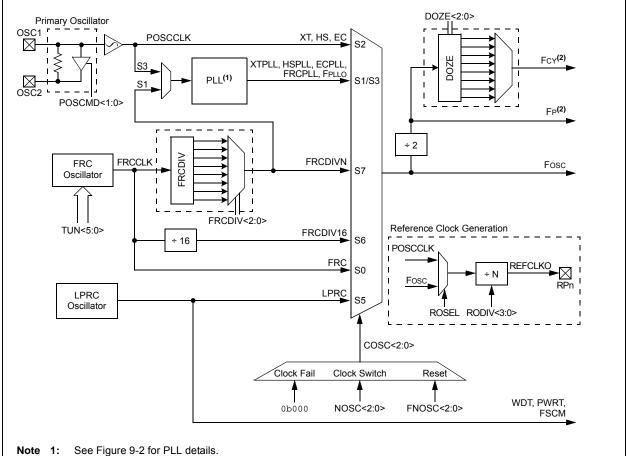

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X oscillator system provides:

- On-chip Phase-Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources

- On-the-fly clock switching between various clock sources

- · Doze mode for system power savings

- Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Configuration bits for clock source selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

### FIGURE 9-1: OSCILLATOR SYSTEM DIAGRAM

2: The term, FP, refers to the clock source for all peripherals, while FCY refers to the clock source for the CPU. Throughout this document, FCY and FP are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used with a doze ratio of 1:2 or lower.

# **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 4 Unimplemented: Read as '0'

- bit 3 **CF:** Clock Fail Detect bit<sup>(3)</sup>

- 1 = FSCM has detected clock failure

- 0 = FSCM has not detected clock failure

- bit 2-1 Unimplemented: Read as '0'

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Requests oscillator switch to selection specified by the NOSC<2:0> bits

- 0 = Oscillator switch is complete

- **Note 1:** Writes to this register require an unlock sequence. Refer to **"Oscillator"** (DS70580) in the *"dsPIC33/ PIC24 Family Reference Manual"* (available from the Microchip web site) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

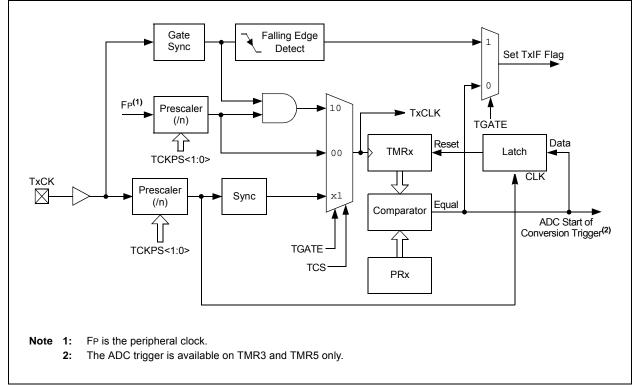

### FIGURE 13-2: TYPE C TIMER BLOCK DIAGRAM (x = 3 AND 5)

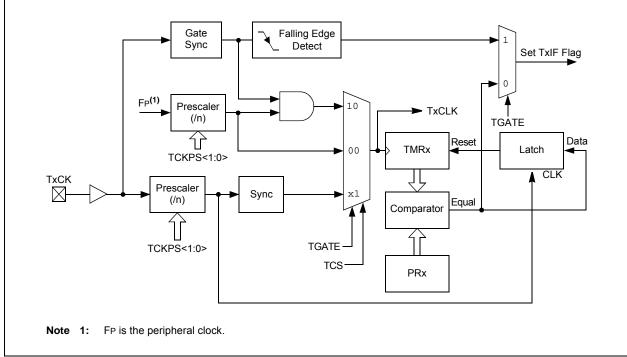

## FIGURE 13-1:TYPE B TIMER BLOCK DIAGRAM (x = 2 AND 4)

# **19.2** I<sup>2</sup>C Control Registers

### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER

| R/W-0      | U-0                                                                                                                                                | R/W-0                                  | R/W-1, HC                  | R/W-0                        | R/W-0            | R/W-0           | R/W-0          |  |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------|------------------------------|------------------|-----------------|----------------|--|--|--|--|

| I2CEN      | —                                                                                                                                                  | I2CSIDL                                | SCLREL                     | IPMIEN <sup>(1)</sup>        | A10M             | DISSLW          | SMEN           |  |  |  |  |

| bit 15     |                                                                                                                                                    |                                        |                            |                              |                  |                 | bit 8          |  |  |  |  |

|            |                                                                                                                                                    |                                        |                            |                              |                  |                 |                |  |  |  |  |

| R/W-0      | R/W-0                                                                                                                                              | R/W-0                                  | R/W-0, HC                  | R/W-0, HC                    | R/W-0, HC        | R/W-0, HC       | R/W-0, HC      |  |  |  |  |

| GCEN       | STREN                                                                                                                                              | ACKDT                                  | ACKEN                      | RCEN                         | PEN              | RSEN            | SEN            |  |  |  |  |

| bit 7      |                                                                                                                                                    |                                        |                            |                              |                  |                 | bit 0          |  |  |  |  |

| Legend:    |                                                                                                                                                    | HC = Hardware                          | Cloarable bit              |                              |                  |                 |                |  |  |  |  |

| R = Readab | le hit                                                                                                                                             | W = Writable bi                        |                            | II = I Inimpler              | mented bit, rea  | d as '0'        |                |  |  |  |  |

|            | -n = Value at POR (1' = Bit is set (0' = Bit is cleared x = Bit is unknown                                                                         |                                        |                            |                              |                  |                 |                |  |  |  |  |

|            |                                                                                                                                                    |                                        |                            |                              |                  |                 | nown           |  |  |  |  |

| bit 15     | <b>12CEN:</b> 12Cx                                                                                                                                 | Enable bit                             |                            |                              |                  |                 |                |  |  |  |  |

|            |                                                                                                                                                    | he I2Cx module                         |                            |                              |                  |                 | ;              |  |  |  |  |

|            | 0 = Disables                                                                                                                                       | the I2Cx module;                       | all l <sup>2</sup> C™ pins | are controlled               | by port functior | ıs              |                |  |  |  |  |

| bit 14     | Unimplemen                                                                                                                                         | ted: Read as '0'                       |                            |                              |                  |                 |                |  |  |  |  |

| bit 13     |                                                                                                                                                    | x Stop in Idle Mo                      |                            |                              |                  |                 |                |  |  |  |  |

|            | 1 = Discontinues module operation when device enters an Idle mode                                                                                  |                                        |                            |                              |                  |                 |                |  |  |  |  |

| bit 12     | <ul> <li>0 = Continues module operation in Idle mode</li> <li>SCLREL: SCLx Release Control bit (when operating as I<sup>2</sup>C slave)</li> </ul> |                                        |                            |                              |                  |                 |                |  |  |  |  |

|            | 1 = Releases                                                                                                                                       |                                        |                            |                              | slave)           |                 |                |  |  |  |  |

|            |                                                                                                                                                    | Lx clock low (clo                      | ck stretch)                |                              |                  |                 |                |  |  |  |  |

|            | If STREN = 1                                                                                                                                       | <u>:</u>                               | -                          |                              |                  |                 |                |  |  |  |  |

|            | •                                                                                                                                                  | ., software can w                      |                            |                              |                  | ,               |                |  |  |  |  |

|            |                                                                                                                                                    | ing of every slav<br>reception. Hardw  |                            |                              |                  |                 | t every slave  |  |  |  |  |

|            | If STREN = 0                                                                                                                                       | -                                      |                            |                              |                  |                 |                |  |  |  |  |

|            |                                                                                                                                                    | <u>.</u><br>, software can or          | nly write '1' to re        | elease clock). I             | Hardware is cle  | ar at the begir | ning of every  |  |  |  |  |

|            | -                                                                                                                                                  | te transmission.                       |                            |                              | -                | address byte re | eception.      |  |  |  |  |

| bit 11     |                                                                                                                                                    | ligent Peripheral                      |                            |                              |                  |                 |                |  |  |  |  |

|            | 1 = IPMI mod<br>0 = IPMI mod                                                                                                                       | e is enabled; all                      | addresses are              | Acknowledged                 | 1                |                 |                |  |  |  |  |

| bit 10     |                                                                                                                                                    | Slave Address b                        | i+                         |                              |                  |                 |                |  |  |  |  |

|            |                                                                                                                                                    | is a 10-bit slave                      |                            |                              |                  |                 |                |  |  |  |  |

|            |                                                                                                                                                    | is a 7-bit slave a                     |                            |                              |                  |                 |                |  |  |  |  |

| bit 9      | DISSLW: Dis                                                                                                                                        | able Slew Rate C                       | Control bit                |                              |                  |                 |                |  |  |  |  |

|            |                                                                                                                                                    | control is disable                     |                            |                              |                  |                 |                |  |  |  |  |

|            |                                                                                                                                                    | control is enable                      |                            |                              |                  |                 |                |  |  |  |  |

| bit 8      |                                                                                                                                                    | us Input Levels b                      |                            | 0145                         | <b>c</b>         |                 |                |  |  |  |  |

|            |                                                                                                                                                    | /O pin thresholds<br>SMBus input thre  |                            | n SMBus speci                | fication         |                 |                |  |  |  |  |

| bit 7      |                                                                                                                                                    | ral Call Enable b                      |                            | ing as I <sup>2</sup> C slav | /e)              |                 |                |  |  |  |  |

|            | 1 = Enables in                                                                                                                                     | terrupt when a ge<br>all address disat | neral call addre           | -                            |                  | dule is enabled | for reception) |  |  |  |  |

|            |                                                                                                                                                    |                                        |                            |                              |                  |                 |                |  |  |  |  |

Note 1: When performing master operations, ensure that the IPMIEN bit is set to '0'.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

### REGISTER 21-16: CxRXFnSID: ECANx ACCEPTANCE FILTER n STANDARD IDENTIFIER REGISTER (n = 0-15)

| RW-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x         SID10       SID9       SID8       SID7       SID6       SID5       SID4       SID3         bit 15       bit 15       bit 8       bit 8       bit 8       bit 8       bit 8         R/W-x       R/W-x       R/W-x       U-0       R/W-x       U-0       R/W-x       R/W-x         SID2       SID1       SID0       -       EXIDE       -       EID17       EID16         bit 7       5ID2       SID1       SID0       -       EXIDE       -       EID17       EID16         bit 7       -       -       EID17       EID16       bit 0       bit 0         Legend:       R       Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |                                                                                                                                                              |                  |               |                                    |       |                 |       |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|------------------------------------|-------|-----------------|-------|--|--|--|--|

| bit 15 bit 2 bit 3 bit 8 bit 8 bit 8 bit 7 bit 7 bit 9 bit 7 bit 0 bit 0 bit 7 bit 0 bit 0 bit 7 bit 0 bit 0 bit 0 bit 1 bit 9 bit 1 bit 9 bit 1 bit 1 bit 9 bit 1 | R/W-x         | R/W-x                                                                                                                                                        | R/W-x            | R/W-x         | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |  |  |  |

| R/W-x       R/W-x       U-0       R/W-x       U-0       R/W-x       R/W-x         SID2       SID1       SID0       -       EXIDE       -       EID17       EID16         bit 7       bit 0         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'       bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses       0 = Matches only messages with Standard Identifier addresses         0 = Matches only messages with Standard Identifier addresses       Ignores EXIDE bit.       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'       bit 1-0       EID       EID         bit 1-0       EID       Extended Identifier bits       1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SID10         | SID9                                                                                                                                                         | SID8             | SID7          | SID6                               | SID5  | SID4            | SID3  |  |  |  |  |

| SID2       SID1       SID0       —       EXIDE       —       EID17       EID16         bit 7       bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 15        | ÷                                                                                                                                                            |                  |               |                                    |       |                 | bit 8 |  |  |  |  |

| SID2       SID1       SID0       —       EXIDE       —       EID17       EID16         bit 7       bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                                                                                                                                                              |                  |               |                                    |       |                 |       |  |  |  |  |

| bit 7       bit 0         Legend:       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter       x = Bit is unknown         bit 4       Unimplemented: Read as '0'       bit 3       EXIDE: Extended Identifier Enable bit       If MIDE = 1:         1 = Matches only messages with Extended Identifier addresses       0 = Matches only messages with Standard Identifier addresses         0 = Matches only messages with Standard Identifier addresses       If MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'       bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter       1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-x         | R/W-x                                                                                                                                                        | R/W-x            | U-0           | R/W-x                              | U-0   | R/W-x           | R/W-x |  |  |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses         If MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SID2          | SID1                                                                                                                                                         | SID0             | _             | EXIDE                              |       | EID17           | EID16 |  |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses       0 = Matches only messages with Standard Identifier addresses         1f MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID         a Matches bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 7         |                                                                                                                                                              |                  |               |                                    |       |                 | bit 0 |  |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Message Sit, SIDE       5         bit 2       Unimplemented: Read as '0'         bit 2       Unimplemented: Read as '0'         bit 4       Unimplemented: Read as '0'         bit 1-0       EID         if MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID         a Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |                                                                                                                                                              |                  |               |                                    |       |                 |       |  |  |  |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         o = Message address bit, SIDx, must be '1' to match filter       0' = Bit is cleared       x = Bit is unknown         bit 4       Unimplemented: Read as '0'       bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses       0 = Matches only messages with Standard Identifier addresses         If MIDE = 0:       Ignores EXIDE bit.       If MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter       1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Legend:       |                                                                                                                                                              |                  |               |                                    |       |                 |       |  |  |  |  |

| bit 15-5       SID<10:0>: Standard Identifier bits         1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses         0 = Matches only messages with Standard Identifier addresses         1 f MIDE = 0:         Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R = Readable  | e bit                                                                                                                                                        | W = Writable     | bit           | U = Unimplemented bit, read as '0' |       |                 |       |  |  |  |  |

| 1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses       0 = Matches only messages with Standard Identifier addresses         If MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID         I= Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -n = Value at | POR                                                                                                                                                          | '1' = Bit is set |               | '0' = Bit is cle                   | ared  | x = Bit is unkr | nown  |  |  |  |  |

| If MIDE = 1:         1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses         If MIDE = 0:         Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 4         | 0 = Message                                                                                                                                                  | address bit, SI  | Dx, must be ' |                                    |       |                 |       |  |  |  |  |

| bit 1-0 EID<17:16>: Extended Identifier bits<br>1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 3         | If MIDE = 1:<br>1 = Matches only messages with Extended Identifier addresses<br>0 = Matches only messages with Standard Identifier addresses<br>If MIDE = 0: |                  |               |                                    |       |                 |       |  |  |  |  |

| 1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 2         | Unimplemen                                                                                                                                                   | ted: Read as '   | כ'            |                                    |       |                 |       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 1-0       | EID<17:16>:                                                                                                                                                  | Extended Iden    | tifier bits   |                                    |       |                 |       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | •                                                                                                                                                            |                  |               |                                    |       |                 |       |  |  |  |  |

| Bit Field             | Description                                                                                                                                                                                   |