Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | ·                                                                              |

| RAM Size                   | 8K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128gp206-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for digital signal processing. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

# 3.1 Registers

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can act as a data, address or address offset register. The 16th working register (W15) operates as a Software Stack Pointer for interrupts and calls.

# 3.2 Instruction Set

The instruction set for dsPIC33EPXXXGP50X and dsPIC33EPXXXMC20X/50X devices has two classes of instructions: the MCU class of instructions and the DSP class of instructions. The instruction set for PIC24EPXXXGP/MC20X devices has the MCU class of instructions only and does not support DSP instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

## 3.3 Data Space Addressing

The base Data Space can be addressed as 64 Kbytes (32K words).

The Data Space includes two ranges of memory, referred to as X and Y data memory. Each memory range is accessible through its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. On dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Spaces have memory locations that are device-specific, and are described further in the data memory maps in **Section 4.2 "Data Address Space"**.

The upper 32 Kbytes of the Data Space memory map can optionally be mapped into Program Space (PS) at any 32-Kbyte aligned program word boundary. The Program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Moreover, the Base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space (EDS) address. The EDS can be addressed as 8M words or 16 Mbytes. Refer to the "**Data Memory**" (DS70595) and "**Program Memory**" (DS70613) sections in the "*dsPIC33/PIC24 Family Reference Manual*" for more details on EDS, PSV and table accesses.

On the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data re-ordering for radix-2 FFT algorithms. PIC24EPXXXGP/MC20X devices do not support Modulo and Bit-Reversed Addressing.

# 3.4 Addressing Modes

The CPU supports these addressing modes:

- Inherent (no operand)

- Relative

- Literal

- · Memory Direct

- Register Direct

- Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

### 3.7 CPU Control Registers

| REGISTER               | 3-1: SR: Cl                                                                                                                       | PU STATUS I                                                           | REGISTER                    |                          |                    |                   |               |  |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------|--------------------------|--------------------|-------------------|---------------|--|--|

| R/W-0                  | R/W-0                                                                                                                             | R/W-0                                                                 | R/W-0                       | R/C-0                    | R/C-0              | R-0               | R/W-0         |  |  |

| 0A <sup>(1)</sup>      | OB <sup>(1)</sup>                                                                                                                 | SA <sup>(1,4)</sup>                                                   | SB <sup>(1,4)</sup>         | OAB <sup>(1)</sup>       | SAB <sup>(1)</sup> | DA <sup>(1)</sup> | DC            |  |  |

| bit 15                 |                                                                                                                                   |                                                                       |                             |                          |                    |                   | bit 8         |  |  |

| R/W-0 <sup>(2,3)</sup> | R/W-0 <sup>(2,3)</sup>                                                                                                            | R/W-0 <sup>(2,3)</sup>                                                | R-0                         | R/W-0                    | R/W-0              | R/W-0             | R/W-0         |  |  |

| IPL2                   | IPL1                                                                                                                              | IPL0                                                                  | RA                          | N                        | OV                 | Z                 | С             |  |  |

| bit 7                  | ·                                                                                                                                 | •                                                                     |                             | •                        |                    |                   | bit (         |  |  |

| Legend:                |                                                                                                                                   | C = Clearable                                                         | e bit                       |                          |                    |                   |               |  |  |

| R = Readab             | le bit                                                                                                                            | W = Writable                                                          | bit                         | U = Unimpler             | nented bit, read   | l as '0'          |               |  |  |

| -n = Value a           | t POR                                                                                                                             | '1'= Bit is set                                                       |                             | '0' = Bit is cle         | ared               | x = Bit is unkr   | iown          |  |  |

|                        |                                                                                                                                   |                                                                       |                             |                          |                    |                   |               |  |  |

| bit 15                 | OA: Accumul                                                                                                                       | ator A Overflov                                                       | v Status bit <sup>(1)</sup> |                          |                    |                   |               |  |  |

|                        | 1 = Accumula                                                                                                                      | ator A has over                                                       | flowed                      |                          |                    |                   |               |  |  |

|                        | 0 = Accumula                                                                                                                      | ator A has not o                                                      | verflowed                   |                          |                    |                   |               |  |  |

| bit 14                 | OB: Accumul                                                                                                                       | ator B Overflov                                                       | v Status bit <sup>(1)</sup> |                          |                    |                   |               |  |  |

|                        | 1 = Accumula                                                                                                                      | ator B has over                                                       | flowed                      |                          |                    |                   |               |  |  |

|                        |                                                                                                                                   | ator B has not c                                                      |                             |                          |                    |                   |               |  |  |

| bit 13                 | SA: Accumul                                                                                                                       | ator A Saturatio                                                      | on 'Sticky' Sta             | tus bit <sup>(1,4)</sup> |                    |                   |               |  |  |

|                        | <ul> <li>1 = Accumulator A is saturated or has been saturated at some time</li> <li>0 = Accumulator A is not saturated</li> </ul> |                                                                       |                             |                          |                    |                   |               |  |  |

| bit 12                 | SB: Accumul                                                                                                                       | ator B Saturatio                                                      | on 'Sticky' Sta             | tus bit <sup>(1,4)</sup> |                    |                   |               |  |  |

|                        | 1 = Accumula                                                                                                                      | ator B is saturat<br>ator B is not sat                                | ted or has bee              |                          | some time          |                   |               |  |  |

| bit 11                 |                                                                                                                                   |                                                                       |                             | vorflow Status           | ы#(1)              |                   |               |  |  |

|                        |                                                                                                                                   | OAB: OA    OB Combined Accumulator Overflow Status bit <sup>(1)</sup> |                             |                          |                    |                   |               |  |  |

|                        | <ul> <li>1 = Accumulators A or B have overflowed</li> <li>0 = Neither Accumulators A or B have overflowed</li> </ul>              |                                                                       |                             |                          |                    |                   |               |  |  |

| bit 10                 |                                                                                                                                   | B Combined Ad                                                         |                             |                          | (1)                |                   |               |  |  |

|                        |                                                                                                                                   |                                                                       |                             |                          | urated at some     | time              |               |  |  |

|                        | 0 = Neither A                                                                                                                     | ccumulators A                                                         | or B are satur              | ated                     |                    |                   |               |  |  |

| bit 9                  | DA: DO Loop                                                                                                                       | Active bit <sup>(1)</sup>                                             |                             |                          |                    |                   |               |  |  |

|                        | 1 = DO <b>loop is</b>                                                                                                             | s in progress                                                         |                             |                          |                    |                   |               |  |  |

|                        | 0 = DO <b>loop</b> is                                                                                                             | s not in progres                                                      | S                           |                          |                    |                   |               |  |  |

| bit 8                  | DC: MCU AL                                                                                                                        | U Half Carry/Bo                                                       | orrow bit                   |                          |                    |                   |               |  |  |

|                        |                                                                                                                                   | out from the 4th sult occurred                                        | low-order bit (             | for byte-sized c         | lata) or 8th low-  | order bit (for wo | rd-sized data |  |  |

|                        | 0 = No carry                                                                                                                      |                                                                       |                             | oit (for byte-siz        | ed data) or 8th    | low-order bit (f  | or word-size  |  |  |

|                        | his bit is available                                                                                                              |                                                                       |                             |                          |                    |                   | -             |  |  |

| L                      | he IPL<2:0> bits<br>evel. The value ir<br>PL<3> = 1.                                                                              |                                                                       |                             |                          |                    |                   |               |  |  |

#### REGISTER 3-1: SR: CPU STATUS REGISTER

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **4:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

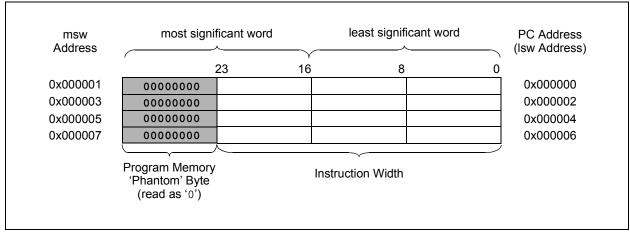

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-6).

Program memory addresses are always word-aligned on the lower word and addresses are incremented, or decremented by two, during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

## 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices reserve the addresses between 0x000000 and 0x000200 for hardcoded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of Flash memory, with the actual address for the start of code at address, 0x000002, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in **Section 7.1** "Interrupt Vector Table".

### FIGURE 4-6: PROGRAM MEMORY ORGANIZATION

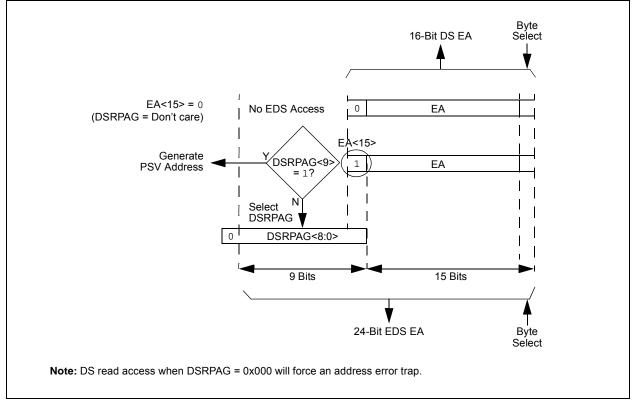

#### 4.4.1 PAGED MEMORY SCHEME

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre-modified and post-modified Effective Addresses (EA). The upper half of the base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Read Page register (DSRPAG) or the 9-bit Write Page register (DSWPAG), to form an Extended Data Space (EDS) address or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

Construction of the EDS address is shown in Example 4-1. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when base address bit, EA<15> = 1, DSWPAG<8:0> are concatenated onto EA<14:0> to form the 24-bit EDS write address.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|                 | 12. 2007.00                                                                                                                        |                                       |              |                   |                  |                 |        |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------|-------------------|------------------|-----------------|--------|--|--|

| U-0             | U-0                                                                                                                                | U-0                                   | U-0          | U-0               | U-0              | U-0             | U-0    |  |  |

| —               | —                                                                                                                                  | —                                     | —            | —                 | —                | —               | —      |  |  |

| bit 15          |                                                                                                                                    |                                       |              |                   |                  |                 | bit 8  |  |  |

|                 |                                                                                                                                    |                                       |              |                   |                  |                 |        |  |  |

| U-0             | U-0                                                                                                                                | U-0                                   | U-0          | R-0               | R-0              | R-0             | R-0    |  |  |

| —               |                                                                                                                                    | —                                     | —            | RQCOL3            | RQCOL2           | RQCOL1          | RQCOL0 |  |  |

| bit 7           |                                                                                                                                    |                                       |              |                   |                  |                 | bit 0  |  |  |

|                 |                                                                                                                                    |                                       |              |                   |                  |                 |        |  |  |

| Legend:         |                                                                                                                                    |                                       |              |                   |                  |                 |        |  |  |

| R = Readable    | bit                                                                                                                                | W = Writable                          | bit          | U = Unimpler      | mented bit, read | l as '0'        |        |  |  |

| -n = Value at F | POR                                                                                                                                | '1' = Bit is set                      |              | '0' = Bit is cle  | ared             | x = Bit is unkr | nown   |  |  |

|                 |                                                                                                                                    |                                       |              |                   |                  |                 |        |  |  |

| bit 15-4        | Unimplemen                                                                                                                         | ted: Read as '                        | כ'           |                   |                  |                 |        |  |  |

| bit 3           | RQCOL3: DN                                                                                                                         | /IA Channel 3 T                       | ransfer Requ | est Collision F   | ag bit           |                 |        |  |  |

|                 |                                                                                                                                    | e and interrupt<br>est collision is d |              | st collision is d | etected          |                 |        |  |  |

| <b>h</b> # 0    | •                                                                                                                                  |                                       |              | est Callisian Fl  | aa hit           |                 |        |  |  |

| bit 2           |                                                                                                                                    | /A Channel 2 T                        | •            |                   | 0                |                 |        |  |  |

|                 | <ul> <li>1 = User force and interrupt-based request collision is detected</li> <li>0 = No request collision is detected</li> </ul> |                                       |              |                   |                  |                 |        |  |  |

| bit 1           | RQCOL1: DMA Channel 1 Transfer Request Collision Flag bit                                                                          |                                       |              |                   |                  |                 |        |  |  |

|                 | 1 = User for                                                                                                                       | e and interrupt                       | -based reque | st collision is d | etected          |                 |        |  |  |

|                 | 0 = No reque                                                                                                                       | est collision is d                    | etected      |                   |                  |                 |        |  |  |

| bit 0           | RQCOLO: DN                                                                                                                         | /IA Channel 0 T                       | ransfer Requ | est Collision F   | lag bit          |                 |        |  |  |

|                 | 1 = User force                                                                                                                     | e and interrupt                       | -based reque | st collision is d | etected          |                 |        |  |  |

### REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER

0 = No request collision is detected

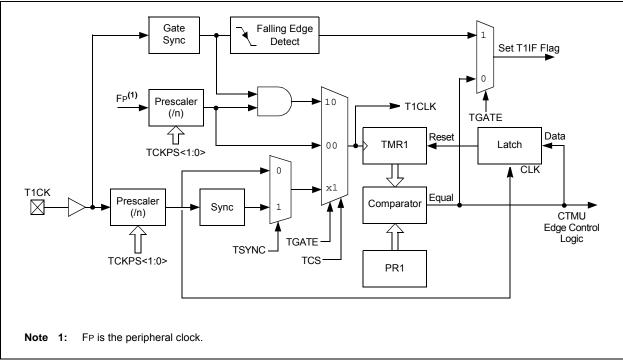

# 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer that can operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated in Asynchronous Counter mode from an external clock source

- The external clock input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler

- A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FCY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit setting for different operating modes are given in the Table 12-1.

| Mode                    | TCS | TGATE | TSYNC |

|-------------------------|-----|-------|-------|

| Timer                   | 0   | 0     | х     |

| Gated Timer             | 0   | 1     | x     |

| Synchronous<br>Counter  | 1   | х     | 1     |

| Asynchronous<br>Counter | 1   | x     | 0     |

#### TABLE 12-1: TIMER MODE SETTINGS

### FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

#### 16.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FOSCSEL<6>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring, PWMLOCK = 0. To gain write access to these locked registers, the user application must write two consecutive values of (0xABCD and 0x4321) to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 16-1.

#### EXAMPLE 16-1: PWMx WRITE-PROTECTED REGISTER UNLOCK SEQUENCE

|                                                                                                          | lled low externally in order to clear and disable the fault<br>egister requires unlock sequence                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0x0000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,FCLCON1</pre> | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of FCLCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to FCLCON1 register</pre> |

| -                                                                                                        | d polarity using the IOCON1 register<br>gister requires unlock sequence                                                                                                                                                                                                                           |

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0xF000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,IOCON1</pre>  | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of IOCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to IOCON1 register</pre>   |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0   | R/W-0            | R/W-0                                                | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

|-----------------|-------|------------------|------------------------------------------------------|------------------------------------|-------|-------|-------|--|--|

| —               | —     |                  | DTRx<13:8>                                           |                                    |       |       |       |  |  |

| bit 15          |       |                  |                                                      |                                    |       |       | bit 8 |  |  |

|                 |       |                  |                                                      |                                    |       |       |       |  |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0                                                | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

|                 |       |                  | DTR                                                  | x<7:0>                             |       |       |       |  |  |

| bit 7           |       |                  |                                                      |                                    |       |       | bit 0 |  |  |

|                 |       |                  |                                                      |                                    |       |       |       |  |  |

| Legend:         |       |                  |                                                      |                                    |       |       |       |  |  |

| R = Readable    | bit   | W = Writable b   | bit                                                  | U = Unimplemented bit, read as '0' |       |       |       |  |  |

| -n = Value at F | POR   | '1' = Bit is set | = Bit is set '0' = Bit is cleared x = Bit is unknown |                                    |       |       |       |  |  |

## REGISTER 16-10: DTRx: PWMx DEAD-TIME REGISTER

bit 15-14 Unimplemented: Read as '0'

bit 13-0 DTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

#### REGISTER 16-11: ALTDTRx: PWMx ALTERNATE DEAD-TIME REGISTER

| U-0             | U-0   | R/W-0            | R/W-0 | R/W-0                                   | R/W-0   | R/W-0 | R/W-0 |

|-----------------|-------|------------------|-------|-----------------------------------------|---------|-------|-------|

| —               | _     |                  |       | ALTDTR                                  | x<13:8> |       |       |

| bit 15          |       |                  |       |                                         |         |       | bit 8 |

|                 |       |                  |       |                                         |         |       |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0   | R/W-0 | R/W-0 |

|                 |       |                  | ALTDT | Rx<7:0>                                 |         |       |       |

| bit 7           |       |                  |       |                                         |         |       | bit 0 |

| Legend:         |       |                  |       |                                         |         |       |       |

| R = Readable    | bit   | W = Writable t   | oit   | U = Unimplemented bit, read as '0'      |         |       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |         |       | nown  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 ALTDTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

#### REGISTER 16-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER<sup>(1)</sup>

- bit 7-3 FLTSRC<4:0>: Fault Control Signal Source Select for PWM Generator # bits 11111 = Fault 32 (default) 11110 = Reserved . . 01100 = Reserved 01011 = Comparator 4 01010 = Op Amp/Comparator 3

- 01001 = Op Amp/Comparator 2

- 01000 = Op Amp/Comparator 1

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Reserved

- 00100 = Reserved

- 00011 = Fault 4

- 00010 = Fault 3

- 00001 = Fault 2 00000 = Fault 1

- bit 2 ELTROL Fault Delarity for DWM Concrete

# bit 2 **FLTPOL:** Fault Polarity for PWM Generator # bit<sup>(2)</sup>

- 1 = The selected Fault source is active-low

- 0 = The selected Fault source is active-high

- bit 1-0 FLTMOD<1:0>: Fault Mode for PWM Generator # bits

- 11 = Fault input is disabled

- 10 = Reserved

- 01 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (cycle)

- 00 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (latched condition)

- **Note 1:** If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

- **2:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

| U-0                 | U-0                                                                                                                                                                                                                                              | U-0                                                                                          | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |  |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------|----------------------|----------------------|----------------------|----------------------|--|--|

|                     | —                                                                                                                                                                                                                                                | _                                                                                            | DISSCK                                | DISSDO               | MODE16               | SMP                  | CKE <sup>(1)</sup>   |  |  |

| bit 15              |                                                                                                                                                                                                                                                  | •                                                                                            |                                       | •                    | •                    | •                    | bit                  |  |  |

| R/W-0               | R/W-0                                                                                                                                                                                                                                            | R/W-0                                                                                        | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |  |  |

| SSEN <sup>(2)</sup> | CKP                                                                                                                                                                                                                                              | MSTEN                                                                                        | SPRE2 <sup>(3)</sup>                  | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |  |  |

| bit 7               | CKF                                                                                                                                                                                                                                              | WIGTEN                                                                                       | SFREZ 7                               | SFREI?               | SFREU 7              | FFREN                | bit                  |  |  |

|                     |                                                                                                                                                                                                                                                  |                                                                                              |                                       |                      |                      |                      |                      |  |  |

| Legend:             |                                                                                                                                                                                                                                                  |                                                                                              |                                       |                      |                      |                      |                      |  |  |

| R = Readabl         | le bit                                                                                                                                                                                                                                           | W = Writable                                                                                 | bit                                   | U = Unimpler         | mented bit, read     | d as '0'             |                      |  |  |

| -n = Value at       | t POR                                                                                                                                                                                                                                            | '1' = Bit is se                                                                              | t                                     | '0' = Bit is cle     | ared                 | x = Bit is unkr      | nown                 |  |  |

|                     |                                                                                                                                                                                                                                                  |                                                                                              |                                       |                      |                      |                      |                      |  |  |

| bit 15-13           | Unimplemen                                                                                                                                                                                                                                       | ted: Read as                                                                                 | 0'                                    |                      |                      |                      |                      |  |  |

| bit 12              |                                                                                                                                                                                                                                                  |                                                                                              | bit (SPIx Mas                         | -                    | ()                   |                      |                      |  |  |

|                     |                                                                                                                                                                                                                                                  |                                                                                              | sabled, pin fun                       | ctions as I/O        |                      |                      |                      |  |  |

| oit 11              |                                                                                                                                                                                                                                                  | <ul> <li>0 = Internal SPIx clock is enabled</li> <li>DISSDO: Disable SDOx Pin bit</li> </ul> |                                       |                      |                      |                      |                      |  |  |

|                     | 1 = SDOx pin is not used by the module; pin functions as I/O                                                                                                                                                                                     |                                                                                              |                                       |                      |                      |                      |                      |  |  |

|                     | 0 = SDOx pin is controlled by the module                                                                                                                                                                                                         |                                                                                              |                                       |                      |                      |                      |                      |  |  |

| bit 10              | MODE16: Word/Byte Communication Select bit                                                                                                                                                                                                       |                                                                                              |                                       |                      |                      |                      |                      |  |  |

|                     | 1 = Communication is word-wide (16 bits)                                                                                                                                                                                                         |                                                                                              |                                       |                      |                      |                      |                      |  |  |

|                     | 0 = Communication is byte-wide (8 bits)                                                                                                                                                                                                          |                                                                                              |                                       |                      |                      |                      |                      |  |  |

| bit 9               |                                                                                                                                                                                                                                                  | SMP: SPIx Data Input Sample Phase bit                                                        |                                       |                      |                      |                      |                      |  |  |

|                     | Master mode                                                                                                                                                                                                                                      | -                                                                                            | end of data o                         | utout time           |                      |                      |                      |  |  |

|                     |                                                                                                                                                                                                                                                  |                                                                                              | middle of data                        |                      |                      |                      |                      |  |  |

|                     | Slave mode:                                                                                                                                                                                                                                      |                                                                                              |                                       |                      |                      |                      |                      |  |  |

|                     | SMP must be cleared when SPIx is used in Slave mode.                                                                                                                                                                                             |                                                                                              |                                       |                      |                      |                      |                      |  |  |

| bit 8               |                                                                                                                                                                                                                                                  | lock Edge Sele                                                                               |                                       |                      |                      |                      |                      |  |  |

|                     | <ul> <li>1 = Serial output data changes on transition from active clock state to Idle clock state (refer to bit 6)</li> <li>0 = Serial output data changes on transition from Idle clock state to active clock state (refer to bit 6)</li> </ul> |                                                                                              |                                       |                      |                      |                      |                      |  |  |

| bit 7               |                                                                                                                                                                                                                                                  |                                                                                              |                                       |                      |                      | ve clock state (I    |                      |  |  |

|                     | <b>SSEN:</b> Slave Select Enable bit (Slave mode) <sup>(2)</sup><br>1 = SSx pin is used for Slave mode                                                                                                                                           |                                                                                              |                                       |                      |                      |                      |                      |  |  |

|                     | $1 = \frac{33}{55}$ pin is used for Slave mode<br>0 = SSx pin is not used by the module; pin is controlled by port function                                                                                                                      |                                                                                              |                                       |                      |                      |                      |                      |  |  |

| bit 6               | CKP: Clock F                                                                                                                                                                                                                                     | Polarity Select                                                                              | bit                                   |                      |                      |                      |                      |  |  |

|                     |                                                                                                                                                                                                                                                  |                                                                                              | nigh level; activ<br>ow level; active |                      |                      |                      |                      |  |  |

| bit 5               | MSTEN: Mas                                                                                                                                                                                                                                       | ter Mode Enat                                                                                | ole bit                               |                      |                      |                      |                      |  |  |

|                     | 1 = Master m<br>0 = Slave mo                                                                                                                                                                                                                     |                                                                                              |                                       |                      |                      |                      |                      |  |  |

| Note 1: T           | he CKE bit is not                                                                                                                                                                                                                                | used in Frame                                                                                | d SPI modes. I                        | Program this bi      | it to '0' for Fram   | ed SPI modes (       | FRMEN = 1            |  |  |

|                     | his bit must be cl                                                                                                                                                                                                                               |                                                                                              |                                       |                      |                      |                      |                      |  |  |

| <b>0</b>            |                                                                                                                                                                                                                                                  |                                                                                              |                                       |                      |                      |                      |                      |  |  |

### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1

- **3:** Do not set both primary and secondary prescalers to the value of 1:1.

# REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 6         | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)<br>Used in conjunction with the SCLREL bit.<br>1 = Enables software or receives clock stretching<br>0 = Disables software or receives clock stretching |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5         | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                                     |

|               | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                                       |

| bit 4         | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                   |

|               | <ul> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits ACKDT data bit. Hardware is clear at the end of the master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul>              |

| bit 3         | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                   |

|               | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware is clear at the end of the eighth bit of the master receive data byte.</li> <li>0 = Receive sequence is not in progress</li> </ul>                                             |

| bit 2         | <b>PEN:</b> Stop Condition Enable bit (when operating as $I^2C$ master)                                                                                                                                                                       |

| 511 2         | 1 = Initiates Stop condition on SDAx and SCLx pins. Hardware is clear at the end of the master Stop sequence.                                                                                                                                 |

| <b>h</b> :+ 4 | 0 = Stop condition is not in progress                                                                                                                                                                                                         |

| bit 1         | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                  |

|               | <ul> <li>1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware is clear at the end of the<br/>master Repeated Start sequence.</li> <li>0 = Repeated Start condition is not in progress</li> </ul>                            |

| bit 0         | <b>SEN:</b> Start Condition Enable bit (when operating as $l^2C$ master)                                                                                                                                                                      |

|               | <ul> <li>1 = Initiates Start condition on SDAx and SCLx pins. Hardware is clear at the end of the master Start sequence.</li> <li>0 = Start condition is not in progress</li> </ul>                                                           |

**Note 1:** When performing master operations, ensure that the IPMIEN bit is set to '0'.

### REGISTER 20-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement is disabled or completed</li> </ul> |

| bit 4   | URXINV: UARTx Receive Polarity Inversion bit                                                                                                                                                                                              |

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                                                  |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                                                                           |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul>                                                        |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                                                                                |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                                                                             |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                                                                             |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                                                                                     |

|         | Refer to the " <b>UART</b> " (DS70582) section in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for receive or transmit operation.                                                             |

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

- 3: This feature is only available on 44-pin and 64-pin devices.

- 4: This feature is only available on 64-pin devices.

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| FLTEN15 | FLTEN14 | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10 | FLTEN9 | FLTEN8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

| FLTEN7  | FLTEN6  | FLTEN5  | FLTEN4  | FLTEN3  | FLTEN2  | FLTEN1 | FLTEN0 |

| bit 7   |         |         |         |         |         |        | bit 0  |

|         |         |         |         |         |         |        |        |

| Legend: |         |         |         |         |         |        |        |

#### REGISTER 21-11: CxFEN1: ECANx ACCEPTANCE FILTER ENABLE REGISTER 1

| Legend:           |                  |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

bit 15-0

FLTEN<15:0>: Enable Filter n to Accept Messages bits

1 = Enables Filter n

0 = Disables Filter n

REGISTER 21-12: CxBUFPNT1: ECANx FILTER 0-3 BUFFER POINTER REGISTER 1

| R/W-0         | R/W-0                                                 | R/W-0                                                                                                       | R/W-0                                          | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |

|---------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------|-----------------|----------|-------|

|               | F3BI                                                  | P<3:0>                                                                                                      |                                                |                                         | F2BI            | P<3:0>   |       |

| bit 15        |                                                       |                                                                                                             |                                                |                                         |                 |          | bit 8 |

| R/W-0         | R/W-0                                                 | R/W-0                                                                                                       | R/W-0                                          | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |

| F1BP<3:0>     |                                                       |                                                                                                             |                                                |                                         | F0BI            | P<3:0>   |       |

| bit 7         |                                                       |                                                                                                             |                                                |                                         |                 |          | bit ( |

| Legend:       |                                                       |                                                                                                             |                                                |                                         |                 |          |       |

| R = Readable  | e bit                                                 | W = Writable                                                                                                | bit                                            | U = Unimplem                            | nented bit, rea | d as '0' |       |

| -n = Value at | POR                                                   | '1' = Bit is set                                                                                            |                                                | '0' = Bit is cleared x = Bit is unknown |                 |          |       |

| bit 15-12     | 1111 = Filte<br>1110 = Filte<br>•<br>•<br>•<br>•<br>• | : RX Buffer Mas<br>er hits received in<br>er hits received in<br>er hits received in<br>er hits received in | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | iffer                                   |                 |          |       |

| bit 11-8      | F2BP<3:0>                                             | : RX Buffer Mas                                                                                             | k for Filter 2 b                               | oits (same value                        | s as bits<15:1  | 2>)      |       |

| bit 7-4       | F1BP<3:0>                                             | : RX Buffer Mas                                                                                             | k for Filter 1 k                               | oits (same value                        | s as bits<15:1  | 2>)      |       |

|               |                                                       |                                                                                                             |                                                |                                         |                 |          |       |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

# REGISTER 24-4: PTGT0LIM: PTG TIMER0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|------------------------------------|-------|-------|-------|-------------------|-----------------|-----------------|-------|

|                                    |       |       | PTGT0 | _IM<15:8>         |                 |                 |       |

| bit 15                             |       |       |       |                   |                 |                 | bit 8 |

|                                    |       |       |       |                   |                 |                 |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                                    |       |       | PTGT0 | LIM<7:0>          |                 |                 |       |

| bit 7                              |       |       |       |                   |                 |                 | bit 0 |

|                                    |       |       |       |                   |                 |                 |       |

| Legend:                            |       |       |       |                   |                 |                 |       |

| R = Readable bit W = Writable bit  |       |       | bit   | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

#### bit 15-0 **PTGT0LIM<15:0>:** PTG Timer0 Limit Register bits General Purpose Timer0 Limit register (effective only with a PTGT0 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

# REGISTER 24-5: PTGT1LIM: PTG TIMER1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0   | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|---------|---------|-------|-------|-------|

|        |       |       | PTGT1LI | M<15:8> |       |       |       |

| bit 15 |       |       |         |         |       |       | bit 8 |

|        |       |       |         |         |       |       |       |

| R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|--------|----------|-------|-------|-------|

|       |       |       | PTGT1L | -IM<7:0> |       |       |       |

| bit 7 |       |       |        |          |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-0 **PTGT1LIM<15:0>:** PTG Timer1 Limit Register bits

General Purpose Timer1 Limit register (effective only with a PTGT1 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

### REGISTER 25-2: CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2 OR 3) (CONTINUED)

| bit 7-6 | EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits                                                                                                                                                                                                      |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)</li> <li>10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)</li> </ul> |

|         | If CPOL = 1 (inverted polarity):<br>Low-to-high transition of the comparator output.                                                                                                                                                                          |

|         | If CPOL = 0 (non-inverted polarity):<br>High-to-low transition of the comparator output.                                                                                                                                                                      |