Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128gp206t-e-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

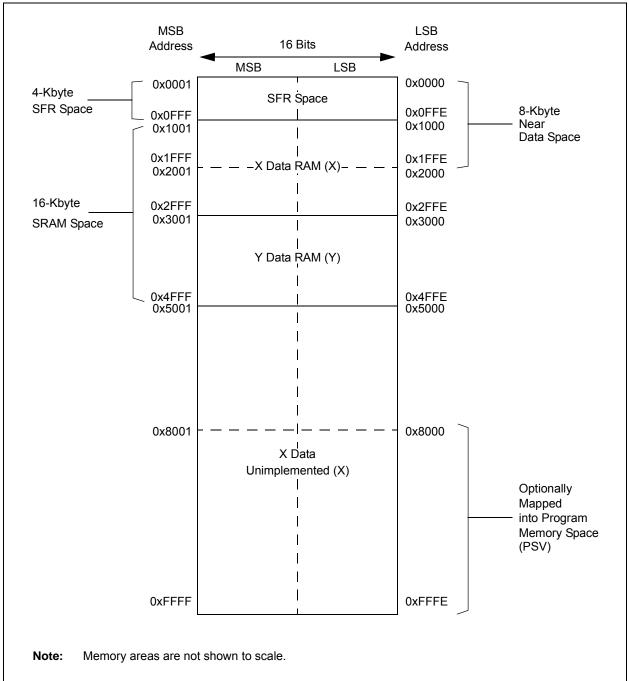

# FIGURE 4-9: DATA MEMORY MAP FOR dsPIC33EP128MC20X/50X AND dsPIC33EP128GP50X DEVICES

#### TABLE 4-46: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|---------|---------|---------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|---------------|

| TRISA        | 0E00  | _      | _      |        | TRISA12 | TRISA11 | TRISA10 | TRISA9 | TRISA8 | TRISA7 | _     |       | TRISA4 | _     |       | TRISA1 | TRISA0 | 1F93          |

| PORTA        | 0E02  | _      | _      | -      | RA12    | RA11    | RA10    | RA9    | RA8    | RA7    | _     |       | RA4    | _     | -     | RA1    | RA0    | 0000          |

| LATA         | 0E04  |        | _      | _      | LATA12  | LATA11  | LATA10  | LATA9  | LATA8  | LATA7  |       | _     | LATA4  |       | _     | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  |        | _      | _      | ODCA12  | ODCA11  | ODCA10  | ODCA9  | ODCA8  | ODCA7  |       | _     | ODCA4  |       | _     | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  |        | _      | _      | CNIEA12 | CNIEA11 | CNIEA10 | CNIEA9 | CNIEA8 | CNIEA7 |       | _     | CNIEA4 |       | _     | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  |        | _      | _      | CNPUA12 | CNPUA11 | CNPUA10 | CNPUA9 | CNPUA8 | CNPUA7 |       | _     | CNPUA4 |       | _     | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  |        | _      | _      | CNPDA12 | CNPDA11 | CNPDA10 | CNPDA9 | CNPDA8 | CNPDA7 |       | _     | CNPDA4 |       | _     | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | _      | _      | ANSA12  | ANSA11  |         | _      | -      | _      | _     | _     | ANSA4  | _     | _     | ANSA1  | ANSA0  | 1813          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-47: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | —       | _       | -       | _       | _      | ANSB8  | -      | _      | -      | -      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-48: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|--------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISC        | 0E20  | TRISC15 | _      | TRISC13 | TRISC12 | TRISC11 | TRISC10 | TRISC9 | TRISC8 | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | BFFF          |

| PORTC        | 0E22  | RC15    | _      | RC13    | RC12    | RC11    | RC10    | RC9    | RC8    | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xxxx          |

| LATC         | 0E24  | LATC15  | _      | LATC13  | LATC12  | LATC11  | LATC10  | LATC9  | LATC8  | LATC7  | LATC6  | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  | ODCC15  | -      | ODCC13  | ODCC12  | ODCC11  | ODCC10  | ODCC9  | ODCC8  | ODCC7  | ODCC6  | ODCC5  | ODCC4  | ODCC3  | ODCC2  | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | CNIEC15 | —      | CNIEC13 | CNIEC12 | CNIEC11 | CNIEC10 | CNIEC9 | CNIEC8 | CNIEC7 | CNIEC6 | CNIEC5 | CNIEC4 | CNIEC3 | CNIEC2 | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  | CNPUC15 | —      | CNPUC13 | CNPUC12 | CNPUC11 | CNPUC10 | CNPUC9 | CNPUC8 | CNPUC7 | CNPUC6 | CNPUC5 | CNPUC4 | CNPUC3 | CNPUC2 | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  | CNPDC15 | —      | CNPDC13 | CNPDC12 | CNPDC11 | CNPDC10 | CNPDC9 | CNPDC8 | CNPDC7 | CNPDC6 | CNPDC5 | CNPDC4 | CNPDC3 | CNPDC2 | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | _       | _      | _       | _       | ANSC11  | _       | _      | _      | _      | _      | _      | _      | _      | ANSC2  | ANSC1  | ANSC0  | 0807          |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

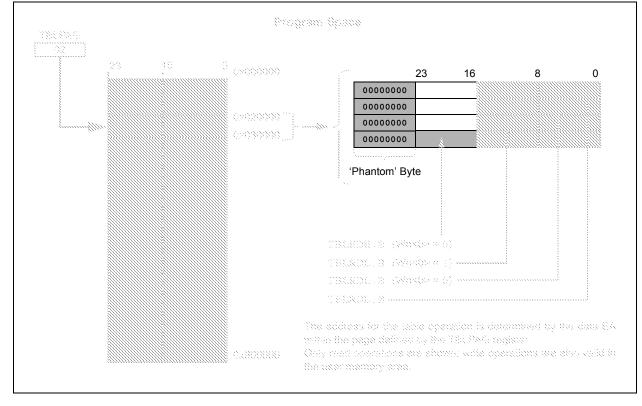

#### 4.8.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the Program Space without going through Data Space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a Program Space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit-wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from Program Space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the Program Space location (P<15:0>) to a data address (D<15:0>)

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>) is always '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a Program Space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user application and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

## FIGURE 4-23: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

## **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 4 Unimplemented: Read as '0'

- bit 3 **CF:** Clock Fail Detect bit<sup>(3)</sup>

- 1 = FSCM has detected clock failure

- 0 = FSCM has not detected clock failure

- bit 2-1 Unimplemented: Read as '0'

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Requests oscillator switch to selection specified by the NOSC<2:0> bits

- 0 = Oscillator switch is complete

- **Note 1:** Writes to this register require an unlock sequence. Refer to **"Oscillator"** (DS70580) in the *"dsPIC33/ PIC24 Family Reference Manual"* (available from the Microchip web site) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0      | U-0   | U-0   | U-0   | U-0       | U-0   | U-0   | U-0   |

|----------|-------|-------|-------|-----------|-------|-------|-------|

| —        | —     | —     | —     | —         | —     | —     | —     |

| bit 15   |       |       |       |           |       |       | bit 8 |

|          |       |       |       |           |       |       |       |

| U-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

| —        |       |       |       | SS2R<6:0> |       |       |       |

| bit 7    |       |       |       |           |       |       | bit 0 |

|          |       |       |       |           |       |       |       |

| l egend: |       |       |       |           |       |       |       |

#### REGISTER 11-13: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0  | <b>SS2R&lt;6:0&gt;:</b> Assign SPI2 Slave Select (SS2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111001 = Input tied to RPI121                                                                                                            |

|          |                                                                                                                                           |

|          | •                                                                                                                                         |

|          | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss                                                                               |

#### REGISTER 11-14: RPINR26: PERIPHERAL PIN SELECT INPUT REGISTER 26 (dsPIC33EPXXXGP/MC50X DEVICES ONLY)

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|------------|-------|-------|-------|

| _      | —     | —     | _     | _          | _     | —     | —     |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|        |       |       |       | C1RXR<6:0> | >     |       |       |

| bit 7  |       |       |       |            |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                              |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0  | <b>C1RXR&lt;6:0&gt;:</b> Assign CAN1 RX Input (CRX1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111001 = Input tied to RPI121                                                                                                          |

|          | •                                                                                                                                       |

|          |                                                                                                                                         |

|          | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss                                                                             |

## 13.0 TIMER2/3 AND TIMER4/5

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 operate in three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with all 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

- They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare Modules (Timer2 and Timer3 only)

- ADC1 Event Trigger (32-bit timer pairs, and Timer3 and Timer5 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, and T4CON, T5CON registers. T2CON and T4CON are shown in generic form in Register 13-1. T3CON and T5CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word (lsw); Timer3 and Timer5 are the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

A block diagram for an example 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 13-3.

**Note:** Only Timer2, 3, 4 and 5 can trigger a DMA data transfer.

#### 15.1 Output Compare Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 15.1.1 KEY RESOURCES

- "Output Compare" (DS70358) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0   | U-0              | U-0   | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

| —               | -     | —                | —     |                   | LEB             | <11:8>          |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | LEE   | 3<7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen      | nented bit, rea | id as '0'       |       |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

## REGISTER 16-17: LEBDLYx: PWMx LEADING-EDGE BLANKING DELAY REGISTER

bit 15-12 Unimplemented: Read as '0'

bit 11-0 LEB<11:0>: Leading-Edge Blanking Delay for Current-Limit and Fault Inputs bits

#### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4 | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Receiver is active                                                                                                                                                                                                           |

| bit 3 | <b>PERR:</b> Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character (character at the top of the receive FIFO) 0 = Parity error has not been detected                                                                                                  |

| bit 2 | <pre>FERR: Framing Error Status bit (read-only) 1 = Framing error has been detected for the current character (character at the top of the receive FIFO) 0 = Framing error has not been detected</pre>                                                                                           |

| bit 1 | <ul> <li>OERR: Receive Buffer Overrun Error Status bit (clear/read-only)</li> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 → 0 transition) resets the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | <ul> <li>URXDA: UARTx Receive Buffer Data Available bit (read-only)</li> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                |

**Note 1:** Refer to the "**UART**" (DS70582) section in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UARTx module for transmit operation.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                                                                                                                          | U-0                                                                                       | U-0              | U-0            | U-0                  | U-0    | U-0                | U-0    |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------|----------------|----------------------|--------|--------------------|--------|--|--|--|

| _                                                                                                                            | - – – – –                                                                                 |                  | —              | —                    | —      | —                  |        |  |  |  |

| bit 15                                                                                                                       |                                                                                           |                  |                |                      |        |                    | bit 8  |  |  |  |

|                                                                                                                              |                                                                                           |                  |                |                      |        |                    |        |  |  |  |

| U-0                                                                                                                          | U-0                                                                                       | U-0              | R-0            | R-0                  | R-0    | R-0                | R-0    |  |  |  |

| —                                                                                                                            | —                                                                                         | —                | DNCNT4         | DNCNT3               | DNCNT2 | DNCNT1             | DNCNT0 |  |  |  |

| bit 7                                                                                                                        |                                                                                           |                  |                |                      |        |                    | bit 0  |  |  |  |

|                                                                                                                              |                                                                                           |                  |                |                      |        |                    |        |  |  |  |

| Legend:                                                                                                                      |                                                                                           |                  |                |                      |        |                    |        |  |  |  |

| R = Readabl                                                                                                                  | e bit                                                                                     | W = Writable bit |                | U = Unimpler         | as '0' |                    |        |  |  |  |

| -n = Value at                                                                                                                | POR                                                                                       | '1' = Bit is set |                | '0' = Bit is cleared |        | x = Bit is unknown |        |  |  |  |

|                                                                                                                              |                                                                                           |                  |                |                      |        |                    |        |  |  |  |

| bit 15-5                                                                                                                     | Unimplemen                                                                                | ted: Read as '   | 0'             |                      |        |                    |        |  |  |  |

| bit 4-0                                                                                                                      | DNCNT<4:0>                                                                                | : DeviceNet™     | Filter Bit Num | iber bits            |        |                    |        |  |  |  |

|                                                                                                                              | 10010-11111 = Invalid selection<br>10001 = Compares up to Data Byte 3, bit 6 with EID<17> |                  |                |                      |        |                    |        |  |  |  |

|                                                                                                                              | •                                                                                         |                  |                |                      |        |                    |        |  |  |  |

|                                                                                                                              | •                                                                                         |                  |                |                      |        |                    |        |  |  |  |

|                                                                                                                              | •                                                                                         |                  |                |                      |        |                    |        |  |  |  |

| <ul> <li>00001 = Compares up to Data Byte 1, bit 7 with EID&lt;0&gt;</li> <li>00000 = Does not compare data bytes</li> </ul> |                                                                                           |                  |                |                      |        |                    |        |  |  |  |

NOTES:

| R/W-0         | R/W-0                                                                                       | R/W-0                                                                                                                                                                                  | R/W-0                                                                                                                                    | R/W-0                                                                                    | R/W-0                                 | R/W-0           | R/W-0 |

|---------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------|-----------------|-------|

| ITRIM5        | ITRIM4                                                                                      | ITRIM3                                                                                                                                                                                 | ITRIM2                                                                                                                                   | ITRIM1                                                                                   | ITRIM0                                | IRNG1           | IRNG0 |

| bit 15        |                                                                                             |                                                                                                                                                                                        |                                                                                                                                          |                                                                                          |                                       |                 | bit   |

|               |                                                                                             |                                                                                                                                                                                        |                                                                                                                                          |                                                                                          |                                       |                 |       |

| U-0           | U-0                                                                                         | U-0                                                                                                                                                                                    | U-0                                                                                                                                      | U-0                                                                                      | U-0                                   | U-0             | U-0   |

|               | <u> </u>                                                                                    | _                                                                                                                                                                                      | _                                                                                                                                        |                                                                                          | _                                     | _               | _     |

| bit 7         |                                                                                             |                                                                                                                                                                                        |                                                                                                                                          |                                                                                          |                                       |                 | bit   |

| Legend:       |                                                                                             |                                                                                                                                                                                        |                                                                                                                                          |                                                                                          |                                       |                 |       |

| R = Readabl   | e bit                                                                                       | W = Writable                                                                                                                                                                           | bit                                                                                                                                      | U = Unimplem                                                                             | nented bit, read                      | 1 as '0'        |       |

| -n = Value at | POR                                                                                         | '1' = Bit is set                                                                                                                                                                       |                                                                                                                                          | '0' = Bit is clea                                                                        |                                       | x = Bit is unkr | nown  |

|               |                                                                                             |                                                                                                                                                                                        |                                                                                                                                          |                                                                                          |                                       |                 |       |

|               | 011110 = Ma<br>•                                                                            |                                                                                                                                                                                        | e change nom                                                                                                                             |                                                                                          | 1 00 /0                               |                 |       |

|               | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | nimum positive<br>nimum positive<br>minal current c<br>nimum negative                                                                                                                  | change from r<br>change from r<br>output specified<br>e change from                                                                      | nominal current<br>nominal current<br>l by IRNG<1:0><br>nominal curren<br>nominal curren | + 4%<br>+ 2%<br>t – 2%                |                 |       |

|               | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                          | nimum positive<br>nimum positive<br>minal current o<br>nimum negative<br>nimum negative<br>ximum negative                                                                              | change from r<br>change from r<br>output specified<br>e change from<br>e change from<br>re change from                                   | nominal current<br>nominal current<br>l by IRNG<1:0><br>nominal curren                   | + 4%<br>+ 2%<br>-<br>t – 2%<br>t – 4% |                 |       |

| bit 9-8       | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                          | nimum positive<br>nimum positive<br>minal current o<br>nimum negative<br>nimum negative<br>ximum negative<br>current Source<br>ase Current <sup>(2)</sup><br>se Current <sup>(2)</sup> | change from r<br>change from r<br>output specified<br>e change from<br>e change from<br>re change from<br>re change from<br>Range Select | nominal current<br>nominal current<br>l by IRNG<1:0><br>nominal curren<br>nominal curren | + 4%<br>+ 2%<br>-<br>t – 2%<br>t – 4% |                 |       |

#### REGISTER 22-3: CTMUICON: CTMU CURRENT CONTROL REGISTER

2: Refer to the CTMU Current Source Specifications (Table 30-56) in Section 30.0 "Electrical Characteristics" for the current range selection values.

#### 25.3 Op Amp/Comparator Registers

| R/W-0         | U-0                                                                 | U-0                                                 | U-0                          | R-0                     | R-0                  | R-0                  | R-0                  |  |  |  |

|---------------|---------------------------------------------------------------------|-----------------------------------------------------|------------------------------|-------------------------|----------------------|----------------------|----------------------|--|--|--|

| PSIDL         |                                                                     | _                                                   | _                            | C4EVT <sup>(1)</sup>    | C3EVT <sup>(1)</sup> | C2EVT <sup>(1)</sup> | C1EVT <sup>(1)</sup> |  |  |  |

| bit 15        |                                                                     |                                                     | •                            |                         |                      |                      | bit                  |  |  |  |

|               |                                                                     |                                                     |                              |                         |                      |                      |                      |  |  |  |

| U-0           | U-0                                                                 | U-0                                                 | U-0                          | R-0                     | R-0                  | R-0                  | R-0                  |  |  |  |

| _             | —                                                                   | _                                                   | _                            | C4OUT <sup>(2)</sup>    | C3OUT <sup>(2)</sup> | C2OUT <sup>(2)</sup> | C10UT <sup>(2)</sup> |  |  |  |

| bit 7         |                                                                     |                                                     |                              |                         |                      |                      | bit                  |  |  |  |

|               |                                                                     |                                                     |                              |                         |                      |                      |                      |  |  |  |

| Legend:       | - 1-14                                                              |                                                     | L:4                          |                         |                      |                      |                      |  |  |  |

| R = Readabl   |                                                                     | W = Writable                                        |                              | -                       | nented bit, read     |                      |                      |  |  |  |

| -n = Value at | PUR                                                                 | '1' = Bit is se                                     | [                            | '0' = Bit is clea       | ared                 | x = Bit is unkr      | IOWN                 |  |  |  |

| bit 15        | PSIDI · Comr                                                        | parator Stop in                                     | Idle Mode hit                |                         |                      |                      |                      |  |  |  |

|               |                                                                     |                                                     |                              | ators when devi         | ce enters Idle n     | node                 |                      |  |  |  |

|               |                                                                     |                                                     |                              | rs in Idle mode         |                      |                      |                      |  |  |  |

| bit 14-12     | Unimplemen                                                          | ted: Read as                                        | 0'                           |                         |                      |                      |                      |  |  |  |

| bit 11        | <b>C4EVT:</b> Op A                                                  | mp/Comparate                                        | or 4 Event Sta               | atus bit <sup>(1)</sup> |                      |                      |                      |  |  |  |

|               |                                                                     | comparator eve                                      |                              |                         |                      |                      |                      |  |  |  |

|               |                                                                     | comparator eve                                      |                              |                         |                      |                      |                      |  |  |  |

| bit 10        |                                                                     | C3EVT: Comparator 3 Event Status bit <sup>(1)</sup> |                              |                         |                      |                      |                      |  |  |  |

|               | 1 = Comparator event occurred<br>0 = Comparator event did not occur |                                                     |                              |                         |                      |                      |                      |  |  |  |

| bit 9         | •                                                                   | parator 2 Ever                                      |                              |                         |                      |                      |                      |  |  |  |

|               |                                                                     | = Comparator event occurred                         |                              |                         |                      |                      |                      |  |  |  |

|               | •                                                                   | tor event did n                                     |                              |                         |                      |                      |                      |  |  |  |

| bit 8         |                                                                     | parator 1 Ever                                      |                              |                         |                      |                      |                      |  |  |  |

|               |                                                                     | tor event occu<br>tor event did n                   |                              |                         |                      |                      |                      |  |  |  |

| bit 7-4       |                                                                     | ited: Read as                                       |                              |                         |                      |                      |                      |  |  |  |

| bit 3         | -                                                                   | parator 4 Outp                                      |                              | 2)                      |                      |                      |                      |  |  |  |

|               | When CPOL                                                           |                                                     |                              |                         |                      |                      |                      |  |  |  |

|               | 1 = VIN + > VII                                                     | N-                                                  |                              |                         |                      |                      |                      |  |  |  |

|               | 0 = VIN + < VII                                                     |                                                     |                              |                         |                      |                      |                      |  |  |  |

|               | $\frac{\text{When CPOL} = 1:}{1 = \text{VIN+} < \text{VIN-}}$       |                                                     |                              |                         |                      |                      |                      |  |  |  |

|               | 0 = VIN + > VII                                                     |                                                     |                              |                         |                      |                      |                      |  |  |  |

| bit 2         | C3OUT: Com                                                          | parator 3 Outp                                      | out Status bit <sup>(;</sup> | 2)                      |                      |                      |                      |  |  |  |

|               | When CPOL                                                           |                                                     |                              |                         |                      |                      |                      |  |  |  |

|               | 1 = VIN+ > VII<br>0 = VIN+ < VII                                    |                                                     |                              |                         |                      |                      |                      |  |  |  |

|               | 0 = VIN + < VII<br>When CPOL                                        |                                                     |                              |                         |                      |                      |                      |  |  |  |

|               | 1 = VIN + < VII                                                     |                                                     |                              |                         |                      |                      |                      |  |  |  |

|               | $\perp = VIN + < VII$                                               | N-                                                  |                              |                         |                      |                      |                      |  |  |  |

#### REGISTER 25-1: CMSTAT: OP AMP/COMPARATOR STATUS REGISTER

- **Note 1:** Reflects the value of the of the CEVT bit in the respective Op Amp/Comparator Control register, CMxCON<9>.

- 2: Reflects the value of the COUT bit in the respective Op Amp/Comparator Control register, CMxCON<8>.

#### REGISTER 25-3: CM4CON: COMPARATOR 4 CONTROL REGISTER (CONTINUED)

- bit 5 Unimplemented: Read as '0'

- bit 4 **CREF:** Comparator Reference Select bit (VIN+ input)<sup>(1)</sup>

- 1 = VIN+ input connects to internal CVREFIN voltage

- 0 = VIN+ input connects to C4IN1+ pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Channel Select bits<sup>(1)</sup>

- 11 = VIN- input of comparator connects to OA3/AN6

- 10 = VIN- input of comparator connects to OA2/AN0

- 01 = VIN- input of comparator connects to OA1/AN3

- 00 = VIN- input of comparator connects to C4IN1-

- Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

| DC CHARACTERISTICS |        |                                                     | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extende |    |      |      |                                                                |  |

|--------------------|--------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|------|----------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                      | Min.     Typ. <sup>(1)</sup> Max.     Units     Conditions                                                                                                                                          |    |      |      |                                                                |  |

|                    |        | Program Flash Memory                                |                                                                                                                                                                                                     |    |      |      |                                                                |  |

| D130               | Eр     | Cell Endurance                                      | 10,000                                                                                                                                                                                              | —  | _    | E/W  | -40°C to +125°C                                                |  |

| D131               | Vpr    | VDD for Read                                        | 3.0                                                                                                                                                                                                 | —  | 3.6  | V    |                                                                |  |

| D132b              | VPEW   | VDD for Self-Timed Write                            | 3.0                                                                                                                                                                                                 | —  | 3.6  | V    |                                                                |  |

| D134               | TRETD  | Characteristic Retention                            | 20                                                                                                                                                                                                  | _  |      | Year | Provided no other specifications are violated, -40°C to +125°C |  |

| D135               | IDDP   | Supply Current during<br>Programming <sup>(2)</sup> | —                                                                                                                                                                                                   | 10 |      | mA   |                                                                |  |

| D136               | IPEAK  | Instantaneous Peak Current<br>During Start-up       | —                                                                                                                                                                                                   | —  | 150  | mA   |                                                                |  |

| D137a              | Тре    | Page Erase Time                                     | 17.7                                                                                                                                                                                                | —  | 22.9 | ms   | TPE = 146893 FRC cycles,<br>TA = +85°C (See <b>Note 3)</b>     |  |

| D137b              | Тре    | Page Erase Time                                     | 17.5                                                                                                                                                                                                | —  | 23.1 | ms   | TPE = 146893 FRC cycles,<br>TA = +125°C (See <b>Note 3)</b>    |  |

| D138a              | Tww    | Word Write Cycle Time                               | 41.7                                                                                                                                                                                                | —  | 53.8 | μs   | Tww = 346 FRC cycles,<br>TA = +85°C (See <b>Note 3)</b>        |  |

| D138b              | Tww    | Word Write Cycle Time                               | 41.2                                                                                                                                                                                                | —  | 54.4 | μs   | Tww = 346 FRC cycles,<br>TA = +125°C (See <b>Note 3)</b>       |  |

#### TABLE 30-14: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

2: Parameter characterized but not tested in manufacturing.

3: Other conditions: FRC = 7.37 MHz, TUN<5:0> = 011111 (for Minimum), TUN<5:0> = 100000 (for Maximum). This parameter depends on the FRC accuracy (see Table 30-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). For complete details on calculating the Minimum and Maximum time, see Section 5.3 "Programming Operations".

| AC CHARACTERISTICS (unless other |                                          |                                             |                                            | d Operating Conditions: 3.0V to 3.6V<br>otherwise stated)<br>g temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |     |     |  |  |

|----------------------------------|------------------------------------------|---------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--|--|

| Maximum<br>Data Rate             | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex) | CKE                                                                                                                                                                                      | СКР | SMP |  |  |

| 15 MHz                           | Table 30-33                              | _                                           | _                                          | 0,1                                                                                                                                                                                      | 0,1 | 0,1 |  |  |

| 9 MHz                            | _                                        | Table 30-34                                 | —                                          | 1                                                                                                                                                                                        | 0,1 | 1   |  |  |

| 9 MHz                            | —                                        | Table 30-35                                 | —                                          | 0                                                                                                                                                                                        | 0,1 | 1   |  |  |

| 15 MHz                           | —                                        | —                                           | Table 30-36                                | 1                                                                                                                                                                                        | 0   | 0   |  |  |

| 11 MHz                           | —                                        | —                                           | Table 30-37                                | 1                                                                                                                                                                                        | 1   | 0   |  |  |

| 15 MHz                           | _                                        | —                                           | Table 30-38                                | 0                                                                                                                                                                                        | 1   | 0   |  |  |

| 11 MHz                           | _                                        | —                                           | Table 30-39                                | 0                                                                                                                                                                                        | 0   | 0   |  |  |

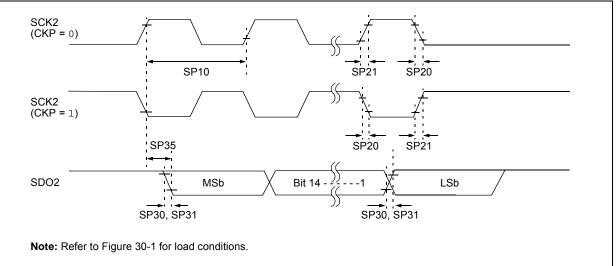

#### TABLE 30-33: SPI2 MAXIMUM DATA/CLOCK RATE SUMMARY

#### FIGURE 30-14: SPI2 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

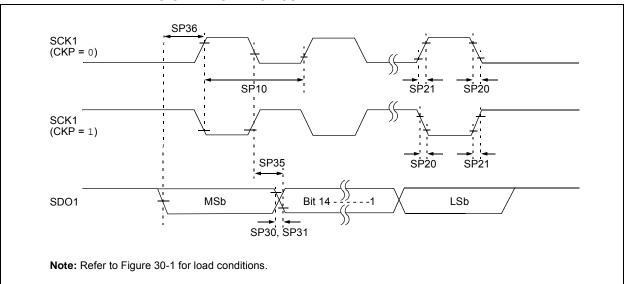

#### FIGURE 30-23: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 1) TIMING CHARACTERISTICS

#### TABLE 30-42: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| AC CHA | RACTERIST             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |            |                                |

|--------|-----------------------|-------------------------------------------------------|---------------------|------|-------|------------|--------------------------------|

| Param. | Symbol                | Min.                                                  | Typ. <sup>(2)</sup> | Max. | Units | Conditions |                                |

| SP10   | FscP                  | Maximum SCK1 Frequency                                | —                   |      | 15    | MHz        | (Note 3)                       |

| SP20   | TscF                  | SCK1 Output Fall Time                                 | -                   | _    | _     | ns         | See Parameter DO32<br>(Note 4) |

| SP21   | TscR                  | SCK1 Output Rise Time                                 | —                   | —    | _     | ns         | See Parameter DO31 (Note 4)    |

| SP30   | TdoF                  | SDO1 Data Output Fall Time                            | -                   | _    | _     | ns         | See Parameter DO32<br>(Note 4) |

| SP31   | TdoR                  | SDO1 Data Output Rise Time                            | —                   | —    | _     | ns         | See Parameter DO31 (Note 4)    |

| SP35   | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge             | —                   | 6    | 20    | ns         |                                |

| SP36   | TdiV2scH,<br>TdiV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge          | 30                  |      |       | ns         |                                |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

## 31.0 HIGH-TEMPERATURE ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X electrical characteristics for devices operating in an ambient temperature range of -40°C to +150°C.

The specifications between  $-40^{\circ}$ C to  $+150^{\circ}$ C are identical to those shown in **Section 30.0** "**Electrical Characteristics**" for operation between  $-40^{\circ}$ C to  $+125^{\circ}$ C, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, Parameter DC10 in **Section 30.0 "Electrical Characteristics"** is the Industrial and Extended temperature equivalent of HDC10.

Absolute maximum ratings for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X high-temperature devices are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias <sup>(2)</sup>                                     | 40°C to +150°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +160°C       |

| Voltage on VDD with respect to Vss                                                | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(3)</sup>     | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(3)</sup> | 0.3V to 3.6V         |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(3)}$      | 0.3V to 5.5V         |

| Maximum current out of Vss pin                                                    | 60 mA                |

| Maximum current into Vod pin <sup>(4)</sup>                                       | 60 mA                |

| Maximum junction temperature                                                      | +155°C               |

| Maximum current sourced/sunk by any 4x I/O pin                                    | 10 mA                |

| Maximum current sourced/sunk by any 8x I/O pin                                    | 15 mA                |

| Maximum current sunk by all ports combined                                        | 70 mA                |

| Maximum current sourced by all ports combined <sup>(4)</sup>                      | 70 mA                |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

- 2: AEC-Q100 reliability testing for devices intended to operate at +150°C is 1,000 hours. Any design in which the total operating time from +125°C to +150°C will be greater than 1,000 hours is not warranted without prior written approval from Microchip Technology Inc.

- 3: Refer to the "Pin Diagrams" section for 5V tolerant pins.

- 4: Maximum allowable current is a function of device maximum power dissipation (see Table 31-2).

# 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL A

|                         | Units  | N              | <b>IILLIMETER</b> | S     |  |

|-------------------------|--------|----------------|-------------------|-------|--|

| Dimension               | Limits | MIN            | NOM               | MAX   |  |

| Number of Pins          | Ν      |                | 44                |       |  |

| Number of Pins per Side | ND     |                | 12                |       |  |

| Number of Pins per Side | NE     |                | 10                |       |  |

| Pitch                   | е      | 0.50 BSC       |                   |       |  |

| Overall Height          | Α      | 0.80           | 0.90              | 1.00  |  |

| Standoff                | A1     | 0.025          | -                 | 0.075 |  |

| Overall Width           | Е      |                | 6.00 BSC          |       |  |

| Exposed Pad Width       | E2     | 4.40 4.55 4.70 |                   |       |  |

| Overall Length          | D      | 6.00 BSC       |                   |       |  |

| Exposed Pad Length      | D2     | 4.40           | 4.55              | 4.70  |  |

| Contact Width           | b      | 0.20           | 0.25              | 0.30  |  |

| Contact Length          | L      | 0.20           | 0.25              | 0.30  |  |

| Contact-to-Exposed Pad  | К      | 0.20           | -                 | -     |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-157C Sheet 2 of 2

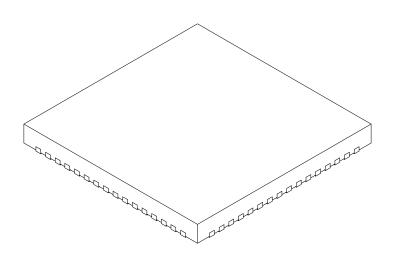

## 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |          |          |      |  |

|------------------------|-------------|----------|----------|------|--|

| Dimension              | MIN         | NOM      | MAX      |      |  |

| Number of Pins         | N           |          | 64       |      |  |

| Pitch                  | е           |          | 0.50 BSC |      |  |

| Overall Height         | A           | 0.80     | 0.90     | 1.00 |  |

| Standoff               | A1          | 0.00     | 0.02     | 0.05 |  |

| Contact Thickness      | A3          | 0.20 REF |          |      |  |

| Overall Width          | E           | 9.00 BSC |          |      |  |

| Exposed Pad Width      | E2          | 5.30     | 5.40     | 5.50 |  |

| Overall Length         | D           |          | 9.00 BSC |      |  |

| Exposed Pad Length     | D2          | 5.30     | 5.40     | 5.50 |  |

| Contact Width          | b           | 0.20     | 0.25     | 0.30 |  |

| Contact Length         | L           | 0.30     | 0.40     | 0.50 |  |

| Contact-to-Exposed Pad | K           | 0.20     | -        | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-154A Sheet 2 of 2