Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Betuns                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 8K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128mc202-e-mm |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.4 Special Function Register Maps

## TABLE 4-1: CPU CORE REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND dsPIC33EPXXXGP50X DEVICES ONLY

|           |       | 0.00   |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              | 011 401    |        |       | 20/00/      |        |       |        |         |          |          | -     | r     |               |

|-----------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------|------------|--------|-------|-------------|--------|-------|--------|---------|----------|----------|-------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Bit 13 | Bit 12       | Bit 11     | Bit 10 | Bit 9 | Bit 8       | Bit 7  | Bit 6 | Bit 5  | Bit 4   | Bit 3    | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

| W0        | 0000  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        |       | W0 (WR      | EG)    |       |        |         |          |          |       |       | xxxx          |

| W1        | 0002  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        |       | W1          |        |       |        |         |          |          |       |       | xxxx          |

| W2        | 0004  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        |       | W2          |        |       |        |         |          |          |       |       | xxxx          |

| W3        | 0006  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        |       | W3          |        |       |        |         |          |          |       |       | xxxx          |

| W4        | 8000  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        |       | W4          |        |       |        |         |          |          |       |       | xxxx          |

| W5        | 000A  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        |       | W5          |        |       |        |         |          |          |       |       | xxxx          |

| W6        | 000C  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        |       | W6          |        |       |        |         |          |          |       |       | xxxx          |

| W7        | 000E  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        |       | W7          |        |       |        |         |          |          |       |       | xxxx          |

| W8        | 0010  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        |       | W8          |        |       |        |         |          |          |       |       | xxxx          |

| W9        | 0012  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        |       | W9          |        |       |        |         |          |          |       |       | xxxx          |

| W10       | 0014  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        |       | W10         |        |       |        |         |          |          |       |       | xxxx          |

| W11       | 0016  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        |       | W11         |        |       |        |         |          |          |       |       | xxxx          |

| W12       | 0018  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        |       | W12         |        |       |        |         |          |          |       |       | xxxx          |

| W13       | 001A  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        |       | W13         |        |       |        |         |          |          |       |       | xxxx          |

| W14       | 001C  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        |       | W14         |        |       |        |         |          |          |       |       | xxxx          |

| W15       | 001E  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        |       | W15         |        |       |        |         |          |          |       |       | xxxx          |

| SPLIM     | 0020  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        |       | SPLI        | N      |       |        |         |          |          |       |       | 0000          |

| ACCAL     | 0022  |        | W11       XXX         W12       XXX         W13       XXX         W14       XXX         W15       XXX         SPLIM       000         ACCAL       000         Sign Extension of ACCA<39>       ACCAL       000         ACCBL       000       000 |        |              |            |        |       |             |        |       |        | 0000    |          |          |       |       |               |

| ACCAH     | 0024  |        | W10XXXW11XXXW12XXXW13XXXW14XXXW15XXXSPLIM000ACCAL000ACCAH000ACCBL000ACCBH000ACCBH000ACCBH000ACCBH000ACCBH000ACCBH000ACCBH000ACCBH000ACCBH000ACCBH000ACCBH000ACCBH000ACCBH000ACCBH000                                                                                                                                                                                                                                                                         |        |              |            |        |       |             |        |       |        | 0000    |          |          |       |       |               |

| ACCAU     | 0026  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Si     | gn Extensior | n of ACCA< | 39>    |       |             |        |       |        | ACO     | CAU      |          |       |       | 0000          |

| ACCBL     | 0028  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        |       | ACCB        | L      |       |        |         |          |          |       |       | 0000          |

| ACCBH     | 002A  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        |       | ACCB        | Н      |       |        |         |          |          |       |       | 0000          |

| ACCBU     | 002C  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Si     | gn Extensior | n of ACCB< | 39>    |       |             |        |       |        | ACO     | CBU      |          |       |       | 0000          |

| PCL       | 002E  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        | F     | PCL<15:0>   |        |       |        |         |          |          |       | —     | 0000          |

| PCH       | 0030  | _      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _      | —            | _          | _      | —     | _           | _      |       |        |         | PCH<6:0> |          |       |       | 0000          |

| DSRPAG    | 0032  | _      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _      | —            | _          | _      |       |             |        |       | DSRPAC | 6<9:0>  |          |          |       |       | 0001          |

| DSWPAG    | 0034  | _      |                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _      | —            |            | _      | _     |             |        |       | DS     | WPAG<8: | 0>       |          |       |       | 0001          |

| RCOUNT    | 0036  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        |       | RCOUNT<     | :15:0> |       |        |         |          |          |       |       | 0000          |

| DCOUNT    | 0038  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        |       | DCOUNT<     | :15:0> |       |        |         |          |          |       |       | 0000          |

| DOSTARTL  | 003A  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        | DOS   | STARTL<15:1 | >      |       |        |         |          |          |       |       | 0000          |

| DOSTARTH  | 003C  | _      | —                                                                                                                                                                                                                                                                                                                                                                                                                                                            | —      | _            | —          | —      | —     | _           | _      | —     |        |         | DOSTAF   | RTH<5:0> |       |       | 0000          |

| DOENDL    | 003E  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        | DO    | ENDL<15:1>  | >      |       |        |         |          |          |       |       | 0000          |

| DOENDH    | 0040  | _      | —                                                                                                                                                                                                                                                                                                                                                                                                                                                            | —      | —            | —          | —      | _     | —           | —      | —     |        |         | DOEND    | )H<5:0>  |       |       | 0000          |

|           |       |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |              |            |        |       |             |        |       |        |         |          |          |       |       |               |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

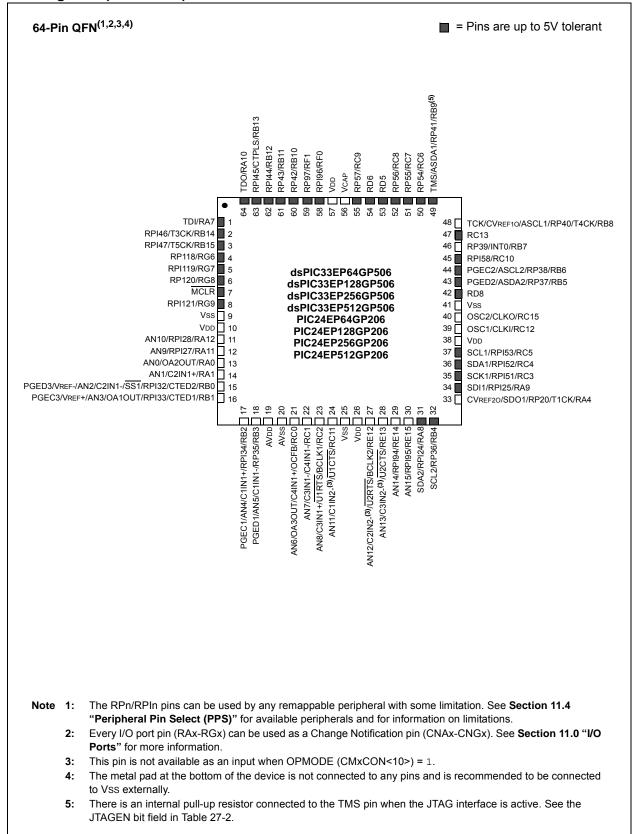

#### EXAMPLE 4-2: EXTENDED DATA SPACE (EDS) WRITE ADDRESS GENERATION

The paged memory scheme provides access to multiple 32-Kbyte windows in the EDS and PSV memory. The Data Space Page registers, DSxPAG, in combination with the upper half of the Data Space address, can provide up to 16 Mbytes of additional address space in the EDS and 8 Mbytes (DSRPAG only) of PSV address space. The paged data memory space is shown in Example 4-3.

The Program Space (PS) can be accessed with a DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG. Writes to PS are not supported, so DSWPAG is dedicated to DS, including EDS only. The Data Space and EDS can be read from, and written to, using DSRPAG and DSWPAG, respectively.

| R/W-0         | U-0                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| ROON          |                                                                                                                                                                                                                                              | ROSSLP                                                                                                                                                                                                                                                                                                                                                                                                   | ROSEL                                                                                                                                                                                                                 | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |

| bit 15        |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       | •                     | bit                   |

| U-0           | U-0                                                                                                                                                                                                                                          | U-0                                                                                                                                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                                                                                                   | U-0                   | U-0                   | U-0                   | U-0                   |

|               | _                                                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                       | _                     |                       | _                     |                       |

| bit 7         |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       |                       | bit                   |

| Legend:       |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       |                       |                       |

| R = Readable  | e bit                                                                                                                                                                                                                                        | W = Writable                                                                                                                                                                                                                                                                                                                                                                                             | bit                                                                                                                                                                                                                   | U = Unimpler          | nented bit, read      | l as '0'              |                       |

| -n = Value at |                                                                                                                                                                                                                                              | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                       | '0' = Bit is cle      |                       | x = Bit is unkr       | iown                  |

| bit 14        | 0 = Reference                                                                                                                                                                                                                                | e oscillator outp<br>e oscillator outp<br>i <b>ted:</b> Read as '                                                                                                                                                                                                                                                                                                                                        | out is disabled                                                                                                                                                                                                       |                       | .K pin <sup>(2)</sup> |                       |                       |

| bit 13        | -                                                                                                                                                                                                                                            | ference Oscilla                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       | en hit                |                       |                       |                       |

|               | 1 = Reference                                                                                                                                                                                                                                | e oscillator out<br>e oscillator out                                                                                                                                                                                                                                                                                                                                                                     | out continues                                                                                                                                                                                                         | to run in Sleep       |                       |                       |                       |

| bit 12        | 1 = Oscillator                                                                                                                                                                                                                               | erence Oscillato<br>crystal is used<br>lock is used as                                                                                                                                                                                                                                                                                                                                                   | as the refere                                                                                                                                                                                                         | nce clock             |                       |                       |                       |

| bit 11-8      | 1111 = Refer<br>1110 = Refer<br>1101 = Refer<br>1000 = Refer<br>1011 = Refer<br>1001 = Refer<br>1000 = Refer<br>0111 = Refer<br>0111 = Refer<br>0101 = Refer<br>0100 = Refer<br>0101 = Refer<br>0011 = Refer<br>0011 = Refer<br>0011 = Refer | Reference Os<br>rence clock divi<br>rence clock divi | ded by 32,763<br>ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048<br>ded by 1,024<br>ded by 512<br>ded by 512<br>ded by 256<br>ded by 128<br>ded by 64<br>ded by 32<br>ded by 16<br>ded by 8<br>ded by 4 | 8                     |                       |                       |                       |

|               | 0000 = Refer                                                                                                                                                                                                                                 | ence clock                                                                                                                                                                                                                                                                                                                                                                                               | -                                                                                                                                                                                                                     |                       |                       |                       |                       |

#### REGISTER 9-5: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

#### REGISTER 11-9: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|--------------|--------------|--------------------------------------------------------|---------------|------------------|-----------------|-----------------|--------|

| _            |              |                                                        |               | HOME1R<6:0       | >               |                 |        |

| bit 15       |              |                                                        |               |                  |                 |                 | bit 8  |

|              |              | <b>D</b> # 4 4 0                                       | 54446         | 5444.0           | 5444.0          | -               | 5444.6 |

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|              |              |                                                        |               | INDX1R<6:0>      | >               |                 |        |

| bit 7        |              |                                                        |               |                  |                 |                 | bit C  |

| Legend:      |              |                                                        |               |                  |                 |                 |        |

| R = Readab   | le bit       | W = Writable                                           | bit           | U = Unimplen     | nented bit, rea | ad as '0'       |        |

| -n = Value a | t POR        | '1' = Bit is set                                       |               | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |

|              |              | nput tied to RPI                                       |               |                  |                 |                 |        |

|              |              | nput tied to CM<br>nput tied to Vss                    |               |                  |                 |                 |        |

| bit 7        |              | nted: Read as '                                        |               |                  |                 |                 |        |

| bit 6-0      | (see Table 1 | : Assign QEI1<br>1-2 for input pin<br>nput tied to RPI | selection nun | ,                | responding RI   | Pn Pin bits     |        |

|              |              | nput tied to CM                                        |               |                  |                 |                 |        |

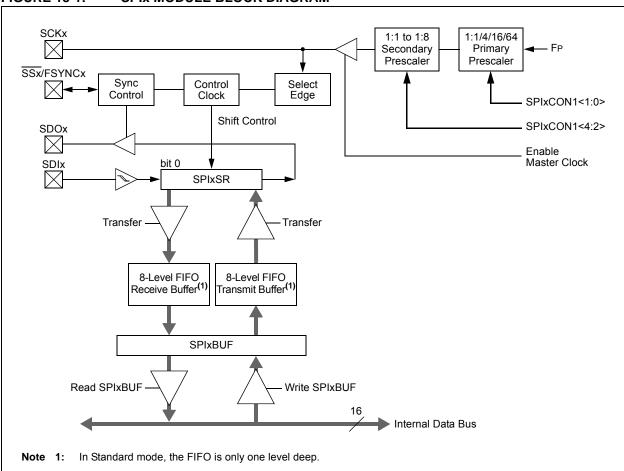

#### FIGURE 18-1: SPIX MODULE BLOCK DIAGRAM

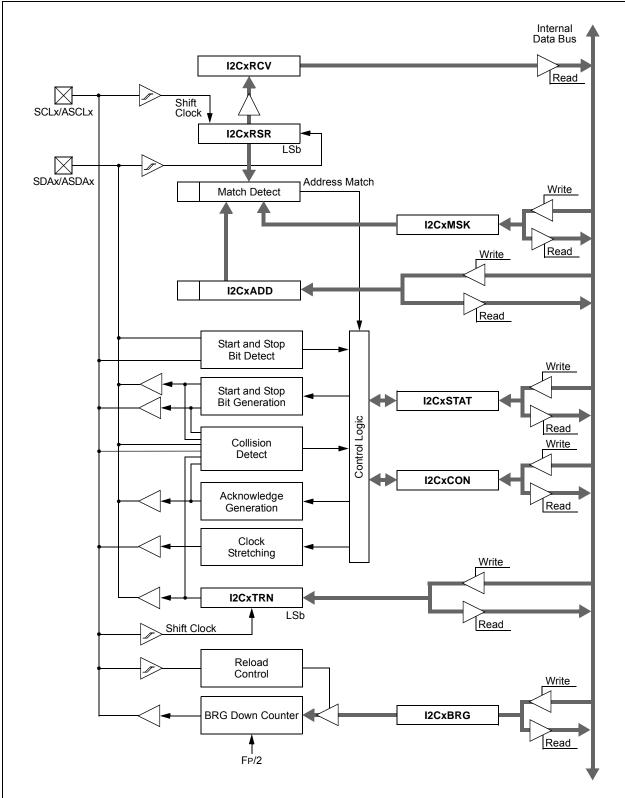

FIGURE 19-1: I2Cx BLOCK DIAGRAM (X = 1 OR 2)

# **19.2** I<sup>2</sup>C Control Registers

#### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER

| R/W-0        | U-0                          | R/W-0                                  | R/W-1, HC                  | R/W-0                        | R/W-0            | R/W-0           | R/W-0          |

|--------------|------------------------------|----------------------------------------|----------------------------|------------------------------|------------------|-----------------|----------------|

| I2CEN        | _                            | I2CSIDL                                | SCLREL                     | IPMIEN <sup>(1)</sup>        | A10M             | DISSLW          | SMEN           |

| bit 15       |                              |                                        |                            |                              |                  |                 | bit 8          |

|              |                              |                                        |                            |                              |                  |                 |                |

| R/W-0        | R/W-0                        | R/W-0                                  | R/W-0, HC                  | R/W-0, HC                    | R/W-0, HC        | R/W-0, HC       | R/W-0, HC      |

| GCEN         | STREN                        | ACKDT                                  | ACKEN                      | RCEN                         | PEN              | RSEN            | SEN            |

| bit 7        |                              |                                        |                            |                              |                  |                 | bit 0          |

| Legend:      |                              | HC = Hardware                          | Cloarable bit              |                              |                  |                 |                |

| R = Readab   | le hit                       | W = Writable bi                        |                            | II = I Inimpler              | mented bit, rea  | d as '0'        |                |

| -n = Value a |                              | '1' = Bit is set                       | L .                        | '0' = Bit is cle             |                  | x = Bit is unk  | nown           |

|              |                              |                                        |                            |                              |                  |                 | nown           |

| bit 15       | <b>12CEN:</b> 12Cx           | Enable bit                             |                            |                              |                  |                 |                |

|              |                              | he I2Cx module                         |                            |                              |                  |                 | ;              |

|              | 0 = Disables                 | the I2Cx module;                       | all l <sup>2</sup> C™ pins | are controlled               | by port functior | ıs              |                |

| bit 14       | Unimplemen                   | ted: Read as '0'                       |                            |                              |                  |                 |                |

| bit 13       |                              | x Stop in Idle Mo                      |                            |                              |                  |                 |                |

|              |                              | ues module oper<br>s module operation  |                            |                              | dle mode         |                 |                |

| bit 12       |                              | Lx Release Conf                        |                            | _                            | ( clave)         |                 |                |

|              | 1 = Releases                 |                                        |                            |                              | slave)           |                 |                |

|              |                              | Lx clock low (clo                      | ck stretch)                |                              |                  |                 |                |

|              | If STREN = 1                 | <u>:</u>                               | -                          |                              |                  |                 |                |

|              | •                            | ., software can w                      |                            |                              |                  | ,               |                |

|              |                              | ing of every slav<br>reception. Hardw  |                            |                              |                  |                 | t every slave  |

|              | If STREN = 0                 | -                                      |                            |                              |                  |                 |                |

|              |                              | <u>.</u><br>, software can or          | nly write '1' to re        | elease clock). I             | Hardware is cle  | ar at the begir | ning of every  |

|              | -                            | te transmission.                       |                            |                              | -                | address byte re | eception.      |

| bit 11       |                              | ligent Peripheral                      |                            |                              |                  |                 |                |

|              | 1 = IPMI mod<br>0 = IPMI mod | e is enabled; all                      | addresses are              | Acknowledged                 | 1                |                 |                |

| bit 10       |                              | Slave Address b                        | i+                         |                              |                  |                 |                |

|              |                              | is a 10-bit slave                      |                            |                              |                  |                 |                |

|              |                              | is a 7-bit slave a                     |                            |                              |                  |                 |                |

| bit 9        | DISSLW: Dis                  | able Slew Rate C                       | Control bit                |                              |                  |                 |                |

|              |                              | control is disable                     |                            |                              |                  |                 |                |

|              |                              | control is enable                      |                            |                              |                  |                 |                |

| bit 8        |                              | us Input Levels b                      |                            | 0145                         | <b>c</b>         |                 |                |

|              |                              | /O pin thresholds<br>SMBus input thre  |                            | n SMBus speci                | fication         |                 |                |

| bit 7        |                              | ral Call Enable b                      |                            | ing as I <sup>2</sup> C slav | /e)              |                 |                |

|              | 1 = Enables in               | terrupt when a ge<br>all address disat | neral call addre           | -                            |                  | dule is enabled | for reception) |

|              |                              |                                        |                            |                              |                  |                 |                |

Note 1: When performing master operations, ensure that the IPMIEN bit is set to '0'.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 21-22: CxRXFUL1: ECANx RECEIVE BUFFER FULL REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9 | RXFUL8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXFUL7 | RXFUL6 | RXFUL5 | RXFUL4 | RXFUL3 | RXFUL2 | RXFUL1 | RXFUL0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           | C = Writable bit, but on | ly '0' can be written to clear t | he bit             |

|-------------------|--------------------------|----------------------------------|--------------------|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit            | , read as '0'      |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared             | x = Bit is unknown |

bit 15-0 **RXFUL<15:0>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

#### REGISTER 21-23: CxRXFUL2: ECANx RECEIVE BUFFER FULL REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL31 | RXFUL30 | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL23 | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writable bit, but only ' | C = Writable bit, but only '0' can be written to clear the bit |                    |  |  |  |  |

|-------------------|------------------------------|----------------------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit             | U = Unimplemented bit, rea                                     | ad as '0'          |  |  |  |  |

| -n = Value at POR | '1' = Bit is set             | '0' = Bit is cleared                                           | x = Bit is unknown |  |  |  |  |

bit 15-0 **RXFUL<31:16>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

| R/W-0         | R/W-0                                  | R/W-0                                 | R/W-0            | R/W-0              | R/W-0           | R/W-0           | R/W-0    |

|---------------|----------------------------------------|---------------------------------------|------------------|--------------------|-----------------|-----------------|----------|

| EDG1MOD       | EDG1POL                                | EDG1SEL3                              | EDG1SEL2         | EDG1SEL1           | EDG1SEL0        | EDG2STAT        | EDG1STAT |

| bit 15        |                                        | 1                                     |                  | 11                 |                 |                 | bit 8    |

|               |                                        |                                       |                  |                    |                 |                 |          |

| R/W-0         | R/W-0                                  | R/W-0                                 | R/W-0            | R/W-0              | R/W-0           | U-0             | U-0      |

| EDG2MOD       | EDG2POL                                | EDG2SEL3                              | EDG2SEL2         | EDG2SEL1           | EDG2SEL0        | —               | _        |

| bit 7         |                                        |                                       |                  | 1 1                |                 | 1               | bit (    |

|               |                                        |                                       |                  |                    |                 |                 |          |

| Legend:       |                                        |                                       |                  |                    |                 |                 |          |

| R = Readabl   | le bit                                 | W = Writable                          | oit              | U = Unimplem       | ented bit, read | l as '0'        |          |

| -n = Value at | POR                                    | '1' = Bit is set                      |                  | '0' = Bit is clea  | red             | x = Bit is unkr | nown     |

|               |                                        |                                       |                  |                    |                 |                 |          |

| bit 15        | EDG1MOD: E                             | Edge 1 Edge Sa                        | ampling Mode     | Selection bit      |                 |                 |          |

|               | 1 = Edge 1 is                          | s edge-sensitive                      | 9                |                    |                 |                 |          |

|               | •                                      | s level-sensitive                     |                  |                    |                 |                 |          |

| bit 14        |                                        | dge 1 Polarity                        |                  |                    |                 |                 |          |

|               |                                        | s programmed f                        |                  |                    |                 |                 |          |

| L:1 40 40     | •                                      | s programmed f                        | •                | •                  |                 |                 |          |

| bit 13-10     | 1xxx = Rese                            | :0>: Edge 1 So                        | urce Select bits | 5                  |                 |                 |          |

|               | 01xx = Rese                            |                                       |                  |                    |                 |                 |          |

|               | 0011 = CTEE                            |                                       |                  |                    |                 |                 |          |

|               | 0010 = CTEE                            | •                                     |                  |                    |                 |                 |          |

|               | 0001 = OC1                             |                                       |                  |                    |                 |                 |          |

| hit O         | 0000 = Timer                           |                                       | :+               |                    |                 |                 |          |

| bit 9         |                                        | Edge 2 Status b                       |                  | vritten to control | the odge cou    | reo             |          |

|               | 1 = Edge 2 h                           |                                       |                  |                    | the edge sou    | ice.            |          |

|               |                                        | as not occurred                       | ł                |                    |                 |                 |          |

| bit 8         | EDG1STAT: E                            | Edge 1 Status b                       | it               |                    |                 |                 |          |

|               |                                        |                                       | 1 and can be v   | vritten to control | the edge sou    | rce.            |          |

|               | 1 = Edge 1 h                           |                                       |                  |                    |                 |                 |          |

|               | -                                      | as not occurred                       |                  |                    |                 |                 |          |

| bit 7         |                                        | Edge 2 Edge Sa                        |                  | Selection bit      |                 |                 |          |

|               |                                        | s edge-sensitive<br>s level-sensitive |                  |                    |                 |                 |          |

| bit 6         | •                                      | dge 2 Polarity                        |                  |                    |                 |                 |          |

| Sit 0         |                                        | s programmed f                        |                  | dae response       |                 |                 |          |

|               |                                        | s programmed f                        |                  |                    |                 |                 |          |

| bit 5-2       | EDG2SEL<3                              | :0>: Edge 2 So                        | urce Select bits | 3                  |                 |                 |          |

|               | 1111 <b>= Rese</b>                     | rved                                  |                  |                    |                 |                 |          |

|               | 01xx = Rese                            |                                       |                  |                    |                 |                 |          |

|               | 0100 = CMP <sup>2</sup><br>0011 = CTEE |                                       |                  |                    |                 |                 |          |

|               | 0010 = CTEE                            |                                       |                  |                    |                 |                 |          |

|               |                                        | Ji pili                               |                  |                    |                 |                 |          |

|               | 0001 = OC1                             | module                                |                  |                    |                 |                 |          |

|               |                                        | module                                |                  |                    |                 |                 |          |

#### REGISTER 22-2: CTMUCON2: CTMU CONTROL REGISTER 2

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | R/W-0                                                                                                                               | U-0              | U-0                                    | U-0              | R/W-0                  | U-0             | U-0            |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------|------------------|------------------------|-----------------|----------------|

|                 | CVR2OE <sup>(1)</sup>                                                                                                               | _                |                                        | _                | VREFSEL                |                 | _              |

| bit 15          |                                                                                                                                     |                  |                                        |                  |                        |                 | bit            |

| <b>D</b> 444 0  | DANIO                                                                                                                               |                  | <b>D</b> 444.0                         | <b>D</b> 444 0   | DAALO                  | DAMA            | <b>D</b> 444 0 |

| R/W-0           | R/W-0                                                                                                                               | R/W-0            | R/W-0                                  | R/W-0            | R/W-0                  | R/W-0           | R/W-0          |

| CVREN           | CVR10E <sup>(1)</sup>                                                                                                               | CVRR             | CVRSS <sup>(2)</sup>                   | CVR3             | CVR2                   | CVR1            | CVR0           |

| bit 7           |                                                                                                                                     |                  |                                        |                  |                        |                 | bit            |

| Legend:         |                                                                                                                                     |                  |                                        |                  |                        |                 |                |

| R = Readable    | bit                                                                                                                                 | W = Writable     | bit                                    | U = Unimple      | mented bit, read       | as '0'          |                |

| -n = Value at F | POR                                                                                                                                 | '1' = Bit is set | t                                      | '0' = Bit is cle | eared                  | x = Bit is unkn | iown           |

|                 |                                                                                                                                     |                  |                                        |                  |                        |                 |                |

| bit 15          | Unimplement                                                                                                                         |                  |                                        |                  |                        |                 |                |

| bit 14          |                                                                                                                                     | •                | ige Reference                          | •                | ble bit <sup>(1)</sup> |                 |                |

|                 |                                                                                                                                     |                  | nected to the C<br>onnected from       |                  | nin                    |                 |                |

| bit 13-11       | Unimplement                                                                                                                         |                  |                                        |                  | <b>F</b>               |                 |                |

| bit 10          | -                                                                                                                                   |                  | age Reference                          | e Select bit     |                        |                 |                |

|                 | 1 = CVREFIN =                                                                                                                       | -                | U                                      |                  |                        |                 |                |

|                 | 0 = CVREFIN is                                                                                                                      | s generated by   | y the resistor ne                      | etwork           |                        |                 |                |

| bit 9-8         | Unimplement                                                                                                                         | ed: Read as '    | 0'                                     |                  |                        |                 |                |

| bit 7           |                                                                                                                                     |                  | e Reference E                          |                  |                        |                 |                |

|                 |                                                                                                                                     |                  | erence circuit is<br>erence circuit is |                  | wn                     |                 |                |

| bit 6           | CVR1OE: Co                                                                                                                          | mparator Volta   | ige Reference                          | 1 Output Ena     | ble bit <sup>(1)</sup> |                 |                |

|                 |                                                                                                                                     |                  | n the CVREF1C                          |                  | n                      |                 |                |

| bit 5           | CVRR: Comp                                                                                                                          | arator Voltage   | Reference Ra                           | nge Selection    | n bit                  |                 |                |

|                 | 1 = CVRsRc/24 step-size<br>0 = CVRsRc/32 step-size                                                                                  |                  |                                        |                  |                        |                 |                |

| bit 4           | CVRSS: Comparator Voltage Reference Source Selection bit <sup>(2)</sup>                                                             |                  |                                        |                  |                        |                 |                |

|                 | 1 = Comparator voltage reference source, CVRSRC = (VREF+) – (AVSS)<br>0 = Comparator voltage reference source, CVRSRC = AVDD – AVSS |                  |                                        |                  |                        |                 |                |

| bit 3-0         | <b>CVR&lt;3:0&gt;</b> Comparator Voltage Reference Value Selection $0 \le \text{CVR}<3:0> \le 15$ bits                              |                  |                                        |                  |                        |                 |                |

|                 | When CVRR =                                                                                                                         |                  | (CVRSRC)                               |                  |                        |                 |                |

|                 | When CVRR = CVREFIN = (CV                                                                                                           | = 0:             |                                        | $(\mathbf{C})$   |                        |                 |                |

#### REGISTER 25-7: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

- 2: In order to operate with CVRSS = 1, at least one of the comparator modules must be enabled.

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax |                                                  | Description                               | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|-----------------|--------------------------------------------------|-------------------------------------------|---------------|-------------------------------|--------------------------|

| 46                 | MOV                  | MOV             | f,Wn                                             | Move f to Wn                              | 1             | 1                             | None                     |

|                    |                      | MOV             | f                                                | Move f to f                               | 1             | 1                             | None                     |

|                    |                      | MOV             | f,WREG                                           | Move f to WREG                            | 1             | 1                             | None                     |

|                    |                      | MOV             | #litl6,Wn                                        | Move 16-bit literal to Wn                 | 1             | 1                             | None                     |

|                    |                      | MOV.b           | #lit8,Wn                                         | Move 8-bit literal to Wn                  | 1             | 1                             | None                     |

|                    |                      | MOV             | Wn,f                                             | Move Wn to f                              | 1             | 1                             | None                     |

|                    |                      | MOV             | Wso,Wdo                                          | Move Ws to Wd                             | 1             | 1                             | None                     |

|                    |                      | MOV             | WREG, f                                          | Move WREG to f                            | 1             | 1                             | None                     |

|                    |                      | MOV.D           | Wns,Wd                                           | Move Double from W(ns):W(ns + 1) to<br>Wd | 1             | 2                             | None                     |

|                    |                      | MOV.D           | Ws , Wnd                                         | Move Double from Ws to W(nd +<br>1):W(nd) | 1             | 2                             | None                     |

| 47                 | MOVPAG               | MOVPAG          | #lit10,DSRPAG                                    | Move 10-bit literal to DSRPAG             | 1             | 1                             | None                     |

|                    |                      | MOVPAG          | #lit9,DSWPAG                                     | Move 9-bit literal to DSWPAG              | 1             | 1                             | None                     |

|                    |                      | MOVPAG          | #lit8,TBLPAG                                     | Move 8-bit literal to TBLPAG              | 1             | 1                             | None                     |

|                    |                      | MOVPAG          | Ws, DSRPAG                                       | Move Ws<9:0> to DSRPAG                    | 1             | 1                             | None                     |