Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 28-SPDIP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128mc202-e-sp |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

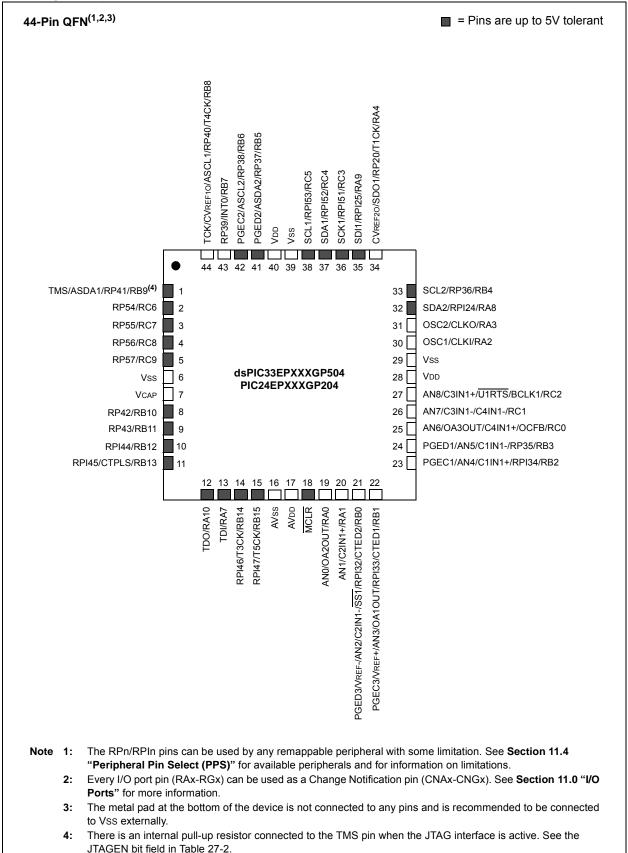

#### **Pin Diagrams (Continued)**

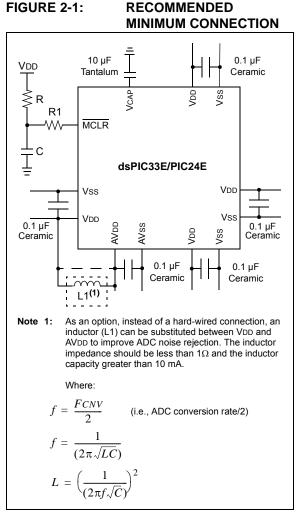

#### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

## 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 1 Ohm) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor greater than 4.7  $\mu$ F (10  $\mu$ F is recommended), 16V connected to ground. The type can be ceramic or tantalum. See **Section 30.0** "**Electrical Characteristics**" for additional information.

The placement of this capacitor should be close to the VCAP pin. It is recommended that the trace length not exceeds one-quarter inch (6 mm). See **Section 27.3 "On-Chip Voltage Regulator"** for details.

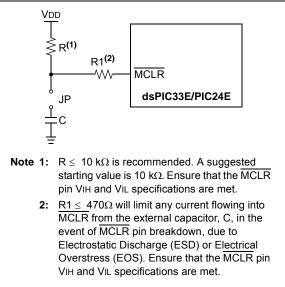

## 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor, C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components as shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

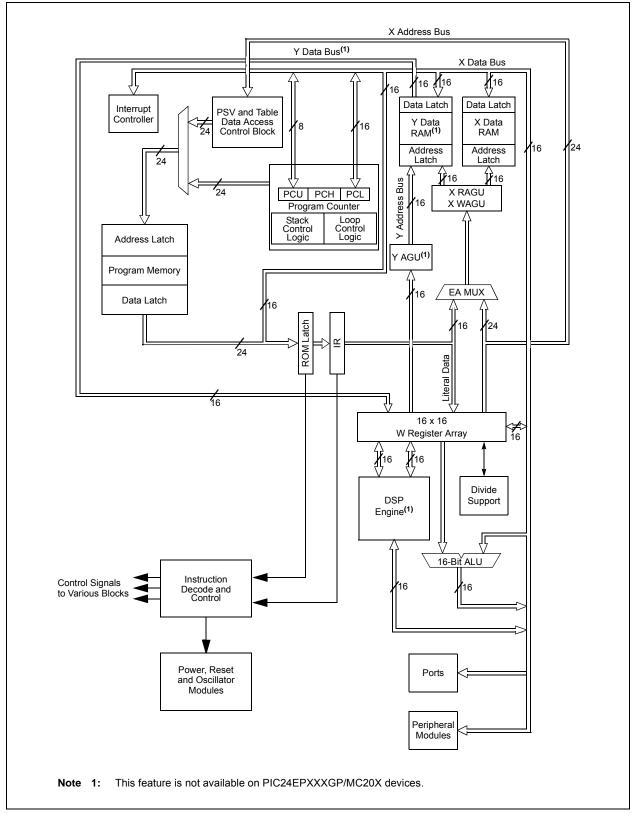

FIGURE 3-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X CPU BLOCK DIAGRAM

| IABLE 4   | -10.  | 001    |                                                                  | JMPARE                                                                 |        |           | OUIFU  |       | ARE 4       | REGIS       |              | <u>٢</u> |        |          |           |          |       |               |

|-----------|-------|--------|------------------------------------------------------------------|------------------------------------------------------------------------|--------|-----------|--------|-------|-------------|-------------|--------------|----------|--------|----------|-----------|----------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14                                                           | Bit 13                                                                 | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8       | Bit 7       | Bit 6        | Bit 5    | Bit 4  | Bit 3    | Bit 2     | Bit 1    | Bit 0 | All<br>Resets |

| OC1CON1   | 0900  | —      | -                                                                | OCSIDL                                                                 | C      | CTSEL<2:0 | )>     | —     | ENFLTB      | ENFLTA      | —            | OCFLTB   | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC1CON2   | 0902  | FLTMD  | FLTOUT                                                           | FLTTRIEN                                                               | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS   |        | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC1RS     | 0904  |        |                                                                  |                                                                        |        |           |        | Outp  | out Compare | e 1 Seconda | ary Register |          |        |          |           |          |       | xxxx          |

| OC1R      | 0906  |        |                                                                  |                                                                        |        |           |        |       | Output Co   | mpare 1 Re  | gister       |          |        |          |           |          |       | xxxx          |

| OC1TMR    | 0908  |        |                                                                  |                                                                        |        |           |        |       | Timer V     | alue 1 Regi | ster         |          |        |          |           |          |       | xxxx          |

| OC2CON1   | 090A  | _      | —                                                                | - OCSIDL OCTSEL<2:0> - ENFLTB ENFLTA - OCFLTB OCFLTA TRIGMODE OCM<2:0> |        |           |        |       |             |             | 0000         |          |        |          |           |          |       |               |

| OC2CON2   | 090C  | FLTMD  | FLTOUT                                                           | TOUT FLTTRIEN OCINV OC32 OCTRIG TRIGSTAT OCTRIS SYNCSEL<4:0>           |        |           |        |       |             |             |              | 000C     |        |          |           |          |       |               |

| OC2RS     | 090E  |        |                                                                  | Output Compare 2 Secondary Register                                    |        |           |        |       |             |             | xxxx         |          |        |          |           |          |       |               |

| OC2R      | 0910  |        |                                                                  |                                                                        |        |           |        |       | Output Co   | mpare 2 Re  | gister       |          |        |          |           |          |       | xxxx          |

| OC2TMR    | 0912  |        |                                                                  |                                                                        |        |           |        |       | Timer V     | alue 2 Regi | ster         |          |        |          |           |          |       | xxxx          |

| OC3CON1   | 0914  | _      | —                                                                | OCSIDL                                                                 | 0      | CTSEL<2:0 | )>     | _     | ENFLTB      | ENFLTA      | _            | OCFLTB   | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC3CON2   | 0916  | FLTMD  | FLTOUT                                                           | FLTTRIEN                                                               | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS   |        | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC3RS     | 0918  |        |                                                                  |                                                                        |        |           |        | Outp  | out Compare | e 3 Seconda | ary Register |          |        |          |           |          |       | xxxx          |

| OC3R      | 091A  |        |                                                                  |                                                                        |        |           |        |       | Output Co   | mpare 3 Re  | gister       |          |        |          |           |          |       | xxxx          |

| OC3TMR    | 091C  |        |                                                                  |                                                                        |        |           |        |       | Timer V     | alue 3 Regi | ster         |          |        |          |           |          |       | xxxx          |

| OC4CON1   | 091E  | _      | —                                                                | OCSIDL                                                                 | 0      | CTSEL<2:0 | )>     | _     | ENFLTB      | ENFLTA      | _            | OCFLTB   | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC4CON2   | 0920  | FLTMD  | D FLTOUT FLTTRIEN OCINV OC32 OCTRIG TRIGSTAT OCTRIS SYNCSEL<4:0> |                                                                        |        |           |        |       |             |             | 000C         |          |        |          |           |          |       |               |

| OC4RS     | 0922  |        |                                                                  |                                                                        |        |           |        | Outp  | out Compare | e 4 Seconda | ary Register |          |        |          |           |          |       | xxxx          |

| OC4R      | 0924  |        |                                                                  |                                                                        |        |           |        |       | Output Co   | mpare 4 Re  | gister       |          |        |          |           |          |       | xxxx          |

| OC4TMR    | 0926  |        |                                                                  |                                                                        |        |           |        |       | Timer V     | alue 4 Regi | ster         |          |        |          |           |          |       | xxxx          |

## TABLE 4-10: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 4 REGISTER MAP

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4                                                                        | -12:  | PWM RI   | EGISTE                   | R MAP  | FOR de | sPIC33E | PXXXN  | AC20X/50 | DX AND F | PIC24EP | PXXXM | C20X [ | DEVICE | S ONI | _Y    |       |       |               |

|--------------------------------------------------------------------------------|-------|----------|--------------------------|--------|--------|---------|--------|----------|----------|---------|-------|--------|--------|-------|-------|-------|-------|---------------|

| File Name                                                                      | Addr. | Bit 15   | Bit 14                   | Bit 13 | Bit 12 | Bit 11  | Bit 10 | Bit 9    | Bit 8    | Bit 7   | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| PTCON                                                                          | 0C00  | PTEN     |                          |        |        |         |        |          |          |         |       |        |        | 0000  |       |       |       |               |

| PTCON2                                                                         | 0C02  | _        | PCLKDIV<2:0> 0000        |        |        |         |        |          |          |         |       |        | 0000   |       |       |       |       |               |

| PTPER                                                                          | 0C04  |          | PTPER<15:0> 00F8         |        |        |         |        |          |          |         |       |        |        |       |       |       |       |               |

| SEVTCMP                                                                        | 0C06  |          |                          |        |        |         |        |          | SEVTCMP< | 5:0>    |       |        |        |       |       |       |       | 0000          |

| MDC                                                                            | 0C0A  |          |                          |        |        |         |        |          | MDC<15:  | )>      |       |        |        |       |       |       |       | 0000          |

| CHOP                                                                           | 0C1A  | CHPCLKEN | PCLKEN CHOPCLK<9:0> 0000 |        |        |         |        |          |          |         |       |        |        |       |       |       |       |               |

| PWMKEY                                                                         | 0C1E  |          |                          |        |        |         |        |          | PWMKEY<1 | 5:0>    |       |        |        |       |       |       |       | 0000          |

| Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |       |          |                          |        |        |         |        |          |          |         |       |        |        |       |       |       |       |               |

## TABLE 4-13: PWM GENERATOR 1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

|           | 10.   |         |        |         |                                                                                      |          | I OIT U |        |           |          |        | 1102- |        |       |          |       |       |               |

|-----------|-------|---------|--------|---------|--------------------------------------------------------------------------------------|----------|---------|--------|-----------|----------|--------|-------|--------|-------|----------|-------|-------|---------------|

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12                                                                               | Bit 11   | Bit 10  | Bit 9  | Bit 8     | Bit 7    | Bit 6  | Bit 5 | Bit 4  | Bit 3 | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

| PWMCON1   | 0C20  | FLTSTAT | CLSTAT | TRGSTAT | FLTIEN                                                                               | CLIEN    | TRGIEN  | ITB    | MDCS      | DTC<     | :1:0>  | DTCP  | _      | MTBS  | CAM      | XPRES | IUE   | 0000          |

| IOCON1    | 0C22  | PENH    | PENL   | POLH    | POLL                                                                                 | PMOD     | <1:0>   | OVRENH | OVRENL    | OVRDA    | T<1:0> | FLTDA | T<1:0> | CLDA  | T<1:0>   | SWAP  | OSYNC | C000          |

| FCLCON1   | 0C24  | _       |        | (       | CLSRC<4:0> CLPOL CLMOD FLTSRC<4:0> FLTPOL FLTMOD<1:0>                                |          |         |        |           |          | 0000   |       |        |       |          |       |       |               |

| PDC1      | 0C26  |         |        |         | PDC1<15:0>                                                                           |          |         |        |           |          | FFF8   |       |        |       |          |       |       |               |

| PHASE1    | 0C28  |         |        |         |                                                                                      |          |         |        | PHASE1<15 | :0>      |        |       |        |       |          |       |       | 0000          |

| DTR1      | 0C2A  | _       | _      |         |                                                                                      |          |         |        |           | DTR1<13: | 0>     |       |        |       |          |       |       | 0000          |

| ALTDTR1   | 0C2C  | _       | _      |         |                                                                                      |          |         |        | А         | LTDTR1<1 | 3:0>   |       |        |       |          |       |       | 0000          |

| TRIG1     | 0C32  |         |        |         |                                                                                      |          |         |        | TRGCMP<18 | 5:0>     |        |       |        |       |          |       |       | 0000          |

| TRGCON1   | 0C34  |         | TRGDI  | V<3:0>  |                                                                                      | _        | _       | _      | _         | _        | _      |       |        | TRG   | STRT<5:0 | >     |       | 0000          |

| LEBCON1   | 0C3A  | PHR     | PHF    | PLR     | PLF                                                                                  | FLTLEBEN | CLLEBEN | _      | _         | _        | _      | BCH   | BCL    | BPHH  | BPHL     | BPLH  | BPLL  | 0000          |

| LEBDLY1   | 0C3C  | _       | _      | —       | LEB<11:0>00                                                                          |          |         |        |           |          | 0000   |       |        |       |          |       |       |               |

| AUXCON1   | 0C3E  | —       | —      | _       | -     BLANKSEL<3:0>     -     -     CHOPSEL<3:0>     CHOPHEN     CHOPLEN     CHOPLEN |          |         |        |           | 0000     |        |       |        |       |          |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-37: PMD REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | _     | _     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      |       | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  |        | —      | _      | —      | _      | CMPMD  | _     | -     | CRCMD  | _     |       |        |        | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  |        | —      | _      | —      | _      |        | _     | -     | —      | _     |       |        | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  |        | _      |        | —      | _      |        | _     |       | —      | _     |       |        |        | —      | —      |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  | _      |        |        | _      |        |        |       |       |        |       |       | DMA1MD | PTGMD  | _      |        |       | 0000          |

|              | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-38: PMD REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  |        | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      |        | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | —      | -      | _      |        |        | PWM3MD | PWM2MD | PWM1MD | _      | —     | —     | _      |        | —      | _      |       | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

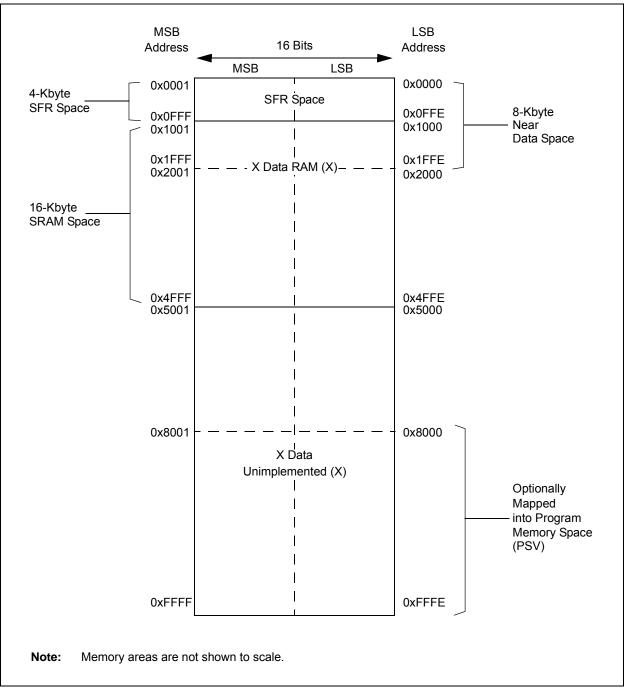

## 4.8 Interfacing Program and Data Memory Spaces

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture uses a 24-bit-wide Program Space (PS) and a 16-bit-wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

#### TABLE 4-65: PROGRAM SPACE ADDRESS CONSTRUCTION

|                        | Access        | Program Space Address    |                              |          |               |     |  |  |  |  |  |

|------------------------|---------------|--------------------------|------------------------------|----------|---------------|-----|--|--|--|--|--|

| Access Type            | Space         | <23>                     | <22:16>                      | <15>     | <14:1>        | <0> |  |  |  |  |  |

| Instruction Access     | User          | 0                        |                              | PC<22:1> |               | 0   |  |  |  |  |  |

| (Code Execution)       |               |                          | 0xx xxxx xxxx xxxx xxxx xxx0 |          |               |     |  |  |  |  |  |

| TBLRD/TBLWT            | User          | TB                       | LPAG<7:0>                    |          | Data EA<15:0> |     |  |  |  |  |  |

| (Byte/Word Read/Write) |               | 0xxx xxxx xxxx xxxx xxxx |                              |          |               |     |  |  |  |  |  |

|                        | Configuration | TB                       | LPAG<7:0>                    |          | Data EA<15:0> |     |  |  |  |  |  |

|                        |               | 1                        | xxx xxxx                     | XXXX XX  | ***           |     |  |  |  |  |  |

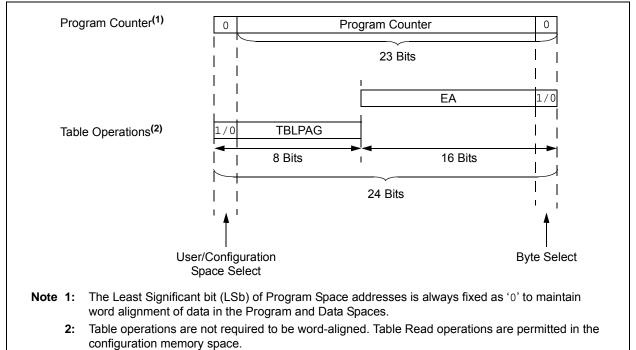

#### FIGURE 4-22: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

#### 4.8.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

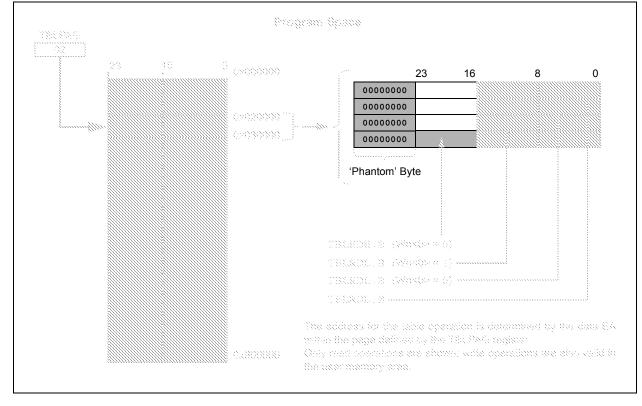

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the Program Space without going through Data Space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a Program Space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit-wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from Program Space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the Program Space location (P<15:0>) to a data address (D<15:0>)

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>) is always '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a Program Space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user application and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

## FIGURE 4-23: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

## 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.4.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

#### 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs. In comparison, some digital-only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include  $I^2C^{TM}$  and the PWM. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheralselectable pin is handled in two different ways, depending on whether an input or output is being mapped.

#### REGISTER 17-2: QEI1IOC: QEI1 I/O CONTROL REGISTER (CONTINUED)

- bit 2 INDEX: Status of INDXx Input Pin After Polarity Control

- 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

- bit 1 QEB: Status of QEBx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1' 0 = Pin is at logic '0'

- bit 0 **QEA:** Status of QEAx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

#### REGISTER 20-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement is disabled or completed</li> </ul> |

| bit 4   | URXINV: UARTx Receive Polarity Inversion bit                                                                                                                                                                                              |

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                                                  |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                                                                           |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul>                                                        |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                                                                                |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                                                                             |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                                                                             |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                                                                                     |

|         | Refer to the " <b>UART</b> " (DS70582) section in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for receive or transmit operation.                                                             |

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

- 3: This feature is only available on 44-pin and 64-pin devices.

- 4: This feature is only available on 64-pin devices.

#### REGISTER 25-1: CMSTAT: OP AMP/COMPARATOR STATUS REGISTER (CONTINUED)

- C2OUT: Comparator 2 Output Status bit<sup>(2)</sup> bit 1 When CPOL = 0: 1 = VIN + > VIN -0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -C10UT: Comparator 1 Output Status bit<sup>(2)</sup> bit 0 When CPOL = 0: 1 = VIN + > VIN-0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -

- **Note 1:** Reflects the value of the of the CEVT bit in the respective Op Amp/Comparator Control register, CMxCON<9>.

- 2: Reflects the value of the COUT bit in the respective Op Amp/Comparator Control register, CMxCON<8>.

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax                            | Description                                 | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|--------|--------------------------------------------|---------------------------------------------|---------------|-------------------------------|--------------------------|

| 25                 | DAW                  | DAW    | Wn                                         | Wn = decimal adjust Wn                      | 1             | 1                             | С                        |

| 26                 | DEC                  | DEC    | f                                          | f = f - 1                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | DEC    | f,WREG                                     | WREG = f – 1                                | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | DEC    | Ws,Wd                                      | Wd = Ws - 1                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 27                 | DEC2                 | DEC2   | f                                          | f = f - 2                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | DEC2   | f,WREG                                     | WREG = f – 2                                | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | DEC2   | Ws,Wd                                      | Wd = Ws - 2                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 28                 | DISI                 | DISI   | #lit14                                     | Disable Interrupts for k instruction cycles | 1             | 1                             | None                     |

| 29                 | DIV                  | DIV.S  | Wm,Wn                                      | Signed 16/16-bit Integer Divide             | 1             | 18                            | N,Z,C,OV                 |

|                    |                      | DIV.SD | Wm,Wn                                      | Signed 32/16-bit Integer Divide             | 1             | 18                            | N,Z,C,OV                 |

|                    |                      | DIV.U  | Wm,Wn                                      | Unsigned 16/16-bit Integer Divide           | 1             | 18                            | N,Z,C,OV                 |

|                    |                      | DIV.UD | Wm,Wn                                      | Unsigned 32/16-bit Integer Divide           | 1             | 18                            | N,Z,C,OV                 |

| 30                 | DIVF                 | DIVF   | Wm , Wn <sup>(1)</sup>                     | Signed 16/16-bit Fractional Divide          | 1             | 18                            | N,Z,C,OV                 |

| 31                 | DO                   | DO     | #lit15,Expr <sup>(1)</sup>                 | Do code to PC + Expr, lit15 + 1 times       | 2             | 2                             | None                     |

|                    |                      | DO     | Wn, Expr(1)                                | Do code to PC + Expr, (Wn) + 1 times        | 2             | 2                             | None                     |

| 32                 | ED                   | ED     | Wm*Wm,Acc,Wx,Wy,Wxd <sup>(1)</sup>         | Euclidean Distance (no accumulate)          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 33                 | EDAC                 | EDAC   | Wm*Wm,Acc,Wx,Wy,Wxd <sup>(1)</sup>         | Euclidean Distance                          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 34                 | EXCH                 | EXCH   | Wns,Wnd                                    | Swap Wns with Wnd                           | 1             | 1                             | None                     |

| 35                 | FBCL                 | FBCL   | Ws,Wnd                                     | Find Bit Change from Left (MSb) Side        | 1             | 1                             | С                        |

| 36                 | FF1L                 | FF1L   | Ws,Wnd                                     | Find First One from Left (MSb) Side         | 1             | 1                             | С                        |

| 37                 | FF1R                 | FF1R   | Ws,Wnd                                     | Find First One from Right (LSb) Side        | 1             | 1                             | С                        |

| 38                 | GOTO                 | GOTO   | Expr                                       | Go to address                               | 2             | 4                             | None                     |

|                    |                      | GOTO   | Wn                                         | Go to indirect                              | 1             | 4                             | None                     |

|                    |                      | GOTO.L | Wn                                         | Go to indirect (long address)               | 1             | 4                             | None                     |

| 39                 | INC                  | INC    | f                                          | f = f + 1                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | INC    | f,WREG                                     | WREG = f + 1                                | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | INC    | Ws,Wd                                      | Wd = Ws + 1                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 40                 | INC2                 | INC2   | f                                          | f = f + 2                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | INC2   | f,WREG                                     | WREG = f + 2                                | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | INC2   | Ws,Wd                                      | Wd = Ws + 2                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 41                 | IOR                  | IOR    | f                                          | f = f .IOR. WREG                            | 1             | 1                             | N,Z                      |

|                    |                      | IOR    | f,WREG                                     | WREG = f .IOR. WREG                         | 1             | 1                             | N,Z                      |

|                    |                      | IOR    | #lit10,Wn                                  | Wd = lit10 .IOR. Wd                         | 1             | 1                             | N,Z                      |

|                    |                      | IOR    | Wb,Ws,Wd                                   | Wd = Wb .IOR. Ws                            | 1             | 1                             | N,Z                      |

|                    |                      | IOR    | Wb,#lit5,Wd                                | Wd = Wb .IOR. lit5                          | 1             | 1                             | N,Z                      |

| 42                 | LAC                  | LAC    | Wso,#Slit4,Acc                             | Load Accumulator                            | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 43                 | LNK                  | LNK    | #lit14                                     | Link Frame Pointer                          | 1             | 1                             | SFA                      |

| 44                 | LSR                  | LSR    | f                                          | f = Logical Right Shift f                   | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | LSR    | f,WREG                                     | WREG = Logical Right Shift f                | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | LSR    | Ws,Wd                                      | Wd = Logical Right Shift Ws                 | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | LSR    | Wb,Wns,Wnd                                 | Wnd = Logical Right Shift Wb by Wns         | 1             | 1                             | N,Z                      |

|                    |                      | LSR    | Wb,#lit5,Wnd                               | Wnd = Logical Right Shift Wb by lit5        | 1             | 1                             | N,Z                      |

| 45                 | MAC                  | MAC    | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd,AWB <sup>(1)</sup> | Multiply and Accumulate                     | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MAC    | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd <sup>(1)</sup>     | Square and Accumulate                       | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

| AC CH        | ARACTEI | RISTICS                                              | Standard O<br>(unless oth<br>Operating te | erwise  | ture -40°C                        | ≤ Ta ≤ + | 7 <b>to 3.6V</b><br>-85°C for Industrial<br>-125°C for Extended                               |

|--------------|---------|------------------------------------------------------|-------------------------------------------|---------|-----------------------------------|----------|-----------------------------------------------------------------------------------------------|

| Param<br>No. | Symbol  | Characteristic                                       | Min.                                      | Тур.    | Max.                              | Units    | Conditions                                                                                    |

|              |         |                                                      | Devi                                      | ce Sup  | ply                               |          |                                                                                               |

| AD01         | AVDD    | Module VDD Supply                                    | Greater of:<br>VDD – 0.3<br>or 3.0        |         | Lesser of:<br>VDD + 0.3<br>or 3.6 | V        |                                                                                               |

| AD02         | AVss    | Module Vss Supply                                    | Vss – 0.3                                 |         | Vss + 0.3                         | V        |                                                                                               |

|              |         |                                                      | Refere                                    | ence In | puts                              |          |                                                                                               |

| AD05         | Vrefh   | Reference Voltage High                               | AVss + 2.5                                |         | AVDD                              | V        | VREFH = VREF+<br>VREFL = VREF- <b>(Note 1)</b>                                                |

| AD05a        |         |                                                      | 3.0                                       | _       | 3.6                               | V        | VREFH = AVDD<br>VREFL = AVSS = 0                                                              |

| AD06         | VREFL   | Reference Voltage Low                                | AVss                                      |         | AVDD - 2.5                        | V        | (Note 1)                                                                                      |

| AD06a        |         |                                                      | 0                                         | _       | 0                                 | V        | VREFH = AVDD<br>VREFL = AVSS = 0                                                              |

| AD07         | VREF    | Absolute Reference<br>Voltage                        | 2.5                                       | _       | 3.6                               | V        | VREF = VREFH - VREFL                                                                          |

| AD08         | IREF    | Current Drain                                        | _                                         |         | 10<br>600                         | μΑ<br>μΑ | ADC off<br>ADC on                                                                             |

| AD09         | Iad     | Operating Current <sup>(2)</sup>                     | —                                         | 5       | —                                 | mA       | ADC operating in 10-bit mode (Note 1)                                                         |

|              |         |                                                      | —                                         | 2       | —                                 | mA       | ADC operating in 12-bit mode (Note 1)                                                         |

|              | •       |                                                      | Ana                                       | log Inp | ut                                |          |                                                                                               |

| AD12         | Vinh    | Input Voltage Range<br>VinH                          | VINL                                      |         | Vrefh                             | V        | This voltage reflects Sample-and-<br>Hold Channels 0, 1, 2 and 3<br>(CH0-CH3), positive input |

| AD13         | VINL    | Input Voltage Range<br>VINL                          | Vrefl                                     | _       | AVss + 1V                         | V        | This voltage reflects Sample-and-<br>Hold Channels 0, 1, 2 and 3<br>(CH0-CH3), negative input |

| AD17         | Rin     | Recommended<br>Impedance of Analog<br>Voltage Source | _                                         | _       | 200                               | Ω        | Impedance to achieve maximum<br>performance of ADC                                            |

## TABLE 30-57: ADC MODULE SPECIFICATIONS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

2: Parameter is characterized but not tested in manufacturing.

NOTES:

# 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL A

|                         | Units  | N     | <b>IILLIMETER</b> | S     |

|-------------------------|--------|-------|-------------------|-------|

| Dimension               | Limits | MIN   | NOM               | MAX   |

| Number of Pins          | Ν      |       | 44                |       |

| Number of Pins per Side | ND     |       | 12                |       |

| Number of Pins per Side | NE     |       | 10                |       |

| Pitch                   | е      |       | 0.50 BSC          |       |

| Overall Height          | Α      | 0.80  | 0.90              | 1.00  |

| Standoff                | A1     | 0.025 | -                 | 0.075 |

| Overall Width           | Е      |       | 6.00 BSC          |       |

| Exposed Pad Width       | E2     | 4.40  | 4.55              | 4.70  |

| Overall Length          | D      |       | 6.00 BSC          |       |

| Exposed Pad Length      | D2     | 4.40  | 4.55              | 4.70  |

| Contact Width           | b      | 0.20  | 0.25              | 0.30  |

| Contact Length          | L      | 0.20  | 0.25              | 0.30  |

| Contact-to-Exposed Pad  | К      | 0.20  | -                 | -     |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-157C Sheet 2 of 2

## APPENDIX A: REVISION HISTORY

## **Revision A (April 2011)**

This is the initial released version of the document.

## Revision B (July 2011)

This revision includes minor typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in Table A-1.

#### TABLE A-1: MAJOR SECTION UPDATES

| Section Name                                                                     | Update Description                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-bit<br>Digital Signal Controllers<br>and Microcontrollers" | Changed all pin diagrams references of VLAP to TLA.                                                                                                                                                                                                                                                                     |

| Section 4.0 "Memory<br>Organization"                                             | Updated the All Resets values for CLKDIV and PLLFBD in the System Control Register Map (see Table 4-35).                                                                                                                                                                                                                |

| Section 5.0 "Flash Program<br>Memory"                                            | Updated "one word" to "two words" in the first paragraph of <b>Section 5.2 "RTSP Operation</b> ".                                                                                                                                                                                                                       |

| Section 9.0 "Oscillator<br>Configuration"                                        | Updated the PLL Block Diagram (see Figure 9-2).<br>Updated the Oscillator Mode, Fast RC Oscillator (FRC) with divide-by-N and PLL<br>(FRCPLL), by changing (FRCDIVN + PLL) to (FRCPLL).                                                                                                                                 |

|                                                                                  | Changed (FRCDIVN + PLL) to (FRCPLL) for COSC<2:0> = 001 and NOSC<2:0> = 001 in the Oscillator Control Register (see Register 9-1).                                                                                                                                                                                      |

|                                                                                  | Changed the POR value from 0 to 1 for the DOZE<1:0> bits, from 1 to 0 for the FRCDIV<0> bit, and from 0 to 1 for the PLLPOST<0> bit; Updated the default definitions for the DOZE<2:0> and FRCDIV<2:0> bits and updated all bit definitions for the PLLPOST<1:0> bits in the Clock Divisor Register (see Register 9-2). |

|                                                                                  | Changed the POR value from 0 to 1 for the PLLDIV<5:4> bits and updated the default definitions for all PLLDIV<8:0> bits in the PLL Feedback Division Register (see Register 9-2).                                                                                                                                       |

| Section 22.0 "Charge Time<br>Measurement Unit (CTMU)"                            | Updated the bit definitions for the IRNG<1:0> bits in the CTMU Current Control Register (see Register 22-3).                                                                                                                                                                                                            |

| Section 25.0 "Op amp/<br>Comparator Module"                                      | Updated the voltage reference block diagrams (see Figure 25-1 and Figure 25-2).                                                                                                                                                                                                                                         |

| TyCON (Timer3 and Timer5 Control)    |        |

|--------------------------------------|--------|

| UxMODE (UARTx Mode)                  |        |

| UxSTA (UARTx Status and Control)     |        |

| VEL1CNT (Velocity Counter 1)         | 259    |

| Resets                               | 123    |

| Brown-out Reset (BOR)                |        |

| Configuration Mismatch Reset (CM)    | 123    |

| Illegal Condition Reset (IOPUWR)     | 123    |

| Illegal Opcode                       | 123    |

| Security                             |        |

| Uninitialized W Register             | 123    |

| Master Clear (MCLR) Pin Reset        | 123    |

| Power-on Reset (POR)                 |        |

| RESET Instruction (SWR)              |        |

| Resources                            |        |

| Trap Conflict Reset (TRAPR)          | 123    |

| Watchdog Timer Time-out Reset (WDTO) | 123    |

| Resources Required for Digital PFC   | 32, 34 |

| Revision History                     |        |

## S

| Serial Peripheral Interface (SPI)<br>Software Stack Pointer (SSP) |     |

|-------------------------------------------------------------------|-----|

| Special Features of the CPU                                       |     |

| SPI                                                               |     |

| Control Registers                                                 | 268 |

| Helpful Tips                                                      | 267 |

| Resources                                                         | 267 |

## т

| Temperature and Voltage Specifications |

|----------------------------------------|

| AC                                     |

| Thermal Operating Conditions           |

| Thermal Packaging Characteristics      |

| Timer1                                 |

| Control Register                       |

| Resources                              |

| Timer2/3 and Timer4/5                  |

| Control Registers                      |

| Resources                              |

| Timing Diagrams                        |

| 10-Bit ADC Conversion (CHPS<1:0> = 01, |

| SIMSAM = 0, ASAM = 0, SSRC<2:0> = 000, |

| SSRCG = 0)                             |

| 10-Bit ADC Conversion (CHPS<1:0> = 01, |

| SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, |

| SSRCG = 0, SAMC<4:0> = 00010)          |

| 12-Bit ADC Conversion (ASAM = 0,       |

| SSRC<2:0> = 000, SSRCG = 0)            |

| BOR and Master Clear Reset             |

| ECANx I/O                              |

| External Clock414                      |

| High-Speed PWMx Fault422               |

| High-Speed PWMx Module                 |

| I/O Characteristics                    |

| I2Cx Bus Data (Master Mode)450         |

| I2Cx Bus Data (Slave Mode)             |

| I2Cx Bus Start/Stop Bits (Master Mode) |

| I2Cx Bus Start/Stop Bits (Slave Mode)  |

|                                        |

| Input Capture x (ICx)                         | . 420 |

|-----------------------------------------------|-------|

| OCx/PWMx                                      |       |

| Output Compare x (OCx)                        | . 421 |

| QEA/QEB Input                                 | . 424 |

| QEI Module Index Pulse                        | . 425 |

| SPI1 Master Mode (Full-Duplex, CKE = 0,       |       |

| CKP = x, SMP = 1)                             | . 441 |

| SPI1 Master Mode (Full-Duplex, CKE = 1,       |       |

| CKP = x, SMP = 1)                             | . 440 |

| SPI1 Master Mode (Half-Duplex, Transmit Only, |       |

| CKE = 0)                                      | . 438 |

| SPI1 Master Mode (Half-Duplex, Transmit Only, |       |

| CKE = 1)                                      | . 439 |

| SPI1 Slave Mode (Full-Duplex, CKE = 0,        |       |

| CKP = 0, SMP = 0)                             | . 448 |

| SPI1 Slave Mode (Full-Duplex, CKE = 0,        |       |

| CKP = 1, SMP = 0)                             | . 446 |

| SPI1 Slave Mode (Full-Duplex, CKE = 1,        |       |

| CKP = 0, SMP = 0)                             | . 442 |

| SPI1 Slave Mode (Full-Duplex, CKE = 1,        |       |

| CKP = 1, SMP = 0)                             | . 444 |

| SPI2 Master Mode (Full-Duplex, CKE = 0,       |       |

| CKP = x, SMP = 1)                             | . 429 |

| SPI2 Master Mode (Full-Duplex, CKE = 1,       |       |

| CKP = x, SMP = 1)                             | . 428 |

| SPI2 Master Mode (Half-Duplex, Transmit Only, |       |

| CKE = 0)                                      | . 426 |

| SPI2 Master Mode (Half-Duplex, Transmit Only, |       |

| CKE = 1)                                      | . 427 |

| SPI2 Slave Mode (Full-Duplex, CKE = 0,        |       |

| CKP = 0, SMP = 0)                             | . 436 |

| SPI2 Slave Mode (Full-Duplex, CKE = 0,        |       |

| CKP = 1, SMP = 0)                             | . 434 |

| SPI2 Slave Mode (Full-Duplex, CKE = 1,        |       |

| CKP = 0, SMP = 0)                             | . 430 |

| SPI2 Slave Mode (Full-Duplex, CKE = 1,        |       |

| CKP = 1, SMP = 0)                             |       |

| Timer1-Timer5 External Clock                  |       |

| TimerQ (QEI Module) External Clock            |       |

| UARTx I/O                                     | . 454 |

|                                               |       |

## U

| Universal Asynchronous Receiver |       |

|---------------------------------|-------|

| Transmitter (UART)              | . 281 |

| Control Registers               | . 283 |

| Helpful Tips                    | . 282 |

| Resources                       | . 282 |

| User ID Words                   | . 384 |

| V                               |       |

| Voltage Regulator (On-Chip)     | . 384 |

## w

| Watchdog Timer (WDT)       | 379, 385 |

|----------------------------|----------|

| Programming Considerations | 385      |

| WWW Address                | 524      |

| WWW, On-Line Support       | 23       |