#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128mc202-e-ss |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

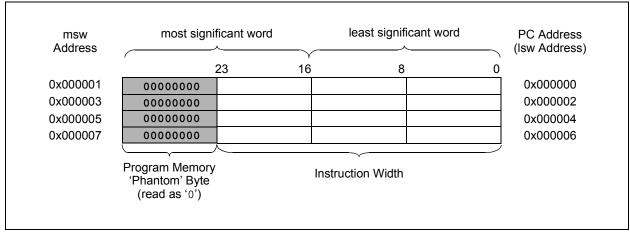

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-6).

Program memory addresses are always word-aligned on the lower word and addresses are incremented, or decremented by two, during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

# 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices reserve the addresses between 0x000000 and 0x000200 for hardcoded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of Flash memory, with the actual address for the start of code at address, 0x000002, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in **Section 7.1** "Interrupt Vector Table".

## FIGURE 4-6: PROGRAM MEMORY ORGANIZATION

# TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8 | Bit 7 | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|-------|-------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >     |       | —       | _           | _       | —       | _      | —           |        | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<    | 2:0>  |       | PT      | GSTEPIP<2   | :0>     | —       | —      | _           | -      | 4440          |

| IPC37        | 088A  | _      | —      | —          | _      | _      | F      | PTG3IP<2:0 | )>    |       |         | PTG2IP<2:0> | >       | _       |        | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     |        |        |        | _          | _     | _     | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     | _      | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      | _      |        |            | —     |       | _       | —           | —       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | —      | —          | _      | _      |        |            | —     |       | _       | DAE         | DOOVR   | _       | —      | —           |        | 0000          |

| INTCON4      | 08C6  | _      | _      | _          | _      | _      | -      | _          | —     | _     | _       | _           | _       | —       | —      | —           | SGHT   | 0000          |

| INTTREG      | 08C8  | Ι      | _      | _          | _      |        | ILR<   | 3:0>       |       |       |         |             | VECN    | UM<7:0> |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

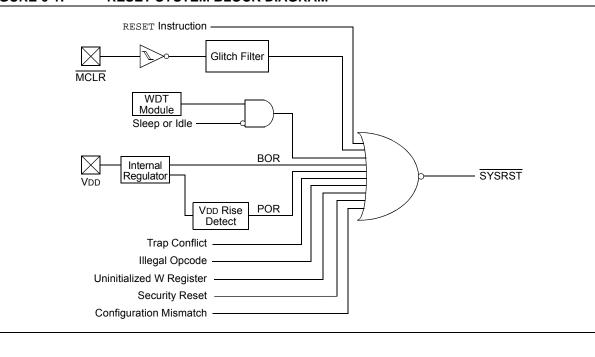

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- · BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Time-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 4.0 "Memory Organization" of this manual for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR and BOR bits (RCON<1:0>), that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

For all Resets, the default clock source is determined by the FNOSC<2:0> bits in the FOSCSEL Configuration register. The value of the FNOSC<2:0> bits is loaded into NOSC<2:0> (OSCCON<10:8>) on Reset, which in turn, initializes the system clock.

|                                                     | Vector  | IRQ        |                   | Inte     | errupt Bit L | ocation      |

|-----------------------------------------------------|---------|------------|-------------------|----------|--------------|--------------|

| Interrupt Source                                    | #       | #          | IVT Address       | Flag     | Enable       | Priority     |

| QEI1 – QEI1 Position Counter Compare <sup>(2)</sup> | 66      | 58         | 0x000088          | IFS3<10> | IEC3<10>     | IPC14<10:8>  |

| Reserved                                            | 67-72   | 59-64      | 0x00008A-0x000094 | _        | _            | _            |

| U1E – UART1 Error Interrupt                         | 73      | 65         | 0x000096          | IFS4<1>  | IEC4<1>      | IPC16<6:4>   |

| U2E – UART2 Error Interrupt                         | 74      | 66         | 0x000098          | IFS4<2>  | IEC4<2>      | IPC16<10:8>  |

| CRC – CRC Generator Interrupt                       | 75      | 67         | 0x00009A          | IFS4<3>  | IEC4<3>      | IPC16<14:12> |

| Reserved                                            | 76-77   | 68-69      | 0x00009C-0x00009E | —        | _            | —            |

| C1TX – CAN1 TX Data Request <sup>(1)</sup>          | 78      | 70         | 0x000A0           | IFS4<6>  | IEC4<6>      | IPC17<10:8>  |

| Reserved                                            | 79-84   | 71-76      | 0x0000A2-0x0000AC | —        | _            | —            |

| CTMU – CTMU Interrupt                               | 85      | 77         | 0x0000AE          | IFS4<13> | IEC4<13>     | IPC19<6:4>   |

| Reserved                                            | 86-101  | 78-93      | 0x0000B0-0x0000CE | —        | _            | —            |

| PWM1 – PWM Generator 1 <sup>(2)</sup>               | 102     | 94         | 0x0000D0          | IFS5<14> | IEC5<14>     | IPC23<10:8>  |

| PWM2 – PWM Generator 2 <sup>(2)</sup>               | 103     | 95         | 0x0000D2          | IFS5<15> | IEC5<15>     | IPC23<14:12> |

| PWM3 – PWM Generator 3 <sup>(2)</sup>               | 104     | 96         | 0x0000D4          | IFS6<0>  | IEC6<0>      | IPC24<2:0>   |

| Reserved                                            | 105-149 | 97-141     | 0x0001D6-0x00012E | —        | _            | —            |

| ICD – ICD Application                               | 150     | 142        | 0x000142          | IFS8<14> | IEC8<14>     | IPC35<10:8>  |

| JTAG – JTAG Programming                             | 151     | 143        | 0x000130          | IFS8<15> | IEC8<15>     | IPC35<14:12> |

| Reserved                                            | 152     | 144        | 0x000134          | —        | —            | _            |

| PTGSTEP – PTG Step                                  | 153     | 145        | 0x000136          | IFS9<1>  | IEC9<1>      | IPC36<6:4>   |

| PTGWDT – PTG Watchdog Time-out                      | 154     | 146        | 0x000138          | IFS9<2>  | IEC9<2>      | IPC36<10:8>  |

| PTG0 – PTG Interrupt 0                              | 155     | 147        | 0x00013A          | IFS9<3>  | IEC9<3>      | IPC36<14:12> |

| PTG1 – PTG Interrupt 1                              | 156     | 148        | 0x00013C          | IFS9<4>  | IEC9<4>      | IPC37<2:0>   |

| PTG2 – PTG Interrupt 2                              | 157     | 149        | 0x00013E          | IFS9<5>  | IEC9<5>      | IPC37<6:4>   |

| PTG3 – PTG Interrupt 3                              | 158     | 150        | 0x000140          | IFS9<6>  | IEC9<6>      | IPC37<10:8>  |

| Reserved                                            | 159-245 | 151-245    | 0x000142-0x0001FE | —        | —            | _            |

|                                                     | Lowe    | est Natura | I Order Priority  |          |              |              |

## TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

2: This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

## 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the powersaving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the ECAN<sup>™</sup> module has been configured for 500 kbps, based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the ECAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

#### 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

| Note: | If a PMD bit is set, the corresponding        |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|

|       | module is disabled after a delay of one       |  |  |  |  |  |

|       | instruction cycle. Similarly, if a PMD bit is |  |  |  |  |  |

|       | cleared, the corresponding module is          |  |  |  |  |  |

|       | enabled after a delay of one instruction      |  |  |  |  |  |

|       | cycle (assuming the module control regis-     |  |  |  |  |  |

|       | ters are already configured to enable         |  |  |  |  |  |

|       | module operation).                            |  |  |  |  |  |

## 10.5 Power-Saving Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

#### 10.5.1 KEY RESOURCES

- "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| U-0             | U-0                                                                                                                                               | R/W-0            | R/W-0      | R/W-0                              | R/W-0  | R/W-0           | R/W-0 |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------|------------------------------------|--------|-----------------|-------|--|--|--|--|

| —               | —                                                                                                                                                 |                  |            | RP57                               | R<5:0> |                 |       |  |  |  |  |

| bit 15          |                                                                                                                                                   |                  |            |                                    |        |                 | bit 8 |  |  |  |  |

|                 |                                                                                                                                                   |                  |            |                                    |        |                 |       |  |  |  |  |

| U-0             | U-0                                                                                                                                               | R/W-0            | R/W-0      | R/W-0                              | R/W-0  | R/W-0           | R/W-0 |  |  |  |  |

| _               | —                                                                                                                                                 |                  | RP56R<5:0> |                                    |        |                 |       |  |  |  |  |

| bit 7           |                                                                                                                                                   |                  |            |                                    |        |                 | bit 0 |  |  |  |  |

|                 |                                                                                                                                                   |                  |            |                                    |        |                 |       |  |  |  |  |

| Legend:         |                                                                                                                                                   |                  |            |                                    |        |                 |       |  |  |  |  |

| R = Readable I  | bit                                                                                                                                               | W = Writable     | bit        | U = Unimplemented bit, read as '0' |        |                 |       |  |  |  |  |

| -n = Value at P | OR                                                                                                                                                | '1' = Bit is set | :          | '0' = Bit is clea                  | ared   | x = Bit is unkr | iown  |  |  |  |  |

|                 |                                                                                                                                                   |                  |            |                                    |        |                 |       |  |  |  |  |

| bit 15-14       | Unimplemen                                                                                                                                        | ted: Read as '   | 0'         |                                    |        |                 |       |  |  |  |  |

| bit 13-8        | bit 13-8 <b>RP57R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP57 Output Pin bits (see Table 11-3 for peripheral function numbers) |                  |            |                                    |        |                 |       |  |  |  |  |

| bit 7-6         | Unimplemented: Read as '0'                                                                                                                        |                  |            |                                    |        |                 |       |  |  |  |  |

## REGISTER 11-24: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| (see Table 11-3 for peripheral function numbers) |

|--------------------------------------------------|

|                                                  |

## REGISTER 11-25: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP97  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

RP56R<5:0>: Peripheral Output Function is Assigned to RP56 Output Pin bits

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   |     | —   | —   |     | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP97R<5:0>:** Peripheral Output Function is Assigned to RP97 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-0 Unimplemented: Read as '0'

bit 5-0

# 13.2 Timer Control Registers

| R/W-0         | U-0                                                                                                                                     | R/W-0                                                                                                                        | U-0            | U-0              | U-0             | U-0             | U-0   |  |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|--|

| TON           |                                                                                                                                         | TSIDL                                                                                                                        | —              | _                |                 |                 | _     |  |  |  |  |  |  |

| bit 15        |                                                                                                                                         |                                                                                                                              |                |                  |                 |                 | bit 8 |  |  |  |  |  |  |

|               |                                                                                                                                         |                                                                                                                              |                |                  |                 |                 |       |  |  |  |  |  |  |

| U-0           | R/W-0                                                                                                                                   | R/W-0                                                                                                                        | R/W-0          | R/W-0            | U-0             | R/W-0           | U-0   |  |  |  |  |  |  |

| _             | TGATE                                                                                                                                   | TCKPS1                                                                                                                       | TCKPS0         | T32              | _               | TCS             | _     |  |  |  |  |  |  |

| bit 7         |                                                                                                                                         |                                                                                                                              |                |                  |                 |                 | bit ( |  |  |  |  |  |  |

| <u> </u>      |                                                                                                                                         |                                                                                                                              |                |                  |                 |                 |       |  |  |  |  |  |  |

| Legend:       | - 1-:4                                                                                                                                  |                                                                                                                              |                | II II.           |                 |                 |       |  |  |  |  |  |  |

| R = Readable  |                                                                                                                                         | W = Writable                                                                                                                 |                | -                | nented bit, rea |                 |       |  |  |  |  |  |  |

| -n = Value at | PUR                                                                                                                                     | '1' = Bit is set                                                                                                             |                | '0' = Bit is cle | areo            | x = Bit is unkn | own   |  |  |  |  |  |  |

| bit 15        | TON. Timery                                                                                                                             | On hit                                                                                                                       |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | When T32 = 2                                                                                                                            | TON: Timerx On bit<br>When T32 = 1                                                                                           |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | 1 = Starts 32-                                                                                                                          | bit Timerx/y                                                                                                                 |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | •                                                                                                                                       | 0 = Stops 32-bit Timerx/y                                                                                                    |                |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                                                                                                                         | <u>When T32 = 0:</u><br>1 = Starts 16-bit Timerx                                                                             |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | 0 = Stops 16-bit Timerx                                                                                                                 |                                                                                                                              |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 14        | Unimplemen                                                                                                                              | Unimplemented: Read as '0'                                                                                                   |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 13        | TSIDL: Timerx Stop in Idle Mode bit                                                                                                     |                                                                                                                              |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul> |                                                                                                                              |                |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                                                                                                                         | -                                                                                                                            |                | ode              |                 |                 |       |  |  |  |  |  |  |

| bit 12-7      | -                                                                                                                                       | ted: Read as '                                                                                                               |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 6         | TGATE: Timerx Gated Time Accumulation Enable bit                                                                                        |                                                                                                                              |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | $\frac{\text{When TCS} = 1}{\text{This bit is ignored.}}$                                                                               |                                                                                                                              |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | When TCS = $0$ :                                                                                                                        |                                                                                                                              |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | 1 = Gated time accumulation is enabled                                                                                                  |                                                                                                                              |                |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                                                                                                                         | 0 = Gated time accumulation is disabled                                                                                      |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 5-4       |                                                                                                                                         | : Timerx Input                                                                                                               | Clock Prescal  | e Select bits    |                 |                 |       |  |  |  |  |  |  |

|               | 11 = 1:256<br>10 = 1:64                                                                                                                 | 11 = 1:256                                                                                                                   |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | 01 = 1:8                                                                                                                                |                                                                                                                              |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | 00 = 1:1                                                                                                                                |                                                                                                                              |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 3         | T32: 32-Bit Ti                                                                                                                          | mer Mode Sele                                                                                                                | ect bit        |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                                                                                                                         | <ul> <li>1 = Timerx and Timery form a single 32-bit timer</li> <li>0 = Timerx and Timery act as two 16-bit timers</li> </ul> |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 2         | Unimplemen                                                                                                                              | ted: Read as '                                                                                                               | )'             |                  |                 |                 |       |  |  |  |  |  |  |

| bit 1         | TCS: Timerx                                                                                                                             | Clock Source S                                                                                                               | elect bit      |                  |                 |                 |       |  |  |  |  |  |  |

|               | 1 = External c<br>0 = Internal cl                                                                                                       | clock is from pir<br>lock (FP)                                                                                               | n, TxCK (on th | ne rising edge)  |                 |                 |       |  |  |  |  |  |  |

| bit 0         | Unimplomon                                                                                                                              | ted: Read as '                                                                                                               | ı'             |                  |                 |                 |       |  |  |  |  |  |  |

# REGISTER 13-1: TxCON: (TIMER2 AND TIMER4) CONTROL REGISTER

#### 16.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FOSCSEL<6>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring, PWMLOCK = 0. To gain write access to these locked registers, the user application must write two consecutive values of (0xABCD and 0x4321) to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 16-1.

#### EXAMPLE 16-1: PWMx WRITE-PROTECTED REGISTER UNLOCK SEQUENCE

|                                                                                                          | ; FLT32 pin must be pulled low externally in order to clear and disable the fault<br>; Writing to FCLCON1 register requires unlock sequence                                                                                                                                                       |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0x0000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,FCLCON1</pre> | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of FCLCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to FCLCON1 register</pre> |  |  |  |  |  |  |  |  |

| -                                                                                                        | d polarity using the IOCON1 register<br>gister requires unlock sequence                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0xF000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,IOCON1</pre>  | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of IOCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to IOCON1 register</pre>   |  |  |  |  |  |  |  |  |

## REGISTER 17-13: QEI1LECH: QEI1 LESS THAN OR EQUAL COMPARE HIGH WORD REGISTER

| R/W-0                                                                      | R/W-0                                                                | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|----------------------------------------------------------------------------|----------------------------------------------------------------------|-------|-------|----------|-------|-------|-------|--|--|--|--|

|                                                                            |                                                                      |       | QEILE | C<31:24> |       |       |       |  |  |  |  |

| bit 15                                                                     | bit 15 bit 8                                                         |       |       |          |       |       |       |  |  |  |  |

|                                                                            |                                                                      |       |       |          |       |       |       |  |  |  |  |

| R/W-0                                                                      | R/W-0                                                                | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|                                                                            |                                                                      |       | QEILE | C<23:16> |       |       |       |  |  |  |  |

| bit 7                                                                      |                                                                      |       |       |          |       |       | bit 0 |  |  |  |  |

|                                                                            |                                                                      |       |       |          |       |       |       |  |  |  |  |

| Legend:                                                                    |                                                                      |       |       |          |       |       |       |  |  |  |  |

| R = Readable                                                               | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |       |          |       |       |       |  |  |  |  |

| -n = Value at POR (1' = Bit is set (0' = Bit is cleared x = Bit is unknown |                                                                      |       |       |          |       |       | nown  |  |  |  |  |

bit 15-0 QEILEC<31:16>: High Word Used to Form 32-Bit Less Than or Equal Compare Register (QEI1LEC) bits

# REGISTER 17-14: QEI1LECL: QEI1 LESS THAN OR EQUAL COMPARE LOW WORD REGISTER

| R = Readable bit<br>-n = Value at POR |       | W = Writable bit<br>'1' = Bit is set |       | U = Unimplemented bit, rea<br>'0' = Bit is cleared |       | ead as '0'<br>x = Bit is unknown |       |

|---------------------------------------|-------|--------------------------------------|-------|----------------------------------------------------|-------|----------------------------------|-------|

| Legend:                               |       |                                      |       |                                                    |       |                                  |       |

|                                       |       |                                      |       |                                                    |       |                                  |       |

| bit 7                                 |       |                                      |       |                                                    |       |                                  | bit   |

|                                       |       |                                      | QEIL  | EC<7:0>                                            |       |                                  |       |

| R/W-0                                 | R/W-0 | R/W-0                                | R/W-0 | R/W-0                                              | R/W-0 | R/W-0                            | R/W-0 |

| bit 15                                |       |                                      |       |                                                    |       |                                  | bit   |

|                                       |       |                                      | QEILE | EC<15:8>                                           |       |                                  |       |

| R/W-0                                 | R/W-0 | R/W-0                                | R/W-0 | R/W-0                                              | R/W-0 | R/W-0                            | R/W-0 |

bit 15-0 QEILEC<15:0>: Low Word Used to Form 32-Bit Less Than or Equal Compare Register (QEI1LEC) bits

# **19.2** I<sup>2</sup>C Control Registers

#### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER

| R/W-0        | U-0                          | R/W-0                                  | R/W-1, HC                  | R/W-0                        | R/W-0            | R/W-0           | R/W-0          |

|--------------|------------------------------|----------------------------------------|----------------------------|------------------------------|------------------|-----------------|----------------|

| I2CEN        | _                            | I2CSIDL                                | SCLREL                     | IPMIEN <sup>(1)</sup>        | A10M             | DISSLW          | SMEN           |

| bit 15       |                              |                                        |                            |                              |                  |                 | bit 8          |

|              |                              |                                        |                            |                              |                  |                 |                |

| R/W-0        | R/W-0                        | R/W-0                                  | R/W-0, HC                  | R/W-0, HC                    | R/W-0, HC        | R/W-0, HC       | R/W-0, HC      |

| GCEN         | STREN                        | ACKDT                                  | ACKEN                      | RCEN                         | PEN              | RSEN            | SEN            |

| bit 7        |                              |                                        |                            |                              |                  |                 | bit 0          |

| Legend:      |                              | HC = Hardware                          | Cloarable bit              |                              |                  |                 |                |

| R = Readab   | le hit                       | W = Writable bi                        |                            | II = I Inimpler              | mented bit, rea  | d as '0'        |                |

| -n = Value a |                              | '1' = Bit is set                       | L .                        | '0' = Bit is cle             |                  | x = Bit is unk  | nown           |

|              |                              |                                        |                            |                              |                  |                 | nown           |

| bit 15       | <b>12CEN:</b> 12Cx           | Enable bit                             |                            |                              |                  |                 |                |

|              |                              | he I2Cx module                         |                            |                              |                  |                 | ;              |

|              | 0 = Disables                 | the I2Cx module;                       | all l <sup>2</sup> C™ pins | are controlled               | by port functior | ıs              |                |

| bit 14       | Unimplemen                   | ted: Read as '0'                       |                            |                              |                  |                 |                |

| bit 13       |                              | x Stop in Idle Mo                      |                            |                              |                  |                 |                |

|              |                              | ues module oper<br>s module operation  |                            |                              | dle mode         |                 |                |

| bit 12       |                              | Lx Release Conf                        |                            | _                            | ( clave)         |                 |                |

|              | 1 = Releases                 |                                        |                            |                              | slave)           |                 |                |

|              |                              | Lx clock low (clo                      | ck stretch)                |                              |                  |                 |                |

|              | If STREN = 1                 | <u>:</u>                               | -                          |                              |                  |                 |                |

|              | •                            | ., software can w                      |                            |                              |                  | ,               |                |

|              |                              | ing of every slav<br>reception. Hardw  |                            |                              |                  |                 | t every slave  |

|              | If STREN = 0                 | -                                      |                            |                              |                  |                 |                |

|              |                              | <u>.</u><br>, software can or          | nly write '1' to re        | elease clock). I             | Hardware is cle  | ar at the begir | ning of every  |

|              | -                            | te transmission.                       |                            |                              | -                | address byte re | eception.      |

| bit 11       |                              | ligent Peripheral                      |                            |                              |                  |                 |                |

|              | 1 = IPMI mod<br>0 = IPMI mod | e is enabled; all                      | addresses are              | Acknowledged                 | 1                |                 |                |

| bit 10       |                              | Slave Address b                        | i+                         |                              |                  |                 |                |

|              |                              | is a 10-bit slave                      |                            |                              |                  |                 |                |

|              |                              | is a 7-bit slave a                     |                            |                              |                  |                 |                |

| bit 9        | DISSLW: Dis                  | able Slew Rate C                       | Control bit                |                              |                  |                 |                |

|              |                              | control is disable                     |                            |                              |                  |                 |                |

|              |                              | control is enable                      |                            |                              |                  |                 |                |

| bit 8        |                              | us Input Levels b                      |                            | 0145                         | <b>c</b>         |                 |                |

|              |                              | /O pin thresholds<br>SMBus input thre  |                            | n SMBus speci                | fication         |                 |                |

| bit 7        |                              | ral Call Enable b                      |                            | ing as I <sup>2</sup> C slav | /e)              |                 |                |

|              | 1 = Enables in               | terrupt when a ge<br>all address disat | neral call addre           | -                            |                  | dule is enabled | for reception) |

|              |                              |                                        |                            |                              |                  |                 |                |

Note 1: When performing master operations, ensure that the IPMIEN bit is set to '0'.

| R/W-0                                                | R/W-0                        | R/W-0                                                                                                                      | R/W-0                                          | R/W-0                              | R/W-0          | R/W-0              | R/W-0  |  |

|------------------------------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------|----------------|--------------------|--------|--|

|                                                      | F15B                         | P<3:0>                                                                                                                     |                                                | F14BP<3:0>                         |                |                    |        |  |

| bit 15                                               |                              |                                                                                                                            |                                                |                                    |                |                    | bit 8  |  |

| R/W-0                                                | R/W-0                        | R/W-0                                                                                                                      | R/W-0                                          | R/W-0                              | R/W-0          | R/W-0              | R/W-0  |  |

| 1010 0                                               |                              | P<3:0>                                                                                                                     | 10110                                          |                                    |                | P<3:0>             | 1010 0 |  |

| bit 7                                                |                              |                                                                                                                            |                                                |                                    |                |                    | bit 0  |  |

| Legend:                                              |                              |                                                                                                                            |                                                |                                    |                |                    |        |  |

| R = Readabl                                          | e bit                        | W = Writable bit                                                                                                           |                                                | U = Unimplemented bit, read as '0' |                |                    |        |  |

| -n = Value at                                        | t POR                        | '1' = Bit is set                                                                                                           |                                                | '0' = Bit is cleared               |                | x = Bit is unknown |        |  |

| bit 15-12                                            | 1111 = Filte<br>1110 = Filte | RX Buffer Ma<br>r hits received in<br>r hits received in<br>r hits received in<br>r hits received in<br>r hits received in | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | ıffer<br>4                         |                |                    |        |  |

| bit 11-8                                             | F14BP<3:0;                   | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 4 bits (same val                   | ues as bits<15 | :12>)              |        |  |

| bit 7-4                                              | F13BP<3:0;                   | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 3 bits (same val                   | ues as bits<15 | :12>)              |        |  |

| bit 3-0 F12BP<3:0>: RX Buffer Mask for Filter 12 bit |                              | 2 bits (same val                                                                                                           | ues as bits<15                                 | :12>)                              |                |                    |        |  |

## REGISTER 21-15: CxBUFPNT4: ECANx FILTER 12-15 BUFFER POINTER REGISTER 4

## REGISTER 23-1: AD1CON1: ADC1 CONTROL REGISTER 1 (CONTINUED)

| bit 7-5 | SSRC<2:0>: Sample Trigger Source Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | If SSRCG = 1:<br>111 = Reserved<br>110 = PTGO15 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>101 = PTGO14 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>100 = PTGO13 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>011 = PTGO12 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>010 = PWM Generator 3 primary trigger compare ends sampling and starts conversion <sup>(2)</sup><br>001 = PWM Generator 2 primary trigger compare ends sampling and starts conversion <sup>(2)</sup><br>000 = PWM Generator 1 primary trigger compare ends sampling and starts conversion <sup>(2)</sup> |

|         | If SSRCG = 0:<br>111 = Internal counter ends sampling and starts conversion (auto-convert)<br>110 = CTMU ends sampling and starts conversion<br>101 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | <ul> <li>101 - Reserved</li> <li>100 = Timer5 compare ends sampling and starts conversion</li> <li>011 = PWM primary Special Event Trigger ends sampling and starts conversion</li> <li>010 = Timer3 compare ends sampling and starts conversion</li> <li>001 = Active transition on the INT0 pin ends sampling and starts conversion</li> <li>000 = Clearing the Sample bit (SAMP) ends sampling and starts conversion (Manual mode)</li> </ul>                                                                                                                                                                                                                                                                        |

| bit 4   | SSRCG: Sample Trigger Source Group bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | See SSRC<2:0> for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 3   | <ul> <li>SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS&lt;1:0&gt; = 01 or 1x)</li> <li><u>In 12-bit mode (AD21B = 1), SIMSAM is Unimplemented and is Read as '0':</u></li> <li>1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS&lt;1:0&gt; = 1x); or samples CH0 and CH1 simultaneously (when CHPS&lt;1:0&gt; = 01)</li> <li>0 = Samples multiple channels individually in sequence</li> </ul>                                                                                                                                                                                                                                                                                              |

| bit 2   | ASAM: ADC1 Sample Auto-Start bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = Sampling begins immediately after the last conversion; SAMP bit is auto-set</li> <li>0 = Sampling begins when the SAMP bit is set</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| bit 1   | SAMP: ADC1 Sample Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = ADC Sample-and-Hold amplifiers are sampling</li> <li>0 = ADC Sample-and-Hold amplifiers are holding</li> <li>If ASAM = 0, software can write '1' to begin sampling. Automatically set by hardware if ASAM = 1. If SSRC&lt;2:0&gt; = 000, software can write '0' to end sampling and start conversion. If SSRC&lt;2:0&gt; ≠ 000, automatically cleared by hardware to end sampling and start conversion.</li> </ul>                                                                                                                                                                                                                                                                                         |

| bit 0   | DONE: ADC1 Conversion Status bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         | <ul> <li>1 = ADC conversion cycle has completed</li> <li>0 = ADC conversion has not started or is in progress</li> <li>Automatically set by hardware when the ADC conversion is complete. Software can write '0' to clear the DONE status bit (software is not allowed to write '1'). Clearing this bit does NOT affect any operation in progress. Automatically cleared by hardware at the start of a new conversion.</li> </ul>                                                                                                                                                                                                                                                                                       |

| Note 1: | See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

- 2: This setting is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- **3:** Do not clear the DONE bit in software if Auto-Sample is enabled (ASAM = 1).

|              | R/W-0         | U-0                 | U-0                         | U-0             | R/W-0                                | R/W-0                | R/W-0                |

|--------------|---------------|---------------------|-----------------------------|-----------------|--------------------------------------|----------------------|----------------------|

| CSS31        | CSS30         | —                   | —                           | _               | CSS26 <sup>(2)</sup>                 | CSS25 <sup>(2)</sup> | CSS24 <sup>(2)</sup> |

| bit 15       | - 1           |                     |                             |                 |                                      |                      | bit 8                |

|              |               |                     |                             |                 |                                      |                      |                      |

| U-0          | U-0           | U-0                 | U-0                         | U-0             | U-0                                  | U-0                  | U-0                  |

| _            |               | _                   | _                           | _               |                                      | _                    |                      |

| bit 7        |               |                     |                             |                 |                                      |                      | bit (                |

|              |               |                     |                             |                 |                                      |                      |                      |

| Legend:      |               |                     |                             |                 |                                      |                      |                      |

| R = Readab   | le bit        | W = Writable        | bit                         | U = Unimple     | emented bit, read                    | d as '0'             |                      |

| -n = Value a | t POR         | '1' = Bit is set    |                             | '0' = Bit is cl | eared                                | x = Bit is unk       | nown                 |

|              |               |                     |                             |                 |                                      |                      |                      |

| bit 15       |               | 1 Input Scan S      |                             |                 |                                      |                      |                      |

|              |               |                     |                             |                 | input scan (Ope                      |                      |                      |

|              | •             | •                   |                             | surement for ir | nput scan (Open                      | )                    |                      |

| bit 14       |               | 1 Input Scan S      |                             |                 |                                      |                      |                      |

|              |               |                     |                             |                 | or input scan (CT<br>input scan (CTN |                      |                      |

| bit 13-11    | Unimplemen    | ted: Read as '      | 0'                          |                 |                                      |                      |                      |

| bit 10       | CSS26: ADC    | 1 Input Scan S      | election bit <sup>(2)</sup> |                 |                                      |                      |                      |

|              | 1 = Selects C | )<br>A3/AN6 for inp | ut scan                     |                 |                                      |                      |                      |

|              | 0 = Skips OA  | 3/AN6 for input     | scan                        |                 |                                      |                      |                      |

| bit 9        | CSS25: ADC    | 1 Input Scan S      | election bit <sup>(2)</sup> |                 |                                      |                      |                      |

|              | 1 = Selects C | 0A2/AN0 for inp     | ut scan                     |                 |                                      |                      |                      |

|              | 0 = Skips OA  | 2/AN0 for input     | scan                        |                 |                                      |                      |                      |

| bit 8        | CSS24: ADC    | 1 Input Scan S      | election bit <sup>(2)</sup> |                 |                                      |                      |                      |

|              |               | 0A1/AN3 for inp     |                             |                 |                                      |                      |                      |

|              | 0 = Skips OA  | 1/AN3 for input     | scan                        |                 |                                      |                      |                      |

|              |               |                     |                             |                 |                                      |                      |                      |

# REGISTER 23-7: AD1CSSH: ADC1 INPUT SCAN SELECT REGISTER HIGH<sup>(1)</sup>

2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

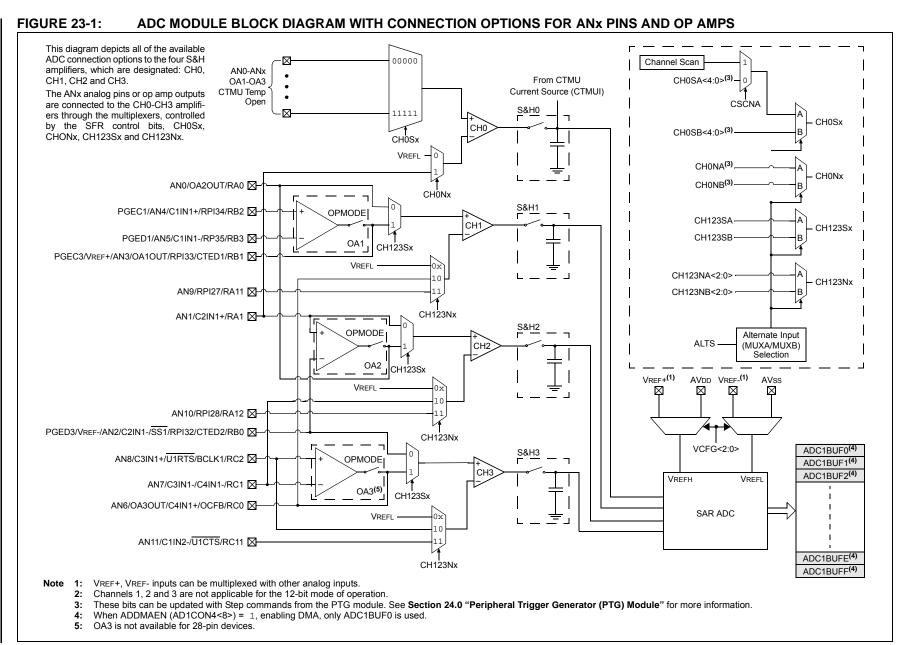

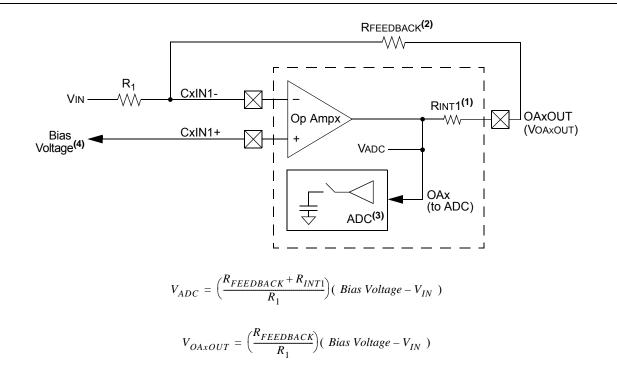

## 25.1 Op Amp Application Considerations

There are two configurations to take into consideration when designing with the op amp modules that available in the dsPIC33EPXXXGP50X. are dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X devices. Configuration A (see Figure 25-6) takes advantage of the internal connection to the ADC module to route the output of the op amp directly to the ADC for measurement. Configuration B (see Figure 25-7) requires that the designer externally route the output of the op amp (OAxOUT) to a separate analog input pin (ANy) on the device. Table 30-55 in Section 30.0 "Electrical Characteristics" describes the performance characteristics for the op amps, distinguishing between the two configuration types where applicable.

## 25.1.1 OP AMP CONFIGURATION A

Figure 25-6 shows a typical inverting amplifier circuit taking advantage of the internal connections from the op amp output to the input of the ADC. The advantage of this configuration is that the user does not need to consume another analog input (ANy) on the device, and allows the user to simultaneously sample all three op amps with the ADC module, if needed. However, the presence of the internal resistance, RINT1, adds an error in the feedback path. Since RINT1 is an internal resistance, in relation to the op amp output (VOAXOUT) and ADC internal connection (VADC), RINT1 must be included in the numerator term of the transfer function. See Table 30-53 in Section 30.0 "Electrical Characteristics" for the typical value of RINT1. Table 30-60 and Table 30-61 in Section 30.0 "Electrical Characteristics" describe the minimum sample time (TSAMP) requirements for the ADC module in this configuration. Figure 25-6 also defines the equations that should be used when calculating the expected voltages at points, VADC and VOAXOUT.

#### FIGURE 25-6: OP AMP CONFIGURATION A

Note 1: See Table 30-53 for the Typical value.