Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128mc202-h-mm |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

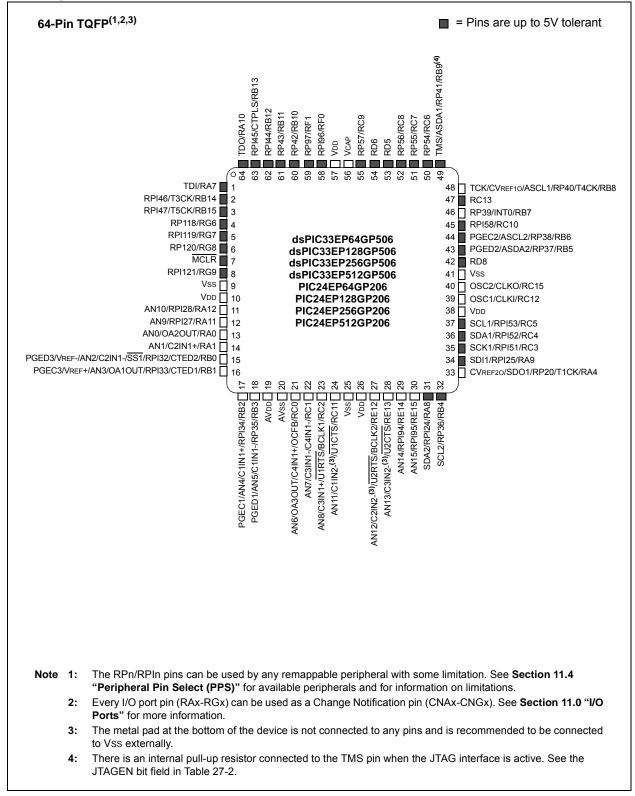

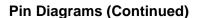

#### **Pin Diagrams (Continued)**

| TABLE        | 4-2:  | CPU C  | CORE RE | EGISTER | R MAP F | FOR PIC | 24EPX) | XGP/M | C20X D   | EVICES   | ONLY   |       |           |          |       |       |       |               |

|--------------|-------|--------|---------|---------|---------|---------|--------|-------|----------|----------|--------|-------|-----------|----------|-------|-------|-------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8    | Bit 7    | Bit 6  | Bit 5 | Bit 4     | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| W0           | 0000  |        |         |         |         |         |        |       | W0 (WR   | EG)      |        |       |           |          |       |       |       | xxxx          |

| W1           | 0002  |        |         |         |         |         |        |       | W1       |          |        |       |           |          |       |       |       | xxxx          |

| W2           | 0004  |        |         |         |         |         |        |       | W2       |          |        |       |           |          |       |       |       | xxxx          |

| W3           | 0006  |        |         |         |         |         |        |       | W3       |          |        |       |           |          |       |       |       | xxxx          |

| W4           | 0008  |        |         |         |         |         |        |       | W4       |          |        |       |           |          |       |       |       | xxxx          |

| W5           | 000A  |        |         |         |         |         |        |       | W5       |          |        |       |           |          |       |       |       | xxxx          |

| W6           | 000C  |        |         |         |         |         |        |       | W6       |          |        |       |           |          |       |       |       | xxxx          |

| W7           | 000E  |        |         |         |         |         |        |       | W7       |          |        |       |           |          |       |       |       | xxxx          |

| W8           | 0010  |        |         |         |         |         |        |       | W8       |          |        |       |           |          |       |       |       | xxxx          |

| W9           | 0012  |        |         |         |         |         |        |       | W9       |          |        |       |           |          |       |       |       | xxxx          |

| W10          | 0014  |        |         |         |         |         |        |       | W10      |          |        |       |           |          |       |       |       | xxxx          |

| W11          | 0016  |        |         |         |         |         |        |       | W11      |          |        |       |           |          |       |       |       | xxxx          |

| W12          | 0018  |        |         |         |         |         |        |       | W12      |          |        |       |           |          |       |       |       | xxxx          |

| W13          | 001A  |        |         |         |         |         |        |       | W13      |          |        |       |           |          |       |       |       | xxxx          |

| W14          | 001C  |        |         |         |         |         |        |       | W14      |          |        |       |           |          |       |       |       | xxxx          |

| W15          | 001E  |        |         |         |         |         |        |       | W15      |          |        |       |           |          |       |       |       | xxxx          |

| SPLIM        | 0020  |        |         |         |         |         |        |       | SPLIM<1  | 5:0>     |        |       |           |          |       |       |       | 0000          |

| PCL          | 002E  |        |         |         |         |         |        | P     | CL<15:1> |          |        |       |           |          |       |       | —     | 0000          |

| PCH          | 0030  | —      | -       | _       | _       | —       | —      | —     | —        | _        |        |       |           | PCH<6:0> |       |       |       | 0000          |

| DSRPAG       | 0032  | —      | -       | _       | _       | —       | —      |       |          |          |        | DSRPA | G<9:0>    |          |       |       |       | 0001          |

| DSWPAG       | 0034  | _      |         |         |         | _       |        | _     |          |          |        | DS    | SWPAG<8:0 | >        |       |       |       | 0001          |

| RCOUNT       | 0036  |        |         |         |         |         |        |       | RCOUNT<  | 15:0>    |        |       |           |          |       |       |       | 0000          |

| SR           | 0042  | _      |         |         |         | —       |        | _     | DC       | IPL2     | IPL1   | IPL0  | RA        | N        | OV    | Z     | С     | 0000          |

| CORCON       | 0044  | VAR    | _       | -       | _       | —       |        | —     | _        | -        | _      | —     | -         | IPL3     | SFA   | —     | _     | 0020          |

| DISICNT      | 0052  | _      | _       |         |         |         |        |       |          | DISICNT< | :13:0> |       |           |          |       |       |       | 0000          |

| TBLPAG       | 0054  | _      | _       | -       | _       | —       |        | —     | _        |          |        |       | TBLPA     | G<7:0>   |       |       |       | 0000          |

| MSTRPR       | 0058  |        |         |         |         |         |        |       | MSTRPR<  | 15:0>    |        |       |           |          |       |       |       | 0000          |

#### **D** I -4.0 - -

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-45: DMAC REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|---------|--------|--------|--------|---------------|

| DMA0CON   | 0B00  | CHEN   | SIZE   | DIR    | HALF   | NULLW  |        | _     | _      | _     | _     | AMOD  | E<1:0> | _       | _      | MODE   | <1:0>  | 0000          |

| DMA0REQ   | 0B02  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       | •     | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA0STAL  | 0B04  |        |        |        |        |        |        |       | STA<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0STAH  | 0B06  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA0STBL  | 0B08  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0STBH  | 0B0A  | _      | —      | _      | _      | _      | —      | —     | —      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA0PAD   | 0B0C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0CNT   | 0B0E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA1CON   | 0B10  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | —     | —      | _     | —     | AMOD  | E<1:0> | —       | —      | MODE   | <1:0>  | 0000          |

| DMA1REQ   | 0B12  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA1STAL  | 0B14  |        |        |        |        |        |        |       | STA<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1STAH  | 0B16  | _      | —      | _      | _      | _      | _      | —     | —      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA1STBL  | 0B18  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1STBH  | 0B1A  | _      | _      | _      | _      |        | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA1PAD   | 0B1C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1CNT   | 0B1E  | _      | —      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA2CON   | 0B20  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | —      | _     | _      | _     | _     | AMOD  | E<1:0> |         | —      | MODE   | <1:0>  | 0000          |

| DMA2REQ   | 0B22  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA2STAL  | 0B24  |        |        |        |        |        |        |       | STA<18 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2STAH  | 0B26  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA2STBL  | 0B28  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2STBH  | 0B2A  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA2PAD   | 0B2C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2CNT   | 0B2E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA3CON   | 0B30  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _      | _     | _     | AMOD  | E<1:0> | -       | —      | MODE   | <1:0>  | 0000          |

| DMA3REQ   | 0B32  | FORCE  | _      | _      | _      | _      | _      | _     | _      |       |       |       | IRQSE  | L<7:0>  |        |        |        | 00FF          |

| DMA3STAL  | 0B34  |        |        |        |        |        |        |       | STA<18 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3STAH  | 0B36  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA3STBL  | 0B38  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3STBH  | 0B3A  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA3PAD   | 0B3C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3CNT   | 0B3E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMAPWC    | 0BF0  | —      | —      | —      | —      | —      | —      |       | _      | —     | —     |       | —      | PWCOL3  | PWCOL2 | PWCOL1 | PWCOL0 | 0000          |

| DMARQC    | 0BF2  | _      | —      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      | RQCOL3  | RQCOL2 | RQCOL1 | RQCOL0 | 0000          |

| DMAPPS    | 0BF4  | _      | —      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      | PPST3   | PPST2  | PPST1  | PPST0  | 0000          |

| DMALCA    | 0BF6  | _      | _      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      |         | LSTCH  | 1<3:0> |        | 000F          |

| DSADRL    | 0BF8  |        |        |        |        |        |        |       | DSADR< | 15:0> |       |       |        |         |        |        |        | 0000          |

| DSADRH    | 0BFA  | _      | —      | —      | —      | —      | —      | —     | —      |       |       |       | DSADR• | <23:16> |        |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2013 Microchip Technology Inc.

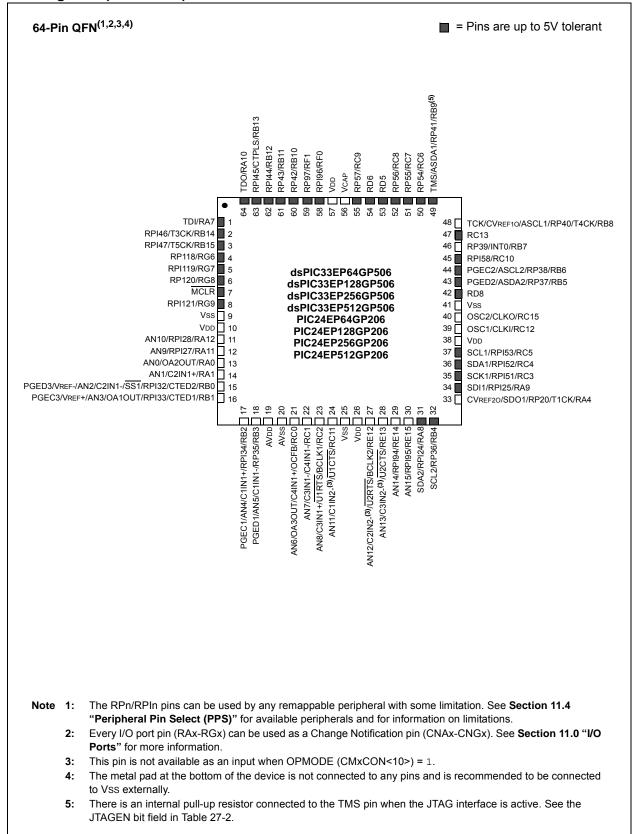

#### 4.8.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the Program Space without going through Data Space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a Program Space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit-wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from Program Space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the Program Space location (P<15:0>) to a data address (D<15:0>)

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>) is always '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a Program Space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user application and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

### FIGURE 4-23: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

| U-0     | U-0 | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   |

|---------|-----|-------|-------|-------|-------|-------|-------|

| —       | —   | —     | —     | —     | —     | —     | —     |

| bit 15  |     |       |       |       |       |       | bit 8 |

|         |     |       |       |       |       |       |       |

| U-0     | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —       | —   | TUN5  | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7   |     |       |       |       |       |       | bit 0 |

|         |     |       |       |       |       |       |       |

| Logondi |     |       |       |       |       |       |       |

#### REGISTER 9-4: OSCTUN: FRC OSCILLATOR TUNING REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **TUN<5:0>:** FRC Oscillator Tuning bits 011111 = Maximum frequency deviation of 1.453% (7.477 MHz) 011110 = Center frequency + 1.406% (7.474 MHz) •••• 000001 = Center frequency + 0.047% (7.373 MHz) 000000 = Center frequency (7.37 MHz nominal) 111111 = Center frequency - 0.047% (7.367 MHz) ••• 100001 = Center frequency - 1.453% (7.263 MHz) 100000 = Minimum frequency deviation of -1.5% (7.259 MHz)

#### 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs other than VDD by using external pull-up resistors. The maximum open-drain voltage allowed on any pin is the same as the maximum VIH specification for that particular pin.

See the **"Pin Diagrams"** section for the available 5V tolerant pins and Table 30-11 for the maximum VIH specification for each pin.

#### 11.2 Configuring Analog and Digital Port Pins

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

Pins with analog functions affected by the ANSELx registers are listed with a buffer type of analog in the Pinout I/O Descriptions (see Table 1-1).

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or comparator module.

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 11.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP, as shown in Example 11-1.

#### **11.3** Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State.

Three control registers are associated with the Change Notification (CN) functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups and pulldowns act as a current source or sink source connected to the pin and eliminate the need for external resistors when push button, or keypad devices are connected. The pull-ups and pull-downs are enabled separately, using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

| Note: | Pull-ups and pull-downs on Change Noti-      |

|-------|----------------------------------------------|

|       | fication pins should always be disabled      |

|       | when the port pin is configured as a digital |

|       | output.                                      |

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, W0 | ; Configure PORTB<15:8> |

|------|------------|-------------------------|

|      |            | ; as inputs             |

| MOV  | W0, TRISB  | ; and PORTB<7:0>        |

|      |            | ; as outputs            |

| NOP  |            | ; Delay 1 cycle         |

| BTSS | PORTB, #13 | ; Next Instruction      |

|      |            |                         |

| Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment | Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment |

|--------------------------------------------------|------------------|----------------|--------------------------------------------------|------------------|----------------|

| 010 1000                                         | I/O              | RP40           | 101 0101                                         | —                | _              |

| 010 1001                                         | I/O              | RP41           | 101 0110                                         | —                | —              |

| 010 1010                                         | I/O              | RP42           | 101 0111                                         | —                | —              |

| 010 1011                                         | I/O              | RP43           | 101 1000                                         |                  | —              |

| 010 1100                                         | I                | RPI44          | 101 1001                                         |                  | —              |

| 101 1010                                         | —                | _              | 110 1101                                         | —                | _              |

| 101 1011                                         | —                | —              | 110 1110                                         |                  | —              |

| 101 1100                                         | —                | —              | 110 1111                                         |                  | —              |

| 101 1101                                         | —                | _              | 111 0000                                         | —                | _              |

| 101 1110                                         | 1                | RPI94          | 111 0001                                         |                  | _              |

| 101 1111                                         | I                | RP195          | 111 0010                                         |                  | —              |

| 110 0000                                         | I                | RPI96          | 111 0011                                         | —                | —              |

| 110 0001                                         | I/O              | RP97           | 111 0100                                         |                  | —              |

| 110 0010                                         | —                | —              | 111 0101                                         |                  | —              |

| 110 0011                                         | —                | —              | 111 0110                                         | I/O              | RP118          |

| 110 0100                                         | —                | —              | 111 0111                                         | Ι                | RPI119         |

| 110 0101                                         | —                | —              | 111 1000                                         | I/O              | RP120          |

| 110 0110                                         | _                |                | 111 1001                                         | Ι                | RPI121         |

| 110 0111                                         |                  |                | 111 1010                                         | —                |                |

| 110 1000                                         | —                | _              | 111 1011                                         | —                | _              |

| 110 1001                                         | —                |                | 111 1100                                         | —                |                |

| 110 1010                                         |                  |                | 111 1101                                         | —                |                |

| 110 1011                                         | —                | _              | 111 1110                                         | —                |                |

| 110 1100                                         | —                | _              | 111 1111                                         | _                |                |

#### TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES (CONTINUED)

Legend: Shaded rows indicate PPS Input register values that are unimplemented.

Note 1: See Section 11.4.4.1 "Virtual Connections" for more information on selecting this pin assignment.

2: These inputs are available on dsPIC33EPXXXGP/MC50X devices only.

### 11.5 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 30-11, under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD - 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 2.4V @ IOH = -8 mA and VDD = 3.3VThe maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 30.0 "Electrical Characteristics" for additional information.

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input provided there is no external analog input, such as for a built-in self-test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

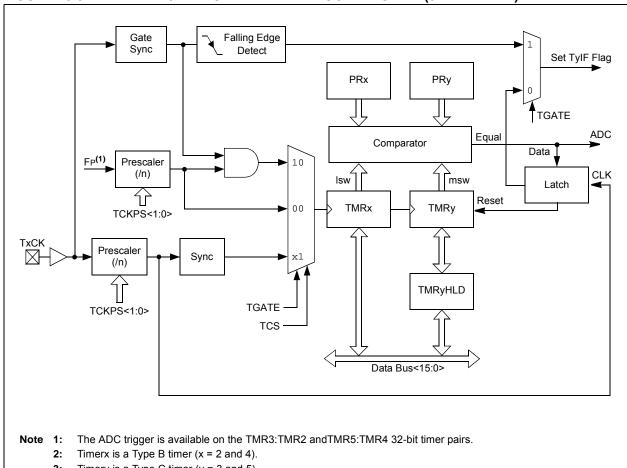

#### **FIGURE 13-3:** TYPE B/TYPE C TIMER PAIR BLOCK DIAGRAM (32-BIT TIMER)

3: Timery is a Type C timer (y = 3 and 5).

#### **Timerx/y Resources** 13.1

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/                                                                                      |

|       | wwwproducts/Devices.aspx?d<br>DocName=en555464                                                                 |

#### **KEY RESOURCES** 13.1.1

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 17-13: QEI1LECH: QEI1 LESS THAN OR EQUAL COMPARE HIGH WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0          | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|----------------|-----------------|-------|

|                 |       |                  | QEILE | C<31:24>          |                |                 |       |

| bit 15          |       |                  |       |                   |                |                 | bit 8 |

|                 |       |                  |       |                   |                |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0          | R/W-0           | R/W-0 |

|                 |       |                  | QEILE | C<23:16>          |                |                 |       |

| bit 7           |       |                  |       |                   |                |                 | bit 0 |

|                 |       |                  |       |                   |                |                 |       |

| Legend:         |       |                  |       |                   |                |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimplem      | ented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | red            | x = Bit is unkr | nown  |

bit 15-0 QEILEC<31:16>: High Word Used to Form 32-Bit Less Than or Equal Compare Register (QEI1LEC) bits

### REGISTER 17-14: QEI1LECL: QEI1 LESS THAN OR EQUAL COMPARE LOW WORD REGISTER

| R = Readable t |       | W = Writable<br>'1' = Bit is set |       | U = Unimplen<br>'0' = Bit is cle |       | ad as '0'<br>x = Bit is unknown |       |

|----------------|-------|----------------------------------|-------|----------------------------------|-------|---------------------------------|-------|

| Legend:        |       |                                  |       |                                  |       |                                 |       |

|                |       |                                  |       |                                  |       |                                 |       |

| bit 7          |       |                                  |       |                                  |       |                                 | bit   |

|                |       |                                  | QEIL  | EC<7:0>                          |       |                                 |       |

| R/W-0          | R/W-0 | R/W-0                            | R/W-0 | R/W-0                            | R/W-0 | R/W-0                           | R/W-0 |

| bit 15         |       |                                  |       |                                  |       |                                 | bit   |

|                |       |                                  | QEILE | EC<15:8>                         |       |                                 |       |

| R/W-0          | R/W-0 | R/W-0                            | R/W-0 | R/W-0                            | R/W-0 | R/W-0                           | R/W-0 |

bit 15-0 QEILEC<15:0>: Low Word Used to Form 32-Bit Less Than or Equal Compare Register (QEI1LEC) bits

#### REGISTER 21-6: CxINTF: ECANx INTERRUPT FLAG REGISTER (CONTINUED)

- bit 1 **RBIF:** RX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 **TBIF:** TX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

| U-0                          | U-0                                              | U-0                                   | U-0            | U-0          | U-0              | U-0             | U-0   |  |  |  |  |  |

|------------------------------|--------------------------------------------------|---------------------------------------|----------------|--------------|------------------|-----------------|-------|--|--|--|--|--|

| _                            | —                                                | —                                     |                | —            | —                | —               | _     |  |  |  |  |  |

| bit 15                       |                                                  |                                       |                |              |                  |                 | bit   |  |  |  |  |  |

|                              |                                                  |                                       |                |              |                  |                 |       |  |  |  |  |  |

| R/W-0                        | R/W-0                                            | R/W-0                                 | U-0            | R/W-0        | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |  |

| IVRIE                        | WAKIE                                            | ERRIE                                 | —              | FIFOIE       | RBOVIE           | RBIE            | TBIE  |  |  |  |  |  |

| bit 7                        |                                                  |                                       |                |              |                  |                 | bit   |  |  |  |  |  |

|                              |                                                  |                                       |                |              |                  |                 |       |  |  |  |  |  |

| <b>Legend:</b><br>R = Readab | la hit                                           | W = Writable b                        | .it            |              | montod bit rook  | l oo 'O'        |       |  |  |  |  |  |

| n = Value a                  |                                                  | '1' = Bit is set                      | אנ             | 0 = Onimpler | mented bit, read | x = Bit is unkr |       |  |  |  |  |  |

|                              | IL POR                                           | I = DILIS SEL                         |                |              | areu             |                 | IOWI  |  |  |  |  |  |

| bit 15-8                     | Unimplemen                                       | ted: Read as '0                       | ,              |              |                  |                 |       |  |  |  |  |  |

| bit 7                        | -                                                | Message Inter                         |                | bit          |                  |                 |       |  |  |  |  |  |

|                              |                                                  | request is enabl                      | •              | ~            |                  |                 |       |  |  |  |  |  |

|                              |                                                  | request is not er                     |                |              |                  |                 |       |  |  |  |  |  |

| bit 6                        | WAKIE: Bus Wake-up Activity Interrupt Enable bit |                                       |                |              |                  |                 |       |  |  |  |  |  |

|                              | 1 = Interrupt request is enabled                 |                                       |                |              |                  |                 |       |  |  |  |  |  |

|                              | 0 = Interrupt request is not enabled             |                                       |                |              |                  |                 |       |  |  |  |  |  |

| bit 5                        | ERRIE: Error Interrupt Enable bit                |                                       |                |              |                  |                 |       |  |  |  |  |  |

|                              |                                                  | request is enabl<br>request is not er |                |              |                  |                 |       |  |  |  |  |  |

| bit 4                        |                                                  | ted: Read as '0                       |                |              |                  |                 |       |  |  |  |  |  |

| bit 3                        | -                                                | Almost Full Int                       |                | o hit        |                  |                 |       |  |  |  |  |  |

| DIL J                        |                                                  | request is enabl                      | •              | ebit         |                  |                 |       |  |  |  |  |  |

|                              |                                                  | request is not er                     |                |              |                  |                 |       |  |  |  |  |  |

| bit 2                        | <b>RBOVIE:</b> RX                                | Buffer Overflow                       | / Interrupt Er | nable bit    |                  |                 |       |  |  |  |  |  |

|                              | 1 = Interrupt                                    | equest is enabl                       | ed             |              |                  |                 |       |  |  |  |  |  |

|                              | 0 = Interrupt i                                  | request is not er                     | nabled         |              |                  |                 |       |  |  |  |  |  |

| bit 1                        |                                                  | ffer Interrupt En                     |                |              |                  |                 |       |  |  |  |  |  |

|                              |                                                  | equest is enabl                       |                |              |                  |                 |       |  |  |  |  |  |

|                              |                                                  | request is not er                     | nabled         |              |                  |                 |       |  |  |  |  |  |

|                              | •                                                | •                                     |                |              |                  |                 |       |  |  |  |  |  |

| bit 0                        | TBIE: TX Buf                                     | fer Interrupt Ena<br>request is enabl | able bit       |              |                  |                 |       |  |  |  |  |  |

#### REGISTER 21-7: CXINTE: ECANX INTERRUPT ENABLE REGISTER

| R/W-x        | R/W-x                                        | R/W-x                                           | R/W-x         | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |  |  |  |

|--------------|----------------------------------------------|-------------------------------------------------|---------------|------------------------------------|-------|--------------------|-------|--|--|--|--|

| EID5         | EID4                                         | EID3                                            | EID2          | EID1                               | EID0  | RTR                | RB1   |  |  |  |  |

| bit 15       |                                              |                                                 |               |                                    |       |                    | bit 8 |  |  |  |  |

|              |                                              |                                                 |               |                                    |       |                    |       |  |  |  |  |

| U-x          | U-x                                          | U-x                                             | R/W-x         | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |  |  |  |

| —            | —                                            | —                                               | RB0           | DLC3                               | DLC2  | DLC1               | DLC0  |  |  |  |  |

| bit 7        |                                              |                                                 |               |                                    |       |                    | bit 0 |  |  |  |  |

|              |                                              |                                                 |               |                                    |       |                    |       |  |  |  |  |

| Legend:      |                                              |                                                 |               |                                    |       |                    |       |  |  |  |  |

| R = Readab   | le bit                                       | W = Writable                                    | bit           | U = Unimplemented bit, read as '0' |       |                    |       |  |  |  |  |

| -n = Value a | t POR                                        | '1' = Bit is set                                |               | '0' = Bit is cleared               |       | x = Bit is unknown |       |  |  |  |  |

|              |                                              |                                                 |               |                                    |       |                    |       |  |  |  |  |

| bit 15-10    | EID<5:0>: E                                  | xtended Identifi                                | er bits       |                                    |       |                    |       |  |  |  |  |

| bit 9        | RTR: Remot                                   | RTR: Remote Transmission Request bit            |               |                                    |       |                    |       |  |  |  |  |

|              | When IDE =                                   | When IDE = 1:                                   |               |                                    |       |                    |       |  |  |  |  |

|              | 1 = Message will request remote transmission |                                                 |               |                                    |       |                    |       |  |  |  |  |

|              |                                              | 0 = Normal message                              |               |                                    |       |                    |       |  |  |  |  |

|              |                                              | <u>When IDE = 0:</u><br>The RTR bit is ignored. |               |                                    |       |                    |       |  |  |  |  |

| bit 8        |                                              | RB1: Reserved Bit 1                             |               |                                    |       |                    |       |  |  |  |  |

|              |                                              | User must set this bit to '0' per CAN protocol. |               |                                    |       |                    |       |  |  |  |  |

| bit 7-5      |                                              | nted: Read as '                                 | -             |                                    |       |                    |       |  |  |  |  |

| bit 4        | RB0: Reserv                                  |                                                 | -             |                                    |       |                    |       |  |  |  |  |

|              |                                              | et this bit to '0' p                            | per CAN proto | ocol.                              |       |                    |       |  |  |  |  |

| hit 2 0      |                                              | Data Langth Ca                                  | -             |                                    |       |                    |       |  |  |  |  |

#### BUFFER 21-3: ECAN™ MESSAGE BUFFER WORD 2

bit 3-0 DLC<3:0>: Data Length Code bits

#### BUFFER 21-4: ECAN<sup>™</sup> MESSAGE BUFFER WORD 3

| R/W-x             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x | R/W-x |

|-------------------|-------|------------------|-------|------------------------------------|-------|-------|-------|

|                   |       |                  | Ву    | /te 1                              |       |       |       |

| bit 15            |       |                  |       |                                    |       |       | bit 8 |

| R/W-x             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x | R/W-x |

|                   |       |                  | Ву    | rte 0                              |       |       |       |

| bit 7             |       |                  |       |                                    |       |       | bit 0 |

| Legend:           |       |                  |       |                                    |       |       |       |

| R = Readable      | bit   | W = Writable     | bit   | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at POR |       | '1' = Bit is set |       | 0' = Bit is cleared x = Bit is unk |       | nown  |       |

bit 15-8 Byte 1<15:8>: ECAN Message Byte 1 bits

bit 7-0 Byte 0<7:0>: ECAN Message Byte 0 bits

#### 27.2 User ID Words

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices contain four User ID Words, located at addresses, 0x800FF8 through 0x800FFE. The User ID Words can be used for storing product information such as serial numbers, system manufacturing dates, manufacturing lot numbers and other application-specific information.

The User ID Words register map is shown in Table 27-3.

TABLE 27-3:USER ID WORDS REGISTER<br/>MAP

| File Name | Address  | Bits 23-16 | Bits 15-0 |

|-----------|----------|------------|-----------|

| FUID0     | 0x800FF8 | _          | UID0      |

| FUID1     | 0x800FFA | _          | UID1      |

| FUID2     | 0x800FFC | _          | UID2      |

| FUID3     | 0x800FFE | _          | UID3      |

**Legend:** — = unimplemented, read as '1'.

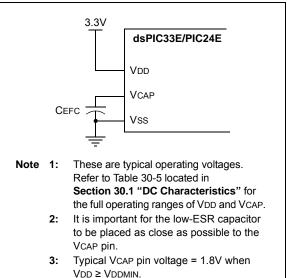

#### 27.3 On-Chip Voltage Regulator

All of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X devices power their core digital logic at a nominal 1.8V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family incorporate an onchip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. A low-ESR (less than 1 Ohm) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 30-5 located in **Section 30.0 "Electrical Characteristics"**.

Note: It is important for the low-ESR capacitor to be placed as close as possible to the VCAP pin.

# FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE

REGULATOR<sup>(1,2,3)</sup>

### 27.4 Brown-out Reset (BOR)

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated supply voltage, VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT Time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM is applied. The total delay in this case is TFSCM. Refer to Parameter SY35 in Table 30-22 of **Section 30.0 "Electrical Characteristics"** for specific TFSCM values.

The BOR status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax                                  | Description                               | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|--------|--------------------------------------------------|-------------------------------------------|---------------|-------------------------------|--------------------------|

| 46                 | MOV                  | MOV    | f,Wn                                             | Move f to Wn                              | 1             | 1                             | None                     |

|                    |                      | MOV    | f                                                | Move f to f                               | 1             | 1                             | None                     |

|                    |                      | MOV    | f,WREG                                           | Move f to WREG                            | 1             | 1                             | None                     |

|                    |                      | MOV    | #litl6,Wn                                        | Move 16-bit literal to Wn                 | 1             | 1                             | None                     |

|                    |                      | MOV.b  | #lit8,Wn                                         | Move 8-bit literal to Wn                  | 1             | 1                             | None                     |

|                    |                      | MOV    | Wn,f                                             | Move Wn to f                              | 1             | 1                             | None                     |

|                    |                      | MOV    | Wso,Wdo                                          | Move Ws to Wd                             | 1             | 1                             | None                     |

|                    |                      | MOV    | WREG, f                                          | Move WREG to f                            | 1             | 1                             | None                     |

|                    |                      | MOV.D  | Wns,Wd                                           | Move Double from W(ns):W(ns + 1) to<br>Wd | 1             | 2                             | None                     |

|                    |                      | MOV.D  | Ws , Wnd                                         | Move Double from Ws to W(nd +<br>1):W(nd) | 1             | 2                             | None                     |

| 47                 | MOVPAG               | MOVPAG | #lit10,DSRPAG                                    | Move 10-bit literal to DSRPAG             | 1             | 1                             | None                     |

|                    |                      | MOVPAG | #lit9,DSWPAG                                     | Move 9-bit literal to DSWPAG              | 1             | 1                             | None                     |

|                    |                      | MOVPAG | #lit8,TBLPAG                                     | Move 8-bit literal to TBLPAG              | 1             | 1                             | None                     |

|                    |                      | MOVPAG | Ws, DSRPAG                                       | Move Ws<9:0> to DSRPAG                    | 1             | 1                             | None                     |

|                    |                      | MOVPAG | Ws, DSWPAG                                       | Move Ws<8:0> to DSWPAG                    | 1             | 1                             | None                     |

|                    |                      | MOVPAG | Ws, TBLPAG                                       | Move Ws<7:0> to TBLPAG                    | 1             | 1                             | None                     |

| 48                 | MOVSAC               | MOVSAC | Acc,Wx,Wxd,Wy,Wyd,AWB <sup>(1)</sup>             | Prefetch and store accumulator            | 1             | 1                             | None                     |

| 49                 | MPY                  | MPY    | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd(1)                       | Multiply Wm by Wn to Accumulator          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MPY    | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd <sup>(1)</sup>           | Square Wm to Accumulator                  | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 50                 | MPY.N                | MPY.N  | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd(1)                       | -(Multiply Wm by Wn) to Accumulator       | 1             | 1                             | None                     |

| 51                 | MSC                  | MSC    | Wm*Wm, Acc, Wx, Wxd, Wy, Wyd, AWB <sup>(1)</sup> | Multiply and Subtract from Accumulator    | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

| DC CHARACTERISTICS |        |                                         | (unless                     | d Operating<br>otherwise<br>g temperat | <b>stated)</b><br>ure -40° | C ≤ TA ≤ | <b>/ to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended                                                                               |

|--------------------|--------|-----------------------------------------|-----------------------------|----------------------------------------|----------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                          | Min. Typ. Max. Units Condit |                                        |                            |          | Conditions                                                                                                                                    |

|                    | liL    | Input Leakage Current <sup>(1,2)</sup>  |                             |                                        |                            |          |                                                                                                                                               |

| DI50               |        | I/O Pins 5V Tolerant <sup>(3)</sup>     | -1                          | —                                      | +1                         | μA       | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in at high-impedance} \end{split}$                         |

| DI51               |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                          | _                                      | +1                         | μA       | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ Pin \text{ at high-impedance}, \\ -40^\circC \leq TA \leq +85^\circC \end{array}$ |

| DI51a              |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                          | _                                      | +1                         | μA       | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +85^{\circ}C$                                                 |

| DI51b              |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                          | _                                      | +1                         | μA       | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance,<br>-40°C ≤ TA ≤ +125°C                                                                      |

| DI51c              |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                          | _                                      | +1                         | μA       | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +125^{\circ}C$                                                |

| DI55               |        | MCLR                                    | -5                          | —                                      | +5                         | μA       | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                                      |

| DI56               |        | OSC1                                    | -5                          | —                                      | +5                         | μΑ       | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ XT \text{ and } HS \text{ modes} \end{array}$                                     |

#### TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 2: Negative current is defined as current sourced by the pin.

- 3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 4: VIL source < (Vss 0.3). Characterized but not tested.

- **5:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

8: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

| AC CHA              | RACTER  | ISTICS                          |                           | Standard Operatin<br>(unless otherwise<br>Operating tempera | stated)<br>iture -40 | )°C ≤ Ta ≤   | +85°C for Industrial           |   |    |   |

|---------------------|---------|---------------------------------|---------------------------|-------------------------------------------------------------|----------------------|--------------|--------------------------------|---|----|---|

| Param<br>No. Symbol |         | Characteristic <sup>(4)</sup>   |                           | Min. <sup>(1)</sup> Max.                                    |                      | Units        | +125°C for Extended Conditions |   |    |   |

| IM10                | TLO:SCL | Clock Low Time                  | 100 kHz mode              | Tcy/2 (BRG + 2)                                             | _                    | μS           |                                |   |    |   |

|                     |         |                                 | 400 kHz mode              | TCY/2 (BRG + 2)                                             |                      | μS           |                                |   |    |   |

|                     |         |                                 | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                             |                      | μs           |                                |   |    |   |

| IM11                | THI:SCL | Clock High Time                 | 100 kHz mode              | Tcy/2 (BRG + 2)                                             |                      | μS           |                                |   |    |   |

|                     |         | Ū                               | 400 kHz mode              | Tcy/2 (BRG + 2)                                             |                      | μ <b>S</b>   |                                |   |    |   |

|                     |         |                                 | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                             |                      | μ <b>S</b>   |                                |   |    |   |

| IM20                | TF:SCL  | SDAx and SCLx                   | 100 kHz mode              |                                                             | 300                  | ns           | CB is specified to be          |   |    |   |

|                     |         | Fall Time                       | 400 kHz mode              | 20 + 0.1 Св                                                 | 300                  | ns           | from 10 to 400 pF              |   |    |   |

|                     |         |                                 | 1 MHz mode <sup>(2)</sup> |                                                             | 100                  | ns           | -                              |   |    |   |

| IM21                | TR:SCL  | SDAx and SCLx                   | 100 kHz mode              |                                                             | 1000                 | ns           | CB is specified to be          |   |    |   |

|                     |         | Rise Time                       | 400 kHz mode              | 20 + 0.1 Св                                                 | 300                  | ns           | from 10 to 400 pF              |   |    |   |

|                     |         |                                 | 1 MHz mode <sup>(2)</sup> |                                                             | 300                  | ns           | -                              |   |    |   |

| IM25                | TSU:DAT | DAT Data Input                  | 100 kHz mode              | 250                                                         |                      | ns           |                                |   |    |   |

|                     |         | Setup Time                      | 400 kHz mode              | 100                                                         | _                    | ns           |                                |   |    |   |

|                     |         |                                 | 1 MHz mode <sup>(2)</sup> | 40                                                          |                      | ns           | -                              |   |    |   |

| IM26 THD:DAT        | THD:DAT | Data Input<br>Hold Time         | 100 kHz mode              | 0                                                           | _                    | μS           |                                |   |    |   |

|                     |         |                                 | 400 kHz mode              | 0                                                           | 0.9                  | μS           |                                |   |    |   |

|                     |         |                                 | 1 MHz mode <sup>(2)</sup> | 0.2                                                         |                      | μs           | -                              |   |    |   |

| IM30                | TSU:STA | Start Condition<br>Setup Time   | 100 kHz mode              | Tcy/2 (BRG + 2)                                             |                      | μ <b>S</b>   | Only relevant for              |   |    |   |

|                     |         |                                 | 400 kHz mode              | Tcy/2 (BRG + 2)                                             |                      | μS           | Repeated Start condition       |   |    |   |

|                     |         |                                 | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                             | _                    | μs           |                                |   |    |   |

| IM31                | THD:STA | TA Start Condition<br>Hold Time | 100 kHz mode              | Tcy/2 (BRG + 2)                                             |                      | μ <b>s</b>   | After this period, the         |   |    |   |

|                     |         |                                 | 400 kHz mode              | Tcy/2 (BRG +2)                                              |                      | μS           | first clock pulse is           |   |    |   |

|                     |         |                                 | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                             | _                    | μS           | generated                      |   |    |   |

| IM33                | Tsu:sto | Stop Condition                  | 100 kHz mode              | Tcy/2 (BRG + 2)                                             | _                    | μs           |                                |   |    |   |

|                     |         |                                 |                           |                                                             | Setup Time           | 400 kHz mode | Tcy/2 (BRG + 2)                | _ | μs | 1 |

|                     |         |                                 | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                             | —                    | μS           |                                |   |    |   |

| IM34                | THD:STO | Stop Condition                  | 100 kHz mode              | Tcy/2 (BRG + 2)                                             | _                    | μs           |                                |   |    |   |

|                     |         | Hold Time                       | 400 kHz mode              | Tcy/2 (BRG + 2)                                             | —                    | μS           |                                |   |    |   |

|                     |         |                                 | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                             | —                    | μS           |                                |   |    |   |

| IM40                | TAA:SCL | Output Valid                    | 100 kHz mode              |                                                             | 3500                 | ns           |                                |   |    |   |

|                     |         | From Clock                      | 400 kHz mode              | —                                                           | 1000                 | ns           | İ.                             |   |    |   |

|                     |         |                                 | 1 MHz mode <sup>(2)</sup> | —                                                           | 400                  | ns           | İ.                             |   |    |   |

| IM45                | TBF:SDA | Bus Free Time                   | 100 kHz mode              | 4.7                                                         | —                    | μs           | Time the bus must be           |   |    |   |

|                     |         |                                 | 400 kHz mode              | 1.3                                                         | _                    | μ <b>s</b>   | free before a new              |   |    |   |

|                     |         |                                 | 1 MHz mode <sup>(2)</sup> | 0.5                                                         | _                    | μ <b>s</b>   | transmission can star          |   |    |   |

| IM50                | Св      | Bus Capacitive L                |                           | _                                                           | 400                  | pF           |                                |   |    |   |

| IM51                | TPGD    | Pulse Gobbler De                | -                         | 65                                                          | 390                  | ns           | (Note 3)                       |   |    |   |

#### TABLE 30-49: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

Note 1: BRG is the value of the l<sup>2</sup>C<sup>™</sup> Baud Rate Generator. Refer to "Inter-Integrated Circuit (l<sup>2</sup>C<sup>™</sup>)" (DS70330) in the "dsPIC33/PIC24 Family Reference Manual". Please see the Microchip web site for the latest family reference manual sections.

- 2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

- **3:** Typical value for this parameter is 130 ns.

- 4: These parameters are characterized, but not tested in manufacturing.

# Revision E (April 2012)

This revision includes typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in Table A-3.