Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XFI

| Betuils                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128mc202-i-mm |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

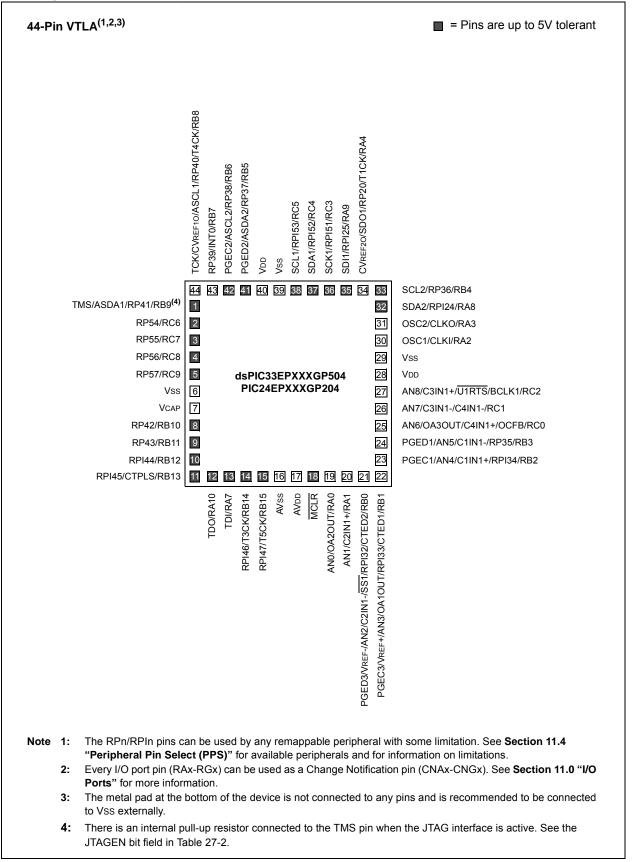

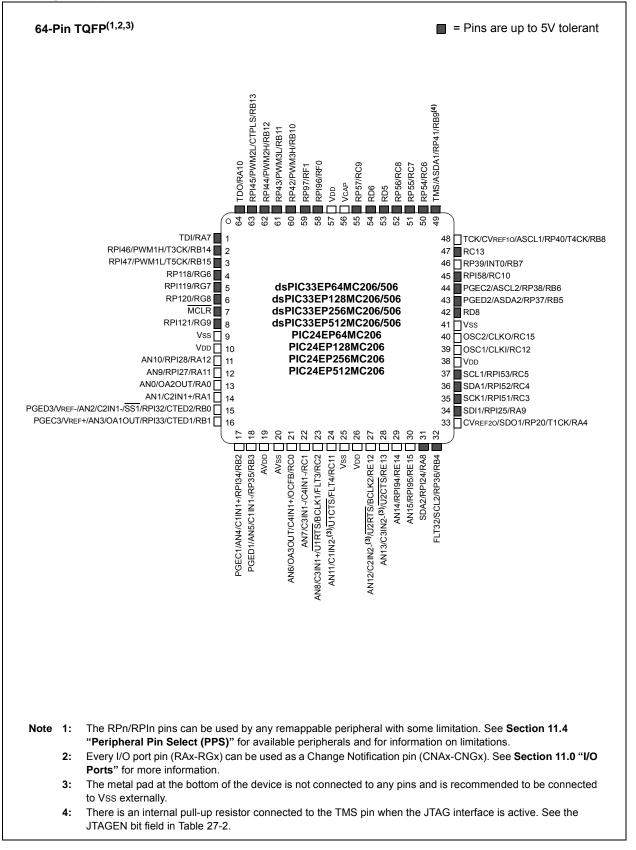

### **Pin Diagrams (Continued)**

### Pin Diagrams (Continued)

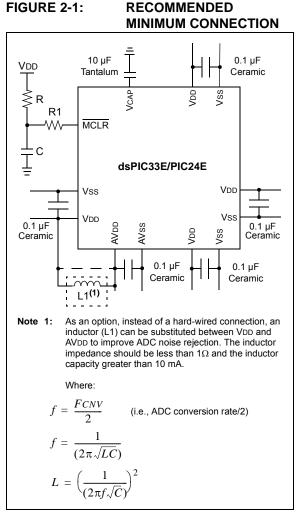

### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

## 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 1 Ohm) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor greater than 4.7  $\mu$ F (10  $\mu$ F is recommended), 16V connected to ground. The type can be ceramic or tantalum. See **Section 30.0** "**Electrical Characteristics**" for additional information.

The placement of this capacitor should be close to the VCAP pin. It is recommended that the trace length not exceeds one-quarter inch (6 mm). See **Section 27.3 "On-Chip Voltage Regulator"** for details.

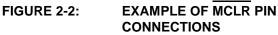

# 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor, C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components as shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

#### TABLE 4-53: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|---------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | _      | _      | _      | _      | TRISA10 | TRISA9 | TRISA8 | TRISA7 | -     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 079F          |

| PORTA        | 0E02  |        | _      | _      | -      | _      | RA10    | RA9    | RA8    | RA7    | -     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | LATA10  | LATA9  | LATA8  | LATA7  | -     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | —      | —      | _      |        | ODCA10  | ODCA9  | ODCA8  | ODCA7  | —     | —     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | —      | —      | _      |        | CNIEA10 | CNIEA9 | CNIEA8 | CNIEA7 | —     | —     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | —      | —      | _      |        | CNPUA10 | CNPUA9 | CNPUA8 | CNPUA7 | —     | —     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | —      | —      | _      |        | CNPDA10 | CNPDA9 | CNPDA8 | CNPDA7 | —     | —     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | _      | _      | —       | _      | —      | _      | _     | —     | ANSA4  | _      | _      | ANSA1  | ANSA0  | 0013          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-54: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | -       | -      | ANSB8  | _      | _      | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-55: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISC        | 0E20  | —      | _      | _      |        | —      | _      | TRISC9 | TRISC8 | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 03FF          |

| PORTC        | 0E22  | _      | _      | _      | _      | _      | —      | RC9    | RC8    | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xxxx          |

| LATC         | 0E24  | —      | —      | _      | —      |        | —      | LATC9  | LATC8  | LATC7  | LATC6  | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  | —      | —      | _      | —      |        | —      | ODCC9  | ODCC8  | ODCC7  | ODCC6  | ODCC5  | ODCC4  | ODCC3  | ODCC2  | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | —      | —      | _      | —      |        | —      | CNIEC9 | CNIEC8 | CNIEC7 | CNIEC6 | CNIEC5 | CNIEC4 | CNIEC3 | CNIEC2 | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  | —      | —      | _      | —      |        | —      | CNPUC9 | CNPUC8 | CNPUC7 | CNPUC6 | CNPUC5 | CNPUC4 | CNPUC3 | CNPUC2 | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  | —      | —      | _      | —      |        | —      | CNPDC9 | CNPDC8 | CNPDC7 | CNPDC6 | CNPDC5 | CNPDC4 | CNPDC3 | CNPDC2 | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | —      | —      | _      | _      |        | —      | _      |        |        |        | —      |        | _      | ANSC2  | ANSC1  | ANSC0  | 0007          |

Legend: x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2013 Microchip Technology Inc.

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configuring the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages, by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address prior to modification addresses an EDS or PSV page

- The EA calculation uses Pre-Modified or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-61 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

|             | -                   | SV SI ACE BOON |              |                        |                |              |                        |

|-------------|---------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|

| 0/11        |                     |                | Before       |                        |                | After        |                        |

| O/U,<br>R/W | Operation           | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page<br>Description    |

| O,<br>Read  |                     | DSRPAG = 0x1FF | 1            | EDS: Last page         | DSRPAG = 0x1FF | 0            | See Note 1             |

| O,<br>Read  | [++Wn]              | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page |

| O,<br>Read  | <b>Or</b><br>[Wn++] | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0            | See Note 1             |

| O,<br>Write |                     | DSWPAG = 0x1FF | 1            | EDS: Last page         | DSWPAG = 0x1FF | 0            | See Note 1             |

| U,<br>Read  |                     | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0            | See Note 1             |

| U,<br>Read  | [Wn]<br>Or<br>[Wn]  | DSRPAG = 0x200 | 1            | PSV: First Isw<br>page | DSRPAG = 0x200 | 0            | See Note 1             |

| U,<br>Read  | [ //11 - ]          | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>page  |

# TABLE 4-61: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS and PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

Legend: O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

- **3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

- 4: Pseudo-Linear Addressing is not supported for large offsets.

### 4.5 Instruction Addressing Modes

The addressing modes shown in Table 4-63 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

### 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

### 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

- Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

### TABLE 4-63: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

# 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X CPU.

The interrupt controller has the following features:

- Up to eight processor exceptions and software traps

- Eight user-selectable priority levels

- Interrupt Vector Table (IVT) with a unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Fixed interrupt entry and return latencies

## 7.1 Interrupt Vector Table

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X Interrupt Vector Table (IVT), shown in Figure 7-1, resides in program memory starting at location, 000004h. The IVT contains seven non-maskable trap vectors and up to 246 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit-wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

# 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER     | TU-5: PIVID6 | . PERIPHER       |                           | DISABLE C                          | UNIROL RE             | GISIER 6              |                       |  |  |

|--------------|--------------|------------------|---------------------------|------------------------------------|-----------------------|-----------------------|-----------------------|--|--|

| U-0          | U-0          | U-0              | U-0                       | U-0                                | R/W-0                 | R/W-0                 | R/W-0                 |  |  |

| —            | —            | —                | —                         | —                                  | PWM3MD <sup>(1)</sup> | PWM2MD <sup>(1)</sup> | PWM1MD <sup>(1)</sup> |  |  |

| bit 15       |              |                  |                           |                                    |                       |                       | bit 8                 |  |  |

|              |              |                  |                           |                                    |                       |                       |                       |  |  |

| U-0          | U-0          | U-0              | U-0                       | U-0                                | U-0                   | U-0                   | U-0                   |  |  |

|              |              |                  |                           |                                    |                       |                       |                       |  |  |

| bit 7        |              |                  |                           |                                    |                       |                       | bit 0                 |  |  |

|              |              |                  |                           |                                    |                       |                       |                       |  |  |

| Legend:      |              |                  |                           |                                    |                       |                       |                       |  |  |

| R = Readab   | le bit       | W = Writable     | bit                       | U = Unimplemented bit, read as '0' |                       |                       |                       |  |  |

| -n = Value a | t POR        | '1' = Bit is set |                           | '0' = Bit is clea                  | ared                  | x = Bit is unkr       | iown                  |  |  |

|              |              |                  |                           |                                    |                       |                       |                       |  |  |

| bit 15-11    | Unimplement  | ted: Read as '   | כ'                        |                                    |                       |                       |                       |  |  |

| bit 10       | PWM3MD: P\   | NM3 Module D     | isable bit <sup>(1)</sup> |                                    |                       |                       |                       |  |  |

|              | 1 = PWM3 mo  | odule is disable | ed                        |                                    |                       |                       |                       |  |  |

|              | 0 = PWM3 mo  | odule is enable  | d                         |                                    |                       |                       |                       |  |  |

| bit 9        | PWM2MD: P\   | NM2 Module D     | isable bit <sup>(1)</sup> |                                    |                       |                       |                       |  |  |

|              | 1 = PWM2 mo  | odule is disable | ed                        |                                    |                       |                       |                       |  |  |

|              | 0 = PWM2 mo  | odule is enable  | d                         |                                    |                       |                       |                       |  |  |

| bit 8        | PWM1MD: P\   | NM1 Module D     | isable bit <sup>(1)</sup> |                                    |                       |                       |                       |  |  |

|              |              | odule is disable |                           |                                    |                       |                       |                       |  |  |

|              | 0 = PWM1 mo  | odule is enable  | d                         |                                    |                       |                       |                       |  |  |

| bit 7-0      | Unimplement  | ted: Read as '   | כ'                        |                                    |                       |                       |                       |  |  |

# REGISTER 10-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

Note 1: This bit is available on dsPIC33EPXXXMC50X/20X and PIC24EPXXXMC20X devices only.

| Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment | Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment |

|--------------------------------------------------|------------------|----------------|--------------------------------------------------|------------------|----------------|

| 010 1000                                         | I/O              | RP40           | 101 0101                                         | —                | _              |

| 010 1001                                         | I/O              | RP41           | 101 0110                                         | —                | —              |

| 010 1010                                         | I/O              | RP42           | 101 0111                                         | —                | —              |

| 010 1011                                         | I/O              | RP43           | 101 1000                                         |                  | —              |

| 010 1100                                         | I                | RPI44          | 101 1001                                         |                  | —              |

| 101 1010                                         | —                | _              | 110 1101                                         | —                | _              |

| 101 1011                                         | —                | —              | 110 1110                                         |                  | —              |

| 101 1100                                         | —                | —              | 110 1111                                         |                  | —              |

| 101 1101                                         | —                | _              | 111 0000                                         | —                | _              |

| 101 1110                                         | 1                | RPI94          | 111 0001                                         | —                | _              |

| 101 1111                                         | I                | RP195          | 111 0010                                         |                  | —              |

| 110 0000                                         | I                | RPI96          | 111 0011                                         | —                | —              |

| 110 0001                                         | I/O              | RP97           | 111 0100                                         |                  | —              |

| 110 0010                                         | —                | —              | 111 0101                                         |                  | —              |

| 110 0011                                         | —                | —              | 111 0110                                         | I/O              | RP118          |

| 110 0100                                         | —                | —              | 111 0111                                         | Ι                | RPI119         |

| 110 0101                                         | —                | —              | 111 1000                                         | I/O              | RP120          |

| 110 0110                                         | _                |                | 111 1001                                         | Ι                | RPI121         |

| 110 0111                                         |                  |                | 111 1010                                         | —                |                |

| 110 1000                                         | —                | _              | 111 1011                                         | —                | _              |

| 110 1001                                         | —                |                | 111 1100                                         | —                |                |

| 110 1010                                         |                  |                | 111 1101                                         | —                |                |

| 110 1011                                         | —                | _              | 111 1110                                         | —                |                |

| 110 1100                                         | —                | _              | 111 1111                                         | _                |                |

### TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES (CONTINUED)

Legend: Shaded rows indicate PPS Input register values that are unimplemented.

Note 1: See Section 11.4.4.1 "Virtual Connections" for more information on selecting this pin assignment.

2: These inputs are available on dsPIC33EPXXXGP/MC50X devices only.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP43  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

|        |     |       |       |       |        |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

| —      | —   |       |       | RP42  | R<5:0> |       |       |

### REGISTER 11-22: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

|   | bit | 7 |

|---|-----|---|

| 1 |     |   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP43R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP43 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP42R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 11-3 for peripheral function numbers) |

### REGISTER 11-23: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP55  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------|-----|-------|------------|-------|-------|-------|-------|--|--|

| —     | —   |       | RP54R<5:0> |       |       |       |       |  |  |

| bit 7 |     |       |            |       |       |       | bit 0 |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP55R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP55 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP54R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP54 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 0

### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER (CONTINUED)

| bit 6-4 | SYNCSRC<2:0>: Synchronous Source Selection bits <sup>(1)</sup><br>111 = Reserved<br>100 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-0 | 100 = Reserved<br>011 = PTGO17 <sup>(2)</sup><br>010 = PTGO16 <sup>(2)</sup><br>001 = Reserved<br>000 = SYNCI1 input from PPS<br>SEVTPS<3:0>: PWMx Special Event Trigger Output Postscaler Select bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1111 = 1:16 Postscaler generates Special Event Trigger on every sixteenth compare match event</li> <li>.</li> <l< td=""></l<></ul> |

|         | 0000 = 1:1 Postscaler generates Special Event Trigger on every second compare match event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

- **Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

# REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER (CONTINUED)

| bit 2 | <b>HOMIEN:</b> Home Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled            |

|-------|--------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IDXIRQ:</b> Status Flag for Index Event Status bit<br>1 = Index event has occurred<br>0 = No Index event has occurred |

| bit 0 | <b>IDXIEN:</b> Index Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled           |

Note 1: This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4 | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Receiver is active                                                                                                                                                                                                           |

| bit 3 | <b>PERR:</b> Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character (character at the top of the receive FIFO) 0 = Parity error has not been detected                                                                                                  |

| bit 2 | <pre>FERR: Framing Error Status bit (read-only) 1 = Framing error has been detected for the current character (character at the top of the receive FIFO) 0 = Framing error has not been detected</pre>                                                                                           |

| bit 1 | <ul> <li>OERR: Receive Buffer Overrun Error Status bit (clear/read-only)</li> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 → 0 transition) resets the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | <ul> <li>URXDA: UARTx Receive Buffer Data Available bit (read-only)</li> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                |

**Note 1:** Refer to the "**UART**" (DS70582) section in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UARTx module for transmit operation.

| R-0                                                                  | R-0 | R-0                          | R-0                                                | R-0                                                                                            | R-0                                                                                       | R-0                                                                                                                  |

|----------------------------------------------------------------------|-----|------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

|                                                                      |     | TERR                         | CNT<7:0>                                           |                                                                                                |                                                                                           |                                                                                                                      |

|                                                                      |     |                              |                                                    |                                                                                                |                                                                                           | bit 8                                                                                                                |

|                                                                      |     |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |

| R-0                                                                  | R-0 | R-0                          | R-0                                                | R-0                                                                                            | R-0                                                                                       | R-0                                                                                                                  |

|                                                                      |     | RERR                         | CNT<7:0>                                           |                                                                                                |                                                                                           |                                                                                                                      |

|                                                                      |     |                              |                                                    |                                                                                                |                                                                                           | bit 0                                                                                                                |

|                                                                      |     |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |

|                                                                      |     |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |

| -n = Value at POR '1' = Bit is set                                   |     |                              | '0' = Bit is cleared x = Bit is unkn               |                                                                                                |                                                                                           | nown                                                                                                                 |

|                                                                      | R-0 | R-0 R-0<br>it W = Writable b | TERR<br>R-0 R-0 R-0<br>RERR<br>it W = Writable bit | TERRCNT<7:0>           R-0         R-0         R-0           RERRCNT<7:0>         RERRCNT<7:0> | TERRCNT<7:0>           R-0         R-0         R-0           RERRCNT<7:0>         RERRCNT | TERRCNT<7:0>         R-0       R-0       R-0       R-0         RERRCNT<7:0>       U = Unimplemented bit, read as '0' |

bit 7-0 **RERRCNT<7:0>:** Receive Error Count bits

### REGISTER 21-9: CxCFG1: ECANx BAUD RATE CONFIGURATION REGISTER 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SJW1  | SJW0  | BRP5  | BRP4  | BRP3  | BRP2  | BRP1  | BRP0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0' |

|----------|----------------------------|

|----------|----------------------------|

| bit 7-6 | SJW<1:0>: Synchronization Jump Width bits    |

|---------|----------------------------------------------|

|         | 11 = Length is 4 x TQ                        |

|         | $10 = \text{Length is } 3 \times \text{Tq}$  |

|         | $01 = \text{Length is } 2 \times \text{T} Q$ |

|         | $00 = \text{Length is } 1 \times \text{Tq}$  |

```

bit 5-0 BRP<5:0>: Baud Rate Prescaler bits

```

```

11 1111 = TQ = 2 x 64 x 1/FCAN

```

•

- 00 0010 = TQ = 2 x 3 x 1/FCAN 00 0001 = TQ = 2 x 2 x 1/FCAN

- 00 0000 = Tq = 2 x 1 x 1/FCAN

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| FLTEN15 | FLTEN14 | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10 | FLTEN9 | FLTEN8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

| FLTEN7  | FLTEN6  | FLTEN5  | FLTEN4  | FLTEN3  | FLTEN2  | FLTEN1 | FLTEN0 |

| bit 7   |         |         |         |         |         |        | bit 0  |

|         |         |         |         |         |         |        |        |

| Legend: |         |         |         |         |         |        |        |

### REGISTER 21-11: CxFEN1: ECANx ACCEPTANCE FILTER ENABLE REGISTER 1

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0

FLTEN<15:0>: Enable Filter n to Accept Messages bits

1 = Enables Filter n

0 = Disables Filter n

REGISTER 21-12: CxBUFPNT1: ECANx FILTER 0-3 BUFFER POINTER REGISTER 1

| R/W-0         | R/W-0                                                                    | R/W-0                                                                                                       | R/W-0                                          | R/W-0                                   | R/W-0          | R/W-0  | R/W-0 |  |

|---------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------|----------------|--------|-------|--|

| F3BP<3:0>     |                                                                          |                                                                                                             |                                                |                                         | F2BI           | P<3:0> |       |  |

| bit 15        |                                                                          |                                                                                                             |                                                |                                         |                |        | bit 8 |  |

| R/W-0         | R/W-0                                                                    | R/W-0                                                                                                       | R/W-0                                          | R/W-0                                   | R/W-0          | R/W-0  | R/W-0 |  |

|               | F1BI                                                                     | P<3:0>                                                                                                      |                                                |                                         | F0BI           | P<3:0> |       |  |

| bit 7         |                                                                          |                                                                                                             |                                                |                                         |                |        | bit ( |  |

| Legend:       |                                                                          |                                                                                                             |                                                |                                         |                |        |       |  |

| R = Readable  | e bit                                                                    | W = Writable                                                                                                | bit                                            | U = Unimplemented bit, read as '0'      |                |        |       |  |

| -n = Value at | POR                                                                      | '1' = Bit is set                                                                                            |                                                | '0' = Bit is cleared x = Bit is unknown |                |        | nown  |  |

| bit 15-12     | 1111 = Filte<br>1110 = Filte<br>•<br>•<br>•<br>•<br>•                    | : RX Buffer Mas<br>er hits received in<br>er hits received in<br>er hits received in<br>er hits received in | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | iffer                                   |                |        |       |  |

| bit 11-8      | F2BP<3:0>: RX Buffer Mask for Filter 2 bits (same values as bits<15:12>) |                                                                                                             |                                                |                                         |                |        |       |  |

| bit 7-4       | F1BP<3:0>                                                                | : RX Buffer Mas                                                                                             | k for Filter 1 k                               | oits (same value                        | s as bits<15:1 | 2>)    |       |  |

|               |                                                                          |                                                                                                             |                                                |                                         |                |        |       |  |

### 25.3 Op Amp/Comparator Registers

| R/W-0         | U-0                                                                 | U-0                               | U-0                          | R-0                     | R-0                  | R-0                  | R-0                  |  |  |  |

|---------------|---------------------------------------------------------------------|-----------------------------------|------------------------------|-------------------------|----------------------|----------------------|----------------------|--|--|--|

| PSIDL         |                                                                     | _                                 | _                            | C4EVT <sup>(1)</sup>    | C3EVT <sup>(1)</sup> | C2EVT <sup>(1)</sup> | C1EVT <sup>(1)</sup> |  |  |  |

| bit 15        |                                                                     |                                   | •                            |                         |                      |                      | bit                  |  |  |  |

|               |                                                                     |                                   |                              |                         |                      |                      |                      |  |  |  |

| U-0           | U-0                                                                 | U-0                               | U-0                          | R-0                     | R-0                  | R-0                  | R-0                  |  |  |  |

| _             | —                                                                   | _                                 | _                            | C4OUT <sup>(2)</sup>    | C3OUT <sup>(2)</sup> | C2OUT <sup>(2)</sup> | C10UT <sup>(2)</sup> |  |  |  |

| bit 7         |                                                                     |                                   |                              |                         |                      |                      | bit                  |  |  |  |

|               |                                                                     |                                   |                              |                         |                      |                      |                      |  |  |  |

| Legend:       | - 1-14                                                              |                                   | L:4                          |                         |                      |                      |                      |  |  |  |

| R = Readabl   |                                                                     | W = Writable                      |                              | -                       | nented bit, read     |                      |                      |  |  |  |

| -n = Value at | PUR                                                                 | '1' = Bit is se                   | [                            | '0' = Bit is clea       | ared                 | x = Bit is unkr      | IOWN                 |  |  |  |

| bit 15        | PSIDI · Comr                                                        | parator Stop in                   | Idle Mode hit                |                         |                      |                      |                      |  |  |  |

|               |                                                                     |                                   |                              | ators when devi         | ce enters Idle n     | node                 |                      |  |  |  |

|               |                                                                     |                                   |                              | rs in Idle mode         |                      |                      |                      |  |  |  |

| bit 14-12     | Unimplemen                                                          | ted: Read as                      | 0'                           |                         |                      |                      |                      |  |  |  |

| bit 11        | <b>C4EVT:</b> Op A                                                  | mp/Comparate                      | or 4 Event Sta               | atus bit <sup>(1)</sup> |                      |                      |                      |  |  |  |

|               |                                                                     | comparator eve                    |                              |                         |                      |                      |                      |  |  |  |

|               |                                                                     | comparator eve                    |                              |                         |                      |                      |                      |  |  |  |

| bit 10        | C3EVT: Comparator 3 Event Status bit <sup>(1)</sup>                 |                                   |                              |                         |                      |                      |                      |  |  |  |

|               | 1 = Comparator event occurred<br>0 = Comparator event did not occur |                                   |                              |                         |                      |                      |                      |  |  |  |

| bit 9         | •                                                                   | parator 2 Ever                    |                              |                         |                      |                      |                      |  |  |  |

|               |                                                                     | = Comparator event occurred       |                              |                         |                      |                      |                      |  |  |  |

|               | •                                                                   | tor event did n                   |                              |                         |                      |                      |                      |  |  |  |

| bit 8         |                                                                     | parator 1 Ever                    |                              |                         |                      |                      |                      |  |  |  |

|               |                                                                     | tor event occu<br>tor event did n |                              |                         |                      |                      |                      |  |  |  |

| bit 7-4       |                                                                     | ited: Read as                     |                              |                         |                      |                      |                      |  |  |  |

| bit 3         | -                                                                   | parator 4 Outp                    |                              | 2)                      |                      |                      |                      |  |  |  |

|               | When CPOL                                                           |                                   |                              |                         |                      |                      |                      |  |  |  |

|               | 1 = VIN + > VII                                                     | N-                                |                              |                         |                      |                      |                      |  |  |  |

|               | 0 = VIN + < VII                                                     |                                   |                              |                         |                      |                      |                      |  |  |  |

|               | $\frac{\text{When CPOL}}{1 = \text{VIN} + < \text{VII}}$            |                                   |                              |                         |                      |                      |                      |  |  |  |

|               | 0 = VIN + > VII                                                     |                                   |                              |                         |                      |                      |                      |  |  |  |

| bit 2         | C3OUT: Com                                                          | parator 3 Outp                    | out Status bit <sup>(;</sup> | 2)                      |                      |                      |                      |  |  |  |

|               | When CPOL                                                           |                                   |                              |                         |                      |                      |                      |  |  |  |

|               | 1 = VIN+ > VII<br>0 = VIN+ < VII                                    |                                   |                              |                         |                      |                      |                      |  |  |  |

|               | 0 = VIN + < VII<br>When CPOL                                        |                                   |                              |                         |                      |                      |                      |  |  |  |

|               | 1 = VIN + < VII                                                     |                                   |                              |                         |                      |                      |                      |  |  |  |

|               | $\perp = VIN + < VII$                                               | N-                                |                              |                         |                      |                      |                      |  |  |  |

#### REGISTER 25-1: CMSTAT: OP AMP/COMPARATOR STATUS REGISTER

- **Note 1:** Reflects the value of the of the CEVT bit in the respective Op Amp/Comparator Control register, CMxCON<9>.

- 2: Reflects the value of the COUT bit in the respective Op Amp/Comparator Control register, CMxCON<8>.

# TABLE 30-47:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |                             |  |

|--------------------|-----------------------|----------------------------------------------|-------------------------------------------------------|---------------------|------|-------|-----------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                  | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |  |

| SP70               | FscP                  | Maximum SCK1 Input Frequency                 | —                                                     | —                   | 15   | MHz   | (Note 3)                    |  |

| SP72               | TscF                  | SCK1 Input Fall Time                         | —                                                     | —                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP73               | TscR                  | SCK1 Input Rise Time                         | —                                                     | —                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                   | —                                                     | _                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                   | —                                                     | —                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge    | —                                                     | 6                   | 20   | ns    |                             |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge | 30                                                    | —                   | _    | ns    |                             |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge   | 30                                                    | —                   | _    | ns    |                             |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge    | 30                                                    | —                   | _    | ns    |                             |  |

| SP50               | TssL2scH,<br>TssL2scL | SS1 ↓ to SCK1 ↑ or SCK1 ↓<br>Input           | 120                                                   | —                   | _    | ns    |                             |  |

| SP51               | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance       | 10                                                    | —                   | 50   | ns    | (Note 4)                    |  |

| SP52               | TscH2ssH,<br>TscL2ssH | SS1                                          | 1.5 Tcy + 40                                          | —                   |      | ns    | (Note 4)                    |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 66.7 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

# 33.0 PACKAGING INFORMATION

### 33.1 Package Marking Information

### 28-Lead SPDIP

#### 28-Lead SOIC (.300")

28-Lead SSOP

Example dsPIC33EP64GP 502-I/SP@3 1310017

### Example

### Example

28-Lead QFN-S (6x6x0.9 mm)

Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|--------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | be carried                               | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>of or customer-specific information.                                                                                                                                                                                              |

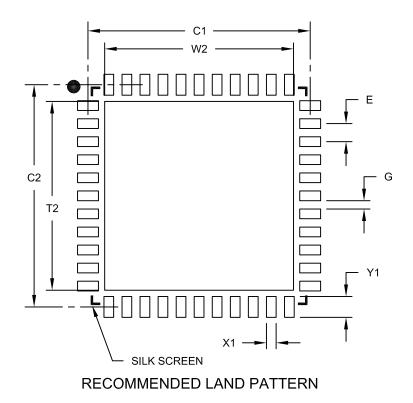

### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |      |          |      |

|----------------------------|-------------|------|----------|------|

| Dimension                  | Limits      | MIN  | NOM      | MAX  |

| Contact Pitch              | E           |      | 0.65 BSC |      |

| Optional Center Pad Width  | W2          |      |          | 6.60 |

| Optional Center Pad Length | T2          |      |          | 6.60 |

| Contact Pad Spacing        | C1          |      | 8.00     |      |

| Contact Pad Spacing        | C2          |      | 8.00     |      |

| Contact Pad Width (X44)    | X1          |      |          | 0.35 |

| Contact Pad Length (X44)   | Y1          |      |          | 0.85 |

| Distance Between Pads      | G           | 0.25 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.