Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 8K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

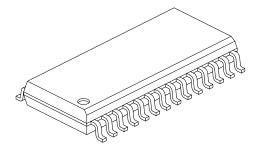

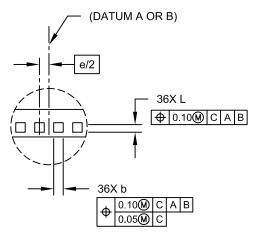

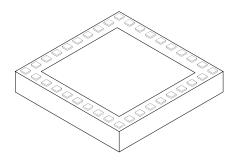

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128mc202-i-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

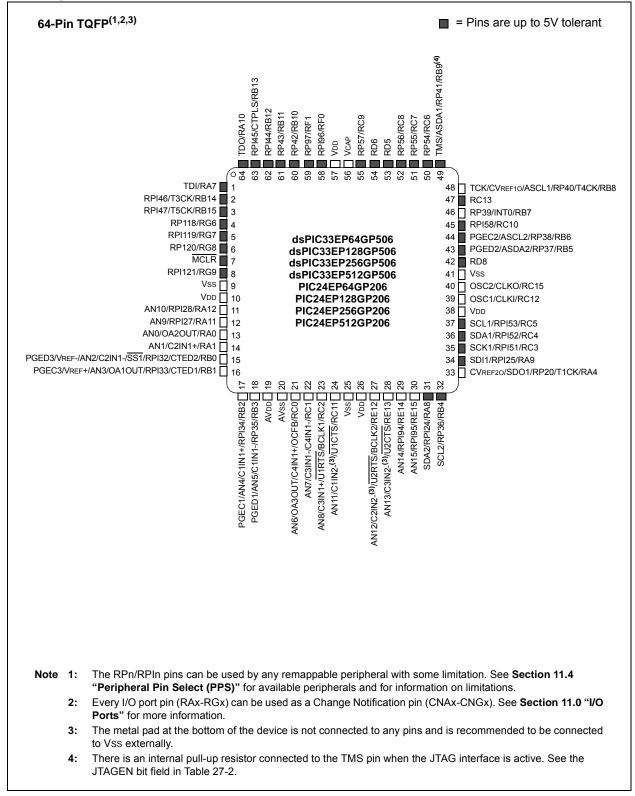

#### **Pin Diagrams (Continued)**

| TABLE 1-1: PINC                           |             | O DESC         | RIPT | IONS (CONTINUED)                                                                                           |  |  |

|-------------------------------------------|-------------|----------------|------|------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name <sup>(4)</sup>                   | Pin<br>Type | Buffer<br>Type | PPS  | Description                                                                                                |  |  |

| U2CTS                                     | Ι           | ST             | No   | UART2 Clear-To-Send.                                                                                       |  |  |

| U2RTS                                     | 0           | —              | No   | UART2 Ready-To-Send.                                                                                       |  |  |

| U2RX                                      | Ι           | ST             | Yes  | UART2 receive.                                                                                             |  |  |

| U2TX                                      | 0           | —              | Yes  | UART2 transmit.                                                                                            |  |  |

| BCLK2                                     | 0           | ST             | No   | UART2 IrDA <sup>®</sup> baud clock output.                                                                 |  |  |

| SCK1                                      | I/O         | ST             | No   | Synchronous serial clock input/output for SPI1.                                                            |  |  |

| SDI1                                      | I           | ST             | No   | SPI1 data in.                                                                                              |  |  |

| SDO1                                      | 0           | —              | No   | SPI1 data out.                                                                                             |  |  |

| SS1                                       | I/O         | ST             | No   | SPI1 slave synchronization or frame pulse I/O.                                                             |  |  |

| SCK2                                      | I/O         | ST             | Yes  | Synchronous serial clock input/output for SPI2.                                                            |  |  |

| SDI2                                      | I           | ST             | Yes  | SPI2 data in.                                                                                              |  |  |

| SDO2                                      | 0           | _              | Yes  | SPI2 data out.                                                                                             |  |  |

| SS2                                       | I/O         | ST             | Yes  | SPI2 slave synchronization or frame pulse I/O.                                                             |  |  |

| SCL1                                      | I/O         | ST             | No   | Synchronous serial clock input/output for I2C1.                                                            |  |  |

| SDA1                                      | I/O         | ST             | No   | Synchronous serial data input/output for I2C1.                                                             |  |  |

| ASCL1                                     | I/O         | ST             | No   | Alternate synchronous serial clock input/output for I2C1.                                                  |  |  |

| ASDA1                                     | I/O         | ST             | No   | Alternate synchronous serial data input/output for I2C1.                                                   |  |  |

| SCL2                                      | I/O         | ST             | No   | Synchronous serial clock input/output for I2C2.                                                            |  |  |

| SDA2                                      | I/O         | ST             | No   | Synchronous serial data input/output for I2C2.                                                             |  |  |

| ASCL2                                     | I/O         | ST             | No   | Alternate synchronous serial clock input/output for I2C2.                                                  |  |  |

| ASDA2                                     | I/O         | ST             | No   | Alternate synchronous serial data input/output for I2C2.                                                   |  |  |

| TMS <sup>(5)</sup>                        | Ι           | ST             | No   | JTAG Test mode select pin.                                                                                 |  |  |

| TCK                                       | Ι           | ST             | No   | JTAG test clock input pin.                                                                                 |  |  |

| TDI                                       | I           | ST             | No   | JTAG test data input pin.                                                                                  |  |  |

| TDO                                       | 0           | _              | No   | JTAG test data output pin.                                                                                 |  |  |

| C1RX <sup>(2)</sup>                       | Ι           | ST             | Yes  | ECAN1 bus receive pin.                                                                                     |  |  |

| C1TX <sup>(2)</sup>                       | 0           | _              | Yes  | ECAN1 bus transmit pin.                                                                                    |  |  |

| FLT1 <sup>(1)</sup> , FLT2 <sup>(1)</sup> | Ι           | ST             | Yes  | PWM Fault Inputs 1 and 2.                                                                                  |  |  |

| FLT3 <sup>(1)</sup> , FLT4 <sup>(1)</sup> | Ι           | ST             | No   | PWM Fault Inputs 3 and 4.                                                                                  |  |  |

| FLT32 <sup>(1,3)</sup>                    | Ι           | ST             | No   | PWM Fault Input 32 (Class B Fault).                                                                        |  |  |

| DTCMP1-DTCMP3 <sup>(1)</sup>              | Ι           | ST             | Yes  | PWM Dead-Time Compensation Inputs 1 through 3.                                                             |  |  |

| PWM1L-PWM3L <sup>(1)</sup>                | 0           | —              | No   | PWM Low Outputs 1 through 3.                                                                               |  |  |

| PWM1H-PWM3H <sup>(1)</sup>                | 0           | —              | No   | PWM High Outputs 1 through 3.                                                                              |  |  |

| SYNCI1 <sup>(1)</sup>                     | Ι           | ST             |      | PWM Synchronization Input 1.                                                                               |  |  |

| SYNCO1 <sup>(1)</sup>                     | 0           |                | Yes  | PWM Synchronization Output 1.                                                                              |  |  |

| INDX1 <sup>(1)</sup>                      | Ι           | ST             | Yes  | Quadrature Encoder Index1 pulse input.                                                                     |  |  |

| HOME1 <sup>(1)</sup>                      | Ι           | ST             | Yes  | Quadrature Encoder Home1 pulse input.                                                                      |  |  |

| QEA1 <sup>(1)</sup>                       | Ι           | ST             | Yes  | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer<br>external clock/gate input in Timer mode. |  |  |

| QEB1 <sup>(1)</sup>                       | ,           | ст             |      |                                                                                                            |  |  |

|                                           | Ι           | ST             | Yes  | Quadrature Encoder Phase B input in QEI1 mode. Auxiliary timer                                             |  |  |

| CNTCMP1 <sup>(1)</sup>                    | 0           |                | Yes  | external clock/gate input in Timer mode.<br>Quadrature Encoder Compare Output 1.                           |  |  |

|                                           | 0           | <br>ompatible  | 162  |                                                                                                            |  |  |

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend:

CMOS = CMOS compatible input or output

Analog = Analog input

ST = Schmitt Trigger input with CMOS levels

O = Output

PPS = Peripheral Pin Select

TTL = TTL input buffer

P = Power I = Input

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

5: There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

## 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for digital signal processing. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

## 3.1 Registers

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can act as a data, address or address offset register. The 16th working register (W15) operates as a Software Stack Pointer for interrupts and calls.

## 3.2 Instruction Set

The instruction set for dsPIC33EPXXXGP50X and dsPIC33EPXXXMC20X/50X devices has two classes of instructions: the MCU class of instructions and the DSP class of instructions. The instruction set for PIC24EPXXXGP/MC20X devices has the MCU class of instructions only and does not support DSP instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

#### 3.3 Data Space Addressing

The base Data Space can be addressed as 64 Kbytes (32K words).

The Data Space includes two ranges of memory, referred to as X and Y data memory. Each memory range is accessible through its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. On dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Spaces have memory locations that are device-specific, and are described further in the data memory maps in **Section 4.2 "Data Address Space"**.

The upper 32 Kbytes of the Data Space memory map can optionally be mapped into Program Space (PS) at any 32-Kbyte aligned program word boundary. The Program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Moreover, the Base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space (EDS) address. The EDS can be addressed as 8M words or 16 Mbytes. Refer to the "**Data Memory**" (DS70595) and "**Program Memory**" (DS70613) sections in the "*dsPIC33/PIC24 Family Reference Manual*" for more details on EDS, PSV and table accesses.

On the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data re-ordering for radix-2 FFT algorithms. PIC24EPXXXGP/MC20X devices do not support Modulo and Bit-Reversed Addressing.

## 3.4 Addressing Modes

The CPU supports these addressing modes:

- Inherent (no operand)

- Relative

- Literal

- · Memory Direct

- Register Direct

- Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

| R/W-0                | R/W-0                   | R/W-0                | R/W-0 | R/C-0 | R/C-0 | R-0   | R/W-0 |

|----------------------|-------------------------|----------------------|-------|-------|-------|-------|-------|

| OA                   | OB                      | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| bit 15               |                         |                      |       |       |       |       | bit 8 |

|                      |                         |                      |       |       |       |       |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>    | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|                      | IPL<2:0> <sup>(2)</sup> |                      | RA    | Ν     | OV    | Z     | С     |

| bit 7                |                         |                      |       |       |       |       | bit 0 |

|                      |                         |                      |       |       |       |       |       |

## REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>        |

|---------|----------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                               |

|         | 101 = CPU Interrupt Priority Level is 5 (13)                               |

|         | 100 = CPU Interrupt Priority Level is 4 (12)                               |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                               |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                               |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                |

- **Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 8-3: DMAXSTAH: DMA CHANNEL X START ADDRESS REGISTER A (HIGH)

| U-0            | U-0   | U-0            | U-0   | U-0          | U-0              | U-0    | U-0   |

|----------------|-------|----------------|-------|--------------|------------------|--------|-------|

| —              | _     | —              | —     | —            | —                | —      | —     |

| bit 15         |       |                |       |              |                  |        | bit 8 |

|                |       |                |       |              |                  |        |       |

| R/W-0          | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

|                |       |                | STA<  | 23:16>       |                  |        |       |

| bit 7          |       |                |       |              |                  |        | bit 0 |

|                |       |                |       |              |                  |        |       |

| Legend:        |       |                |       |              |                  |        |       |

| R = Readable b | oit   | W = Writable b | it    | U = Unimpler | mented bit, read | as '0' |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

#### bit 15-8 Unimplemented: Read as '0'

bit 7-0 STA<23:16>: Primary Start Address bits (source or destination)

#### REGISTER 8-4: DMAXSTAL: DMA CHANNEL x START ADDRESS REGISTER A (LOW)

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|-----------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                 |       |                  | STA   | <15:8>                                  |       |       |       |

| bit 15          |       |                  |       |                                         |       |       | bit 8 |

|                 |       |                  |       |                                         |       |       |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                 |       |                  | STA   | A<7:0>                                  |       |       |       |

| bit 7           |       |                  |       |                                         |       |       | bit 0 |

|                 |       |                  |       |                                         |       |       |       |

| Legend:         |       |                  |       |                                         |       |       |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-0 STA<15:0>: Primary Start Address bits (source or destination)

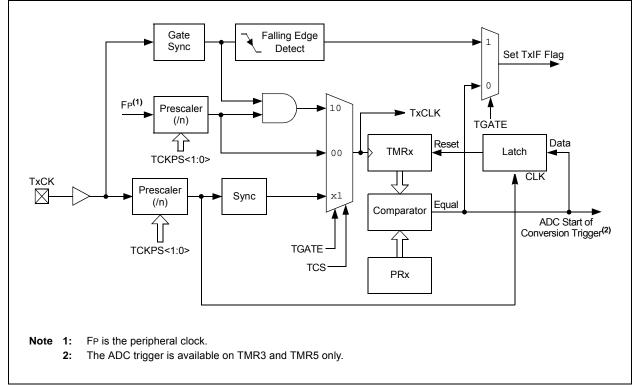

#### FIGURE 13-2: TYPE C TIMER BLOCK DIAGRAM (x = 3 AND 5)

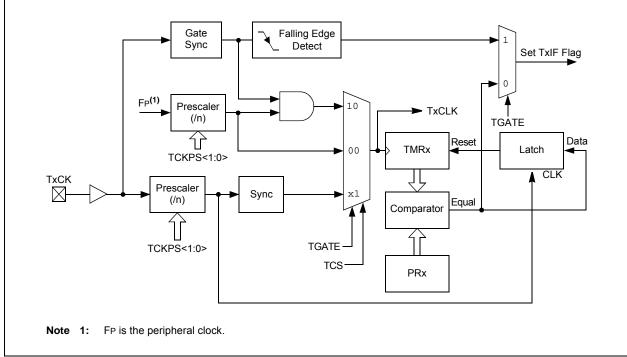

## FIGURE 13-1:TYPE B TIMER BLOCK DIAGRAM (x = 2 AND 4)

NOTES:

#### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER (CONTINUED)

| bit 6-4 | SYNCSRC<2:0>: Synchronous Source Selection bits <sup>(1)</sup><br>111 = Reserved<br>100 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-0 | 100 = Reserved<br>011 = PTGO17 <sup>(2)</sup><br>010 = PTGO16 <sup>(2)</sup><br>001 = Reserved<br>000 = SYNCI1 input from PPS<br>SEVTPS<3:0>: PWMx Special Event Trigger Output Postscaler Select bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1111 = 1:16 Postscaler generates Special Event Trigger on every sixteenth compare match event</li> <li>.</li> <l< td=""></l<></ul> |

|         | 0000 = 1:1 Postscaler generates Special Event Trigger on every second compare match event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

- **Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

| U-0                 | U-0                                                                                                                                                                                                                                              | U-0                                            | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |  |  |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------|----------------------|----------------------|----------------------|----------------------|--|--|--|

|                     | —                                                                                                                                                                                                                                                | _                                              | DISSCK                                | DISSDO               | MODE16               | SMP                  | CKE <sup>(1)</sup>   |  |  |  |

| bit 15              |                                                                                                                                                                                                                                                  | •                                              |                                       | •                    | •                    | •                    | bit                  |  |  |  |

| R/W-0               | R/W-0                                                                                                                                                                                                                                            | R/W-0                                          | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |  |  |  |

| SSEN <sup>(2)</sup> | CKP                                                                                                                                                                                                                                              | MSTEN                                          | SPRE2 <sup>(3)</sup>                  | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |  |  |  |

| bit 7               | CKF                                                                                                                                                                                                                                              | WIGTEN                                         | SFREZ 7                               | SFREI?               | SFREU 7              | FFREN                | bit                  |  |  |  |

|                     |                                                                                                                                                                                                                                                  |                                                |                                       |                      |                      |                      |                      |  |  |  |

| Legend:             |                                                                                                                                                                                                                                                  |                                                |                                       |                      |                      |                      |                      |  |  |  |

| R = Readabl         | le bit                                                                                                                                                                                                                                           | W = Writable                                   | bit                                   | U = Unimpler         | mented bit, read     | d as '0'             |                      |  |  |  |

| -n = Value at       | t POR                                                                                                                                                                                                                                            | '1' = Bit is se                                | t                                     | '0' = Bit is cle     | ared                 | x = Bit is unkr      | nown                 |  |  |  |

|                     |                                                                                                                                                                                                                                                  |                                                |                                       |                      |                      |                      |                      |  |  |  |

| bit 15-13           | Unimplemen                                                                                                                                                                                                                                       | ted: Read as                                   | 0'                                    |                      |                      |                      |                      |  |  |  |

| bit 12              |                                                                                                                                                                                                                                                  |                                                | bit (SPIx Mas                         | -                    | ()                   |                      |                      |  |  |  |

|                     |                                                                                                                                                                                                                                                  | PIx clock is di                                | sabled, pin fun                       | ctions as I/O        |                      |                      |                      |  |  |  |

| oit 11              |                                                                                                                                                                                                                                                  |                                                |                                       |                      |                      |                      |                      |  |  |  |

|                     |                                                                                                                                                                                                                                                  | <b>DISSDO:</b> Disable SDOx Pin bit            |                                       |                      |                      |                      |                      |  |  |  |

|                     | <ul> <li>1 = SDOx pin is not used by the module; pin functions as I/O</li> <li>0 = SDOx pin is controlled by the module</li> </ul>                                                                                                               |                                                |                                       |                      |                      |                      |                      |  |  |  |

| bit 10              | MODE16: Word/Byte Communication Select bit                                                                                                                                                                                                       |                                                |                                       |                      |                      |                      |                      |  |  |  |

|                     | 1 = Communication is word-wide (16 bits)                                                                                                                                                                                                         |                                                |                                       |                      |                      |                      |                      |  |  |  |

|                     |                                                                                                                                                                                                                                                  | ication is byte-                               | . ,                                   |                      |                      |                      |                      |  |  |  |

| bit 9               |                                                                                                                                                                                                                                                  | SMP: SPIx Data Input Sample Phase bit          |                                       |                      |                      |                      |                      |  |  |  |

|                     | Master mode                                                                                                                                                                                                                                      | -                                              | end of data o                         | utout time           |                      |                      |                      |  |  |  |

|                     |                                                                                                                                                                                                                                                  |                                                | middle of data                        |                      |                      |                      |                      |  |  |  |

|                     | Slave mode:                                                                                                                                                                                                                                      |                                                |                                       |                      |                      |                      |                      |  |  |  |

|                     | SMP must be cleared when SPIx is used in Slave mode.                                                                                                                                                                                             |                                                |                                       |                      |                      |                      |                      |  |  |  |

| bit 8               |                                                                                                                                                                                                                                                  | CKE: SPIx Clock Edge Select bit <sup>(1)</sup> |                                       |                      |                      |                      |                      |  |  |  |

|                     | <ul> <li>1 = Serial output data changes on transition from active clock state to Idle clock state (refer to bit 6)</li> <li>0 = Serial output data changes on transition from Idle clock state to active clock state (refer to bit 6)</li> </ul> |                                                |                                       |                      |                      |                      |                      |  |  |  |

| bit 7               |                                                                                                                                                                                                                                                  |                                                |                                       |                      |                      | ve clock state (I    |                      |  |  |  |

|                     | <b>SSEN:</b> Slave Select Enable bit (Slave mode) <sup>(2)</sup><br>1 = SSx pin is used for Slave mode                                                                                                                                           |                                                |                                       |                      |                      |                      |                      |  |  |  |

|                     | $1 = \frac{55x}{55x}$ pin is used for Slave mode<br>0 = SSx pin is not used by the module; pin is controlled by port function                                                                                                                    |                                                |                                       |                      |                      |                      |                      |  |  |  |

| bit 6               | CKP: Clock F                                                                                                                                                                                                                                     | <b>CKP:</b> Clock Polarity Select bit          |                                       |                      |                      |                      |                      |  |  |  |

|                     |                                                                                                                                                                                                                                                  |                                                | nigh level; activ<br>ow level; active |                      |                      |                      |                      |  |  |  |

| bit 5               | MSTEN: Mas                                                                                                                                                                                                                                       | ter Mode Enat                                  | ole bit                               |                      |                      |                      |                      |  |  |  |

|                     | 1 = Master m<br>0 = Slave mo                                                                                                                                                                                                                     |                                                |                                       |                      |                      |                      |                      |  |  |  |

| Note 1: T           | he CKE bit is not                                                                                                                                                                                                                                | used in Frame                                  | d SPI modes. I                        | Program this bi      | it to '0' for Fram   | ed SPI modes (       | FRMEN = 1            |  |  |  |

|                     | his bit must be cl                                                                                                                                                                                                                               |                                                |                                       |                      |                      |                      |                      |  |  |  |

| <b>0</b>            |                                                                                                                                                                                                                                                  |                                                |                                       |                      |                      |                      |                      |  |  |  |

#### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1

- **3:** Do not set both primary and secondary prescalers to the value of 1:1.

| R/W-0         | R/W-0                                    | R/W-0                                          | U-0        | U-0              | U-0             | U-0               | U-0    |  |  |  |

|---------------|------------------------------------------|------------------------------------------------|------------|------------------|-----------------|-------------------|--------|--|--|--|

| FRMEN         | SPIFSD                                   | FRMPOL                                         | —          | —                | _               | —                 | _      |  |  |  |

| bit 15        |                                          |                                                |            |                  |                 |                   | bit 8  |  |  |  |

|               |                                          |                                                |            |                  |                 |                   |        |  |  |  |

| U-0           | U-0                                      | U-0                                            | U-0        | U-0              | U-0             | R/W-0             | R/W-0  |  |  |  |

| _             | <u> </u>                                 | —                                              | _          |                  | _               | FRMDLY            | SPIBEN |  |  |  |

| bit 7         |                                          |                                                |            |                  |                 |                   | bit 0  |  |  |  |

|               |                                          |                                                |            |                  |                 |                   |        |  |  |  |

| Legend:       |                                          |                                                |            |                  |                 |                   |        |  |  |  |

| R = Readable  | e bit                                    | W = Writable b                                 | pit        | U = Unimpler     | nented bit, rea | ead as '0'        |        |  |  |  |

| -n = Value at | POR                                      | '1' = Bit is set                               |            | '0' = Bit is cle | ared            | x = Bit is unkr   | nown   |  |  |  |

|               |                                          |                                                |            |                  |                 |                   |        |  |  |  |

| bit 15        | FRMEN: Fra                               | FRMEN: Framed SPIx Support bit                 |            |                  |                 |                   |        |  |  |  |

|               |                                          | SPIx support is e<br>SPIx support is d         |            | x pin is used as | Frame Sync      | oulse input/outpu | it)    |  |  |  |

| bit 14        | SPIFSD: Fra                              | SPIFSD: Frame Sync Pulse Direction Control bit |            |                  |                 |                   |        |  |  |  |

|               |                                          | ync pulse input (<br>ync pulse output          |            |                  |                 |                   |        |  |  |  |

| bit 13        | FRMPOL: Fr                               | FRMPOL: Frame Sync Pulse Polarity bit          |            |                  |                 |                   |        |  |  |  |

|               | 1 = Frame Sync pulse is active-high      |                                                |            |                  |                 |                   |        |  |  |  |

|               |                                          | ync pulse is activ                             |            |                  |                 |                   |        |  |  |  |

| bit 12-2      | -                                        | nted: Read as '0                               |            |                  |                 |                   |        |  |  |  |

| bit 1         | FRMDLY: Frame Sync Pulse Edge Select bit |                                                |            |                  |                 |                   |        |  |  |  |

|               |                                          | ync pulse coincio<br>ync pulse preceo          |            |                  |                 |                   |        |  |  |  |

| bit 0         | SPIBEN: En                               | hanced Buffer Er                               | nable bit  |                  |                 |                   |        |  |  |  |

|               |                                          | d buffer is enable                             |            |                  |                 |                   |        |  |  |  |

|               | 0 = Enhance                              | d buffer is disabl                             | ed (Standa | rd mode)         |                 |                   |        |  |  |  |

|               |                                          |                                                |            |                  |                 |                   |        |  |  |  |

#### REGISTER 18-3: SPIXCON2: SPIX CONTROL REGISTER 2

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0           | U-0                                                    | U-0                                 | U-0            | U-0                | U-0              | U-0    | U-0    |

|---------------|--------------------------------------------------------|-------------------------------------|----------------|--------------------|------------------|--------|--------|

| —             | —                                                      | —                                   | _              | —                  | —                | —      | —      |

| bit 15        |                                                        |                                     |                |                    |                  |        | bit 8  |

|               |                                                        |                                     |                |                    |                  |        |        |

| U-0           | U-0                                                    | U-0                                 | R-0            | R-0                | R-0              | R-0    | R-0    |

| —             | —                                                      | —                                   | DNCNT4         | DNCNT3             | DNCNT2           | DNCNT1 | DNCNT0 |

| bit 7         |                                                        |                                     |                |                    |                  |        | bit 0  |

|               |                                                        |                                     |                |                    |                  |        |        |

| Legend:       |                                                        |                                     |                |                    |                  |        |        |

| R = Readable  | e bit                                                  | W = Writable                        | bit            | U = Unimpler       | mented bit, read | as '0' |        |

| -n = Value at | n = Value at POR '1' = Bit is set '0' = Bit is cleared |                                     | ared           | x = Bit is unknown |                  |        |        |

|               |                                                        |                                     |                |                    |                  |        |        |

| bit 15-5      | Unimplemen                                             | ted: Read as '                      | 0'             |                    |                  |        |        |

| bit 4-0       | DNCNT<4:0>                                             | : DeviceNet™                        | Filter Bit Num | iber bits          |                  |        |        |

|               |                                                        | 1 = Invalid sele<br>npares up to Da |                | 6 with EID<17      | >                |        |        |

|               | •                                                      |                                     |                |                    |                  |        |        |

|               | •                                                      |                                     |                |                    |                  |        |        |

|               | •                                                      |                                     |                |                    |                  |        |        |

|               |                                                        | npares up to Da<br>s not compare    | •              | 7 with EID<0>      |                  |        |        |

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| FLTEN15 | FLTEN14 | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10 | FLTEN9 | FLTEN8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

| FLTEN7  | FLTEN6  | FLTEN5  | FLTEN4  | FLTEN3  | FLTEN2  | FLTEN1 | FLTEN0 |

| bit 7   |         |         |         |         |         |        | bit 0  |

|         |         |         |         |         |         |        |        |

| Legend: |         |         |         |         |         |        |        |

#### REGISTER 21-11: CxFEN1: ECANx ACCEPTANCE FILTER ENABLE REGISTER 1

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0

FLTEN<15:0>: Enable Filter n to Accept Messages bits

1 = Enables Filter n

0 = Disables Filter n

REGISTER 21-12: CxBUFPNT1: ECANx FILTER 0-3 BUFFER POINTER REGISTER 1

| R/W-0         | R/W-0                                                 | R/W-0                                                                                                       | R/W-0                                          | R/W-0                                   | R/W-0          | R/W-0  | R/W-0 |  |

|---------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------|----------------|--------|-------|--|

|               | F3BI                                                  | P<3:0>                                                                                                      |                                                |                                         | F2BI           | P<3:0> |       |  |

| bit 15        |                                                       |                                                                                                             |                                                |                                         |                |        | bit 8 |  |

| R/W-0         | R/W-0                                                 | R/W-0                                                                                                       | R/W-0                                          | R/W-0                                   | R/W-0          | R/W-0  | R/W-0 |  |

| F1BP<3:0>     |                                                       |                                                                                                             |                                                | F0BI                                    | P<3:0>         |        |       |  |

| bit 7         |                                                       |                                                                                                             |                                                |                                         |                |        | bit ( |  |

| Legend:       |                                                       |                                                                                                             |                                                |                                         |                |        |       |  |

| R = Readable  | e bit                                                 | W = Writable                                                                                                | bit                                            | U = Unimplemented bit, read as '0'      |                |        |       |  |

| -n = Value at | POR                                                   | '1' = Bit is set                                                                                            |                                                | '0' = Bit is cleared x = Bit is unknown |                |        | nown  |  |

| bit 15-12     | 1111 = Filte<br>1110 = Filte<br>•<br>•<br>•<br>•<br>• | : RX Buffer Mas<br>er hits received in<br>er hits received in<br>er hits received in<br>er hits received in | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | iffer                                   |                |        |       |  |

| bit 11-8      | F2BP<3:0>                                             | : RX Buffer Mas                                                                                             | k for Filter 2 b                               | oits (same value                        | s as bits<15:1 | 2>)    |       |  |

| bit 7-4       | F1BP<3:0>                                             | : RX Buffer Mas                                                                                             | k for Filter 1 k                               | oits (same value                        | s as bits<15:1 | 2>)    |       |  |

|               |                                                       |                                                                                                             |                                                |                                         |                |        |       |  |

#### REGISTER 23-6: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER (CONTINUED)

| bit 4-0 | CH0SA<4:0>: Channel 0 Positive Input Select for Sample MUXA bits <sup>(1)</sup>                     |

|---------|-----------------------------------------------------------------------------------------------------|

|         | 11111 = Open; use this selection with CTMU capacitive and time measurement                          |

|         | 11110 = Channel 0 positive input is connected to the CTMU temperature measurement diode (CTMU TEMP) |

|         | 11101 = Reserved                                                                                    |

|         | 11100 = Reserved                                                                                    |

|         | 11011 = Reserved<br>11010 = Channel 0 positive input is the output of OA3/AN6 <sup>(2,3)</sup>      |

|         | 11010 =  Channel 0 positive input is the output of OA3/AN0 <sup>(2)</sup>                           |

|         | 11000 = Channel 0 positive input is the output of OA1/AN3 <sup>(2)</sup>                            |

|         | 10110 = Reserved                                                                                    |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | 10000 = Reserved                                                                                    |

|         | 01111 = Channel 0 positive input is AN15 <sup>(1,3)</sup>                                           |

|         | 01110 = Channel 0 positive input is AN14 <sup>(1,3)</sup>                                           |

|         | 01101 = Channel 0 positive input is AN13 <sup>(1,3)</sup>                                           |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | 00010 = Channel 0 positive input is $AN2^{(1,3)}$                                                   |

|         | 00001 = Channel 0 positive input is $AN1^{(1,3)}$                                                   |

|         | 00000 = Channel 0 positive input is AN0 <sup>(1,3)</sup>                                            |

|         |                                                                                                     |

- **Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

- 3: See the "Pin Diagrams" section for the available analog channels for each device.

| oit 3-0 | Step<br>Command        | OPTION<3:0> | Option Description                                                                                      |

|---------|------------------------|-------------|---------------------------------------------------------------------------------------------------------|

|         | PTGCTRL(1)             | 0000        | Reserved.                                                                                               |

|         |                        | 0001        | Reserved.                                                                                               |

|         |                        | 0010        | Disable Step Delay Timer (PTGSD).                                                                       |

|         |                        | 0011        | Reserved.                                                                                               |

|         |                        | 0100        | Reserved.                                                                                               |

|         |                        | 0101        | Reserved.                                                                                               |

|         |                        | 0110        | Enable Step Delay Timer (PTGSD).                                                                        |

|         |                        | 0111        | Reserved.                                                                                               |

|         |                        | 1000        | Start and wait for the PTG Timer0 to match the Timer0 Limit Register.                                   |

|         |                        | 1001        | Start and wait for the PTG Timer1 to match the Timer1 Limit Register.                                   |

|         |                        | 1010        | Reserved.                                                                                               |

|         |                        | 1011        | Wait for the software trigger bit transition from low-to-high before continuing (PTGSWT = $0$ to $1$ ). |

|         |                        | 1100        | Copy contents of the Counter 0 register to the AD1CHS0 register.                                        |

|         |                        | 1101        | Copy contents of the Counter 1 register to the AD1CHS0 register.                                        |

|         |                        | 1110        | Copy contents of the Literal 0 register to the AD1CHS0 register.                                        |

|         |                        | 1111        | Generate triggers indicated in the Broadcast Trigger Enable register (PTGBTE).                          |

|         | PTGADD <sup>(1)</sup>  | 0000        | Add contents of the PTGADJ register to the Counter 0 Limit register (PTGC0LIM).                         |

|         |                        | 0001        | Add contents of the PTGADJ register to the Counter 1 Limit register (PTGC1LIM).                         |

|         |                        | 0010        | Add contents of the PTGADJ register to the Timer0 Limit register (PTGT0LIM).                            |

|         |                        | 0011        | Add contents of the PTGADJ register to the Timer1 Limit register (PTGT1LIM).                            |

|         |                        | 0100        | Add contents of the PTGADJ register to the Step Delay Limit register (PTGSDLIM)                         |

|         |                        | 0101        | Add contents of the PTGADJ register to the Literal 0 register (PTGL0).                                  |

|         |                        | 0110        | Reserved.                                                                                               |

|         |                        | 0111        | Reserved.                                                                                               |

|         | PTGCOPY <sup>(1)</sup> | 1000        | Copy contents of the PTGHOLD register to the Counter 0 Limit register (PTGC0LIM).                       |

|         |                        | 1001        | Copy contents of the PTGHOLD register to the Counter 1 Limit register (PTGC1LIM).                       |

|         |                        | 1010        | Copy contents of the PTGHOLD register to the Timer0 Limit register (PTGT0LIM).                          |

|         |                        | 1011        | Copy contents of the PTGHOLD register to the Timer1 Limit register (PTGT1LIM).                          |

|         |                        | 1100        | Copy contents of the PTGHOLD register to the Step Delay Limit register (PTGSDLIM).                      |

|         |                        | 1101        | Copy contents of the PTGHOLD register to the Literal 0 register (PTGL0).                                |

|         |                        | 1110        | Reserved.                                                                                               |

|         |                        | 1111        | Reserved.                                                                                               |

#### TABLE 24-1: PTG STEP COMMAND FORMAT (CONTINUED)

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

2: Refer to Table 24-2 for the trigger output descriptions.

3: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

| bit 3-0 | Step<br>Command        | OPTION<3:0> | Option Description                                          |

|---------|------------------------|-------------|-------------------------------------------------------------|

|         | PTGWHI(1)              | 0000        | PWM Special Event Trigger. <sup>(3)</sup>                   |

|         | or (1)                 | 0001        | PWM master time base synchronization output. <sup>(3)</sup> |

|         | PTGWLO(1)              | 0010        | PWM1 interrupt. <sup>(3)</sup>                              |

|         |                        | 0011        | PWM2 interrupt. <sup>(3)</sup>                              |

|         |                        | 0100        | PWM3 interrupt. <sup>(3)</sup>                              |

|         |                        | 0101        | Reserved.                                                   |

|         |                        | 0110        | Reserved.                                                   |

|         |                        | 0111        | OC1 Trigger event.                                          |

|         |                        | 1000        | OC2 Trigger event.                                          |

|         |                        | 1001        | IC1 Trigger event.                                          |

|         |                        | 1010        | CMP1 Trigger event.                                         |

|         |                        | 1011        | CMP2 Trigger event.                                         |

|         |                        | 1100        | CMP3 Trigger event.                                         |

|         |                        | 1101        | CMP4 Trigger event.                                         |

|         |                        | 1110        | ADC conversion done interrupt.                              |

|         |                        | 1111        | INT2 external interrupt.                                    |

|         | PTGIRQ(1)              | 0000        | Generate PTG Interrupt 0.                                   |

|         |                        | 0001        | Generate PTG Interrupt 1.                                   |

|         |                        | 0010        | Generate PTG Interrupt 2.                                   |

|         |                        | 0011        | Generate PTG Interrupt 3.                                   |

|         |                        | 0100        | Reserved.                                                   |

|         |                        | •           | •                                                           |

|         |                        | •           | •                                                           |

|         |                        | •           | •                                                           |

|         | (2)                    | 1111        | Reserved.                                                   |

|         | PTGTRIG <sup>(2)</sup> | 00000       | PTGO0.                                                      |

|         |                        | 00001       | PTGO1.                                                      |

|         |                        | •           | •                                                           |

|         |                        | •           | •                                                           |