## E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | - ·                                                                            |

| RAM Size                   | 8K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 28-SPDIP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128mc202-i-sp |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

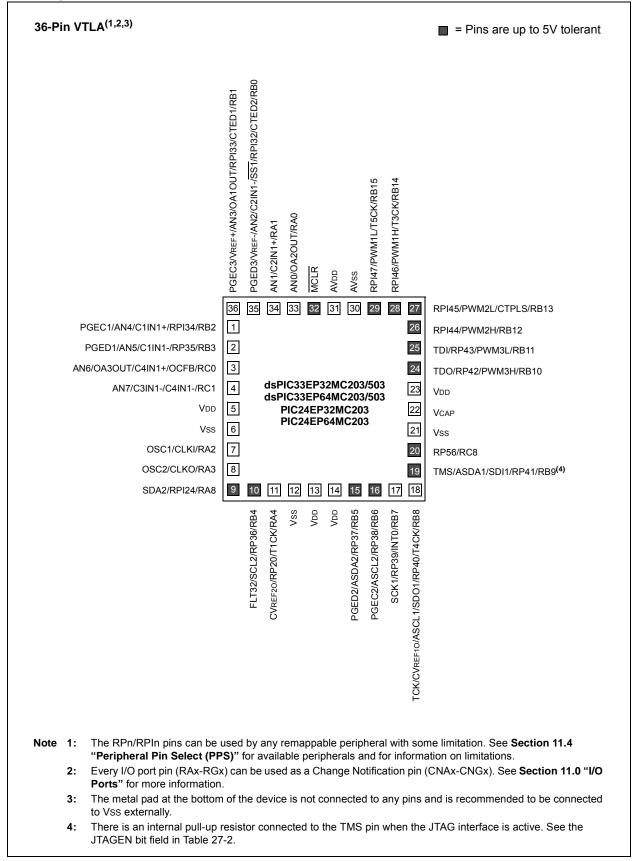

#### Pin Diagrams (Continued)

| Pin Name <sup>(4)</sup>                        | Pin<br>Type         | Buffer<br>Type          | PPS              | Description                                                                                                                                                                        |  |  |  |  |  |

|------------------------------------------------|---------------------|-------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| AN0-AN15                                       | Ι                   | Analog                  | No               | Analog input channels.                                                                                                                                                             |  |  |  |  |  |

| CLKI                                           | I                   | ST/<br>CMOS             | No               | External clock source input. Always associated with OSC1 pin function                                                                                                              |  |  |  |  |  |

| CLKO                                           | 0                   | —                       | No               | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |  |  |  |  |  |

| OSC1                                           | Ι                   | ST/                     | No               | Oscillator crystal input. ST buffer when configured in RC mode; CMOS                                                                                                               |  |  |  |  |  |

| OSC2                                           | I/O                 | CMOS<br>—               | No               | otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.                          |  |  |  |  |  |

| REFCLKO                                        | 0                   |                         | Yes              | Reference clock output.                                                                                                                                                            |  |  |  |  |  |

| IC1-IC4                                        | Ι                   | ST                      | Yes              | Capture Inputs 1 through 4.                                                                                                                                                        |  |  |  |  |  |

| OCFA<br>OCFB<br>OC1-OC4                        | <br> <br> <br>0     | ST<br>ST                | Yes<br>No<br>Yes | Compare Fault A input (for Compare channels).<br>Compare Fault B input (for Compare channels).<br>Compare Outputs 1 through 4.                                                     |  |  |  |  |  |

| INT0                                           | I                   | ST                      | No               | External Interrupt 0.                                                                                                                                                              |  |  |  |  |  |

| INT1<br>INT2                                   |                     | ST<br>ST                | Yes<br>Yes       | External Interrupt 1.<br>External Interrupt 2.                                                                                                                                     |  |  |  |  |  |

| RA0-RA4, RA7-RA12                              | I/O                 | ST                      | No               | PORTA is a bidirectional I/O port.                                                                                                                                                 |  |  |  |  |  |

| RB0-RB15                                       | I/O                 | ST                      | No               | PORTB is a bidirectional I/O port.                                                                                                                                                 |  |  |  |  |  |

| RC0-RC13, RC15                                 | I/O                 | ST                      | No               | PORTC is a bidirectional I/O port.                                                                                                                                                 |  |  |  |  |  |

| RD5, RD6, RD8                                  | I/O                 | ST                      | No               | PORTD is a bidirectional I/O port.                                                                                                                                                 |  |  |  |  |  |

| RE12-RE15                                      | I/O                 | ST                      | No               | PORTE is a bidirectional I/O port.                                                                                                                                                 |  |  |  |  |  |

| RF0, RF1                                       | I/O                 | ST                      | No               | PORTF is a bidirectional I/O port.                                                                                                                                                 |  |  |  |  |  |

| RG6-RG9                                        | I/O                 | ST                      | No               | PORTG is a bidirectional I/O port.                                                                                                                                                 |  |  |  |  |  |

| T1CK                                           | Ι                   | ST                      | No               | Timer1 external clock input.                                                                                                                                                       |  |  |  |  |  |

| T2CK<br>T3CK                                   |                     | ST<br>ST                | Yes              | Timer2 external clock input.                                                                                                                                                       |  |  |  |  |  |

| T4CK                                           |                     | ST                      | No<br>No         | Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                       |  |  |  |  |  |

| T5CK                                           | i                   | ST                      | No               | Timer5 external clock input.                                                                                                                                                       |  |  |  |  |  |

| CTPLS                                          | 0                   | ST                      | No               | CTMU pulse output.                                                                                                                                                                 |  |  |  |  |  |

| CTED1                                          | Ι                   | ST                      | No               | CTMU External Edge Input 1.                                                                                                                                                        |  |  |  |  |  |

| CTED2                                          | Ι                   | ST                      | No               | CTMU External Edge Input 2.                                                                                                                                                        |  |  |  |  |  |

| U1CTS                                          | Ι                   | ST                      | No               | UART1 Clear-To-Send.                                                                                                                                                               |  |  |  |  |  |

| U1RTS                                          | 0                   |                         | No               | UART1 Ready-To-Send.                                                                                                                                                               |  |  |  |  |  |

| U1RX                                           |                     | ST                      | Yes              | UART1 receive.<br>UART1 transmit.                                                                                                                                                  |  |  |  |  |  |

| U1TX<br>BCLK1                                  | 0                   | ST                      | Yes<br>No        | UART1 Iransmit.<br>UART1 IrDA <sup>®</sup> baud clock output.                                                                                                                      |  |  |  |  |  |

| Legend: CMOS = CM<br>ST = Schmi<br>PPS = Perip | MOS co<br>itt Trigg | ompatible<br>er input v | input<br>with CN | or output Analog = Analog input P = Power                                                                                                                                          |  |  |  |  |  |

#### TABLE 1-1:PINOUT I/O DESCRIPTIONS

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

| TABLE 1-1:       PINOUT I/O DESCRIPTIONS (CONTINUED) |             |                |     |                                                                                  |  |  |  |  |

|------------------------------------------------------|-------------|----------------|-----|----------------------------------------------------------------------------------|--|--|--|--|

| Pin Name <sup>(4)</sup>                              | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                      |  |  |  |  |

| U2CTS                                                | Ι           | ST             | No  | UART2 Clear-To-Send.                                                             |  |  |  |  |

| U2RTS                                                | 0           | —              | No  | UART2 Ready-To-Send.                                                             |  |  |  |  |

| U2RX                                                 | Ι           | ST             | Yes | UART2 receive.                                                                   |  |  |  |  |

| U2TX                                                 | 0           | —              | Yes | UART2 transmit.                                                                  |  |  |  |  |

| BCLK2                                                | 0           | ST             | No  | UART2 IrDA <sup>®</sup> baud clock output.                                       |  |  |  |  |

| SCK1                                                 | I/O         | ST             | No  | Synchronous serial clock input/output for SPI1.                                  |  |  |  |  |

| SDI1                                                 | I           | ST             | No  | SPI1 data in.                                                                    |  |  |  |  |

| SDO1                                                 | 0           | —              | No  | SPI1 data out.                                                                   |  |  |  |  |

| SS1                                                  | I/O         | ST             | No  | SPI1 slave synchronization or frame pulse I/O.                                   |  |  |  |  |

| SCK2                                                 | I/O         | ST             | Yes | Synchronous serial clock input/output for SPI2.                                  |  |  |  |  |

| SDI2                                                 | I           | ST             | Yes | SPI2 data in.                                                                    |  |  |  |  |

| SDO2                                                 | 0           | _              | Yes | SPI2 data out.                                                                   |  |  |  |  |

| SS2                                                  | I/O         | ST             | Yes | SPI2 slave synchronization or frame pulse I/O.                                   |  |  |  |  |

| SCL1                                                 | I/O         | ST             | No  | Synchronous serial clock input/output for I2C1.                                  |  |  |  |  |

| SDA1                                                 | I/O         | ST             | No  | Synchronous serial data input/output for I2C1.                                   |  |  |  |  |

| ASCL1                                                | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C1.                        |  |  |  |  |

| ASDA1                                                | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C1.                         |  |  |  |  |

| SCL2                                                 | I/O         | ST             | No  | Synchronous serial clock input/output for I2C2.                                  |  |  |  |  |

| SDA2                                                 | I/O         | ST             | No  | Synchronous serial data input/output for I2C2.                                   |  |  |  |  |

| ASCL2                                                | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C2.                        |  |  |  |  |

| ASDA2                                                | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C2.                         |  |  |  |  |

| TMS <sup>(5)</sup>                                   | Ι           | ST             | No  | JTAG Test mode select pin.                                                       |  |  |  |  |

| TCK                                                  | Ι           | ST             | No  | JTAG test clock input pin.                                                       |  |  |  |  |

| TDI                                                  | I           | ST             | No  | JTAG test data input pin.                                                        |  |  |  |  |

| TDO                                                  | 0           | _              | No  | JTAG test data output pin.                                                       |  |  |  |  |

| C1RX <sup>(2)</sup>                                  | Ι           | ST             | Yes | ECAN1 bus receive pin.                                                           |  |  |  |  |

| C1TX <sup>(2)</sup>                                  | 0           | _              | Yes | ECAN1 bus transmit pin.                                                          |  |  |  |  |

| FLT1 <sup>(1)</sup> , FLT2 <sup>(1)</sup>            | Ι           | ST             | Yes | PWM Fault Inputs 1 and 2.                                                        |  |  |  |  |

| FLT3 <sup>(1)</sup> , FLT4 <sup>(1)</sup>            | Ι           | ST             | No  | PWM Fault Inputs 3 and 4.                                                        |  |  |  |  |

| FLT32 <sup>(1,3)</sup>                               | Ι           | ST             | No  | PWM Fault Input 32 (Class B Fault).                                              |  |  |  |  |

| DTCMP1-DTCMP3 <sup>(1)</sup>                         | Ι           | ST             | Yes | PWM Dead-Time Compensation Inputs 1 through 3.                                   |  |  |  |  |

| PWM1L-PWM3L <sup>(1)</sup>                           | 0           | —              | No  | PWM Low Outputs 1 through 3.                                                     |  |  |  |  |

| PWM1H-PWM3H <sup>(1)</sup>                           | 0           | —              | No  | PWM High Outputs 1 through 3.                                                    |  |  |  |  |

| SYNCI1 <sup>(1)</sup>                                | Ι           | ST             |     | PWM Synchronization Input 1.                                                     |  |  |  |  |

| SYNCO1 <sup>(1)</sup>                                | 0           |                | Yes | PWM Synchronization Output 1.                                                    |  |  |  |  |

| INDX1 <sup>(1)</sup>                                 | Ι           | ST             | Yes | Quadrature Encoder Index1 pulse input.                                           |  |  |  |  |

| HOME1 <sup>(1)</sup>                                 | Ι           | ST             | Yes | Quadrature Encoder Home1 pulse input.                                            |  |  |  |  |

| QEA1 <sup>(1)</sup>                                  | Ι           | ST             | Yes | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer                   |  |  |  |  |

| QEB1 <sup>(1)</sup>                                  | ,           | ст             | Vee | external clock/gate input in Timer mode.                                         |  |  |  |  |

|                                                      | Ι           | ST             | Yes | Quadrature Encoder Phase B input in QEI1 mode. Auxiliary timer                   |  |  |  |  |

| CNTCMP1 <sup>(1)</sup>                               | 0           |                | Yes | external clock/gate input in Timer mode.<br>Quadrature Encoder Compare Output 1. |  |  |  |  |

|                                                      | 0           |                | 162 |                                                                                  |  |  |  |  |

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend:

CMOS = CMOS compatible input or output

Analog = Analog input

ST = Schmitt Trigger input with CMOS levels

O = Output

PPS = Peripheral Pin Select

TTL = TTL input buffer

P = Power I = Input

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

5: There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

|                 |       |        |                  |         |         |         |            |         |          |         |        |       |       |        |          |          |        | All    |

|-----------------|-------|--------|------------------|---------|---------|---------|------------|---------|----------|---------|--------|-------|-------|--------|----------|----------|--------|--------|

| File Name       | Addr. | Bit 15 | Bit 14           | Bit 13  | Bit 12  | Bit 11  | Bit 10     | Bit 9   | Bit 8    | Bit 7   | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1    | Bit 0  | Resets |

| PTGCST          | 0AC0  | PTGEN  | —                | PTGSIDL | PTGTOGL |         | PTGSWT     | PTGSSEN | PTGIVIS  | PTGSTRT | PTGWTO | _     | _     | —      | —        | PTGIT    | M<1:0> | 0000   |

| PTGCON          | 0AC2  | F      | PTGCLK<2         | :0>     |         | F       | PTGDIV<4:0 | >       |          |         | PTGPWD | <3:0> |       | _      | P        | TGWDT<2: | 0>     | 0000   |

| PTGBTE          | 0AC4  |        | ADC              | TS<4:1> |         | IC4TSS  | IC3TSS     | IC2TSS  | IC1TSS   | OC4CS   | OC3CS  | OC2CS | OC1CS | OC4TSS | OC3TSS   | OC2TSS   | OC1TSS | 0000   |

| PTGHOLD         | 0AC6  |        |                  |         |         |         |            |         | PTGHOLD  | <15:0>  |        |       |       |        |          |          |        | 0000   |

| <b>PTGT0LIM</b> | 0AC8  |        | PTGT0LIM<15:0> 0 |         |         |         |            |         |          |         |        |       | 0000  |        |          |          |        |        |

| PTGT1LIM        | 0ACA  |        |                  |         |         |         |            |         | PTGT1LIM | <15:0>  |        |       |       |        |          |          |        | 0000   |

| PTGSDLIM        | 0ACC  |        |                  |         |         |         |            |         | PTGSDLIN | l<15:0> |        |       |       |        |          |          |        | 0000   |

| <b>PTGC0LIM</b> | 0ACE  |        |                  |         |         |         |            |         | PTGC0LIN | <15:0>  |        |       |       |        |          |          |        | 0000   |

| PTGC1LIM        | 0AD0  |        |                  |         |         |         |            |         | PTGC1LIN | <15:0>  |        |       |       |        |          |          |        | 0000   |

| PTGADJ          | 0AD2  |        |                  |         |         |         |            |         | PTGADJ<  | :15:0>  |        |       |       |        |          |          |        | 0000   |

| PTGL0           | 0AD4  |        |                  |         |         |         |            |         | PTGL0<   | 15:0>   |        |       |       |        |          |          |        | 0000   |

| PTGQPTR         | 0AD6  | —      | —                | —       | —       | _       | —          | —       | _        | —       | —      | -     |       | P      | TGQPTR<4 | 4:0>     |        | 0000   |

| PTGQUE0         | 0AD8  |        |                  |         | STEP    | 1<7:0>  |            |         |          |         |        |       | STEPO | )<7:0> |          |          |        | 0000   |

| PTGQUE1         | 0ADA  |        |                  |         | STEP    | '3<7:0> |            |         |          |         |        |       | STEP2 | 2<7:0> |          |          |        | 0000   |

| PTGQUE2         | 0ADC  |        |                  |         | STEP    | 25<7:0> |            |         |          |         |        |       | STEP4 | <7:0>  |          |          |        | 0000   |

| PTGQUE3         | 0ADE  |        |                  |         | STEP    | 7<7:0>  |            |         |          |         |        |       | STEP6 | 6<7:0> |          |          |        | 0000   |

| PTGQUE4         | 0AE0  |        |                  |         | STEP    | 9<7:0>  |            |         |          |         |        |       | STEP8 | 8<7:0> |          |          |        | 0000   |

| PTGQUE5         | 0AE2  |        |                  |         | STEP    | 11<7:0> |            |         |          |         |        |       | STEP1 | 0<7:0> |          |          |        | 0000   |

| PTGQUE6         | 0AE4  |        |                  |         | STEP    | 13<7:0> |            |         |          |         |        |       | STEP1 | 2<7:0> |          |          |        | 0000   |

| PTGQUE7         | 0AE6  |        |                  |         | STEP    | 15<7:0> |            |         |          |         |        |       | STEP1 | 4<7:0> |          |          |        | 0000   |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 78

#### 4.5 Instruction Addressing Modes

The addressing modes shown in Table 4-63 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

#### 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

#### 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

- Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

#### TABLE 4-63: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

|                                                     | Vector  | IRQ        |                   | Interrupt Bit Location |          |              |  |  |

|-----------------------------------------------------|---------|------------|-------------------|------------------------|----------|--------------|--|--|

| Interrupt Source                                    | #       | #          | IVT Address       | Flag                   | Enable   | Priority     |  |  |

| QEI1 – QEI1 Position Counter Compare <sup>(2)</sup> | 66      | 58         | 0x000088          | IFS3<10>               | IEC3<10> | IPC14<10:8>  |  |  |

| Reserved                                            | 67-72   | 59-64      | 0x00008A-0x000094 | _                      | _        | _            |  |  |

| U1E – UART1 Error Interrupt                         | 73      | 65         | 0x000096          | IFS4<1>                | IEC4<1>  | IPC16<6:4>   |  |  |

| U2E – UART2 Error Interrupt                         | 74      | 66         | 0x000098          | IFS4<2>                | IEC4<2>  | IPC16<10:8>  |  |  |

| CRC – CRC Generator Interrupt                       | 75      | 67         | 0x00009A          | IFS4<3>                | IEC4<3>  | IPC16<14:12> |  |  |

| Reserved                                            | 76-77   | 68-69      | 0x00009C-0x00009E | —                      | _        | —            |  |  |

| C1TX – CAN1 TX Data Request <sup>(1)</sup>          | 78      | 70         | 0x000A0           | IFS4<6>                | IEC4<6>  | IPC17<10:8>  |  |  |

| Reserved                                            | 79-84   | 71-76      | 0x0000A2-0x0000AC | —                      | _        | —            |  |  |

| CTMU – CTMU Interrupt                               | 85      | 77         | 0x0000AE          | IFS4<13>               | IEC4<13> | IPC19<6:4>   |  |  |

| Reserved                                            | 86-101  | 78-93      | 0x0000B0-0x0000CE | —                      | _        | —            |  |  |

| PWM1 – PWM Generator 1 <sup>(2)</sup>               | 102     | 94         | 0x0000D0          | IFS5<14>               | IEC5<14> | IPC23<10:8>  |  |  |

| PWM2 – PWM Generator 2 <sup>(2)</sup>               | 103     | 95         | 0x0000D2          | IFS5<15>               | IEC5<15> | IPC23<14:12> |  |  |

| PWM3 – PWM Generator 3 <sup>(2)</sup>               | 104     | 96         | 0x0000D4          | IFS6<0>                | IEC6<0>  | IPC24<2:0>   |  |  |

| Reserved                                            | 105-149 | 97-141     | 0x0001D6-0x00012E | —                      | _        | —            |  |  |

| ICD – ICD Application                               | 150     | 142        | 0x000142          | IFS8<14>               | IEC8<14> | IPC35<10:8>  |  |  |

| JTAG – JTAG Programming                             | 151     | 143        | 0x000130          | IFS8<15>               | IEC8<15> | IPC35<14:12> |  |  |

| Reserved                                            | 152     | 144        | 0x000134          | —                      | —        | _            |  |  |

| PTGSTEP – PTG Step                                  | 153     | 145        | 0x000136          | IFS9<1>                | IEC9<1>  | IPC36<6:4>   |  |  |

| PTGWDT – PTG Watchdog Time-out                      | 154     | 146        | 0x000138          | IFS9<2>                | IEC9<2>  | IPC36<10:8>  |  |  |

| PTG0 – PTG Interrupt 0                              | 155     | 147        | 0x00013A          | IFS9<3>                | IEC9<3>  | IPC36<14:12> |  |  |

| PTG1 – PTG Interrupt 1                              | 156     | 148        | 0x00013C          | IFS9<4>                | IEC9<4>  | IPC37<2:0>   |  |  |

| PTG2 – PTG Interrupt 2                              | 157     | 149        | 0x00013E          | IFS9<5>                | IEC9<5>  | IPC37<6:4>   |  |  |

| PTG3 – PTG Interrupt 3                              | 158     | 150        | 0x000140          | IFS9<6>                | IEC9<6>  | IPC37<10:8>  |  |  |

| Reserved                                            | 159-245 | 151-245    | 0x000142-0x0001FE | —                      | —        | _            |  |  |

|                                                     | Lowe    | est Natura | I Order Priority  |                        |          |              |  |  |

#### TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

2: This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

| R/W-0                  | R/W-0                          | R/W-0                     | R/W-0                             | R/W-0                                | R/W-0                 | R/W-0                | R/W-0                |

|------------------------|--------------------------------|---------------------------|-----------------------------------|--------------------------------------|-----------------------|----------------------|----------------------|

| NSTDIS                 | OVAERR <sup>(1)</sup>          | OVBERR <sup>(1)</sup>     | COVAERR <sup>(1)</sup>            | COVBERR <sup>(1)</sup>               | OVATE <sup>(1)</sup>  | OVBTE <sup>(1)</sup> | COVTE <sup>(1)</sup> |

| pit 15                 |                                |                           |                                   |                                      |                       |                      | bit 8                |

|                        |                                |                           |                                   |                                      |                       |                      |                      |

| R/W-0                  | R/W-0                          | R/W-0                     | R/W-0                             | R/W-0                                | R/W-0                 | R/W-0                | U-0                  |

| SFTACERR <sup>(1</sup> | ) DIV0ERR                      | DMACERR                   | MATHERR                           | ADDRERR                              | STKERR                | OSCFAIL              | —                    |

| pit 7                  |                                |                           |                                   |                                      |                       |                      | bit 0                |

|                        |                                |                           |                                   |                                      |                       |                      |                      |

| _egend:                |                                |                           |                                   |                                      |                       |                      |                      |

| R = Readable           |                                | W = Writable              |                                   | U = Unimpleme                        |                       |                      |                      |

| n = Value at           | POR                            | '1' = Bit is set          |                                   | '0' = Bit is clear                   | ed                    | x = Bit is unk       | nown                 |

| bit 15                 | NSTDIS: Inte                   | errupt Nesting            | Disable hit                       |                                      |                       |                      |                      |

|                        |                                | nesting is disa           |                                   |                                      |                       |                      |                      |

|                        | •                              | nesting is ena            |                                   |                                      |                       |                      |                      |

| pit 14                 | -                              | -                         | Overflow Trap F                   | lag bit <sup>(1)</sup>               |                       |                      |                      |

|                        |                                |                           | erflow of Accur                   |                                      |                       |                      |                      |

|                        | =                              |                           | overflow of A                     |                                      |                       |                      |                      |

| pit 13                 |                                |                           | Overflow Trap F                   | •                                    |                       |                      |                      |

|                        |                                |                           | erflow of Accur                   |                                      |                       |                      |                      |

| pit 12                 | -                              |                           |                                   | Overflow Trap Fla                    | ag bit <sup>(1)</sup> |                      |                      |

|                        | 1 = Trap was                   | caused by ca              | tastrophic over                   | flow of Accumula                     | ator A                |                      |                      |

| pit 11                 |                                |                           |                                   | Overflow Trap Fla                    |                       |                      |                      |

|                        |                                |                           | •                                 | flow of Accumula                     | •                     |                      |                      |

|                        | =                              |                           | -                                 | overflow of Accur                    | nulator B             |                      |                      |

| pit 10                 |                                |                           | erflow Trap Ena                   | able bit <sup>(1)</sup>              |                       |                      |                      |

|                        | 1 = Trap ove<br>0 = Trap is d  | rflow of Accum            | ulator A                          |                                      |                       |                      |                      |

| pit 9                  | OVBTE: Acc                     | umulator B Ov             | erflow Trap En                    | able bit <sup>(1)</sup>              |                       |                      |                      |

|                        | 1 = Trap ove<br>0 = Trap is d  | rflow of Accum<br>isabled | ulator B                          |                                      |                       |                      |                      |

| oit 8                  | COVTE: Cat                     | astrophic Over            | flow Trap Enat                    | ole bit <sup>(1)</sup>               |                       |                      |                      |

|                        | 1 = Trap on o<br>0 = Trap is d |                           | erflow of Accu                    | mulator A or B is                    | enabled               |                      |                      |

| oit 7                  | SFTACERR:                      | Shift Accumul             | ator Error Statu                  | us bit <sup>(1)</sup>                |                       |                      |                      |

|                        |                                | •                         | •                                 | alid accumulator<br>invalid accumula |                       |                      |                      |

| oit 6                  | DIV0ERR: D                     | ivide-by-Zero I           | Error Status bit                  |                                      |                       |                      |                      |

|                        |                                |                           | used by a divide<br>caused by a d |                                      |                       |                      |                      |

|                        | DMACERR:                       |                           |                                   | -                                    |                       |                      |                      |

| oit 5                  |                                |                           |                                   |                                      |                       |                      |                      |

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

#### 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.4.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

#### 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs. In comparison, some digital-only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include  $I^2C^{TM}$  and the PWM. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheralselectable pin is handled in two different ways, depending on whether an input or output is being mapped.

#### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER (CONTINUED)

| bit 6-4 | SYNCSRC<2:0>: Synchronous Source Selection bits <sup>(1)</sup><br>111 = Reserved<br>100 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-0 | 100 = Reserved<br>011 = PTGO17 <sup>(2)</sup><br>010 = PTGO16 <sup>(2)</sup><br>001 = Reserved<br>000 = SYNCI1 input from PPS<br>SEVTPS<3:0>: PWMx Special Event Trigger Output Postscaler Select bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1111 = 1:16 Postscaler generates Special Event Trigger on every sixteenth compare match event</li> <li>.</li> <l< td=""></l<></ul> |

|         | 0000 = 1:1 Postscaler generates Special Event Trigger on every second compare match event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

- **Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

#### REGISTER 17-1: QEI1CON: QEI1 CONTROL REGISTER (CONTINUED)

| bit 6-4 | <b>INTDIV&lt;2:0&gt;:</b> Timer Input Clock Prescale Select bits (interval timer, main timer (position counter), velocity counter and index counter internal clock divider select) <sup>(3)</sup>                                                                                                                            |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = 1:128 prescale value<br/>110 = 1:64 prescale value<br/>101 = 1:32 prescale value<br/>100 = 1:16 prescale value<br/>011 = 1:8 prescale value<br/>010 = 1:4 prescale value<br/>001 = 1:2 prescale value<br/>000 = 1:1 prescale value</pre>                                                                          |

| bit 3   | <b>CNTPOL:</b> Position and Index Counter/Timer Direction Select bit<br>1 = Counter direction is negative unless modified by external up/down signal                                                                                                                                                                         |

|         | <ul> <li>0 = Counter direction is positive unless modified by external up/down signal</li> </ul>                                                                                                                                                                                                                             |

| bit 2   | GATEN: External Count Gate Enable bit                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = External gate signal controls position counter operation</li> <li>0 = External gate signal does not affect position counter/timer operation</li> </ul>                                                                                                                                                          |

| bit 1-0 | CCM<1:0>: Counter Control Mode Selection bits                                                                                                                                                                                                                                                                                |

|         | <ul> <li>11 = Internal Timer mode with optional external count is selected</li> <li>10 = External clock count with optional external count is selected</li> <li>01 = External clock count with external up/down direction is selected</li> <li>00 = Quadrature Encoder Interface (x4 mode) Count mode is selected</li> </ul> |

| Note 1: | When CCM<1:0> = 10 or 11, all of the QEI counters operate as timers and the PIMOD<2:0> bits are ignored.                                                                                                                                                                                                                     |

- 2: When CCM<1:0> = 00, and QEA and QEB values match the Index Match Value (IMV), the POSCNTH and POSCNTL registers are reset. QEA/QEB signals used for the index match have swap and polarity values applied, as determined by the SWPAB and QEAPOL/QEBPOL bits.

- 3: The selected clock rate should be at least twice the expected maximum quadrature count rate.

#### 18.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\frac{1}{SSx}$ .

| Note: | This insures |                       | that  | the       | first | fr | ame |  |  |

|-------|--------------|-----------------------|-------|-----------|-------|----|-----|--|--|

|       | transr       | nission               | after | initializ | ation | is | not |  |  |

|       | shifte       | shifted or corrupted. |       |           |       |    |     |  |  |

- 2. In Non-Framed 3-Wire mode, (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = 0, always place a pull-down resistor on SSx.

- **Note:** This will insure that during power-up and initialization the master/slave will not lose Sync due to an errant SCKx transition that would cause the slave to accumulate data shift errors for both transmit and receive appearing as corrupted data.

- FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame Sync pulse is active on the SSx pin, which indicates the start of a data frame.

- Note: Not all third-party devices support Frame mode timing. Refer to the SPIx specifications in Section 30.0 "Electrical Characteristics" for details.

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPIx data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

To avoid invalid slave read data to the master, the user's master software must ensure enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF Transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPIx Shift register and is empty once the data transmission begins.

#### 18.2 SPI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 18.2.1 KEY RESOURCES

- "Serial Peripheral Interface (SPI)" (DS70569) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 21-17: CxRXFnEID: ECANx ACCEPTANCE FILTER n EXTENDED IDENTIFIER REGISTER (n = 0-15)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| EID15  | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-0 EID<15:0>: Extended Identifier bits

1 = Message address bit, EIDx, must be '1' to match filter

0 = Message address bit, EIDx, must be '0' to match filter

#### REGISTER 21-18: CxFMSKSEL1: ECANx FILTER 7-0 MASK SELECTION REGISTER 1

| R/W-0         | R/W-0       | R/W-0                                                       | R/W-0             | R/W-0                             | R/W-0            | R/W-0              | R/W-0  |

|---------------|-------------|-------------------------------------------------------------|-------------------|-----------------------------------|------------------|--------------------|--------|

| F7MSK<1:0>    |             | F6MSK<1:0>                                                  |                   | F5MSK<1:0>                        |                  | F4MS               | <<1:0> |

| bit 15        |             | ·                                                           |                   |                                   |                  |                    | bit    |

| R/W-0         | R/W-0       | R/W-0                                                       | R/W-0             | R/W-0                             | R/W-0            | R/W-0              | R/W-0  |

| F3MS          | SK<1:0>     | F2MS                                                        | <b>&lt;</b> <1:0> | F1MS                              | K<1:0>           | F0MS               | <<1:0> |

| bit 7         |             |                                                             |                   |                                   |                  |                    | bit (  |

| Legend:       |             |                                                             |                   |                                   |                  |                    |        |

| R = Readable  | e bit       | W = Writable                                                | bit               | U = Unimplen                      | nented bit, read | d as '0'           |        |

| -n = Value at | POR         | '1' = Bit is set                                            |                   | '0' = Bit is clea                 | ared             | x = Bit is unknown |        |

|               | 01 = Accept | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg | gisters contain   | mask                              |                  |                    |        |

| bit 13-12     | F6MSK<1:0   | >: Mask Source                                              | for Filter 6 bit  | s (same values                    | s as bits<15:14  | >)                 |        |

| bit 11-10     | F5MSK<1:0   | >: Mask Source                                              | for Filter 5 bit  | s (same values                    | s as bits<15:14  | >)                 |        |

| bit 9-8       | F4MSK<1:0   | >: Mask Source                                              | for Filter 4 bit  | bits (same values as bits<15:14>) |                  |                    |        |

| bit 7-6       | F3MSK<1:0   | >: Mask Source                                              | for Filter 3 bit  | s (same values                    | s as bits<15:14  | >)                 |        |

| bit 5-4       | F2MSK<1:0   | >: Mask Source                                              | for Filter 2 bit  | s (same values                    | s as bits<15:14  | >)                 |        |

| bit 3-2       | F1MSK<1:0   | >: Mask Source                                              | for Filter 1 bit  | s (same values                    | s as bits<15:14  | >)                 |        |

|               |             |                                                             |                   |                                   |                  |                    |        |

#### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 21-19: CxFMSKSEL2: ECANx FILTER 15-8 MASK SELECTION REGISTER 2

| R/W-0                                        | R/W-0                                                                                                                        | R/W-0                                                                                                                                            | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                   | R/W-0                        | R/W-0  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------|--------|

| F15N                                         | F15MSK<1:0>                                                                                                                  |                                                                                                                                                  | F14MSK<1:0>                                                                                                                                          |                                                                                                                           | F13MSK<1:0>                                                             |                              | K<1:0> |

| bit 15                                       |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              | bit 8  |

| R/W-0                                        | R/W-0                                                                                                                        | R/W-0                                                                                                                                            | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                   | R/W-0                        | R/W-0  |

|                                              | F11MSK<1:0> F10MSK<1:0                                                                                                       |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           | K<1:0>                                                                  |                              | <1:0>  |

| bit 7                                        |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              | bit C  |

|                                              |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |        |

| Legend:                                      |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |        |

| R = Readabl                                  | le bit                                                                                                                       | W = Writable                                                                                                                                     | bit                                                                                                                                                  | U = Unimplem                                                                                                              | nented bit, read                                                        | l as '0'                     |        |

| -n = Value at                                | t POR                                                                                                                        | '1' = Bit is set                                                                                                                                 |                                                                                                                                                      | '0' = Bit is clea                                                                                                         | ared                                                                    | x = Bit is unknown           |        |

|                                              |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |        |

|                                              |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |        |