#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuns                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

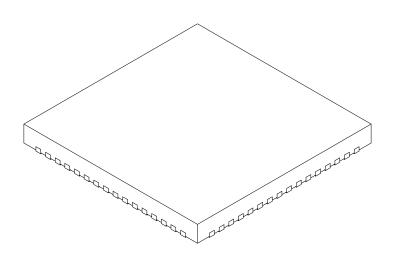

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 28-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128mc202t-e-ss |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

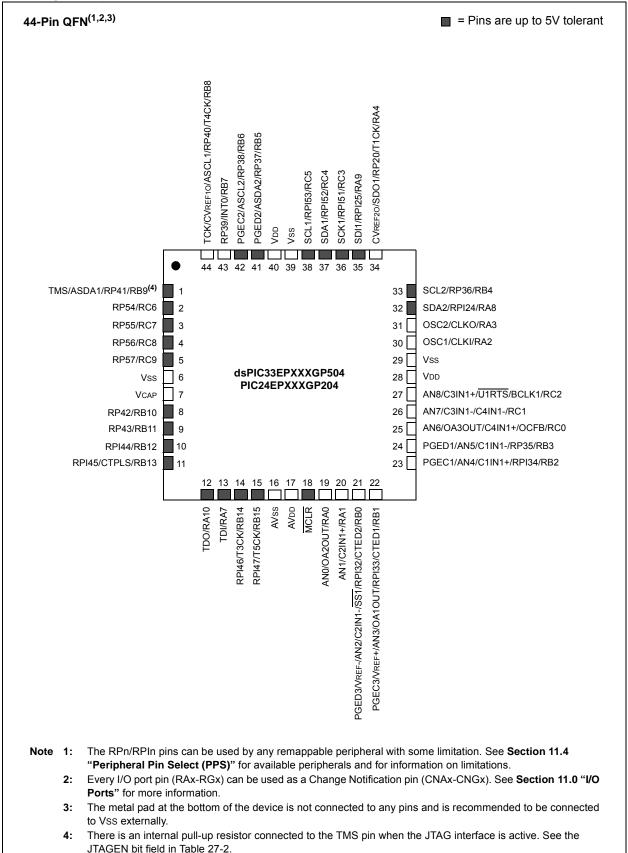

#### **Pin Diagrams (Continued)**

#### 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Program Memory" (DS70613) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture features separate program and data memory spaces, and buses. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

#### 4.1 Program Address Space

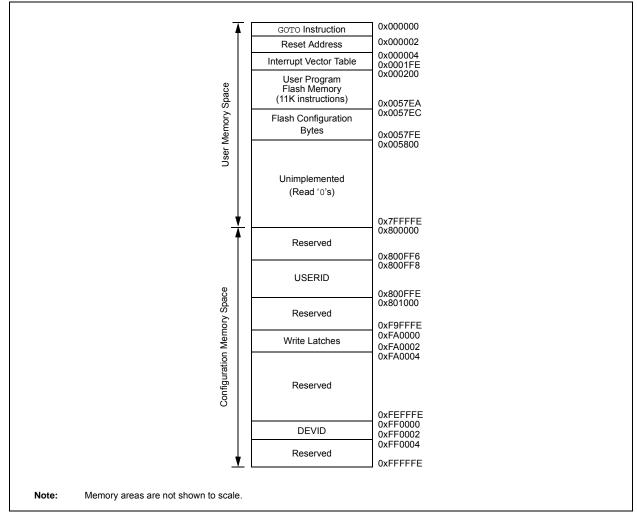

The program address memory space of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit PC during program execution, or from table operation or Data Space remapping, as described in Section 4.8 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFF). The exception is the use of TBLRD operations, which use TBLPAG<7> to read Device ID sections of the configuration memory space.

The program memory maps, which are presented by device family and memory size, are shown in Figure 4-1 through Figure 4-5.

# FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33EP32GP50X, dsPIC33EP32MC20X/50X AND PIC24EP32GP/MC20X DEVICES

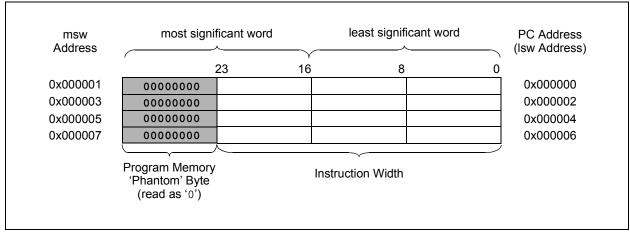

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-6).

Program memory addresses are always word-aligned on the lower word and addresses are incremented, or decremented by two, during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

#### 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices reserve the addresses between 0x000000 and 0x000200 for hardcoded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of Flash memory, with the actual address for the start of code at address, 0x000002, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in **Section 7.1** "Interrupt Vector Table".

#### FIGURE 4-6: PROGRAM MEMORY ORGANIZATION

#### 4.2.5 X AND Y DATA SPACES

# The dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X core has two Data Spaces, X and Y. These Data Spaces can be considered either separate (for some DSP instructions) or as one unified linear address range (for MCU instructions). The Data Spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X Data Space is used by all instructions and supports all addressing modes. X Data Space has separate read and write data buses. The X read data bus is the read data path for all instructions that view Data Space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y Data Space is used in concert with the X Data Space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y Data Spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X Data Space. Modulo Addressing and Bit-Reversed Addressing are not present in PIC24EPXXXGP/MC20X devices.

All data memory writes, including in DSP instructions, view Data Space as combined X and Y address space. The boundary between the X and Y Data Spaces is device-dependent and is not user-programmable.

#### 4.3 Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 4.3.1 KEY RESOURCES

- "Program Memory" (DS70613) in the "dsPIC33/ PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

| TABLE        | 4-2:  | CPU C  | CORE RE | EGISTER | R MAP F | FOR PIC | 24EPX) | XGP/M | C20X D   | EVICES   | ONLY   |       |           |          |       |       |       |               |

|--------------|-------|--------|---------|---------|---------|---------|--------|-------|----------|----------|--------|-------|-----------|----------|-------|-------|-------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8    | Bit 7    | Bit 6  | Bit 5 | Bit 4     | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| W0           | 0000  |        |         |         |         |         |        |       | W0 (WR   | EG)      |        |       |           |          |       |       |       | xxxx          |

| W1           | 0002  |        |         |         |         |         |        |       | W1       |          |        |       |           |          |       |       |       | xxxx          |

| W2           | 0004  |        |         |         |         |         |        |       | W2       |          |        |       |           |          |       |       |       | xxxx          |

| W3           | 0006  |        |         |         |         |         |        |       | W3       |          |        |       |           |          |       |       |       | xxxx          |

| W4           | 0008  |        |         |         |         |         |        |       | W4       |          |        |       |           |          |       |       |       | xxxx          |

| W5           | 000A  |        |         |         |         |         |        |       | W5       |          |        |       |           |          |       |       |       | xxxx          |

| W6           | 000C  |        |         |         |         |         |        |       | W6       |          |        |       |           |          |       |       |       | xxxx          |

| W7           | 000E  |        |         |         |         |         |        |       | W7       |          |        |       |           |          |       |       |       | xxxx          |

| W8           | 0010  |        |         |         |         |         |        |       | W8       |          |        |       |           |          |       |       |       | xxxx          |

| W9           | 0012  |        |         |         |         |         |        |       | W9       |          |        |       |           |          |       |       |       | xxxx          |

| W10          | 0014  |        |         |         |         |         |        |       | W10      |          |        |       |           |          |       |       |       | xxxx          |

| W11          | 0016  |        |         |         |         |         |        |       | W11      |          |        |       |           |          |       |       |       | xxxx          |

| W12          | 0018  |        |         |         |         |         |        |       | W12      |          |        |       |           |          |       |       |       | xxxx          |

| W13          | 001A  |        |         |         |         |         |        |       | W13      |          |        |       |           |          |       |       |       | xxxx          |

| W14          | 001C  |        |         |         |         |         |        |       | W14      |          |        |       |           |          |       |       |       | xxxx          |

| W15          | 001E  |        |         |         |         |         |        |       | W15      |          |        |       |           |          |       |       |       | xxxx          |

| SPLIM        | 0020  |        |         |         |         |         |        |       | SPLIM<1  | 5:0>     |        |       |           |          |       |       |       | 0000          |

| PCL          | 002E  |        |         |         |         |         |        | P     | CL<15:1> |          |        |       |           |          |       |       | —     | 0000          |

| PCH          | 0030  | —      | -       | _       | _       | —       | —      | —     | —        | _        |        |       |           | PCH<6:0> |       |       |       | 0000          |

| DSRPAG       | 0032  | —      | -       | _       | _       | —       | —      |       |          |          |        | DSRPA | G<9:0>    |          |       |       |       | 0001          |

| DSWPAG       | 0034  | _      |         |         |         | _       |        | _     |          |          |        | DS    | SWPAG<8:0 | >        |       |       |       | 0001          |

| RCOUNT       | 0036  |        |         |         |         |         |        |       | RCOUNT<  | 15:0>    |        |       |           |          |       |       |       | 0000          |

| SR           | 0042  | _      |         |         |         | _       |        | —     | DC       | IPL2     | IPL1   | IPL0  | RA        | N        | OV    | Z     | С     | 0000          |

| CORCON       | 0044  | VAR    | _       | -       | -       | —       |        | —     | _        | -        | _      | —     | -         | IPL3     | SFA   | —     | _     | 0020          |

| DISICNT      | 0052  | _      | _       |         |         |         |        |       |          | DISICNT< | :13:0> |       |           |          |       |       |       | 0000          |

| TBLPAG       | 0054  | _      | _       | -       | -       | —       |        | —     | _        |          |        |       | TBLPA     | G<7:0>   |       |       |       | 0000          |

| MSTRPR       | 0058  |        |         |         |         |         |        |       | MSTRPR<  | 15:0>    |        |       |           |          |       |       |       | 0000          |

#### **D** I -4.0 - -

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8 | Bit 7 | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|-------|-------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >     |       | —       | _           | _       | —       | _      | —           |        | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<    | 2:0>  |       | PT      | GSTEPIP<2   | :0>     | —       | —      | _           | -      | 4440          |

| IPC37        | 088A  | _      | —      | —          | _      | _      | F      | PTG3IP<2:0 | )>    |       |         | PTG2IP<2:0> | >       | _       |        | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     |        |        |        | _          | _     | _     | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     | _      | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      | _      |        |            | —     |       | _       | —           | —       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | —      | —          | _      | _      |        |            | —     |       | _       | DAE         | DOOVR   | _       | —      | —           |        | 0000          |

| INTCON4      | 08C6  | _      | _      | _          | _      | _      | -      | _          | —     | _     | _       | _           | _       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | Ι      | _      | _          | _      |        | ILR<   | 3:0>       |       |       |         |             | VECN    | UM<7:0> |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4         | -16:  | QEI1   | REGR               |          | P FOR d    | SPIC33E    | PXXXMO   | 20X/50)  | ( AND PI    | C24EP) |        | 20X DE     | VICES O  | NLY    | 1      |        |        | r             |

|-----------------|-------|--------|--------------------|----------|------------|------------|----------|----------|-------------|--------|--------|------------|----------|--------|--------|--------|--------|---------------|

| File Name       | Addr. | Bit 15 | Bit 14             | Bit 13   | Bit 12     | Bit 11     | Bit 10   | Bit 9    | Bit 8       | Bit 7  | Bit 6  | Bit 5      | Bit 4    | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| QEI1CON         | 01C0  | QEIEN  | —                  | QEISIDL  |            | PIMOD<2:0> |          | IMV      | <1:0>       | -      |        | INTDIV<2:0 | >        | CNTPOL | GATEN  | CCM    | <1:0>  | 0000          |

| QEI1IOC         | 01C2  | QCAPEN | FLTREN             |          | QFDIV<2:0> |            | OUTFN    | NC<1:0>  | SWPAB       | HOMPOL | IDXPOL | QEBPOL     | QEAPOL   | HOME   | INDEX  | QEB    | QEA    | 000x          |

| <b>QEI1STAT</b> | 01C4  | _      | _                  | PCHEQIRQ | PCHEQIEN   | PCLEQIRQ   | PCLEQIEN | POSOVIRQ | POSOVIEN    | PCIIRQ | PCIIEN | VELOVIRQ   | VELOVIEN | HOMIRQ | HOMIEN | IDXIRQ | IDXIEN | 0000          |

| POS1CNTL        | 01C6  |        |                    |          |            |            |          |          | POSCNT<15   | :0>    |        |            |          |        |        |        |        | 0000          |

| POS1CNTH        | 01C8  |        |                    |          |            |            |          | ł        | POSCNT<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| POS1HLD         | 01CA  |        |                    |          |            |            |          |          | POSHLD<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| VEL1CNT         | 01CC  |        |                    |          |            |            |          |          | VELCNT<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| INT1TMRL        | 01CE  |        |                    |          |            |            |          |          | INTTMR<15:  | 0>     |        |            |          |        |        |        |        | 0000          |

| INT1TMRH        | 01D0  |        |                    |          |            |            |          |          | INTTMR<31:  | 6>     |        |            |          |        |        |        |        | 0000          |

| INT1HLDL        | 01D2  |        |                    |          |            |            |          |          | INTHLD<15:  | )>     |        |            |          |        |        |        |        | 0000          |

| INT1HLDH        | 01D4  |        |                    |          |            |            |          |          | INTHLD<31:1 | 6>     |        |            |          |        |        |        |        | 0000          |

| INDX1CNTL       | 01D6  |        |                    |          |            |            |          |          | INDXCNT<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| INDX1CNTH       | 01D8  |        |                    |          |            |            |          |          | NDXCNT<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| INDX1HLD        | 01DA  |        |                    |          |            |            |          |          | INDXHLD<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| QEI1GECL        | 01DC  |        | QEIGEC<15:0> 00    |          |            |            |          |          |             | 0000   |        |            |          |        |        |        |        |               |

| <b>QEI1ICL</b>  | 01DC  |        | QEIIC<15:0> 00     |          |            |            |          |          |             | 0000   |        |            |          |        |        |        |        |               |

| QEI1GECH        | 01DE  |        | QEIGEC<31:16> 000  |          |            |            |          |          |             |        | 0000   |            |          |        |        |        |        |               |

| QEI1ICH         | 01DE  |        |                    |          |            |            |          |          |             |        | 0000   |            |          |        |        |        |        |               |

| QEI1LECL        | 01E0  |        |                    |          |            |            |          |          | QEILEC<15:  | )>     |        |            |          |        |        |        |        | 0000          |

| <b>QEI1LECH</b> | 01E2  |        | QEILEC<31:16> 0000 |          |            |            |          |          |             |        | 0000   |            |          |        |        |        |        |               |

TABLE 4-16: QEI1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-59: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | —      | _      | _      | _      | -      | _     | _     | _     | _     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 001F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | —      | _      | _      | _     | _     | _     | _     | _     | ANSA4  | _      | _      | ANSA1  | ANSA0  | 0013          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-60: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | _       | _      | ANSB8  | _      |        | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-0         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0                                                             | R/W-0           | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|--|

| ROON          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ROSSLP                                                            | ROSEL           | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |  |  |  |

| bit 15        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |                 |                       |                       | •                     | bit                   |  |  |  |

| U-0           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | U-0                                                               | U-0             | U-0                   | U-0                   | U-0                   | U-0                   |  |  |  |

|               | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                                                                 |                 | _                     |                       | _                     |                       |  |  |  |

| bit 7         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |                 |                       |                       |                       | bit                   |  |  |  |

| Legend:       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |                 |                       |                       |                       |                       |  |  |  |

| R = Readable  | e bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | W = Writable                                                      | bit             | U = Unimpler          | nented bit, read      | l as '0'              |                       |  |  |  |

| -n = Value at |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | '1' = Bit is set                                                  |                 | '0' = Bit is cle      |                       | x = Bit is unkr       | iown                  |  |  |  |

| bit 14        | 0 = Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | e oscillator outp<br>e oscillator outp<br>i <b>ted:</b> Read as ' | out is disabled |                       | .K pin <sup>(2)</sup> |                       |                       |  |  |  |

| bit 13        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ference Oscilla                                                   |                 | en hit                |                       |                       |                       |  |  |  |

|               | 1 = Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | e oscillator out<br>e oscillator out                              | out continues   | to run in Sleep       |                       |                       |                       |  |  |  |

| bit 12        | 1 = Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                                                                 | as the refere   | nce clock             |                       |                       |                       |  |  |  |

| bit 11-8      | 1 = Oscillator crystal is used as the reference clock 0 = System clock is used as the reference clock <b>RODIV&lt;3:0&gt;:</b> Reference Oscillator Divider bits <sup>(1)</sup> 1111 = Reference clock divided by 32,768 1100 = Reference clock divided by 16,384 1101 = Reference clock divided by 4,096 1011 = Reference clock divided by 2,048 1010 = Reference clock divided by 1,024 1001 = Reference clock divided by 256 0111 = Reference clock divided by 128 0110 = Reference clock divided by 4,096 1011 = Reference clock divided by 512 1000 = Reference clock divided by 256 0111 = Reference clock divided by 4,096 0111 = Reference clock divided by 256 0111 = Reference clock divided by 128 0110 = Reference clock divided by 4,096 0101 = Reference clock divided by 4,094 010 = Reference clock divided by 4,094 010 = Reference clock divided by 256 0111 = Reference clock divided by 128 0110 = Reference clock divided by 4,096 010 = Reference clock divided by 2 |                                                                   |                 |                       |                       |                       |                       |  |  |  |

|               | 0000 = Refer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ence clock                                                        | -               |                       |                       |                       |                       |  |  |  |

#### REGISTER 9-5: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

#### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP43  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

|        |     |       |       |       |        |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

| —      | —   |       |       | RP42  | R<5:0> |       |       |

#### REGISTER 11-22: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

|   | bit | 7 |

|---|-----|---|

| 1 |     |   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP43R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP43 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP42R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-23: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP55  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP54  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP55R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP55 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP54R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP54 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 0

#### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0        | R/W-0                               | R/W-0      | R/W-0                    | R/W-0            | R/W-0           | R/W-0 |  |

|-----------------|------------|-------------------------------------|------------|--------------------------|------------------|-----------------|-------|--|

| —               | —          |                                     |            | RP57                     | R<5:0>           |                 |       |  |

| bit 15          |            |                                     |            |                          |                  |                 | bit 8 |  |

|                 |            |                                     |            |                          |                  |                 |       |  |

| U-0             | U-0        | R/W-0                               | R/W-0      | R/W-0                    | R/W-0            | R/W-0           | R/W-0 |  |

| _               | —          |                                     | RP56R<5:0> |                          |                  |                 |       |  |

| bit 7           |            |                                     |            |                          |                  |                 | bit 0 |  |

|                 |            |                                     |            |                          |                  |                 |       |  |

| Legend:         |            |                                     |            |                          |                  |                 |       |  |

| R = Readable I  | bit        | W = Writable                        | bit        | U = Unimplen             | nented bit, read | d as '0'        |       |  |

| -n = Value at P | OR         | '1' = Bit is set                    | :          | '0' = Bit is clea        | ared             | x = Bit is unkr | iown  |  |

|                 |            |                                     |            |                          |                  |                 |       |  |

| bit 15-14       | Unimplemen | ted: Read as '                      | 0'         |                          |                  |                 |       |  |

| bit 13-8        |            | : Peripheral Ou<br>-3 for periphera |            | is Assigned to<br>mbers) | RP57 Output F    | Pin bits        |       |  |

| bit 7-6         | Unimplemen | nted: Read as '0'                   |            |                          |                  |                 |       |  |

#### REGISTER 11-24: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| (see Table 11-3 for peripheral function numbers) |

|--------------------------------------------------|

|                                                  |

#### REGISTER 11-25: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP97  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

RP56R<5:0>: Peripheral Output Function is Assigned to RP56 Output Pin bits

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   |     | —   | —   |     | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP97R<5:0>:** Peripheral Output Function is Assigned to RP97 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-0 Unimplemented: Read as '0'

bit 5-0

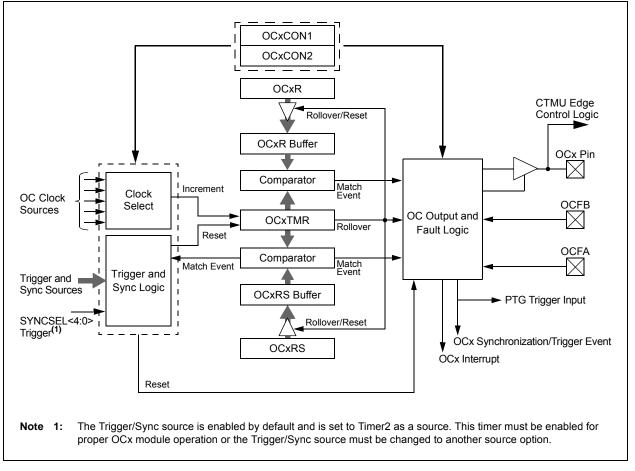

#### 15.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Output Compare" (DS70358) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The output compare module can select one of seven available clock sources for its time base. The module compares the value of the timer with the value of one or two compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the compare register value. The output compare module generates either a single output pulse or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events and trigger DMA data transfers.

Note: See "Output Compare" (DS70358) in the "dsPIC33/PIC24 Family Reference Manual" for OCxR and OCxRS register restrictions.

#### REGISTER 17-2: QEI1IOC: QEI1 I/O CONTROL REGISTER (CONTINUED)

- bit 2 INDEX: Status of INDXx Input Pin After Polarity Control

- 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

- bit 1 QEB: Status of QEBx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1' 0 = Pin is at logic '0'

- bit 0 **QEA:** Status of QEAx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

#### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 21-17: CxRXFnEID: ECANx ACCEPTANCE FILTER n EXTENDED IDENTIFIER REGISTER (n = 0-15)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| EID15  | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-0 EID<15:0>: Extended Identifier bits

1 = Message address bit, EIDx, must be '1' to match filter

0 = Message address bit, EIDx, must be '0' to match filter

#### REGISTER 21-18: CxFMSKSEL1: ECANx FILTER 7-0 MASK SELECTION REGISTER 1

| R/W-0         | R/W-0                                                                  | R/W-0                                                        | R/W-0            | R/W-0                                  | R/W-0            | R/W-0    | R/W-0  |  |

|---------------|------------------------------------------------------------------------|--------------------------------------------------------------|------------------|----------------------------------------|------------------|----------|--------|--|

| F7MS          | SK<1:0>                                                                | F6MS                                                         | K<1:0>           | <1:0> F5MSK<1:0> F4MSK<1:0>            |                  | K<1:0>   |        |  |

| bit 15        |                                                                        | ·                                                            |                  |                                        |                  |          | bit    |  |

| R/W-0         | R/W-0                                                                  | R/W-0                                                        | R/W-0            | R/W-0                                  | R/W-0            | R/W-0    | R/W-0  |  |

| F3MS          | SK<1:0>                                                                | F2MS                                                         | K<1:0>           | F1MS                                   | K<1:0>           | F0MS     | K<1:0> |  |

| bit 7         |                                                                        |                                                              |                  |                                        |                  |          | bit (  |  |

| Legend:       |                                                                        |                                                              |                  |                                        |                  |          |        |  |

| R = Readable  | e bit                                                                  | W = Writable                                                 | bit              | U = Unimplen                           | nented bit, read | d as '0' |        |  |

| -n = Value at | POR                                                                    | '1' = Bit is set                                             |                  | 0' = Bit is cleared x = Bit is unknown |                  |          |        |  |

|               | 01 = Accept                                                            | red<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg | gisters contain  | mask                                   |                  |          |        |  |

| bit 13-12     | F6MSK<1:0                                                              | >: Mask Source                                               | for Filter 6 bit | s (same values                         | s as bits<15:14  | >)       |        |  |

| bit 11-10     | F5MSK<1:0                                                              | >: Mask Source                                               | for Filter 5 bit | s (same values                         | s as bits<15:14  | >)       |        |  |

| bit 9-8       | F4MSK<1:0                                                              | >: Mask Source                                               | for Filter 4 bit | s (same values                         | s as bits<15:14  | >)       |        |  |

| bit 7-6       | F3MSK<1:0>: Mask Source for Filter 3 bits (same values as bits<15:14>) |                                                              |                  |                                        |                  |          |        |  |

| bit 5-4       | F2MSK<1:0                                                              | >: Mask Source                                               | for Filter 2 bit | s (same values                         | s as bits<15:14  | >)       |        |  |

| bit 3-2       | F1MSK<1:0>: Mask Source for Filter 1 bits (same values as bits<15:14>) |                                                              |                  |                                        |                  |          |        |  |

|               |                                                                        |                                                              |                  |                                        |                  | . )      |        |  |

NOTES:

#### 27.2 User ID Words

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices contain four User ID Words, located at addresses, 0x800FF8 through 0x800FFE. The User ID Words can be used for storing product information such as serial numbers, system manufacturing dates, manufacturing lot numbers and other application-specific information.

The User ID Words register map is shown in Table 27-3.

TABLE 27-3: USER ID WORDS REGISTER MAP

| File Name | Address  | Bits 23-16 | Bits 15-0 |

|-----------|----------|------------|-----------|

| FUID0     | 0x800FF8 | _          | UID0      |

| FUID1     | 0x800FFA | _          | UID1      |

| FUID2     | 0x800FFC | _          | UID2      |

| FUID3     | 0x800FFE | _          | UID3      |

**Legend:** — = unimplemented, read as '1'.

#### 27.3 On-Chip Voltage Regulator

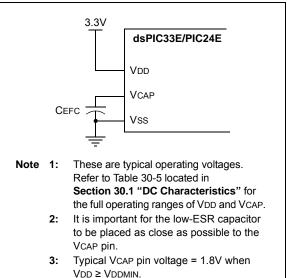

All of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X devices power their core digital logic at a nominal 1.8V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family incorporate an onchip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. A low-ESR (less than 1 Ohm) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 30-5 located in **Section 30.0 "Electrical Characteristics"**.

Note: It is important for the low-ESR capacitor to be placed as close as possible to the VCAP pin.

### FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE

REGULATOR<sup>(1,2,3)</sup>

#### 27.4 Brown-out Reset (BOR)

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated supply voltage, VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT Time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM is applied. The total delay in this case is TFSCM. Refer to Parameter SY35 in Table 30-22 of **Section 30.0 "Electrical Characteristics"** for specific TFSCM values.

The BOR status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

| Base<br>Instr<br># | Assembly<br>Mnemonic |                        | Assembly Syntax               | C Description                                              |   | # of<br>Cycles <sup>(2)</sup><br>1 | Status Flags<br>Affected<br>OA,OB,OAB,<br>SA,SB,SAB |

|--------------------|----------------------|------------------------|-------------------------------|------------------------------------------------------------|---|------------------------------------|-----------------------------------------------------|

| 53                 | NEG                  | NEG Acc <sup>(1)</sup> |                               | Negate Accumulator                                         | 1 |                                    |                                                     |

|                    |                      | NEG                    | f                             | $f = \overline{f} + 1$                                     | 1 | 1                                  | C,DC,N,OV,Z                                         |

|                    |                      | NEG                    | f,WREG                        | WREG = $\overline{f}$ + 1                                  | 1 | 1                                  | C,DC,N,OV,Z                                         |

|                    |                      | NEG                    | Ws,Wd                         | $Wd = \overline{Ws} + 1$                                   | 1 | 1                                  | C,DC,N,OV,Z                                         |

| 54                 | NOP                  | NOP                    |                               | No Operation                                               | 1 | 1                                  | None                                                |

|                    |                      | NOPR                   |                               | No Operation                                               | 1 | 1                                  | None                                                |

| 55                 | POP                  | POP                    | f                             | Pop f from Top-of-Stack (TOS)                              | 1 | 1                                  | None                                                |

|                    |                      | POP                    | Wdo                           | Pop from Top-of-Stack (TOS) to Wdo                         | 1 | 1                                  | None                                                |

|                    |                      | POP.D                  | Wnd                           | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1)          | 1 | 2                                  | None                                                |

|                    |                      | POP.S                  |                               | Pop Shadow Registers                                       | 1 | 1                                  | All                                                 |

| 56                 | PUSH                 | PUSH                   | f                             | Push f to Top-of-Stack (TOS)                               | 1 | 1                                  | None                                                |

|                    |                      | PUSH                   | Wso                           | Push Wso to Top-of-Stack (TOS)                             | 1 | 1                                  | None                                                |

|                    |                      | PUSH.D                 | Wns                           | Push W(ns):W(ns + 1) to Top-of-Stack<br>(TOS)              | 1 | 2                                  | None                                                |

|                    |                      | PUSH.S                 |                               | Push Shadow Registers                                      | 1 | 1                                  | None                                                |

| 57                 | PWRSAV               | PWRSAV                 | #lit1                         | Go into Sleep or Idle mode                                 | 1 | 1                                  | WDTO,Sleep                                          |

| 58                 | RCALL                | RCALL                  | Expr                          | Relative Call                                              | 1 | 4                                  | SFA                                                 |

|                    |                      | RCALL                  | Wn                            | Computed Call                                              | 1 | 4                                  | SFA                                                 |

| 59                 | REPEAT               | REPEAT                 | #lit15                        | Repeat Next Instruction lit15 + 1 times                    | 1 | 1                                  | None                                                |

|                    |                      | REPEAT                 | Wn                            | Repeat Next Instruction (Wn) + 1 times                     | 1 | 1                                  | None                                                |

| 60                 | RESET                | RESET                  |                               | Software device Reset                                      | 1 | 1                                  | None                                                |

| 61                 | RETFIE               | RETFIE                 |                               | Return from interrupt                                      | 1 | 6 (5)                              | SFA                                                 |

| 62                 | RETLW                | RETLW                  | #lit10,Wn                     | Return with literal in Wn                                  | 1 | 6 (5)                              | SFA                                                 |

| 63                 | RETURN               | RETURN                 |                               | Return from Subroutine                                     | 1 | 6 (5)                              | SFA                                                 |

| 64                 | RLC                  | RLC                    | f                             | f = Rotate Left through Carry f                            | 1 | 1                                  | C,N,Z                                               |

|                    |                      | RLC                    | f,WREG                        | WREG = Rotate Left through Carry f                         | 1 | 1                                  | C,N,Z                                               |

|                    |                      | RLC                    | Ws,Wd                         | Wd = Rotate Left through Carry Ws                          | 1 | 1                                  | C,N,Z                                               |

| 65                 | RLNC                 | RLNC                   | f                             | f = Rotate Left (No Carry) f                               | 1 | 1                                  | N,Z                                                 |

|                    |                      | RLNC                   | f,WREG                        | WREG = Rotate Left (No Carry) f                            | 1 | 1                                  | N,Z                                                 |

|                    |                      | RLNC                   | Ws,Wd                         | Wd = Rotate Left (No Carry) Ws                             | 1 | 1                                  | N,Z                                                 |

| 66                 | RRC                  | RRC                    | f                             | f = Rotate Right through Carry f                           | 1 | 1                                  | C,N,Z                                               |

|                    |                      | RRC                    | f,WREG                        | WREG = Rotate Right through Carry f                        | 1 | 1                                  | C,N,Z                                               |

|                    |                      | RRC                    | Ws,Wd                         | Wd = Rotate Right through Carry Ws                         | 1 | 1                                  | C,N,Z                                               |

| 67                 | RRNC                 | RRNC                   | f                             | f = Rotate Right (No Carry) f                              | 1 | 1                                  | N,Z                                                 |

|                    |                      | RRNC                   | f,WREG                        | WREG = Rotate Right (No Carry) f                           | 1 | 1                                  | N,Z                                                 |

| ~~                 |                      | RRNC                   | Ws,Wd                         | Wd = Rotate Right (No Carry) Ws                            | 1 | 1                                  | N,Z                                                 |

| 68                 | SAC                  | SAC                    | Acc,#Slit4,Wdo <sup>(1)</sup> | Store Accumulator                                          | 1 | 1                                  | None                                                |

| <u></u>            |                      | SAC.R                  | Acc,#Slit4,Wdo <sup>(1)</sup> | Store Rounded Accumulator                                  | 1 | 1                                  | None                                                |

| 69                 | SE                   | SE                     | Ws,Wnd                        | Wnd = sign-extended Ws                                     | 1 | 1                                  | C,N,Z                                               |

| 70                 | SETM                 | SETM                   | f                             | f = 0xFFFF                                                 | 1 | 1                                  | None                                                |

|                    |                      | SETM                   | WREG                          | WREG = 0xFFFF                                              | 1 | 1                                  | None                                                |

| 71                 | SFTAC                | SETM                   | Ws<br>Acc, Wn <sup>(1)</sup>  | Ws = 0xFFFF           Arithmetic Shift Accumulator by (Wn) | 1 | 1<br>1                             | None<br>OA,OB,OAB                                   |