Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128mc204-i-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

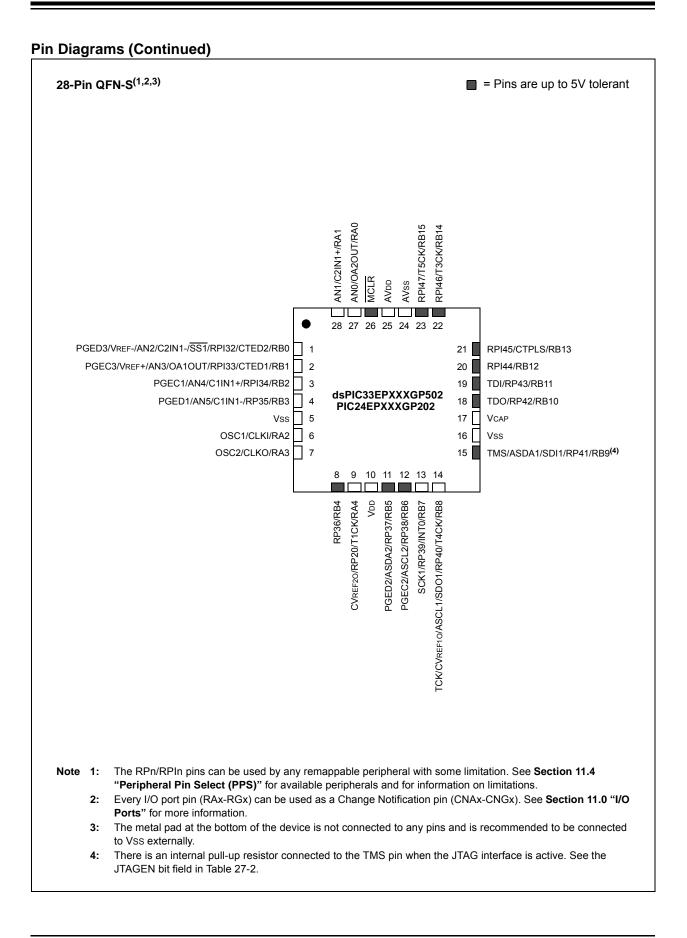

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

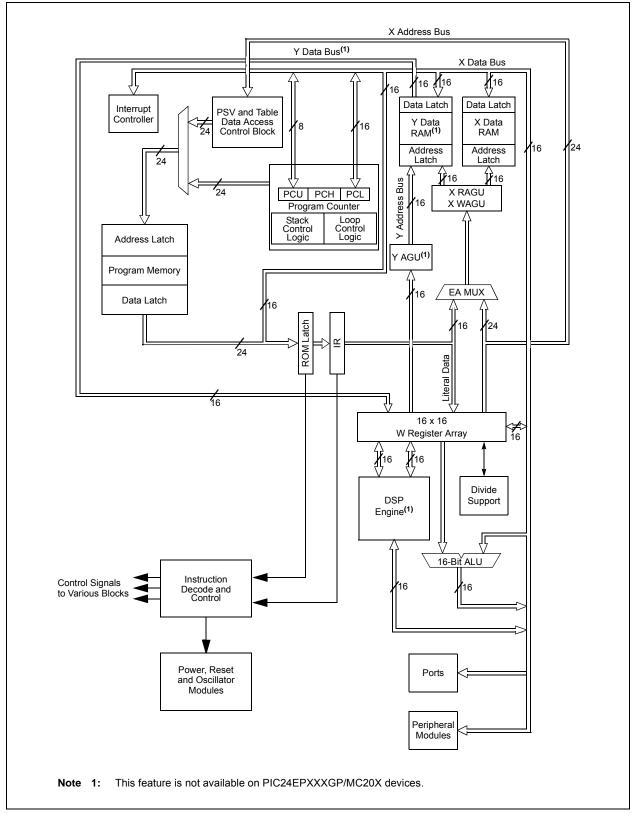

FIGURE 3-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X CPU BLOCK DIAGRAM

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0          | U-0          | U-0                                    | U-0           | U-0                | U-0              | U-0             | U-0    |

|--------------|--------------|----------------------------------------|---------------|--------------------|------------------|-----------------|--------|

| _            | —            | —                                      | —             | —                  | —                | —               | —      |

| bit 15       |              |                                        |               |                    |                  |                 | bit 8  |

|              |              |                                        |               |                    |                  |                 |        |

| U-0          | U-0          | U-0                                    | U-0           | R-0                | R-0              | R-0             | R-0    |

|              |              | <u> </u>                               | _             | PWCOL3             | PWCOL2           | PWCOL1          | PWCOL0 |

| bit 7        |              |                                        |               |                    |                  |                 | bit 0  |

|              |              |                                        |               |                    |                  |                 |        |

| Legend:      |              |                                        |               |                    |                  |                 |        |

| R = Readab   | le bit       | W = Writable                           | bit           | U = Unimpler       | mented bit, read | as '0'          |        |

| -n = Value a | t POR        | '1' = Bit is set                       |               | '0' = Bit is cle   | ared             | x = Bit is unkr | nown   |

|              |              |                                        |               |                    |                  |                 |        |

| bit 15-4     | Unimplemen   | ted: Read as '                         | 0'            |                    |                  |                 |        |

| bit 3        | PWCOL3: DI   | MA Channel 3 F                         | Peripheral Wi | rite Collision Fla | ag bit           |                 |        |

|              |              | lision is detecte                      |               |                    |                  |                 |        |

|              |              | collision is dete                      |               |                    |                  |                 |        |

| bit 2        |              |                                        | •             | rite Collision Fla | ag bit           |                 |        |

|              |              | lision is detecte<br>collision is dete |               |                    |                  |                 |        |

| bit 1        |              |                                        |               | rite Collision Fla | a hit            |                 |        |

| DILI         |              | lision is detecte                      | •             |                    |                  |                 |        |

|              |              | collision is dete                      |               |                    |                  |                 |        |

| bit 0        | PWCOL0: DI   | MA Channel 0 F                         | Peripheral Wi | rite Collision Fla | ag bit           |                 |        |

|              |              | lision is detecte                      | •             | -                  | <b>č</b>         |                 |        |

|              | 0 = No write | collision is dete                      | ected         |                    |                  |                 |        |

|              |              |                                        |               |                    |                  |                 |        |

## REGISTER 8-11: DMAPWC: DMA PERIPHERAL WRITE COLLISION STATUS REGISTER

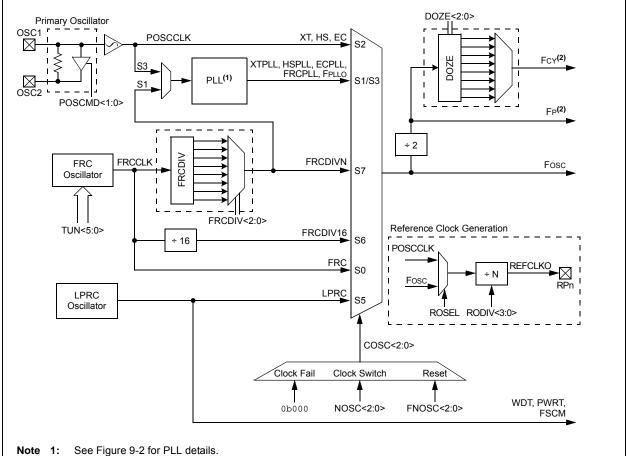

# 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator" (DS70580) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X oscillator system provides:

- On-chip Phase-Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources

- On-the-fly clock switching between various clock sources

- · Doze mode for system power savings

- Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Configuration bits for clock source selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

#### FIGURE 9-1: OSCILLATOR SYSTEM DIAGRAM

2: The term, FP, refers to the clock source for all peripherals, while FCY refers to the clock source for the CPU. Throughout this document, FCY and FP are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used with a doze ratio of 1:2 or lower.

#### 11.4.4 INPUT MAPPING

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-17). Each register contains sets of 7-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 7-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

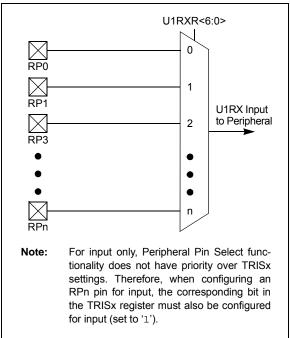

For example, Figure 11-2 illustrates remappable pin selection for the U1RX input.

#### FIGURE 11-2: REMAPPABLE INPUT FOR U1RX

#### 11.4.4.1 Virtual Connections

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices support virtual (internal) connections to the output of the op amp/ comparator module (see Figure 25-1 in Section 25.0 "Op Amp/Comparator Module"), and the PTG module (see Section 24.0 "Peripheral Trigger Generator (PTG) Module").

In addition, dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support virtual connections to the filtered QEI module inputs: FINDX1, FHOME1, FINDX2 and FHOME2 (see Figure 17-1 in Section 17.0 "Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)".

Virtual connections provide a simple way of interperipheral connection without utilizing a physical pin. For example, by setting the FLT1R<6:0> bits of the RPINR12 register to the value of `b0000001, the output of the analog comparator, C1OUT, will be connected to the PWM Fault 1 input, which allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

Virtual connection to the QEI module allows peripherals to be connected to the QEI digital filter input. To utilize this filter, the QEI module must be enabled and its inputs must be connected to a physical RPn pin. Example 11-2 illustrates how the input capture module can be connected to the QEI digital filter.

# EXAMPLE 11-2: CONNECTING IC1 TO THE HOME1 QEI1 DIGITAL FILTER INPUT ON PIN 43 OF THE dsPIC33EPXXXMC206 DEVICE

| RPINR15 = 0x2500; | /* Connect the QEI1 HOME1 input to RP37 (pin 43) */                   |

|-------------------|-----------------------------------------------------------------------|

| RPINR7 = 0x009;   | /* Connect the IC1 input to the digital filter on the FHOME1 input */ |

| QEI1IOC = 0x4000; | /* Enable the QEI digital filter */                                   |

| QEI1CON = 0x8000; | /* Enable the QEI module */                                           |

| U-0          | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|--------------|----------------------------------------------------------|---------------|-------------------|-----------------|-----------------|-------|

| —            |              |                                                          |               | IC4R<6:0>         |                 |                 |       |

| bit 15       |              |                                                          |               |                   |                 |                 | bit 8 |

|              |              |                                                          |               |                   |                 |                 |       |

| U-0          | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| —            |              |                                                          |               | IC3R<6:0>         |                 |                 |       |

| bit 7        |              |                                                          |               |                   |                 |                 | bit C |

|              |              |                                                          |               |                   |                 |                 |       |

| Legend:      |              |                                                          |               |                   |                 |                 |       |

| R = Readab   | ole bit      | W = Writable I                                           | bit           | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value a | at POR       | '1' = Bit is set                                         |               | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              | 0000001 =    | nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss | ⊃1            |                   |                 |                 |       |

| bit 7        | Unimpleme    | nted: Read as 'o                                         | )'            |                   |                 |                 |       |

| bit 6-0      | (see Table 1 | Assign Input Ca<br>1-2 for input pin<br>nput tied to RPI | selection nun |                   | onding RPn Pi   | n bits          |       |

### REGISTER 11-5: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

#### REGISTER 11-15: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0                | R/W-0                                      | R/W-0                                           | R/W-0                                      | R/W-0                              | R/W-0         | R/W-0              | R/W-0 |  |

|--------------------|--------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------|---------------|--------------------|-------|--|

|                    |                                            |                                                 |                                            | SYNCI1R<6:03                       | >             |                    |       |  |

| bit 15             |                                            |                                                 |                                            |                                    |               |                    | bit 8 |  |

|                    |                                            |                                                 |                                            |                                    |               |                    |       |  |

| U-0                | U-0                                        | U-0                                             | U-0                                        | U-0                                | U-0           | U-0                | U-0   |  |

| _                  |                                            |                                                 | —                                          |                                    |               | <u> </u>           | _     |  |

| bit 7              |                                            |                                                 |                                            |                                    |               |                    | bit 0 |  |

|                    |                                            |                                                 |                                            |                                    |               |                    |       |  |

| Legend:            |                                            |                                                 |                                            |                                    |               |                    |       |  |

| R = Readab         | ole bit                                    | W = Writable                                    | bit                                        | U = Unimplemented bit, read as '0' |               |                    |       |  |

| -n = Value a       | it POR                                     | '1' = Bit is set                                |                                            | '0' = Bit is cleared               |               | x = Bit is unknown |       |  |

|                    |                                            |                                                 |                                            |                                    |               |                    |       |  |

|                    |                                            |                                                 |                                            |                                    |               |                    |       |  |

| bit 15             | Unimplemer                                 | nted: Read as '                                 | 0'                                         |                                    |               |                    |       |  |

| bit 15<br>bit 14-8 | SYNCI1R<6:                                 |                                                 | M Synchroniz                               | zation Input 1 to<br>nbers)        | the Correspon | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11                | <b>0&gt;:</b> Assign PW                         | M Synchroniz selection nur                 |                                    | the Correspon | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                                    | the Correspon | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                                    | the Correspon | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11<br>1111001 = I | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz<br>selection nur<br>121<br>P1 |                                    | the Correspon | ding RPn Pin b     | its   |  |

| REGISTE       | R 16-7: PWMC                            | CONX: PWMX (                               | CONTROL R      | EGISTER          |                      |                      |                     |

|---------------|-----------------------------------------|--------------------------------------------|----------------|------------------|----------------------|----------------------|---------------------|

| HS/HC-        | 0 HS/HC-0                               | HS/HC-0                                    | R/W-0          | R/W-0            | R/W-0                | R/W-0                | R/W-0               |

| FLTSTAT       | -(1) CLSTAT <sup>(1)</sup>              | TRGSTAT                                    | FLTIEN         | CLIEN            | TRGIEN               | ITB <sup>(2)</sup>   | MDCS <sup>(2)</sup> |

| bit 15        | ·                                       | •                                          |                | ÷                |                      |                      | bit                 |

| R/W-0         | R/W-0                                   | R/W-0                                      | U-0            | R/W-0            | R/W-0                | R/W-0                | R/W-0               |

| DTC1          |                                         | DTCP <sup>(3)</sup>                        | 0-0            | MTBS             | CAM <sup>(2,4)</sup> | XPRES <sup>(5)</sup> | IUE <sup>(2)</sup>  |

| bit 7         | DICO                                    | DICE                                       | _              | INT DO           | CAIM                 | AFRES'               | bit                 |

|               |                                         |                                            |                |                  |                      |                      | <u> </u>            |

| Legend:       |                                         | HC = Hardware                              | Clearable bit  | HS = Hardwa      | are Settable bit     |                      |                     |

| R = Reada     | able bit                                | W = Writable bi                            | t              | U = Unimple      | mented bit, rea      | ıd as '0'            |                     |

| -n = Value    | at POR                                  | '1' = Bit is set                           |                | '0' = Bit is cle | eared                | x = Bit is unk       | nown                |

| bit 15        | ELTSTAT: ES                             | ult Interrupt Statu                        | is hit(1)      |                  |                      |                      |                     |

| DIL 15        |                                         | rrupt is pending                           |                |                  |                      |                      |                     |

|               |                                         | interrupt is pendi                         | ng             |                  |                      |                      |                     |

|               |                                         | ared by setting F                          |                |                  |                      |                      |                     |

| bit 14        |                                         | rent-Limit Interru                         | •              |                  |                      |                      |                     |

|               |                                         | mit interrupt is pe                        |                |                  |                      |                      |                     |

|               |                                         | nt-limit interrupt is<br>ared by setting C |                |                  |                      |                      |                     |

| bit 13        |                                         | igger Interrupt S                          |                |                  |                      |                      |                     |

|               |                                         | terrupt is pendin                          |                |                  |                      |                      |                     |

|               |                                         | r interrupt is pen                         |                |                  |                      |                      |                     |

|               |                                         | ared by setting T                          |                |                  |                      |                      |                     |

| bit 12        |                                         | t Interrupt Enable                         | e bit          |                  |                      |                      |                     |

|               |                                         | rrupt is enabled rrupt is disabled         | and the FLTS   | TAT bit is clear | ed                   |                      |                     |

| bit 11        |                                         | ent-Limit Interrup                         |                |                  | cu .                 |                      |                     |

|               |                                         | mit interrupt is er                        |                |                  |                      |                      |                     |

|               |                                         | mit interrupt is di                        |                | e CLSTAT bit is  | s cleared            |                      |                     |

| bit 10        | TRGIEN: Trig                            | ger Interrupt En                           | able bit       |                  |                      |                      |                     |

|               |                                         | event generates                            |                |                  | T hit is cleared     |                      |                     |

| bit 9         |                                         | vent interrupts ar<br>dent Time Base I     |                |                  | i bit is cleared     |                      |                     |

| DIL 9         |                                         | register provides                          |                | riad for this PM | VM generator         |                      |                     |

|               |                                         | egister provides f                         | •              |                  | •                    |                      |                     |

| bit 8         |                                         | er Duty Cycle Re                           |                |                  |                      |                      |                     |

|               |                                         | ister provides du<br>jister provides du    |                |                  |                      | r                    |                     |

| Note 1:       | Software must clea                      |                                            |                |                  | -                    |                      | t controller        |

| Note 1.<br>2: | These bits should                       | -                                          |                | -                | -                    | the interrup         |                     |

| 3:            | DTC<1:0> = 11 fo                        | -                                          |                | -                | -                    |                      |                     |

| 4:            | The Independent T<br>CAM bit is ignored | Time Base (ITB =                           |                | •                |                      | igned mode. If       | TTB = 0, the        |

| 5:            | To operate in Exter                     |                                            | t mode, the IT | B bit must be '  | 1' and the CLM       | 10D bit in the I     | FCLCONx             |

## REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER

5: To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

| U-0              | R/W-0                                                                                               | R/W-0                              | R/W-0           | R/W-0             | R/W-0                          | R/W-0                | R/W-0           |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------|------------------------------------|-----------------|-------------------|--------------------------------|----------------------|-----------------|--|--|--|

| _                | CLSRC4                                                                                              | CLSRC3                             | CLSRC2          | CLSRC1            | CLSRC0                         | CLPOL <sup>(2)</sup> | CLMOD           |  |  |  |

| bit 15           |                                                                                                     |                                    | •               |                   |                                |                      | bit 8           |  |  |  |

|                  | <b>D</b> 4 4                                                                                        | D 0.01 4                           | <b>D</b> 444    |                   | DAMA                           | DAMA                 | DAMO            |  |  |  |

| R/W-1            | R/W-1                                                                                               | R/W-1                              | R/W-1           | R/W-1             | R/W-0<br>FLTPOL <sup>(2)</sup> | R/W-0                | R/W-0           |  |  |  |

| FLTSRC4<br>bit 7 | FLTSRC3                                                                                             | FLTSRC2                            | FLTSRC1         | FLTSRC0           | FLIPOL-                        | FLTMOD1              | FLTMOD0<br>bit  |  |  |  |

|                  |                                                                                                     |                                    |                 |                   |                                |                      | DI              |  |  |  |

| Legend:          |                                                                                                     |                                    |                 |                   |                                |                      |                 |  |  |  |

| R = Readable     | bit                                                                                                 | W = Writable                       | bit             | U = Unimpler      | mented bit, read               | l as '0'             |                 |  |  |  |

| -n = Value at I  | POR                                                                                                 | '1' = Bit is set                   |                 | '0' = Bit is cle  | ared                           | x = Bit is unkr      | nown            |  |  |  |

|                  |                                                                                                     |                                    |                 |                   |                                |                      |                 |  |  |  |

| bit 15           | Unimplemen                                                                                          | ted: Read as '                     | 0'              |                   |                                |                      |                 |  |  |  |

| bit 14-10        | CLSRC<4:0>                                                                                          | Current-Limit                      | Control Signa   | al Source Seleo   | ct for PWM Ger                 | nerator # bits       |                 |  |  |  |

|                  | CLSRC<4:0>: Current-Limit Control Signal Source Select for PWM Generator # bits<br>11111 = Fault 32 |                                    |                 |                   |                                |                      |                 |  |  |  |

|                  | 11110 <b>= Res</b>                                                                                  | erved                              |                 |                   |                                |                      |                 |  |  |  |

|                  | •                                                                                                   |                                    |                 |                   |                                |                      |                 |  |  |  |

|                  | •                                                                                                   |                                    |                 |                   |                                |                      |                 |  |  |  |

|                  | 01100 = Res                                                                                         | erved                              |                 |                   |                                |                      |                 |  |  |  |

|                  | 01001 = Comparator 4                                                                                |                                    |                 |                   |                                |                      |                 |  |  |  |

|                  |                                                                                                     | Amp/Comparat                       | or 3            |                   |                                |                      |                 |  |  |  |

|                  | •                                                                                                   | Amp/Comparat                       |                 |                   |                                |                      |                 |  |  |  |

|                  |                                                                                                     | Amp/Comparat                       |                 |                   |                                |                      |                 |  |  |  |

|                  | 00111 = Res                                                                                         |                                    |                 |                   |                                |                      |                 |  |  |  |

|                  | 00110 <b>= Res</b>                                                                                  | erved                              |                 |                   |                                |                      |                 |  |  |  |

|                  | 00101 = Res                                                                                         | erved                              |                 |                   |                                |                      |                 |  |  |  |

|                  | 00100 <b>= Res</b>                                                                                  | erved                              |                 |                   |                                |                      |                 |  |  |  |

|                  | 00011 = Fault 4                                                                                     |                                    |                 |                   |                                |                      |                 |  |  |  |

|                  | 00010 = Fault 3                                                                                     |                                    |                 |                   |                                |                      |                 |  |  |  |

|                  | 00001 = Fault 2                                                                                     |                                    |                 |                   |                                |                      |                 |  |  |  |

|                  | 00000 <b>= Fau</b>                                                                                  | ( <i>)</i>                         |                 |                   | ~                              |                      |                 |  |  |  |

| bit 9            | CLPOL: Current-Limit Polarity for PWM Generator # bit <sup>(2)</sup>                                |                                    |                 |                   |                                |                      |                 |  |  |  |

|                  |                                                                                                     | cted current-lim                   |                 |                   |                                |                      |                 |  |  |  |

|                  | 0 = The selec                                                                                       | cted current-lim                   | it source is ac | tive-high         |                                |                      |                 |  |  |  |

| bit 8            | CLMOD: Cur                                                                                          | rent-Limit Mode                    | e Enable for P  | WM Generator      | r # bit                        |                      |                 |  |  |  |

|                  |                                                                                                     | imit mode is er<br>imit mode is di |                 |                   |                                |                      |                 |  |  |  |

|                  | ne PWMLOCK                                                                                          |                                    |                 | <6>) is a '1', th | e IOCONx regi                  | ster can only be     | e written aftei |  |  |  |

| the              | unlock sequen                                                                                       | ce has been ex                     | ecuted.         |                   |                                |                      |                 |  |  |  |

|                  |                                                                                                     |                                    |                 |                   |                                |                      |                 |  |  |  |

# REGISTER 16-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER<sup>(1)</sup>

2: These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

#### 17.2 QEI Control Registers

|  | REGISTER 17-1: | QEI1CON: QEI1 CONTROL REGISTER |

|--|----------------|--------------------------------|

|--|----------------|--------------------------------|

| U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         —       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |                                        |                       |                       |                     |                     |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------------|-----------------------|-----------------------|---------------------|---------------------|--|

| bit 15       bit 2         U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       -       intdividue       W= Writable bit       U = Unimplemented bit, read as '0'       bit 15       GEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to         bit 13       GEISDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD-2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       100 = Modulo Count mode for position counter         100 = Next index event after home event initializes position counter with contents of QEI1IC register       100 = Next index input event initializes position counter with contents of QEI1IC register       100 = Index input event dees not affect position coun                                                                                                                                                                                                  | R/W-0        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                  | R/W-0                                  | R/W-0                 | R/W-0                 | R/W-0               | R/W-0               |  |

| U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       bit 0       Dit 7       Dit 7       Dit 7       Dit 7       Dit 7         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       Dit 7         en value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN:       Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0         0 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to       Dit 13       QEISDL: QEI Stop in Idle Mode bit         1 = Discontinues module operation in Idle mode       0 = Continues module operation in Idle mode       Di Continues module operation on In Idle mode         Dit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         100 = Modulo Count mode for position counter       101 = Resets the position counter       101 = Resets the position counter with contents of QEI1IC register         101 = Resets the position counter when the position counter with contents of QEI1IC register       000 = Index input e                                                                                                                                                                                                                                          | QEIEN        | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | QEISIDL                | PIMOD2 <sup>(1)</sup>                  | PIMOD1 <sup>(1)</sup> | PIMOD0 <sup>(1)</sup> | IMV1 <sup>(2)</sup> | IMV0 <sup>(2)</sup> |  |

| -       INTDIV2 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       bit 7       bit 0         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       bit 0         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'       Bit is cleared       x = Bit is unknown         bit 13       QEISDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Modulo Count mode for position counter         10 = Resets the position counter when the position counter with contents of QEI1IC register       100 = Second index event after home event initializes position counter with contents of QEI1IC register         10 = Next index input event free home event initializes position counter with contents of QEI1IC register       00 = Index input event does not affect position counter         11 = Resets the position counter       110 = Next index input event me position counter       111 C register         10 = Next index input event me count instina                                                                                                                                                   | bit 15       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |                                        |                       |                       |                     | bit 8               |  |

| -       INTDIV2 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       bit 7       bit 0         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       bit 0         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'       Bit is cleared       x = Bit is unknown         bit 13       QEISDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Modulo Count mode for position counter         10 = Resets the position counter when the position counter with contents of QEI1IC register       100 = Second index event after home event initializes position counter with contents of QEI1IC register         10 = Next index input event free home event initializes position counter with contents of QEI1IC register       00 = Index input event does not affect position counter         11 = Resets the position counter       110 = Next index input event me position counter       111 C register         10 = Next index input event me count instina                                                                                                                                                   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |                                        |                       |                       |                     |                     |  |

| bit 7       bit 0         Legend:       W = Writable bit       U = Unimplemented bit, read as '0'         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Module counters are enabled         0 = Module counters are disabled, but SFRs can be read or written to       0 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'       0 = Continues module operation when device enters Idle mode         0 = Continues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD-2:0-: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Resets the position counter         101 = Resets the position counter when the position counter with contents of QEI1IC register         101 = Nexet input event after home event initializes position counter with contents of QEI1IC register         010 = Next index input event resets the position counter         011 = Every index input event resets the position counter         012 = Nease B match occurs when QEB = 1         0 = Phase B match occurs when QEB = 0         bit 8       IMV0: Index Match Value for Phase A bit <sup>(2)</sup> 1 = Phase A match occurs when QEA = 1 <t< td=""><td>U-0</td><td></td><td></td><td></td><td>R/W-0</td><td>R/W-0</td><td>R/W-0</td><td>R/W-0</td></t<>                                                                       | U-0          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |                                        | R/W-0                 | R/W-0                 | R/W-0               | R/W-0               |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0         0 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to       0         bit 14       Unimplemented: Read as '0'       0         bit 13       QEISIDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         11 = Reserved       111 = Reserved         110 = Modulo Count mode for position counter       101 = Resets the position counter when the position counter equals QEI1GEC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       100 = Second index event after home event initializes position counter with contents of QEI1IC register         101 = First index vent after home event initializes position counter with contents of QEI1IC register       001 = Every index input event resets the position counter         010 = Next index input event does not affect position counter       001 = Every index input event after home event initializes position counter with contents of QEI1IC register                                                                                                                                |              | INTDIV2 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | INTDIV1 <sup>(3)</sup> | INTDIV0 <sup>(3)</sup>                 | CNTPOL                | GATEN                 | CCM1                |                     |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is cleared       x = Bit is unknown         bit 15       QEISIDL: QEI Stop in Idle Mode bit       1 = Module counters are disabled, but SFRs can be read or written to       bit 14         Unimplemented: Read as '0'       East as '0'       East as '0'       East as '0'         bit 13       QEISIDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       10 = Second index event after home event initializes position counter with contents of QEI1IC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter         101 = Reserved       III = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes position counter with contents of QEI1IC register         102 = Mext index input event does not affect position counter       01 = Phase                                                                                              | bit 7        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |                                        |                       |                       |                     | bit 0               |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is cleared       x = Bit is unknown         bit 15       QEISIDL: QEI Stop in Idle Mode bit       1 = Module counters are disabled, but SFRs can be read or written to       bit 14         Unimplemented: Read as '0'       East as '0'       East as '0'       East as '0'         bit 13       QEISIDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       10 = Second index event after home event initializes position counter with contents of QEI1IC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter         101 = Reserved       III = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes position counter with contents of QEI1IC register         102 = Mext index input event does not affect position counter       01 = Phase                                                                                              | Logondy      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |                                        |                       |                       |                     |                     |  |

| n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is unknown         bit 14       Unimplemented: Read as '0'       0'       0'       Bit is cleared       0 = Continues module operation when device enters ldle mode       0 = Continues module operation in ldle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       10 = Second index event after home event initializes position counter with contents of QEI11C register         100 = Second index event after home event initializes position counter with contents of QEI11C register       10 = Next index input event resets the position counter with contents of QEI11C register         101 = Every index input event resets the position counter       00 = Index input event does not affect position counter         001 = Every index input event genst bit <sup>(2)</sup> 1 = Phase B match occurs when QEB = 1         011 = Phase B match occurs when QEB = 1       0 = Phase B match occurs when QEA = 1         015 = Phase A match occurs when QEA = 1       0 = Phase A match occurs when QEA = 1         015 = Phase A match occurs when QEA =                                                                                                  |              | lo hit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                        | hit                                    | II – Unimplor         | monted bit read       | ac '0'              |                     |  |

| bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit         1 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'         bit 13       QEISIDL: QEI Stop in Idle Mode bit         1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         11 = Discontinues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       100 = Second index event after home event initializes position counter with contents of QEI1IC register         011 = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event resets the position counter         001 = Nevery index input eve                                                                                                  |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |                                        | •                     |                       |                     |                     |  |

| <ul> <li>1 = Module counters are enabled</li> <li>0 = Module counters are disabled, but SFRs can be read or written to</li> <li>bit 14</li> <li>Unimplemented: Read as '0'</li> <li>bit 13</li> <li>QEISIDL: QEI Stop in Idle Mode bit</li> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> <li>0 = Continues module operation in Idle mode</li> <li>0 = Continues module operation counter Initialization Mode Select bits<sup>(1)</sup></li> <li>111 = Reserved</li> <li>110 = Modulo Count mode for position counter</li> <li>101 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event initializes the position counter with contents of QEI1IC register</li> <li>010 = Next index input event resets the position counter with contents of QEI1IC register</li> <li>011 = Every index input event resets the position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index Match Value for Phase B bit<sup>(2)</sup></li> <li>1 = Phase B match occurs when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>bit 8</li> <li>IMV0: Index Match Value for Phase A bit<sup>(2)</sup></li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> </ul> | -n = value a | PUR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | I = Bit is set         |                                        | 0 = Bit is cle        | ared                  | x = Bit is unkr     | IOWN                |  |

| bit 13       QEISDL: QEI Stop in Idle Mode bit         1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Modulo Count mode for position counter         100 = Modulo Count mode for position counter       101 = Resets the position counter when the position counter equals QEI1GEC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter with contents of QEI1IC register         011 = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter with contents of QEI1IC register         011 = Every index input event resets the position counter       001 = Every index input event for position counter         001 = Index input event does not affect position counter       000 = Index input event does not affect position counter         001 = Phase B match occurs when QEB = 1       0 = Phase B match occurs when QEB = 0         0it 8       IMV0: Index Match Value for Phase A bit <sup>(2)</sup> 1 = Phase A match occurs when QEA = 1       0 = Phase A match occurs when QEA = 0         0it 7       Unimplemented: Read as '0'                                                                                                                                                                                   | bit 15       | 1 = Module co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ounters are ena        | abled                                  |                       |                       |                     |                     |  |

| <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> <li>bit 12-10</li> <li>PIMOD&lt;2:0&gt;: Position Counter Initialization Mode Select bits<sup>(1)</sup></li> <li>111 = Reserved</li> <li>10 = Modulo Count mode for position counter</li> <li>10 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event resets the position counter with contents of QEI1IC register</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event operation when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>bit 8</li> <li>IMV0: Index Match Value for Phase A bit<sup>(2)</sup></li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                  | bit 14       | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ted: Read as '         | 0'                                     |                       |                       |                     |                     |  |

| <ul> <li>0 = Continues module operation in Idle mode</li> <li>bit 12-10</li> <li>PIMOD&lt;2:0&gt;: Position Counter Initialization Mode Select bits<sup>(1)</sup></li> <li>111 = Reserved</li> <li>10 = Modulo Count mode for position counter</li> <li>101 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event resets the position counter with contents of QEI1IC register</li> <li>001 = Every index input event resets the position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event QEB = 1</li> <li>0 = Phase B match occurs when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>bit 8</li> <li>IMV0: Index Match Value for Phase A bit<sup>(2)</sup></li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> </ul>                                                                                                                                                                                                                                                                                              | bit 13       | QEISIDL: QE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I Stop in Idle M       | lode bit                               |                       |                       |                     |                     |  |