Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

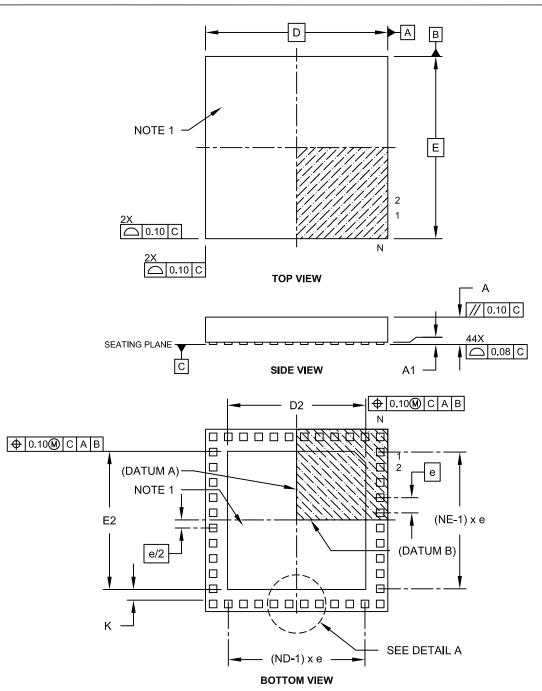

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 48-UFQFN Exposed Pad                                                           |

| Supplier Device Package    | 48-UQFN (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128mc204-i-mv |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.8 Arithmetic Logic Unit (ALU)

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X ALU is 16 bits wide, and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the <u>SR register. The C and DC</u> Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The core CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.8.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier, the ALU supports unsigned, signed, or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit signed x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

### 3.8.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

## 3.9 DSP Engine (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a 40-bit barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The DSP engine can also perform inherent accumulatorto-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or integer DSP multiply (IF)

- · Signed, unsigned or mixed-sign DSP multiply (US)

- · Conventional or convergent rounding (RND)

- · Automatic saturation on/off for ACCA (SATA)

- Automatic saturation on/off for ACCB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACCSAT)

|             | SUMMARY                 |                   |

|-------------|-------------------------|-------------------|

| Instruction | Algebraic<br>Operation  | ACC Write<br>Back |

| CLR         | A = 0                   | Yes               |

| ED          | $A = (x - y)^2$         | No                |

| EDAC        | $A = A + (x - y)^2$     | No                |

| MAC         | $A = A + (x \bullet y)$ | Yes               |

| MAC         | $A = A + x^2$           | No                |

| MOVSAC      | No change in A          | Yes               |

| MPY         | $A = x \bullet y$       | No                |

| MPY         | $A = x^2$               | No                |

| MPY.N       | $A = -x \bullet y$      | No                |

| MSC         | $A = A - x \bullet y$   | Yes               |

TABLE 3-2: DSP INSTRUCTIONS SUMMARY

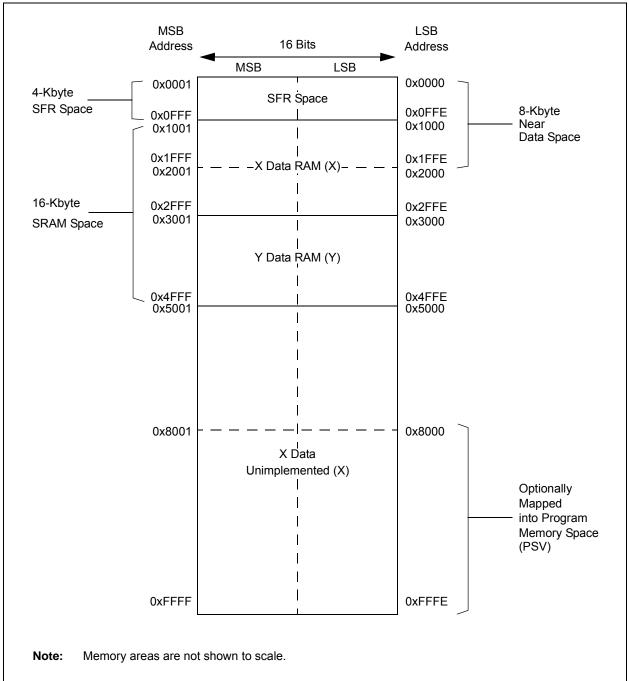

# FIGURE 4-9: DATA MEMORY MAP FOR dsPIC33EP128MC20X/50X AND dsPIC33EP128GP50X DEVICES

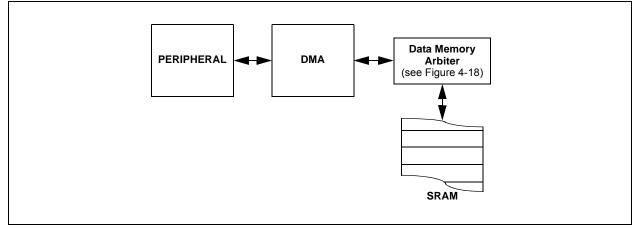

# 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM

In addition, DMA can access the entire data memory space. The Data Memory Bus Arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. Some of the peripherals supported by the DMA Controller include:

- ECAN<sup>™</sup>

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

## FIGURE 8-1: DMA CONTROLLER MODULE

## 9.1 CPU Clocking System

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices provides six system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase Locked Loop (PLL)

- · FRC Oscillator with Postscaler

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- · Low-Power RC (LPRC) Oscillator

Instruction execution speed or device operating frequency, FCY, is given by Equation 9-1.

# EQUATION 9-1: DEVICE OPERATING FREQUENCY

FCY = Fosc/2

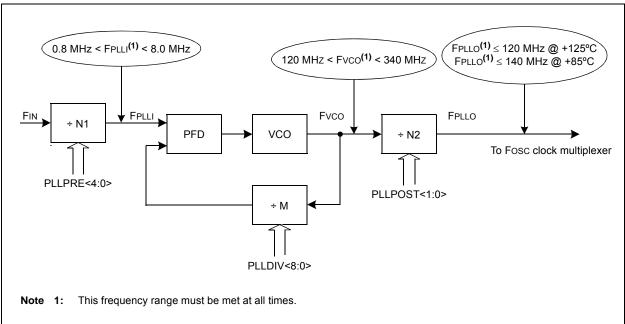

Figure 9-2 is a block diagram of the PLL module.

Equation 9-2 provides the relationship between input frequency (FIN) and output frequency (FPLLO). In clock modes S1 and S3, when the PLL output is selected, FOSC = FPLLO.

Equation 9-3 provides the relationship between input frequency (FIN) and VCO frequency (FVCO).

#### EQUATION 9-2: FPLLO CALCULATION

$$FPLLO = FIN \times \left(\frac{M}{N1 \times N2}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2) \times 2(PLLPOST + 1)}\right)$$

Where:

N1 = PLLPRE + 2 $N2 = 2 \times (PLLPOST + 1)$

M = PLLDIV + 2

### EQUATION 9-3: Fvco CALCULATION

$$Fvco = FIN \times \left(\frac{M}{N1}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2)}\right)$$

DS70000657H-page 154

#### © 2011-2013 Microchip Technology Inc.

# FIGURE 9-2: PLL BLOCK DIAGRAM

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0     | U-0 | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   |

|---------|-----|-------|-------|-------|-------|-------|-------|

| —       | —   | —     | —     | —     | —     | —     | —     |

| bit 15  |     |       |       |       |       |       | bit 8 |

|         |     |       |       |       |       |       |       |

| U-0     | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —       | —   | TUN5  | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7   |     |       |       |       |       |       | bit 0 |

|         |     |       |       |       |       |       |       |

| Logondi |     |       |       |       |       |       |       |

#### REGISTER 9-4: OSCTUN: FRC OSCILLATOR TUNING REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **TUN<5:0>:** FRC Oscillator Tuning bits 011111 = Maximum frequency deviation of 1.453% (7.477 MHz) 011110 = Center frequency + 1.406% (7.474 MHz) •••• 000001 = Center frequency + 0.047% (7.373 MHz) 000000 = Center frequency (7.37 MHz nominal) 111111 = Center frequency - 0.047% (7.367 MHz) ••• 100001 = Center frequency - 1.453% (7.263 MHz) 100000 = Minimum frequency deviation of -1.5% (7.259 MHz)

## **10.0 POWER-SAVING FEATURES**

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of peripherals being clocked constitutes lower consumed power.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices can manage power consumption in four ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- Software-Controlled Doze mode

- · Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

| PWRSAV | #SLEEP_MODE | ; | Put | the | device | into | Sleep mode |  |

|--------|-------------|---|-----|-----|--------|------|------------|--|

| PWRSAV | #IDLE_MODE  | ; | Put | the | device | into | Idle mode  |  |

## 10.1 Clock Frequency and Clock Switching

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or highprecision oscillators by simply changing the NOSCx bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0 "Oscillator Configuration"**.

## 10.2 Instruction-Based Power-Saving Modes

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 10-1.

**Note:** SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

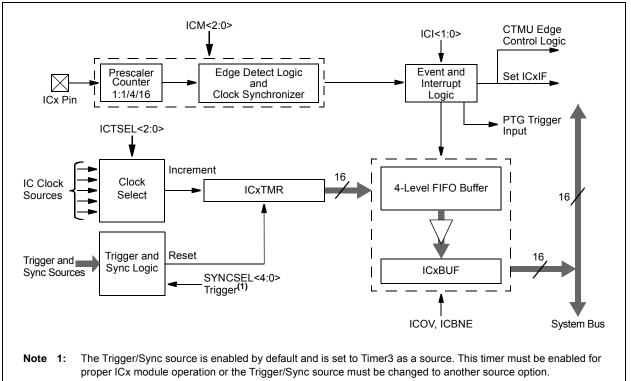

# 14.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70352) in the "dsPIC33/dsPIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices support four input capture channels.

Key features of the input capture module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 19 user-selectable Trigger/Sync sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- Configurable interrupt generation

- Up to six clock sources available for each module, driving a separate internal 16-bit counter

| U-0                 | U-0                                                                                                                                                                                                                                              | U-0                                                                                                    | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |  |  |  |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------|----------------------|----------------------|----------------------|--|--|--|--|

|                     | —                                                                                                                                                                                                                                                | _                                                                                                      | DISSCK                                | DISSDO               | MODE16               | SMP                  | CKE <sup>(1)</sup>   |  |  |  |  |

| bit 15              |                                                                                                                                                                                                                                                  | •                                                                                                      |                                       | •                    | •                    | •                    | bit                  |  |  |  |  |

| R/W-0               | R/W-0                                                                                                                                                                                                                                            | R/W-0                                                                                                  | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |  |  |  |  |

| SSEN <sup>(2)</sup> | CKP                                                                                                                                                                                                                                              | MSTEN                                                                                                  | SPRE2 <sup>(3)</sup>                  | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |  |  |  |  |

| bit 7               | CKF                                                                                                                                                                                                                                              | WIGTEN                                                                                                 | SFREZ 7                               | SFREI?               | SFREU 7              | FFREN                | bit                  |  |  |  |  |

|                     |                                                                                                                                                                                                                                                  |                                                                                                        |                                       |                      |                      |                      |                      |  |  |  |  |

| Legend:             |                                                                                                                                                                                                                                                  |                                                                                                        |                                       |                      |                      |                      |                      |  |  |  |  |

| R = Readabl         | le bit                                                                                                                                                                                                                                           | W = Writable                                                                                           | bit                                   | U = Unimpler         | mented bit, read     | d as '0'             |                      |  |  |  |  |

| -n = Value at       | t POR                                                                                                                                                                                                                                            | '1' = Bit is se                                                                                        | t                                     | '0' = Bit is cle     | ared                 | x = Bit is unkr      | nown                 |  |  |  |  |

|                     |                                                                                                                                                                                                                                                  |                                                                                                        |                                       |                      |                      |                      |                      |  |  |  |  |

| bit 15-13           | Unimplemen                                                                                                                                                                                                                                       | ted: Read as                                                                                           | 0'                                    |                      |                      |                      |                      |  |  |  |  |

| bit 12              |                                                                                                                                                                                                                                                  |                                                                                                        | bit (SPIx Mas                         | -                    | ()                   |                      |                      |  |  |  |  |

|                     |                                                                                                                                                                                                                                                  | 1 = Internal SPIx clock is disabled, pin functions as I/O<br>0 = Internal SPIx clock is enabled        |                                       |                      |                      |                      |                      |  |  |  |  |

| oit 11              |                                                                                                                                                                                                                                                  |                                                                                                        |                                       |                      |                      |                      |                      |  |  |  |  |

|                     |                                                                                                                                                                                                                                                  | <b>DISSDO:</b> Disable SDOx Pin bit<br>1 = SDOx pin is not used by the module; pin functions as I/O    |                                       |                      |                      |                      |                      |  |  |  |  |

|                     | 0 = SDOx pin is not used by the module                                                                                                                                                                                                           |                                                                                                        |                                       |                      |                      |                      |                      |  |  |  |  |

| bit 10              | MODE16: Wo                                                                                                                                                                                                                                       | MODE16: Word/Byte Communication Select bit                                                             |                                       |                      |                      |                      |                      |  |  |  |  |

|                     | 1 = Communication is word-wide (16 bits)                                                                                                                                                                                                         |                                                                                                        |                                       |                      |                      |                      |                      |  |  |  |  |

|                     | 0 = Communication is byte-wide (8 bits)                                                                                                                                                                                                          |                                                                                                        |                                       |                      |                      |                      |                      |  |  |  |  |

| bit 9               |                                                                                                                                                                                                                                                  | ata Input Sam                                                                                          | ole Phase bit                         |                      |                      |                      |                      |  |  |  |  |

|                     | Master mode                                                                                                                                                                                                                                      | -                                                                                                      | end of data o                         | utout time           |                      |                      |                      |  |  |  |  |

|                     |                                                                                                                                                                                                                                                  |                                                                                                        | middle of data                        |                      |                      |                      |                      |  |  |  |  |

|                     | Slave mode:                                                                                                                                                                                                                                      |                                                                                                        |                                       |                      |                      |                      |                      |  |  |  |  |

|                     |                                                                                                                                                                                                                                                  |                                                                                                        | SPIx is used i                        | n Slave mode.        |                      |                      |                      |  |  |  |  |

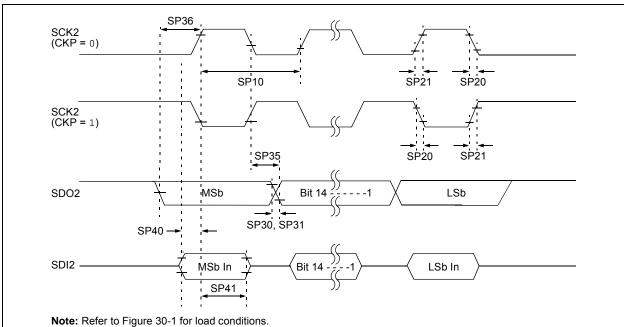

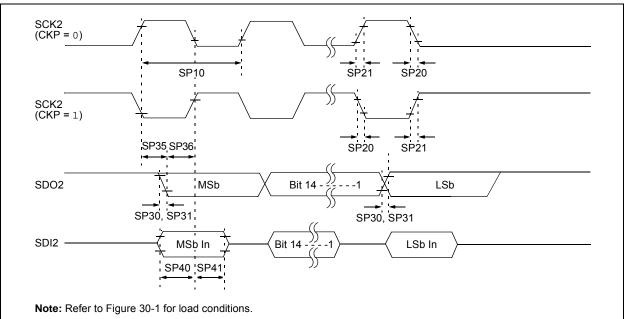

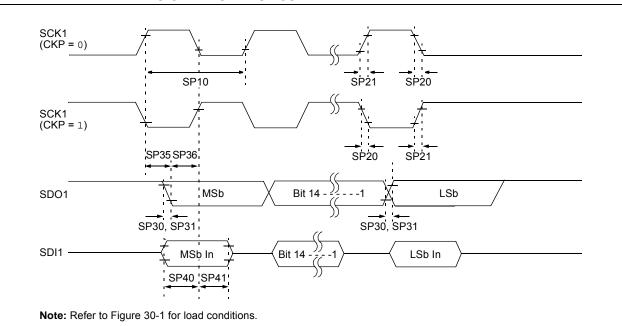

| bit 8               |                                                                                                                                                                                                                                                  | lock Edge Sele                                                                                         |                                       |                      |                      |                      |                      |  |  |  |  |

|                     | <ul> <li>1 = Serial output data changes on transition from active clock state to Idle clock state (refer to bit 6)</li> <li>0 = Serial output data changes on transition from Idle clock state to active clock state (refer to bit 6)</li> </ul> |                                                                                                        |                                       |                      |                      |                      |                      |  |  |  |  |

| bit 7               |                                                                                                                                                                                                                                                  |                                                                                                        |                                       |                      |                      | ve clock state (I    |                      |  |  |  |  |

|                     |                                                                                                                                                                                                                                                  | <b>SSEN:</b> Slave Select Enable bit (Slave mode) <sup>(2)</sup><br>1 = SSx pin is used for Slave mode |                                       |                      |                      |                      |                      |  |  |  |  |

|                     | 0 = SSx pin is used for Slave mode<br>0 = SSx pin is not used by the module; pin is controlled by port function                                                                                                                                  |                                                                                                        |                                       |                      |                      |                      |                      |  |  |  |  |

| bit 6               | CKP: Clock F                                                                                                                                                                                                                                     | Polarity Select                                                                                        | bit                                   |                      |                      |                      |                      |  |  |  |  |

|                     |                                                                                                                                                                                                                                                  |                                                                                                        | nigh level; activ<br>ow level; active |                      |                      |                      |                      |  |  |  |  |

| bit 5               | MSTEN: Mas                                                                                                                                                                                                                                       | ter Mode Enat                                                                                          | ole bit                               |                      |                      |                      |                      |  |  |  |  |

|                     | 1 = Master m<br>0 = Slave mo                                                                                                                                                                                                                     |                                                                                                        |                                       |                      |                      |                      |                      |  |  |  |  |

| Note 1: T           | he CKE bit is not                                                                                                                                                                                                                                | used in Frame                                                                                          | d SPI modes. I                        | Program this bi      | it to '0' for Fram   | ed SPI modes (       | FRMEN = 1            |  |  |  |  |

|                     | his bit must be cl                                                                                                                                                                                                                               |                                                                                                        |                                       |                      |                      |                      |                      |  |  |  |  |

| <b>0</b>            |                                                                                                                                                                                                                                                  |                                                                                                        |                                       |                      |                      |                      |                      |  |  |  |  |

## REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1

- **3:** Do not set both primary and secondary prescalers to the value of 1:1.

| R/W-0         | R/W-0                               | R/W-0                                  | U-0          | U-0              | U-0             | U-0               | U-0    |  |  |  |

|---------------|-------------------------------------|----------------------------------------|--------------|------------------|-----------------|-------------------|--------|--|--|--|

| FRMEN         | SPIFSD                              | FRMPOL                                 | —            | —                | _               | —                 | _      |  |  |  |

| bit 15        |                                     |                                        |              |                  |                 |                   | bit 8  |  |  |  |

|               |                                     |                                        |              |                  |                 |                   |        |  |  |  |

| U-0           | U-0                                 | U-0                                    | U-0          | U-0              | U-0             | R/W-0             | R/W-0  |  |  |  |

| _             | <u> </u>                            | —                                      | _            |                  | _               | FRMDLY            | SPIBEN |  |  |  |

| bit 7         |                                     |                                        |              |                  |                 |                   | bit 0  |  |  |  |

|               |                                     |                                        |              |                  |                 |                   |        |  |  |  |

| Legend:       |                                     |                                        |              |                  |                 |                   |        |  |  |  |

| R = Readable  | e bit                               | W = Writable b                         | pit          | U = Unimpler     | nented bit, rea | ad as '0'         |        |  |  |  |

| -n = Value at | POR                                 | '1' = Bit is set                       |              | '0' = Bit is cle | ared            | x = Bit is unkr   | ıknown |  |  |  |

|               |                                     |                                        |              |                  |                 |                   |        |  |  |  |

| bit 15        | FRMEN: Fra                          | RMEN: Framed SPIx Support bit          |              |                  |                 |                   |        |  |  |  |

|               |                                     | SPIx support is e<br>SPIx support is d |              | x pin is used as | Frame Sync      | oulse input/outpu | it)    |  |  |  |

| bit 14        | SPIFSD: Fra                         | me Sync Pulse [                        | Direction Co | ontrol bit       |                 |                   |        |  |  |  |

|               |                                     | ync pulse input (<br>ync pulse output  |              |                  |                 |                   |        |  |  |  |

| bit 13        | FRMPOL: Fr                          | ame Sync Pulse                         | Polarity bit | t                |                 |                   |        |  |  |  |

|               | 1 = Frame Sync pulse is active-high |                                        |              |                  |                 |                   |        |  |  |  |

|               |                                     | ync pulse is activ                     |              |                  |                 |                   |        |  |  |  |

| bit 12-2      | -                                   | nted: Read as '0                       |              |                  |                 |                   |        |  |  |  |

| bit 1         |                                     | ame Sync Pulse                         | -            |                  |                 |                   |        |  |  |  |

|               |                                     | ync pulse coincio<br>ync pulse preceo  |              |                  |                 |                   |        |  |  |  |

| bit 0         | SPIBEN: En                          | hanced Buffer Er                       | nable bit    |                  |                 |                   |        |  |  |  |

|               |                                     | d buffer is enable                     |              |                  |                 |                   |        |  |  |  |

|               | 0 = Enhance                         | d buffer is disabl                     | ed (Standa   | rd mode)         |                 |                   |        |  |  |  |

|               |                                     |                                        |              |                  |                 |                   |        |  |  |  |

#### REGISTER 18-3: SPIXCON2: SPIX CONTROL REGISTER 2

|                                                                                                                                                                                                       | 1                                                                                                                                                                                             | 0-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMABS1                                                                                                                                                                                                | DMABS0                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                       |                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                       |                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DAMO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0-0                                                                                                                                                                                                   | 0-0                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |