Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VFTLA Exposed Pad                                                           |

| Supplier Device Package    | 44-VTLA (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128mc204-i-tl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33EP64MC506 product page of the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

> In addition to parameters, features and other documentation, the resulting page provides links to the related family reference manual sections.

- "Introduction" (DS70573)

- "CPU" (DS70359)

- "Data Memory" (DS70595)

- "Program Memory" (DS70613)

- "Flash Programming" (DS70609)

- "Interrupts" (DS70600)

- "Oscillator" (DS70580)

- "Reset" (DS70602)

- "Watchdog Timer and Power-Saving Modes" (DS70615)

- "I/O Ports" (DS70598)

- "Timers" (DS70362)

- "Input Capture" (DS70352)

- "Output Compare" (DS70358)

- "High-Speed PWM" (DS70645)

- "Quadrature Encoder Interface (QEI)" (DS70601)

- "Analog-to-Digital Converter (ADC)" (DS70621)

- "UART" (DS70582)

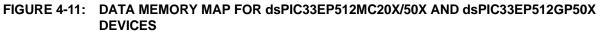

- "Serial Peripheral Interface (SPI)" (DS70569)

- "Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)" (DS70330)

- "Enhanced Controller Area Network (ECAN™)" (DS70353)

- "Direct Memory Access (DMA)" (DS70348)

- "CodeGuard™ Security" (DS70634)

- "Programming and Diagnostics" (DS70608)

- "Op Amp/Comparator" (DS70357)

- "Programmable Cyclic Redundancy Check (CRC)" (DS70346)

- "Device Configuration" (DS70618)

- "Peripheral Trigger Generator (PTG)" (DS70669)

- "Charge Time Measurement Unit (CTMU)" (DS70661)

#### 3.7 CPU Control Registers

| REGISTER               | 3-1: SR: CI                                          | PU STATUS I                            | REGISTER                    |                          |                    |                   |               |

|------------------------|------------------------------------------------------|----------------------------------------|-----------------------------|--------------------------|--------------------|-------------------|---------------|

| R/W-0                  | R/W-0                                                | R/W-0                                  | R/W-0                       | R/C-0                    | R/C-0              | R-0               | R/W-0         |

| 0A <sup>(1)</sup>      | OB <sup>(1)</sup>                                    | SA <sup>(1,4)</sup>                    | SB <sup>(1,4)</sup>         | OAB <sup>(1)</sup>       | SAB <sup>(1)</sup> | DA <sup>(1)</sup> | DC            |

| bit 15                 |                                                      |                                        |                             |                          |                    |                   | bit 8         |

| R/W-0 <sup>(2,3)</sup> | R/W-0 <sup>(2,3)</sup>                               | R/W-0 <sup>(2,3)</sup>                 | R-0                         | R/W-0                    | R/W-0              | R/W-0             | R/W-0         |

| IPL2                   | IPL1                                                 | IPL0                                   | RA                          | N                        | OV                 | Z                 | С             |

| bit 7                  | ·                                                    | •                                      |                             | •                        |                    |                   | bit (         |

| Legend:                |                                                      | C = Clearable                          | e bit                       |                          |                    |                   |               |

| R = Readab             | le bit                                               | W = Writable                           | bit                         | U = Unimpler             | nented bit, read   | l as '0'          |               |

| -n = Value a           | t POR                                                | '1'= Bit is set                        |                             | '0' = Bit is cle         | ared               | x = Bit is unkr   | iown          |

|                        |                                                      |                                        |                             |                          |                    |                   |               |

| bit 15                 | OA: Accumul                                          | ator A Overflov                        | v Status bit <sup>(1)</sup> |                          |                    |                   |               |

|                        | 1 = Accumula                                         | ator A has over                        | flowed                      |                          |                    |                   |               |

|                        | 0 = Accumula                                         | ator A has not o                       | verflowed                   |                          |                    |                   |               |

| bit 14                 | OB: Accumul                                          | ator B Overflov                        | v Status bit <sup>(1)</sup> |                          |                    |                   |               |

|                        | 1 = Accumula                                         | ator B has over                        | flowed                      |                          |                    |                   |               |

|                        |                                                      | ator B has not c                       |                             |                          |                    |                   |               |

| bit 13                 | SA: Accumul                                          | ator A Saturatio                       | on 'Sticky' Sta             | tus bit <sup>(1,4)</sup> |                    |                   |               |

|                        |                                                      | ator A is saturat<br>ator A is not sat |                             | en saturated at          | some time          |                   |               |

| bit 12                 | SB: Accumul                                          | ator B Saturatio                       | on 'Sticky' Sta             | tus bit <sup>(1,4)</sup> |                    |                   |               |

|                        | 1 = Accumula                                         | ator B is saturat<br>ator B is not sat | ted or has bee              |                          | some time          |                   |               |

| bit 11                 |                                                      | B Combined A                           |                             | vorflow Status           | ы#(1)              |                   |               |

|                        |                                                      | ators A or B have                      |                             | vernow Status            | DIL                |                   |               |

|                        |                                                      | ccumulators A                          |                             | erflowed                 |                    |                   |               |

| bit 10                 |                                                      | B Combined Ad                          |                             |                          | (1)                |                   |               |

|                        |                                                      |                                        |                             |                          | urated at some     | time              |               |

|                        | 0 = Neither A                                        | ccumulators A                          | or B are satur              | ated                     |                    |                   |               |

| bit 9                  | DA: DO Loop                                          | Active bit <sup>(1)</sup>              |                             |                          |                    |                   |               |

|                        | 1 = DO <b>loop is</b>                                | s in progress                          |                             |                          |                    |                   |               |

|                        | 0 = DO <b>loop</b> is                                | s not in progres                       | S                           |                          |                    |                   |               |

| bit 8                  | DC: MCU AL                                           | U Half Carry/Bo                        | orrow bit                   |                          |                    |                   |               |

|                        |                                                      | out from the 4th sult occurred         | low-order bit (             | for byte-sized c         | lata) or 8th low-  | order bit (for wo | rd-sized data |

|                        | 0 = No carry                                         |                                        |                             | oit (for byte-siz        | ed data) or 8th    | low-order bit (f  | or word-size  |

|                        | his bit is available                                 |                                        |                             |                          |                    |                   | -             |

| L                      | he IPL<2:0> bits<br>evel. The value ir<br>PL<3> = 1. |                                        |                             |                          |                    |                   |               |

#### REGISTER 3-1: SR: CPU STATUS REGISTER

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **4:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

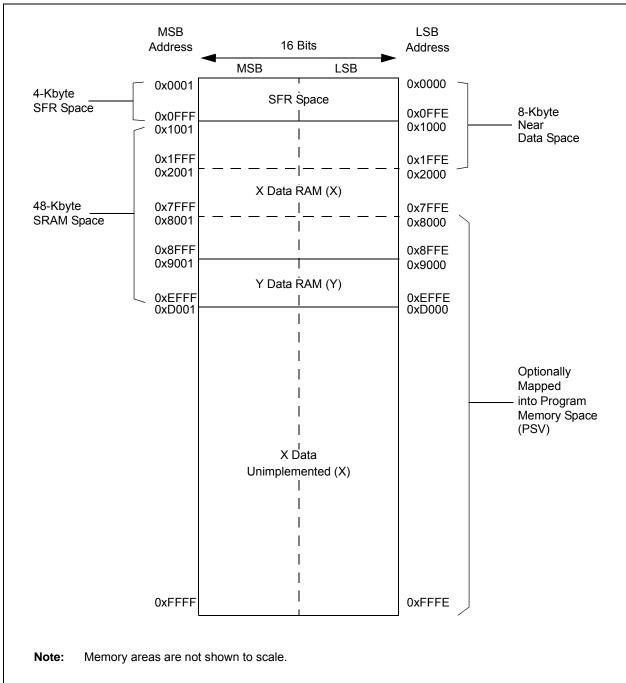

## 4.2 Data Address Space

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a separate 16-bit-wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps, which are presented by device family and memory size, are shown in Figure 4-7 through Figure 4-16.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes (32K words).

The base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space, which has a total address range of 16 Mbytes.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement up to 52 Kbytes of data memory (4 Kbytes of data memory for Special Function Registers and up to 48 Kbytes of data memory for RAM). If an EA points to a location outside of this area, an all-zero word or byte is returned.

## 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit-wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

## 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

## 4.2.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

## 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

## TABLE 4-41: PMD REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | —      | —      | _      | CMPMD  | _      | _      | CRCMD  | _     | —     | _      | —      | —      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      |        | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      | PWM3MD | PWM2MD | PWM1MD | _      | _     | _     | _      | _      | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| PIVID7       | 0760  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 7.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 7.3.1 KEY RESOURCES

- "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 7.4 Interrupt Control and Status Registers

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- INTTREG

## 7.4.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior and also contains the Global Interrupt Enable bit (GIE).

INTCON3 contains the status flags for the DMA and DO stack overflow status trap sources.

The INTCON4 register contains the software generated hard trap status bit (SGHT).

## 7.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

## 7.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

#### 7.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

#### 7.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number bits (VECNUM<7:0>) and Interrupt Priority Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

## 7.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers refer to "**CPU**" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

## 17.2 QEI Control Registers

|  | REGISTER 17-1: | QEI1CON: QEI1 CONTROL REGISTER |

|--|----------------|--------------------------------|

|--|----------------|--------------------------------|

| U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         —       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |                                                                                                  |                                                                                                                 |                                                                                              |                                                                                                |                                                            |                                   |                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------|---------------------|

| bit 15       bit 2         U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       -       intdividue       W= Writable bit       U = Unimplemented bit, read as '0'       bit 15       GEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to         bit 13       GEISDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD-2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       100 = Modulo Count mode for position counter         100 = Next index event after home event initializes position counter with contents of QEI11C register       100 = Next index input event initializes position counter with contents of QEI11C register       100 = Index input event dees not affect position coun                                                                                                                                                                                                  | R/W-0        | U-0                                                                                              | R/W-0                                                                                                           | R/W-0                                                                                        | R/W-0                                                                                          | R/W-0                                                      | R/W-0                             | R/W-0               |

| U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       bit 0       Dit 7       Dit 7       Dit 7       Dit 7       Dit 7         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       Dit 7         en value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN:       Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0         0 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to       Dit 13       QEISDL: QEI Stop in Idle Mode bit         1 = Discontinues module operation in Idle mode       0 = Continues module operation in Idle mode       Di Continues module operation on In Idle mode         Dit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         100 = Modulo Count mode for position counter       101 = Resets the position counter       101 = Resets the position counter with contents of QEI1IC register         101 = Resets the position counter when the position counter with contents of QEI1IC register       000 = Index input e                                                                                                                                                                                                                                          | QEIEN        | _                                                                                                | QEISIDL                                                                                                         | PIMOD2 <sup>(1)</sup>                                                                        | PIMOD1 <sup>(1)</sup>                                                                          | PIMOD0 <sup>(1)</sup>                                      | IMV1 <sup>(2)</sup>               | IMV0 <sup>(2)</sup> |

| -       INTDIV2 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       bit 7       bit 0         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       bit 0         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'       Bit is cleared       x = Bit is unknown         bit 13       QEISDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation unter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Modulo Count mode for position counter         10 = Resets the position counter when the position counter with contents of QEI1IC register       100 = Second index event after home event initializes position counter with contents of QEI1IC register         10 = Next index input event frees the position counter       110 = Resets the position counter         11 = Reserved       11 = First index event after home event initializes position counter with contents of QEI1IC register         10 = Next index input event free home event initializes position counter with contents of QEI1IC register                                                                                                                                          | bit 15       |                                                                                                  |                                                                                                                 |                                                                                              |                                                                                                |                                                            |                                   | bit 8               |

| -       INTDIV2 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       bit 7       bit 0         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       bit 0         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'       Bit is cleared       x = Bit is unknown         bit 13       QEISDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation unter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Modulo Count mode for position counter         10 = Resets the position counter when the position counter with contents of QEI1IC register       100 = Second index event after home event initializes position counter with contents of QEI1IC register         10 = Next index input event frees the position counter       110 = Resets the position counter         11 = Reserved       11 = First index event after home event initializes position counter with contents of QEI1IC register         10 = Next index input event free home event initializes position counter with contents of QEI1IC register                                                                                                                                          |              |                                                                                                  |                                                                                                                 |                                                                                              |                                                                                                |                                                            |                                   |                     |

| bit 7       bit 0         Legend:       W = Writable bit       U = Unimplemented bit, read as '0'         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Module counters are enabled         0 = Module counters are disabled, but SFRs can be read or written to       0 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'       0 = Continues module operation when device enters Idle mode         0 = Continues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD-2:0-: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Resets the position counter         101 = Resets the position counter when the position counter with contents of QEI1IC register         101 = Nexet input event after home event initializes position counter with contents of QEI1IC register         010 = Next index input event resets the position counter         011 = Every index input event resets the position counter         012 = Nease B match occurs when QEB = 1         0 = Phase B match occurs when QEB = 0         bit 8       IMV0: Index Match Value for Phase A bit <sup>(2)</sup> 1 = Phase A match occurs when QEA = 1 <t< td=""><td>U-0</td><td></td><td></td><td></td><td>R/W-0</td><td>R/W-0</td><td>R/W-0</td><td>R/W-0</td></t<>                                                                       | U-0          |                                                                                                  |                                                                                                                 |                                                                                              | R/W-0                                                                                          | R/W-0                                                      | R/W-0                             | R/W-0               |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0         0 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to       0         bit 14       Unimplemented: Read as '0'       0         bit 13       QEISIDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         11 = Reserved       111 = Reserved         110 = Modulo Count mode for position counter       101 = Resets the position counter when the position counter equals QEI1GEC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       100 = Second index event after home event initializes position counter with contents of QEI1IC register         101 = First index vent after home event initializes position counter with contents of QEI1IC register       001 = Every index input event resets the position counter         010 = Next index input event does not affect position counter       001 = Every index input event after home event initializes position counter with contents of QEI1IC register                                                                                                                                |              | INTDIV2 <sup>(3)</sup>                                                                           | INTDIV1 <sup>(3)</sup>                                                                                          | INTDIV0 <sup>(3)</sup>                                                                       | CNTPOL                                                                                         | GATEN                                                      | CCM1                              |                     |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is cleared       x = Bit is unknown         bit 15       QEISIDL: QEI Stop in Idle Mode bit       1 = Module counters are disabled, but SFRs can be read or written to       bit 14         Unimplemented: Read as '0'       East as '0'       East as '0'       East as '0'         bit 13       QEISIDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       10 = Second index event after home event initializes position counter with contents of QEI1IC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter         101 = Reserved       III = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes position counter with contents of QEI1IC register         102 = Next index input event does not affect position counter       01 = Phase                                                                                              | bit 7        |                                                                                                  |                                                                                                                 |                                                                                              |                                                                                                |                                                            |                                   | bit 0               |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is cleared       x = Bit is unknown         bit 15       QEISIDL: QEI Stop in Idle Mode bit       1 = Module counters are disabled, but SFRs can be read or written to       bit 14         Unimplemented: Read as '0'       East as '0'       East as '0'       East as '0'         bit 13       QEISIDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       10 = Second index event after home event initializes position counter with contents of QEI1IC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter         101 = Reserved       III = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes position counter with contents of QEI1IC register         102 = Next index input event does not affect position counter       01 = Phase                                                                                              | Logondy      |                                                                                                  |                                                                                                                 |                                                                                              |                                                                                                |                                                            |                                   |                     |

| n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is unknown         bit 14       Unimplemented: Read as '0'       0'       0'       Bit is cleared       0 = Continues module operation when device enters ldle mode       0 = Continues module operation in ldle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       10 = Second index event after home event initializes position counter with contents of QEI11C register         100 = Second index event after home event initializes position counter with contents of QEI11C register       10 = Next index input event resets the position counter with contents of QEI11C register         101 = Every index input event resets the position counter       00 = Index input event does not affect position counter         001 = Every index input event genst bit <sup>(2)</sup> 1 = Phase B match occurs when QEB = 1         011 = Phase B match occurs when QEB = 1       0 = Phase B match occurs when QEA = 1         015 = Phase A match occurs when QEA = 1       0 = Phase A match occurs when QEA = 1         015 = Phase A match occurs when QEA =                                                                                                  |              | lo hit                                                                                           |                                                                                                                 | hit                                                                                          | II – Unimplor                                                                                  | monted bit read                                            | ac '0'                            |                     |

| bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit         1 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'         bit 13       QEISIDL: QEI Stop in Idle Mode bit         1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         11 = Discontinues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       100 = Second index event after home event initializes position counter with contents of QEI1IC register         011 = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event resets the position counter         001 = Nevery index input eve                                                                                                  |              |                                                                                                  |                                                                                                                 |                                                                                              | •                                                                                              |                                                            |                                   |                     |

| <ul> <li>1 = Module counters are enabled</li> <li>0 = Module counters are disabled, but SFRs can be read or written to</li> <li>bit 14</li> <li>Unimplemented: Read as '0'</li> <li>bit 13</li> <li>QEISIDL: QEI Stop in Idle Mode bit</li> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> <li>0 = Continues module operation in Idle mode</li> <li>0 = Continues module operation counter Initialization Mode Select bits<sup>(1)</sup></li> <li>111 = Reserved</li> <li>110 = Modulo Count mode for position counter</li> <li>101 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event initializes the position counter with contents of QEI1IC register</li> <li>010 = Next index input event resets the position counter with contents of QEI1IC register</li> <li>011 = Every index input event resets the position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index Match Value for Phase B bit<sup>(2)</sup></li> <li>1 = Phase B match occurs when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>bit 8</li> <li>IMV0: Index Match Value for Phase A bit<sup>(2)</sup></li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> </ul> | -n = value a | PUR                                                                                              | I = Bit is set                                                                                                  |                                                                                              | 0 = Bit is cle                                                                                 | ared                                                       | x = Bit is unkr                   | lown                |

| bit 13       QEISDL: QEI Stop in Idle Mode bit         1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Modulo Count mode for position counter         100 = Modulo Count mode for position counter       101 = Resets the position counter when the position counter equals QEI1GEC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter with contents of QEI1IC register         011 = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter with contents of QEI1IC register         011 = Every index input event resets the position counter       001 = Every index input event for position counter         001 = Index input event does not affect position counter       000 = Index input event does not affect position counter         001 = Phase B match occurs when QEB = 1       0 = Phase B match occurs when QEB = 0         0it 8       IMV0: Index Match Value for Phase A bit <sup>(2)</sup> 1 = Phase A match occurs when QEA = 1       0 = Phase A match occurs when QEA = 0         0it 7       Unimplemented: Read as '0'                                                                                                                                                                                   | bit 15       | 1 = Module co                                                                                    | ounters are ena                                                                                                 | abled                                                                                        |                                                                                                |                                                            |                                   |                     |

| <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> <li>bit 12-10</li> <li>PIMOD&lt;2:0&gt;: Position Counter Initialization Mode Select bits<sup>(1)</sup></li> <li>111 = Reserved</li> <li>10 = Modulo Count mode for position counter</li> <li>10 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event resets the position counter with contents of QEI1IC register</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event operation when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>bit 8</li> <li>IMV0: Index Match Value for Phase A bit<sup>(2)</sup></li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                  | bit 14       | Unimplemen                                                                                       | ted: Read as '                                                                                                  | 0'                                                                                           |                                                                                                |                                                            |                                   |                     |

| <ul> <li>0 = Continues module operation in Idle mode</li> <li>bit 12-10</li> <li>PIMOD&lt;2:0&gt;: Position Counter Initialization Mode Select bits<sup>(1)</sup></li> <li>111 = Reserved</li> <li>10 = Modulo Count mode for position counter</li> <li>101 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event resets the position counter with contents of QEI1IC register</li> <li>001 = Every index input event resets the position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event QEB = 1</li> <li>0 = Phase B match occurs when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>bit 8</li> <li>IMV0: Index Match Value for Phase A bit<sup>(2)</sup></li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> </ul>                                                                                                                                                                                                                                                                                              | bit 13       | QEISIDL: QE                                                                                      | I Stop in Idle M                                                                                                | lode bit                                                                                     |                                                                                                |                                                            |                                   |                     |

| <ul> <li>111 = Reserved</li> <li>10 = Modulo Count mode for position counter</li> <li>101 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>011 = First index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event initializes the position counter with contents of QEI1IC register</li> <li>011 = Every index input event resets the position counter with contents of QEI1IC register</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>011 = Phase B match occurs when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>0 = Phase A match occurs when QEA = 0</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |                                                                                                  |                                                                                                                 |                                                                                              |                                                                                                | dle mode                                                   |                                   |                     |

| <ul> <li>110 = Modulo Count mode for position counter</li> <li>101 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>011 = First index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event initializes the position counter with contents of QEI1IC register</li> <li>001 = Every index input event resets the position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event for Phase B bit<sup>(2)</sup></li> <li>1 = Phase B match occurs when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>bit 8</li> <li>IMV0: Index Match Value for Phase A bit<sup>(2)</sup></li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 12-10    | PIMOD<2:0>                                                                                       | : Position Cour                                                                                                 | nter Initializatio                                                                           | on Mode Selec                                                                                  | t bits <sup>(1)</sup>                                      |                                   |                     |

| 1 = Phase B match occurs when QEB = 1         0 = Phase B match occurs when QEB = 0         bit 8       IMV0: Index Match Value for Phase A bit <sup>(2)</sup> 1 = Phase A match occurs when QEA = 1         0 = Phase A match occurs when QEA = 0         bit 7       Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              | 110 = Modulo<br>101 = Resets<br>100 = Second<br>011 = First in<br>010 = Next in<br>001 = Every i | b Count mode f<br>the position co<br>d index event a<br>dex event after<br>index input even<br>index input even | bunter when the<br>fter home event<br>home event in<br>t initializes the<br>put resets the p | e position cou<br>at initializes posi<br>nitializes positi<br>position coun<br>position counte | sition counter wit<br>on counter with<br>ter with contents | h contents of C<br>contents of QE | EI1IC register      |

| 0 = Phase B match occurs when QEB = 0         bit 8         IMV0: Index Match Value for Phase A bit <sup>(2)</sup> 1 = Phase A match occurs when QEA = 1         0 = Phase A match occurs when QEA = 0         bit 7         Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bit 9        | IMV1: Index I                                                                                    | Match Value for                                                                                                 | <sup>-</sup> Phase B bit <sup>(2</sup>                                                       | )                                                                                              |                                                            |                                   |                     |

| bit 8       IMV0: Index Match Value for Phase A bit <sup>(2)</sup> 1 = Phase A match occurs when QEA = 1         0 = Phase A match occurs when QEA = 0         bit 7       Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |                                                                                                  |                                                                                                                 |                                                                                              |                                                                                                |                                                            |                                   |                     |

| 1 = Phase A match occurs when QEA = 10 = Phase A match occurs when QEA = 0bit 7Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |                                                                                                  |                                                                                                                 |                                                                                              | <b>N</b>                                                                                       |                                                            |                                   |                     |

| 0 = Phase A match occurs when QEA = 0         bit 7         Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 8        |                                                                                                  |                                                                                                                 |                                                                                              | 1                                                                                              |                                                            |                                   |                     |

| bit 7 Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                                                                                  |                                                                                                                 |                                                                                              |                                                                                                |                                                            |                                   |                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 7        |                                                                                                  |                                                                                                                 |                                                                                              |                                                                                                |                                                            |                                   |                     |