Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 44-VTLA (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128mc204t-i-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

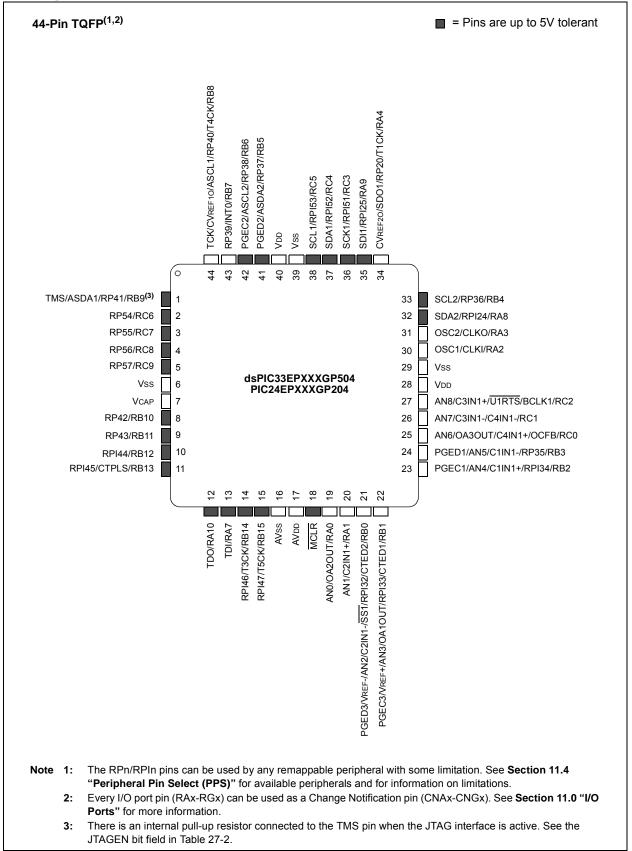

### **Pin Diagrams (Continued)**

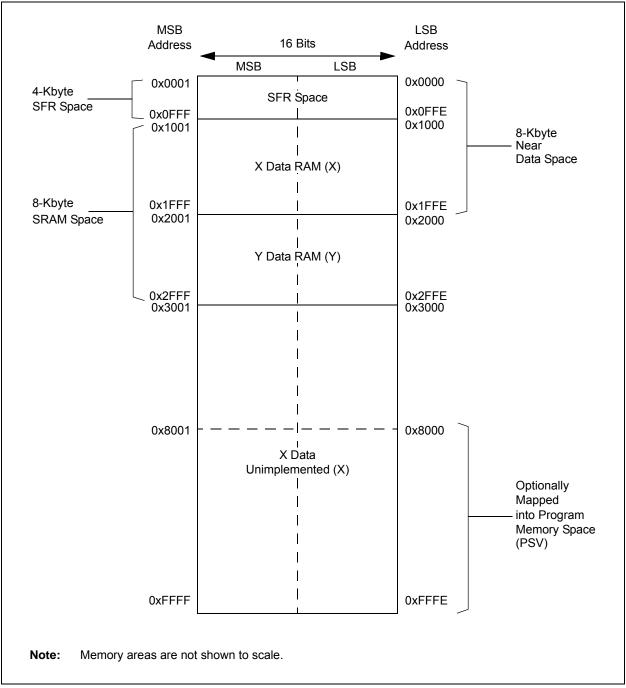

## FIGURE 4-8: DATA MEMORY MAP FOR dsPIC33EP64MC20X/50X AND dsPIC33EP64GP50X DEVICES

### 7.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

### 7.3.1 KEY RESOURCES

- "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

### 7.4 Interrupt Control and Status Registers

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- INTTREG

### 7.4.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior and also contains the Global Interrupt Enable bit (GIE).

INTCON3 contains the status flags for the DMA and DO stack overflow status trap sources.

The INTCON4 register contains the software generated hard trap status bit (SGHT).

### 7.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

### 7.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

### 7.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

### 7.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number bits (VECNUM<7:0>) and Interrupt Priority Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

### 7.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers refer to "**CPU**" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

| REGISTER 7-5: | INTCON3: INTERRUPT CONTROL REGISTER 3 |

|---------------|---------------------------------------|

| U-0                                | U-0                                          | U-0                                          | U-0                                     | U-0          | U-0              | U-0    | U-0   |  |  |  |

|------------------------------------|----------------------------------------------|----------------------------------------------|-----------------------------------------|--------------|------------------|--------|-------|--|--|--|

|                                    | —                                            | _                                            | —                                       | —            | —                | —      | _     |  |  |  |

| bit 15                             |                                              |                                              |                                         |              |                  | •      | bit 8 |  |  |  |

|                                    |                                              |                                              |                                         |              |                  |        |       |  |  |  |

| U-0                                | U-0                                          | R/W-0                                        | R/W-0                                   | U-0          | U-0              | U-0    | U-0   |  |  |  |

| —                                  | —                                            | DAE                                          | DOOVR                                   | —            | —                | —      | —     |  |  |  |

| bit 7                              |                                              |                                              |                                         |              |                  |        | bit 0 |  |  |  |

|                                    |                                              |                                              |                                         |              |                  |        |       |  |  |  |

| Legend:                            |                                              |                                              |                                         |              |                  |        |       |  |  |  |

| R = Readab                         | le bit                                       | W = Writable                                 | bit                                     | U = Unimplei | mented bit, read | as '0' |       |  |  |  |

| -n = Value at POR '1' = Bit is set |                                              | t                                            | '0' = Bit is cleared x = Bit is unknown |              |                  | nown   |       |  |  |  |

|                                    |                                              |                                              |                                         |              |                  |        |       |  |  |  |

| bit 15-6                           | Unimplemen                                   | ted: Read as                                 | '0'                                     |              |                  |        |       |  |  |  |

| bit 5                              | DAE: DMA Address Error Soft Trap Status bit  |                                              |                                         |              |                  |        |       |  |  |  |

|                                    | 1 = DMA add                                  | 1 = DMA address error soft trap has occurred |                                         |              |                  |        |       |  |  |  |

|                                    | 0 = DMA add                                  | ress error soft                              | trap has not o                          | ccurred      |                  |        |       |  |  |  |

| bit 4                              | DOOVR: DO                                    | Stack Overflov                               | v Soft Trap Sta                         | tus bit      |                  |        |       |  |  |  |

|                                    | 1 = DO stack overflow soft trap has occurred |                                              |                                         |              |                  |        |       |  |  |  |

| I = D0 | Stack Overnow  | 3011 11 ap 11 a3 | occurred     |

|--------|----------------|------------------|--------------|

| 0 = DO | stack overflow | soft trap has    | not occurred |

| bit 3-0 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

### REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|-----|-----|-----|-----|-----|-----|-------|

| —       | —   | —   | —   | —   | —   | —   | —     |

| bit 15  |     |     |     |     | •   |     | bit 8 |

|         |     |     |     |     |     |     |       |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

| _       | —   | —   |     | —   | —   | —   | SGHT  |

| bit 7   |     |     |     |     | •   |     | bit 0 |

|         |     |     |     |     |     |     |       |

| Legend: |     |     |     |     |     |     |       |

| 3                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

|                   |                  |                        |                    |

bit 0

SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

| U-0    | U-0 | U-0 | U-0 | U-0   | U-0   | U-0   | U-0   |

|--------|-----|-----|-----|-------|-------|-------|-------|

| _      |     |     |     | _     | —     |       | —     |

| bit 15 |     |     |     |       |       |       | bit 8 |

|        |     |     |     |       |       |       |       |

| U-0    | U-0 | U-0 | U-0 | R-0   | R-0   | R-0   | R-0   |

| —      | —   | —   | _   | PPST3 | PPST2 | PPST1 | PPST0 |

| bit 7  |     |     |     |       |       |       | bit 0 |

### REGISTER 8-14: DMAPPS: DMA PING-PONG STATUS REGISTER

| Legend:                               |                                    |                                                                                       |                                    |                    |  |  |  |

|---------------------------------------|------------------------------------|---------------------------------------------------------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit<br>-n = Value at POR |                                    | W = Writable bit                                                                      | U = Unimplemented bit, read as '0' |                    |  |  |  |

|                                       |                                    | '1' = Bit is set                                                                      | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 15-4                              | Unimplo                            | mented: Read as '0'                                                                   |                                    |                    |  |  |  |

|                                       |                                    | DMA Channel 3 Ping-Pong I                                                             | Modo Status Elag bit               |                    |  |  |  |

| bit 5                                 | 1 = DMA                            | ASTB3 register is selected<br>ASTA3 register is selected                              | vioue Status Flag bit              |                    |  |  |  |

| bit 2                                 | 1 = DMA                            | DMA Channel 2 Ping-Pong I<br>ASTB2 register is selected<br>ASTA2 register is selected | Mode Status Flag bit               |                    |  |  |  |

| bit 1                                 | PPST1:                             | DMA Channel 1 Ping-Pong I                                                             | Mode Status Flag bit               |                    |  |  |  |

|                                       | 1 - DMACTD1 register is calculated |                                                                                       |                                    |                    |  |  |  |

- 1 = DMASTB1 register is selected0 = DMASTA1 register is selected

- bit 0 PPST0: DMA Channel 0 Ping-Pong Mode Status Flag bit

- 1 = DMASTB0 register is selected

- 0 = DMASTA0 register is selected

| REGISTER     | <u>R 10-2: PMD</u> 2                              | 2: PERIPHER                                         | AL MODULE       | DISABLE C         | ONTROL RE       | GISTER 2        |       |  |  |  |

|--------------|---------------------------------------------------|-----------------------------------------------------|-----------------|-------------------|-----------------|-----------------|-------|--|--|--|

| U-0          | U-0                                               | U-0                                                 | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |

| _            |                                                   | _                                                   |                 | IC4MD             | IC3MD           | IC2MD           | IC1MD |  |  |  |

| bit 15       |                                                   |                                                     |                 |                   |                 |                 | bit   |  |  |  |

| U-0          | U-0                                               | U-0                                                 | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |

|              |                                                   |                                                     |                 | OC4MD             | OC3MD           | OC2MD           | OC1MD |  |  |  |

| bit 7        |                                                   |                                                     |                 |                   |                 |                 | bit   |  |  |  |

|              |                                                   |                                                     |                 |                   |                 |                 |       |  |  |  |

| Legend:      | 1.1.1                                             |                                                     |                 |                   |                 |                 |       |  |  |  |

| R = Readab   |                                                   | W = Writable b                                      | Dit             | •                 | nented bit, rea |                 |       |  |  |  |

| -n = Value a | at POR                                            | '1' = Bit is set                                    |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |  |  |  |

| bit 15-12    | Unimplemen                                        | ted: Read as '0                                     | ,               |                   |                 |                 |       |  |  |  |

| bit 11       | -                                                 | t Capture 4 Mod                                     |                 |                   |                 |                 |       |  |  |  |

|              | •                                                 | oture 4 module is                                   |                 |                   |                 |                 |       |  |  |  |

|              | 0 = Input Cap                                     | oture 4 module is                                   | s enabled       |                   |                 |                 |       |  |  |  |

| bit 10       | IC3MD: Input                                      | C3MD: Input Capture 3 Module Disable bit            |                 |                   |                 |                 |       |  |  |  |

|              |                                                   | oture 3 module is                                   |                 |                   |                 |                 |       |  |  |  |

|              |                                                   | oture 3 module is                                   |                 |                   |                 |                 |       |  |  |  |

| bit 9        |                                                   | IC2MD: Input Capture 2 Module Disable bit           |                 |                   |                 |                 |       |  |  |  |

|              |                                                   | oture 2 module is<br>oture 2 module is              |                 |                   |                 |                 |       |  |  |  |

| bit 8        | IC1MD: Input                                      | t Capture 1 Mod                                     | ule Disable bit |                   |                 |                 |       |  |  |  |

|              | 1 = Input Cap                                     | oture 1 module is<br>oture 1 module is              | s disabled      |                   |                 |                 |       |  |  |  |

| bit 7-4      |                                                   | ted: Read as '0                                     |                 |                   |                 |                 |       |  |  |  |

| bit 3        | <b>OC4MD:</b> Output Compare 4 Module Disable bit |                                                     |                 |                   |                 |                 |       |  |  |  |

|              |                                                   | ompare 4 modul                                      |                 |                   |                 |                 |       |  |  |  |

|              | -                                                 | ompare 4 modu                                       |                 |                   |                 |                 |       |  |  |  |

| bit 2        |                                                   | put Compare 3                                       |                 | e bit             |                 |                 |       |  |  |  |

|              | •                                                 | ompare 3 modul                                      |                 |                   |                 |                 |       |  |  |  |

| L:1 4        | -                                                 | ompare 3 modul                                      |                 | . h.:4            |                 |                 |       |  |  |  |

| bit 1        |                                                   | put Compare 2                                       |                 |                   |                 |                 |       |  |  |  |

|              | $\perp$ – Output Co                               | ompare 2 modu                                       |                 |                   |                 |                 |       |  |  |  |

|              | 0 = Output Co                                     | ompare 2 modul                                      | le is enabled   |                   |                 |                 |       |  |  |  |

| bit 0        |                                                   | ompare 2 modul<br>put Compare 1                     |                 | e bit             |                 |                 |       |  |  |  |

| bit 0        | OC1MD: Out                                        | ompare 2 modul<br>put Compare 1 l<br>ompare 1 modul | Module Disable  | e bit             |                 |                 |       |  |  |  |

#### ~

| REGISTER     | TU-5: PIVID6                      | . PERIPHER       |                           | DISABLE C                               | UNIROL RE             | GISIER 6              |                       |  |

|--------------|-----------------------------------|------------------|---------------------------|-----------------------------------------|-----------------------|-----------------------|-----------------------|--|

| U-0          | U-0                               | U-0              | U-0                       | U-0                                     | R/W-0                 | R/W-0                 | R/W-0                 |  |

| —            | —                                 | —                | —                         | —                                       | PWM3MD <sup>(1)</sup> | PWM2MD <sup>(1)</sup> | PWM1MD <sup>(1)</sup> |  |

| bit 15       |                                   |                  |                           |                                         |                       |                       | bit 8                 |  |

|              |                                   |                  |                           |                                         |                       |                       |                       |  |

| U-0          | U-0                               | U-0              | U-0                       | U-0                                     | U-0                   | U-0                   | U-0                   |  |

|              |                                   |                  |                           |                                         |                       |                       |                       |  |

| bit 7        |                                   |                  |                           |                                         |                       |                       | bit 0                 |  |

|              |                                   |                  |                           |                                         |                       |                       |                       |  |

| Legend:      |                                   |                  |                           |                                         |                       |                       |                       |  |

| R = Readab   | R = Readable bit W = Writable bit |                  | bit                       | U = Unimplemented bit, read as '0'      |                       |                       |                       |  |

| -n = Value a | t POR                             | '1' = Bit is set |                           | '0' = Bit is cleared x = Bit is unknown |                       |                       | iown                  |  |

|              |                                   |                  |                           |                                         |                       |                       |                       |  |

| bit 15-11    | Unimplement                       | ted: Read as '   | כ'                        |                                         |                       |                       |                       |  |

| bit 10       | PWM3MD: P\                        | NM3 Module D     | isable bit <sup>(1)</sup> |                                         |                       |                       |                       |  |

|              | 1 = PWM3 mo                       | odule is disable | ed                        |                                         |                       |                       |                       |  |

|              | 0 = PWM3 mo                       | odule is enable  | d                         |                                         |                       |                       |                       |  |

| bit 9        | PWM2MD: P\                        | NM2 Module D     | isable bit <sup>(1)</sup> |                                         |                       |                       |                       |  |

|              | 1 = PWM2 module is disabled       |                  |                           |                                         |                       |                       |                       |  |

|              | 0 = PWM2 mo                       | odule is enable  | d                         |                                         |                       |                       |                       |  |

| bit 8        | PWM1MD: P\                        | NM1 Module D     | isable bit <sup>(1)</sup> |                                         |                       |                       |                       |  |

|              |                                   | odule is disable |                           |                                         |                       |                       |                       |  |

|              | 0 = PWM1 mo                       | odule is enable  | d                         |                                         |                       |                       |                       |  |

| bit 7-0      | Unimplement                       | ted: Read as '   | כ'                        |                                         |                       |                       |                       |  |

### REGISTER 10-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

Note 1: This bit is available on dsPIC33EPXXXMC50X/20X and PIC24EPXXXMC20X devices only.

| U-0          | U-0                            | U-0                                | U-0   | U-0                  | U-0              | U-0                | U-0   |

|--------------|--------------------------------|------------------------------------|-------|----------------------|------------------|--------------------|-------|

| —            | —                              | —                                  | _     | —                    | —                | —                  | _     |

| bit 15       |                                |                                    |       |                      |                  |                    | bit 8 |

|              |                                |                                    |       |                      |                  |                    |       |

| U-0          | R/W-0                          | R/W-0                              | R/W-0 | R/W-0                | R/W-0            | R/W-0              | R/W-0 |

| —            |                                |                                    |       | INT2R<6:0>           |                  |                    |       |

| bit 7        |                                |                                    |       |                      |                  |                    | bit 0 |

|              |                                |                                    |       |                      |                  |                    |       |

| Legend:      |                                |                                    |       |                      |                  |                    |       |

| R = Readal   | ole bit                        | W = Writable                       | bit   | U = Unimpler         | mented bit, read | as '0'             |       |

| -n = Value a | at POR                         | '1' = Bit is set                   |       | '0' = Bit is cleared |                  | x = Bit is unknown |       |

|              |                                |                                    |       |                      |                  |                    |       |

| bit 15-7     | Unimplemen                     | ted: Read as 'd                    | )'    |                      |                  |                    |       |

| bit 6-0      |                                | Assign Externa<br>-2 for input pin |       |                      | orresponding RI  | Pn Pin bits        |       |

|              | 1111001 = Input tied to RPI121 |                                    |       |                      |                  |                    |       |

|              |                                |                                    |       |                      |                  |                    |       |

|              |                                |                                    |       |                      |                  |                    |       |

|              | 0000001 – Ir                   | put tied to CMI                    | ⊃1    |                      |                  |                    |       |

|              |                                | put tied to Civil                  |       |                      |                  |                    |       |

|              |                                |                                    |       |                      |                  |                    |       |

|              |                                |                                    |       |                      |                  |                    |       |

### REGISTER 11-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

### REGISTER 11-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0<br>— T2CKR<6:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |                     |                  |       |                                         |                  |        |       |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------|------------------|-------|-----------------------------------------|------------------|--------|-------|--|

| U-0       R/W-0       R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0          | U-0                 | U-0              | U-0   | U-0                                     | U-0              | U-0    | U-0   |  |

| U-0       R/W-0       R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _            | -                   | —                | _     | —                                       | —                | —      | —     |  |

| —       T2CKR<6:0>         bit 7       t         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 15       |                     |                  |       |                                         |                  |        | bit 8 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                                         |                  |        |       |  |

| bit 7       Image: Constraint of the system of | U-0          | R/W-0               | R/W-0            | R/W-0 | R/W-0                                   | R/W-0            | R/W-0  | R/W-0 |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . <td< td=""><td>—</td><td></td><td></td><td></td><td>T2CKR&lt;6:0&gt;</td><td>&gt;</td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —            |                     |                  |       | T2CKR<6:0>                              | >                |        |       |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 7        |                     |                  |       |                                         |                  |        | bit 0 |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |                     |                  |       |                                         |                  |        |       |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Legend:      |                     |                  |       |                                         |                  |        |       |  |

| bit 15-7 Unimplemented: Read as '0'<br>bit 6-0 T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121<br>0000001 = Input tied to CMP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R = Readab   | ole bit             | W = Writable I   | bit   | U = Unimpler                            | mented bit, read | as '0' |       |  |

| bit 6-0 <b>T2CKR&lt;6:0&gt;:</b> Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -n = Value a | at POR              | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                  |        | nown  |  |

| bit 6-0 <b>T2CKR&lt;6:0&gt;:</b> Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                     |                  |       |                                         |                  |        |       |  |

| (see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121<br>0000001 = Input tied to CMP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 15-7     | Unimplemen          | ted: Read as 'd  | )'    |                                         |                  |        |       |  |

| 1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5 ( ) 1 5 1  |                     |                  |       |                                         |                  |        |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                                         |                  |        |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                                         |                  |        |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                                         |                  |        |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | 0000001 = Ir        | nout tied to CM  | ⊃1    |                                         |                  |        |       |  |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |                     |                  |       |                                         |                  |        |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | 0000000 <b>- II</b> | iput tied to vss |       |                                         |                  |        |       |  |

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|------------|-------|-------|-------|

| —      | —     |       |       | —          | —     | —     | —     |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| —      |       |       |       | U1RXR<6:0> | >     |       |       |

| bit 7  |       |       |       |            |       |       | bit 0 |

|        |       |       |       |            |       |       |       |

### REGISTER 11-10: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0' bit 6-0 U1RXR<6:0>: Assign UART1 Receive (U1RX) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 . . . . . . . . . .

### REGISTER 11-11: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| U-0     | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|------------|-------|-------|-------|

| 0-0     | 0-0   | 0-0   | 0-0   | 0-0        | 0-0   | 0-0   | 0-0   |

|         | —     |       | _     | _          | —     | —     |       |

| bit 15  |       |       |       |            |       |       | bit 8 |

|         |       |       |       |            |       |       |       |

| U-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| —       |       |       |       | U2RXR<6:0> | >     |       |       |