Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | · ·                                                                            |

| RAM Size                   | 8K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128mc206-h-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

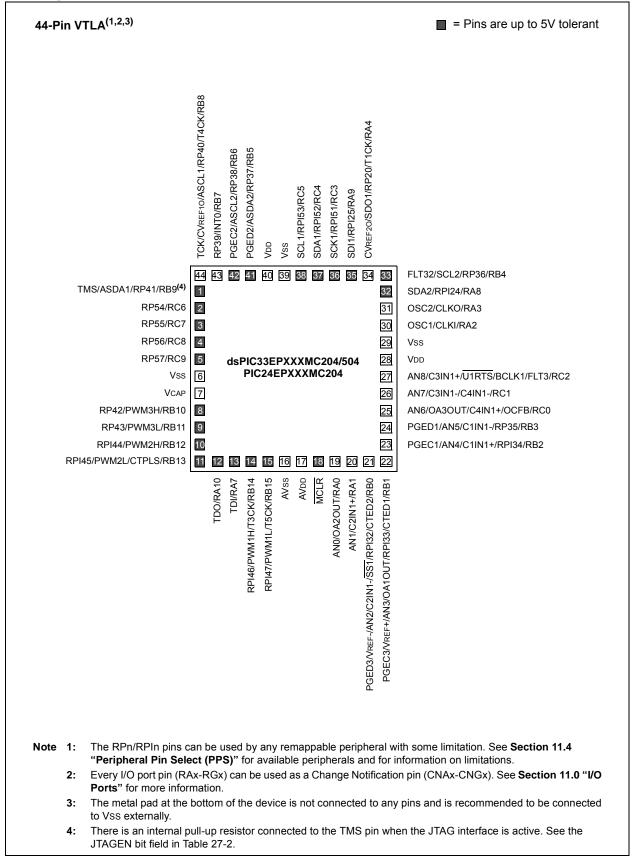

# Pin Diagrams (Continued)

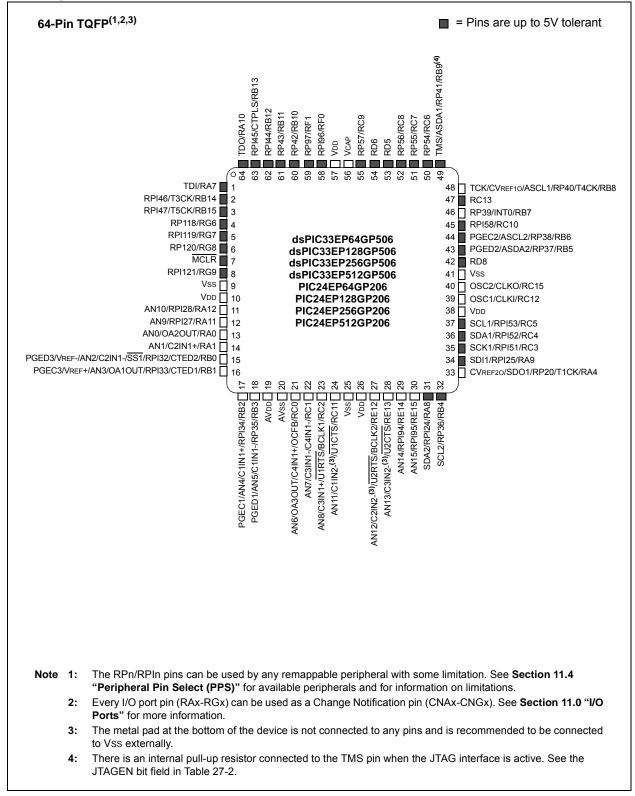

# **Pin Diagrams (Continued)**

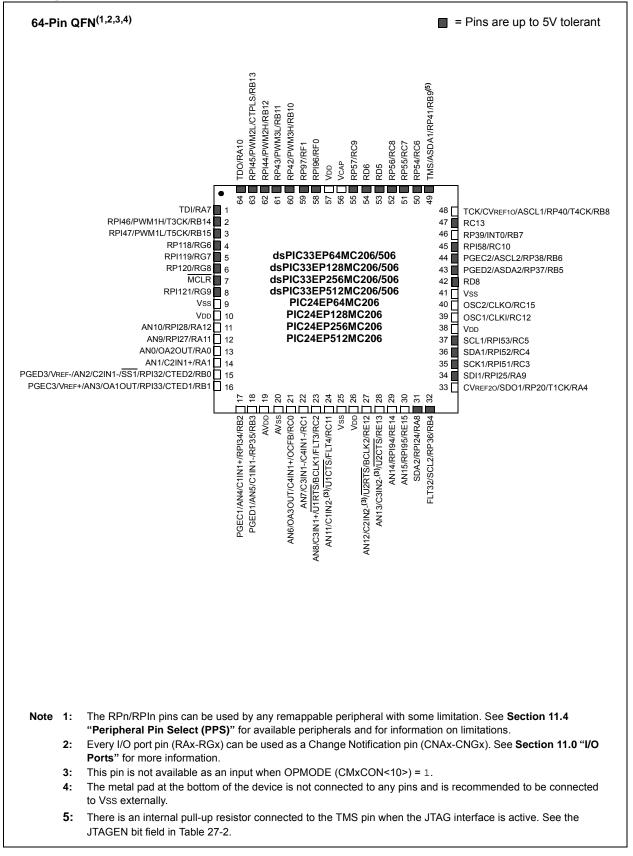

# Pin Diagrams (Continued)

### TABLE 4-53: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|---------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | _      | _      | _      | _      | TRISA10 | TRISA9 | TRISA8 | TRISA7 | -     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 079F          |

| PORTA        | 0E02  |        | _      | _      | -      | _      | RA10    | RA9    | RA8    | RA7    | -     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | LATA10  | LATA9  | LATA8  | LATA7  | -     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | —      | —      | _      |        | ODCA10  | ODCA9  | ODCA8  | ODCA7  | —     | —     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | —      | —      | _      |        | CNIEA10 | CNIEA9 | CNIEA8 | CNIEA7 | —     | —     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | —      | —      | _      |        | CNPUA10 | CNPUA9 | CNPUA8 | CNPUA7 | —     | —     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | —      | —      | _      |        | CNPDA10 | CNPDA9 | CNPDA8 | CNPDA7 | —     | —     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | _      | _      | —       | _      | —      | _      | _     | —     | ANSA4  | _      | _      | ANSA1  | ANSA0  | 0013          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-54: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | -       | -      | ANSB8  | _      | _      | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-55: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISC        | 0E20  | _      | _      | _      |        | —      | _      | TRISC9 | TRISC8 | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 03FF          |

| PORTC        | 0E22  | _      | _      | _      | _      | _      | —      | RC9    | RC8    | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xxxx          |

| LATC         | 0E24  | —      | —      | _      | _      |        | —      | LATC9  | LATC8  | LATC7  | LATC6  | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  | —      | —      | _      | _      |        | —      | ODCC9  | ODCC8  | ODCC7  | ODCC6  | ODCC5  | ODCC4  | ODCC3  | ODCC2  | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | —      | —      | _      | _      |        | —      | CNIEC9 | CNIEC8 | CNIEC7 | CNIEC6 | CNIEC5 | CNIEC4 | CNIEC3 | CNIEC2 | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  | —      | —      | _      | —      |        | —      | CNPUC9 | CNPUC8 | CNPUC7 | CNPUC6 | CNPUC5 | CNPUC4 | CNPUC3 | CNPUC2 | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  | —      | —      | _      | —      |        | —      | CNPDC9 | CNPDC8 | CNPDC7 | CNPDC6 | CNPDC5 | CNPDC4 | CNPDC3 | CNPDC2 | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | —      | —      | _      | _      |        | —      | _      |        |        |        | —      |        | _      | ANSC2  | ANSC1  | ANSC0  | 0007          |

Legend: x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2013 Microchip Technology Inc.

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configuring the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages, by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address prior to modification addresses an EDS or PSV page

- The EA calculation uses Pre-Modified or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-61 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

|             | -                   | SV SI ACE BOON |              |                        |                |              |                        |

|-------------|---------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|

| 0/11        |                     |                | Before       |                        |                | After        |                        |

| O/U,<br>R/W | Operation           | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page<br>Description    |

| O,<br>Read  |                     | DSRPAG = 0x1FF | 1            | EDS: Last page         | DSRPAG = 0x1FF | 0            | See Note 1             |

| O,<br>Read  | [++₩n]<br><b>or</b> | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page |

| O,<br>Read  | [Wn++]              | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0            | See Note 1             |

| O,<br>Write |                     | DSWPAG = 0x1FF | 1            | EDS: Last page         | DSWPAG = 0x1FF | 0            | See Note 1             |

| U,<br>Read  |                     | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0            | See Note 1             |

| U,<br>Read  | [Wn]<br>Or<br>[Wn]  | DSRPAG = 0x200 | 1            | PSV: First Isw<br>page | DSRPAG = 0x200 | 0            | See Note 1             |

| U,<br>Read  | [ //11 - ]          | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>page  |

# TABLE 4-61: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS and PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

Legend: O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

- **3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

- 4: Pseudo-Linear Addressing is not supported for large offsets.

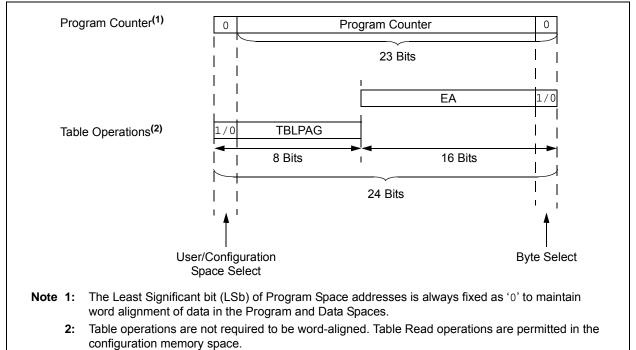

# 4.8 Interfacing Program and Data Memory Spaces

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture uses a 24-bit-wide Program Space (PS) and a 16-bit-wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

# TABLE 4-65: PROGRAM SPACE ADDRESS CONSTRUCTION

|                                                       | Access        | Program Space Address         |           |         |               |     |  |  |  |

|-------------------------------------------------------|---------------|-------------------------------|-----------|---------|---------------|-----|--|--|--|

| Access Type                                           | Space         | <23>                          | <22:16>   | <15>    | <14:1>        | <0> |  |  |  |

| Instruction Access User 0 PC<22:1>                    |               |                               |           |         |               |     |  |  |  |

| Code Execution) 0xx xxxx xxxx xxxx xxxx xxxx xxxx xxx |               |                               |           |         |               |     |  |  |  |

| TBLRD/TBLWT                                           | User          | TBLPAG<7:0> Data EA<15:0>     |           |         |               |     |  |  |  |

| (Byte/Word Read/Write)                                |               | 0xxx xxxx xxxx xxxx xxxx xxxx |           |         |               |     |  |  |  |

|                                                       | Configuration | TB                            | LPAG<7:0> |         | Data EA<15:0> |     |  |  |  |

|                                                       |               | 1                             | xxx xxxx  | XXXX XX |               |     |  |  |  |

# FIGURE 4-22: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

# 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs other than VDD by using external pull-up resistors. The maximum open-drain voltage allowed on any pin is the same as the maximum VIH specification for that particular pin.

See the **"Pin Diagrams"** section for the available 5V tolerant pins and Table 30-11 for the maximum VIH specification for each pin.

# 11.2 Configuring Analog and Digital Port Pins

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

Pins with analog functions affected by the ANSELx registers are listed with a buffer type of analog in the Pinout I/O Descriptions (see Table 1-1).

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or comparator module.

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

# 11.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP, as shown in Example 11-1.

# **11.3** Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State.

Three control registers are associated with the Change Notification (CN) functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups and pulldowns act as a current source or sink source connected to the pin and eliminate the need for external resistors when push button, or keypad devices are connected. The pull-ups and pull-downs are enabled separately, using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

| Note: | Pull-ups and pull-downs on Change Noti-      |

|-------|----------------------------------------------|

|       | fication pins should always be disabled      |

|       | when the port pin is configured as a digital |

|       | output.                                      |

### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, WO | ; Configure PORTB<15:8> |

|------|------------|-------------------------|

|      |            | ; as inputs             |

| MOV  | W0, TRISB  | ; and PORTB<7:0>        |

|      |            | ; as outputs            |

| NOP  |            | ; Delay 1 cycle         |

| BTSS | PORTB, #13 | ; Next Instruction      |

|      |            |                         |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0        | R/W-0                               | R/W-0 | R/W-0                    | R/W-0            | R/W-0           | R/W-0 |

|-----------------|------------|-------------------------------------|-------|--------------------------|------------------|-----------------|-------|

| —               | —          |                                     |       | RP57                     | R<5:0>           |                 |       |

| bit 15          |            |                                     |       |                          |                  |                 | bit 8 |

|                 |            |                                     |       |                          |                  |                 |       |

| U-0             | U-0        | R/W-0                               | R/W-0 | R/W-0                    | R/W-0            | R/W-0           | R/W-0 |

| _               | —          |                                     |       | RP56                     | R<5:0>           |                 |       |

| bit 7           |            |                                     |       |                          |                  |                 | bit 0 |

|                 |            |                                     |       |                          |                  |                 |       |

| Legend:         |            |                                     |       |                          |                  |                 |       |

| R = Readable I  | bit        | W = Writable                        | bit   | U = Unimplen             | nented bit, read | d as '0'        |       |

| -n = Value at P | OR         | '1' = Bit is set                    | :     | '0' = Bit is clea        | ared             | x = Bit is unkr | iown  |

|                 |            |                                     |       |                          |                  |                 |       |

| bit 15-14       | Unimplemen | ted: Read as '                      | 0'    |                          |                  |                 |       |

| bit 13-8        |            | : Peripheral Ou<br>-3 for periphera |       | is Assigned to<br>mbers) | RP57 Output F    | Pin bits        |       |

| bit 7-6         | Unimplemen | ted: Read as '                      | 0'    |                          |                  |                 |       |

# REGISTER 11-24: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| (see Table 11-3 for peripheral function numbers) |

|--------------------------------------------------|

|                                                  |

# REGISTER 11-25: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP97  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

RP56R<5:0>: Peripheral Output Function is Assigned to RP56 Output Pin bits

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   |     | —   | —   |     | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP97R<5:0>:** Peripheral Output Function is Assigned to RP97 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-0 Unimplemented: Read as '0'

bit 5-0

| REGISTE       | R 16-7: PWMC                                                                        | CONX: PWMX (                                                                                | CONTROL R      | EGISTER          |                      |                      |                     |  |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------|------------------|----------------------|----------------------|---------------------|--|--|--|--|--|

| HS/HC-        | 0 HS/HC-0                                                                           | HS/HC-0                                                                                     | R/W-0          | R/W-0            | R/W-0                | R/W-0                | R/W-0               |  |  |  |  |  |

| FLTSTAT       | -(1) CLSTAT <sup>(1)</sup>                                                          | TRGSTAT                                                                                     | FLTIEN         | CLIEN            | TRGIEN               | ITB <sup>(2)</sup>   | MDCS <sup>(2)</sup> |  |  |  |  |  |

| bit 15        | ·                                                                                   | •                                                                                           |                | ÷                |                      |                      | bit                 |  |  |  |  |  |

| R/W-0         | R/W-0                                                                               | R/W-0                                                                                       | U-0            | R/W-0            | R/W-0                | R/W-0                | R/W-0               |  |  |  |  |  |

| DTC1          |                                                                                     | DTCP <sup>(3)</sup>                                                                         | 0-0            | MTBS             | CAM <sup>(2,4)</sup> | XPRES <sup>(5)</sup> | IUE <sup>(2)</sup>  |  |  |  |  |  |

| bit 7         | DICO                                                                                | DICE                                                                                        | _              | INT DO           | CAIM                 | AFRES'               | bit                 |  |  |  |  |  |

|               |                                                                                     |                                                                                             |                |                  |                      |                      | <u> </u>            |  |  |  |  |  |

| Legend:       |                                                                                     | HC = Hardware                                                                               | Clearable bit  | HS = Hardwa      | are Settable bit     |                      |                     |  |  |  |  |  |

| R = Reada     | able bit                                                                            | W = Writable bi                                                                             | t              | U = Unimple      | mented bit, rea      | ıd as '0'            |                     |  |  |  |  |  |

| -n = Value    | at POR                                                                              | '1' = Bit is set                                                                            |                | '0' = Bit is cle | eared                | x = Bit is unk       | nown                |  |  |  |  |  |

| bit 15        | ELTSTAT: ES                                                                         | ult Intorrunt Stati                                                                         | is hit(1)      |                  |                      |                      |                     |  |  |  |  |  |

| DIL 15        |                                                                                     | <b>FLTSTAT:</b> Fault Interrupt Status bit <sup>(1)</sup><br>1 = Fault interrupt is pending |                |                  |                      |                      |                     |  |  |  |  |  |

|               |                                                                                     | interrupt is pendi                                                                          | ng             |                  |                      |                      |                     |  |  |  |  |  |

|               |                                                                                     | ared by setting F                                                                           |                |                  |                      |                      |                     |  |  |  |  |  |

| bit 14        |                                                                                     | rent-Limit Interru                                                                          | •              |                  |                      |                      |                     |  |  |  |  |  |

|               | 1 = Current-limit interrupt is pending<br>0 = No current-limit interrupt is pending |                                                                                             |                |                  |                      |                      |                     |  |  |  |  |  |

|               |                                                                                     | This bit is cleared by setting CLIEN = $0$ .                                                |                |                  |                      |                      |                     |  |  |  |  |  |

| bit 13        |                                                                                     | igger Interrupt S                                                                           |                |                  |                      |                      |                     |  |  |  |  |  |

|               | 1 = Trigger interrupt is pending                                                    |                                                                                             |                |                  |                      |                      |                     |  |  |  |  |  |

|               | 0 = No trigger interrupt is pending<br>This bit is cleared by setting TRGIEN = 0.   |                                                                                             |                |                  |                      |                      |                     |  |  |  |  |  |

|               |                                                                                     |                                                                                             |                |                  |                      |                      |                     |  |  |  |  |  |

| bit 12        |                                                                                     | t Interrupt Enable                                                                          | e bit          |                  |                      |                      |                     |  |  |  |  |  |

|               |                                                                                     | rrupt is enabled rrupt is disabled                                                          | and the FLTS   | TAT bit is clear | ed                   |                      |                     |  |  |  |  |  |

| bit 11        |                                                                                     | -                                                                                           |                |                  | cu .                 |                      |                     |  |  |  |  |  |

|               | CLIEN: Current-Limit Interrupt Enable bit<br>1 = Current-limit interrupt is enabled |                                                                                             |                |                  |                      |                      |                     |  |  |  |  |  |

|               |                                                                                     | mit interrupt is di                                                                         |                | e CLSTAT bit is  | s cleared            |                      |                     |  |  |  |  |  |

| bit 10        | TRGIEN: Trig                                                                        | ger Interrupt En                                                                            | able bit       |                  |                      |                      |                     |  |  |  |  |  |

|               |                                                                                     | event generates                                                                             |                |                  | T hit is cleared     |                      |                     |  |  |  |  |  |

| bit 9         |                                                                                     | vent interrupts ar<br>dent Time Base I                                                      |                |                  | i bit is cleared     |                      |                     |  |  |  |  |  |

| DIL 9         |                                                                                     | register provides                                                                           |                | riad for this PM | VM generator         |                      |                     |  |  |  |  |  |

|               |                                                                                     | egister provides f                                                                          | •              |                  | •                    |                      |                     |  |  |  |  |  |

| bit 8         |                                                                                     | er Duty Cycle Re                                                                            |                |                  |                      |                      |                     |  |  |  |  |  |

|               |                                                                                     | ister provides du<br>jister provides du                                                     |                |                  |                      | r                    |                     |  |  |  |  |  |

| Note 1:       | Software must clea                                                                  |                                                                                             |                |                  | -                    |                      | t controller        |  |  |  |  |  |

| Note 1.<br>2: | These bits should                                                                   | -                                                                                           |                | -                | -                    | the interrup         |                     |  |  |  |  |  |

| 3:            | DTC<1:0> = 11 fo                                                                    | -                                                                                           |                | -                | -                    |                      |                     |  |  |  |  |  |

| 4:            | The Independent T<br>CAM bit is ignored                                             | Time Base (ITB =                                                                            |                | •                |                      | igned mode. If       | TTB = 0, the        |  |  |  |  |  |

| 5:            | To operate in Exter                                                                 |                                                                                             | t mode, the IT | B bit must be '  | 1' and the CLM       | 10D bit in the I     | FCLCONx             |  |  |  |  |  |

# REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER

5: To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

#### 18.3 SPIx Control Registers

#### R/W-0 U-0 R/W-0 U-0 R/W-0 R/W-0 R/W-0 U-0 SPIEN SPISIDL SPIBEC<2:0> \_\_\_\_\_ bit 15 R/W-0 R/W-0 R/W-0 R/C-0, HS R/W-0 R/W-0 R-0, HS, HC R-0, HS, HC SRMPT SPIROV SRXMPT SISEL2 SISEL1 SISEL0 SPITBF SPIRBF bit 7 Legend: C = Clearable bit HS = Hardware Settable bit HC = Hardware Clearable bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 SPIEN: SPIx Enable bit 1 = Enables the module and configures SCKx, SDOx, SDIx and $\overline{SSx}$ as serial port pins 0 = Disables the module bit 14 Unimplemented: Read as '0' bit 13 SPISIDL: SPIx Stop in Idle Mode bit 1 = Discontinues the module operation when device enters Idle mode 0 = Continues the module operation in Idle mode bit 12-11 Unimplemented: Read as '0' bit 10-8 SPIBEC<2:0>: SPIx Buffer Element Count bits (valid in Enhanced Buffer mode) Master mode: Number of SPIx transfers that are pending. Slave mode: Number of SPIx transfers that are unread. SRMPT: SPIx Shift Register (SPIxSR) Empty bit (valid in Enhanced Buffer mode) bit 7 1 = SPIx Shift register is empty and Ready-To-Send or receive the data 0 = SPIx Shift register is not empty bit 6 SPIROV: SPIx Receive Overflow Flag bit

#### REGISTER 18-1: SPIxSTAT: SPIx STATUS AND CONTROL REGISTER

1 = A new byte/word is completely received and discarded; the user application has not read the previous data in the SPIxBUF register 0 = No overflow has occurred SRXMPT: SPIx Receive FIFO Empty bit (valid in Enhanced Buffer mode)

- 1 = RX FIFO is empty

- 0 = RX FIFO is not empty

#### bit 4-2 SISEL<2:0>: SPIx Buffer Interrupt Mode bits (valid in Enhanced Buffer mode)

- 111 = Interrupt when the SPIx transmit buffer is full (SPITBF bit is set)

- 110 = Interrupt when last bit is shifted into SPIxSR and as a result, the TX FIFO is empty

- 101 = Interrupt when the last bit is shifted out of SPIxSR and the transmit is complete

- 100 = Interrupt when one data is shifted into the SPIxSR and as a result, the TX FIFO has one open memory location

- 011 = Interrupt when the SPIx receive buffer is full (SPIRBF bit is set)

- 010 = Interrupt when the SPIx receive buffer is 3/4 or more full

- 001 = Interrupt when data is available in the receive buffer (SRMPT bit is set)

- 000 = Interrupt when the last data in the receive buffer is read and as a result, the buffer is empty (SRXMPT bit is set)

bit 5

bit 8

bit 0

| R/W-0         | R/W-0                                                                         | R/W-0                                                                                                               | R/W-0        | R/W-0             | R/W-0           | R/W-0           | R/W-0    |  |  |  |  |  |

|---------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------|-------------------|-----------------|-----------------|----------|--|--|--|--|--|

| EDG1MOD       | EDG1POL                                                                       | EDG1SEL3                                                                                                            | EDG1SEL2     | EDG1SEL1          | EDG1SEL0        | EDG2STAT        | EDG1STAT |  |  |  |  |  |

| bit 15        |                                                                               | 1                                                                                                                   |              | 11                |                 |                 | bit 8    |  |  |  |  |  |

|               |                                                                               |                                                                                                                     |              |                   |                 |                 |          |  |  |  |  |  |

| R/W-0         | R/W-0                                                                         | R/W-0                                                                                                               | R/W-0        | R/W-0             | R/W-0           | U-0             | U-0      |  |  |  |  |  |

| EDG2MOD       | EDG2POL                                                                       | EDG2SEL3                                                                                                            | EDG2SEL2     | EDG2SEL1          | EDG2SEL0        | —               | _        |  |  |  |  |  |

| bit 7         |                                                                               |                                                                                                                     |              | 1 1               |                 | 1               | bit (    |  |  |  |  |  |

|               |                                                                               |                                                                                                                     |              |                   |                 |                 |          |  |  |  |  |  |

| Legend:       |                                                                               |                                                                                                                     |              |                   |                 |                 |          |  |  |  |  |  |

| R = Readabl   | le bit                                                                        | W = Writable                                                                                                        | oit          | U = Unimplem      | ented bit, read | l as '0'        |          |  |  |  |  |  |

| -n = Value at | POR                                                                           | '1' = Bit is set                                                                                                    |              | '0' = Bit is clea | red             | x = Bit is unkr | nown     |  |  |  |  |  |

|               |                                                                               |                                                                                                                     |              |                   |                 |                 |          |  |  |  |  |  |

| bit 15        | EDG1MOD: E                                                                    | Edge 1 Edge Sa                                                                                                      | ampling Mode | Selection bit     |                 |                 |          |  |  |  |  |  |

|               | 1 = Edge 1 is edge-sensitive                                                  |                                                                                                                     |              |                   |                 |                 |          |  |  |  |  |  |

|               | •                                                                             | 0 = Edge 1 is level-sensitive                                                                                       |              |                   |                 |                 |          |  |  |  |  |  |

| bit 14        |                                                                               | dge 1 Polarity                                                                                                      |              |                   |                 |                 |          |  |  |  |  |  |

|               | 1 = Edge 1 is programmed for a positive edge response                         |                                                                                                                     |              |                   |                 |                 |          |  |  |  |  |  |

| L:1 40 40     | 0 = Edge 1 is programmed for a negative edge response                         |                                                                                                                     |              |                   |                 |                 |          |  |  |  |  |  |

| bit 13-10     | EDG1SEL<3:0>: Edge 1 Source Select bits<br>1xxx = Reserved                    |                                                                                                                     |              |                   |                 |                 |          |  |  |  |  |  |

|               | 01xx = Reserved                                                               |                                                                                                                     |              |                   |                 |                 |          |  |  |  |  |  |

|               | 0011 = CTEE                                                                   |                                                                                                                     |              |                   |                 |                 |          |  |  |  |  |  |

|               | 0010 = CTEE                                                                   | •                                                                                                                   |              |                   |                 |                 |          |  |  |  |  |  |

|               | 0001 = OC1                                                                    |                                                                                                                     |              |                   |                 |                 |          |  |  |  |  |  |

| hit O         | 0000 = Timer                                                                  |                                                                                                                     | :+           |                   |                 |                 |          |  |  |  |  |  |

| bit 9         |                                                                               | <b>EDG2STAT:</b> Edge 2 Status bit<br>Indicates the status of Edge 2 and can be written to control the edge source. |              |                   |                 |                 |          |  |  |  |  |  |

|               | 1 = Edge 2 has occurred                                                       |                                                                                                                     |              |                   |                 |                 |          |  |  |  |  |  |

|               |                                                                               | as not occurred                                                                                                     | ł            |                   |                 |                 |          |  |  |  |  |  |

| bit 8         | EDG1STAT: Edge 1 Status bit                                                   |                                                                                                                     |              |                   |                 |                 |          |  |  |  |  |  |

|               | Indicates the status of Edge 1 and can be written to control the edge source. |                                                                                                                     |              |                   |                 |                 |          |  |  |  |  |  |

|               | 1 = Edge 1 h                                                                  |                                                                                                                     |              |                   |                 |                 |          |  |  |  |  |  |

|               | -                                                                             | <ul> <li>0 = Edge 1 has not occurred</li> <li>EDG2MOD: Edge 2 Edge Sampling Mode Selection bit</li> </ul>           |              |                   |                 |                 |          |  |  |  |  |  |

| bit 7         |                                                                               | • •                                                                                                                 |              | Selection bit     |                 |                 |          |  |  |  |  |  |

|               |                                                                               | s edge-sensitive<br>s level-sensitive                                                                               |              |                   |                 |                 |          |  |  |  |  |  |

| bit 6         | •                                                                             | dge 2 Polarity                                                                                                      |              |                   |                 |                 |          |  |  |  |  |  |

| Sit 0         |                                                                               | s programmed f                                                                                                      |              | dae response      |                 |                 |          |  |  |  |  |  |

|               |                                                                               | s programmed f                                                                                                      |              |                   |                 |                 |          |  |  |  |  |  |

| bit 5-2       | EDG2SEL<3:0>: Edge 2 Source Select bits                                       |                                                                                                                     |              |                   |                 |                 |          |  |  |  |  |  |

|               | 1111 = Reserved                                                               |                                                                                                                     |              |                   |                 |                 |          |  |  |  |  |  |

|               | 01xx = Reserved                                                               |                                                                                                                     |              |                   |                 |                 |          |  |  |  |  |  |

|               | 0100 = CMP <sup>2</sup><br>0011 = CTEE                                        |                                                                                                                     |              |                   |                 |                 |          |  |  |  |  |  |

|               | 0010 = CTEE                                                                   |                                                                                                                     |              |                   |                 |                 |          |  |  |  |  |  |

|               |                                                                               | Ji pili                                                                                                             |              |                   |                 |                 |          |  |  |  |  |  |

|               | 0001 = OC1                                                                    | module                                                                                                              |              |                   |                 |                 |          |  |  |  |  |  |

|               |                                                                               | module                                                                                                              |              |                   |                 |                 |          |  |  |  |  |  |

# REGISTER 22-2: CTMUCON2: CTMU CONTROL REGISTER 2

# REGISTER 25-1: CMSTAT: OP AMP/COMPARATOR STATUS REGISTER (CONTINUED)

- C2OUT: Comparator 2 Output Status bit<sup>(2)</sup> bit 1 When CPOL = 0: 1 = VIN + > VIN -0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -C10UT: Comparator 1 Output Status bit<sup>(2)</sup> bit 0 When CPOL = 0: 1 = VIN + > VIN-0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -

- **Note 1:** Reflects the value of the of the CEVT bit in the respective Op Amp/Comparator Control register, CMxCON<9>.

- 2: Reflects the value of the COUT bit in the respective Op Amp/Comparator Control register, CMxCON<8>.

| R/W-0         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0                           | U-0                 | U-0              | R/W-0            | R/W-0               | R/W-0               |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------|------------------|------------------|---------------------|---------------------|--|--|--|--|--|

| CON           | COE <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CPOL                            | _                   | —                | OPMODE           | CEVT                | COUT                |  |  |  |  |  |

| bit 15        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                 |                     |                  |                  |                     | bit 8               |  |  |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                 |                     |                  |                  |                     |                     |  |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U-0                             | R/W-0               | U-0              | U-0              | R/W-0               | R/W-0               |  |  |  |  |  |

| EVPOL1        | EVPOL0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | —                               | CREF <sup>(1)</sup> | _                | —                | CCH1 <sup>(1)</sup> | CCH0 <sup>(1)</sup> |  |  |  |  |  |

| bit 7         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                 |                     |                  |                  |                     | bit (               |  |  |  |  |  |

| Legend:       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                 |                     |                  |                  |                     |                     |  |  |  |  |  |

| R = Readabl   | e bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | W = Writable                    | bit                 | U = Unimple      | mented bit, read | as '0'              |                     |  |  |  |  |  |