Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 8K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128mc206t-e-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| R/W-0               | U-0                          | R/W-0                                                    | R/W-0                   | R/W-0                       | R-0                       | R-0                | R-0                |

|---------------------|------------------------------|----------------------------------------------------------|-------------------------|-----------------------------|---------------------------|--------------------|--------------------|

| VAR                 | —                            | US1 <sup>(1)</sup>                                       | US0 <sup>(1)</sup>      | EDT <sup>(1,2)</sup>        | DL2 <sup>(1)</sup>        | DL1 <sup>(1)</sup> | DL0 <sup>(1)</sup> |

| bit 15              |                              |                                                          |                         |                             |                           |                    | bit                |

| R/W-0               | R/W-0                        | R/W-1                                                    | R/W-0                   | R/C-0                       | R-0                       | R/W-0              | R/W-0              |

| SATA <sup>(1)</sup> | SATB <sup>(1)</sup>          | SATDW <sup>(1)</sup>                                     | ACCSAT <sup>(1)</sup>   | IPL3(3)                     | SFA                       | RND <sup>(1)</sup> | IF(1)              |

| bit 7               | I                            |                                                          |                         |                             | I                         | 1                  | bit                |

| Legend:             |                              | C = Clearable                                            | e bit                   |                             |                           |                    |                    |

| R = Readabl         | e bit                        | W = Writable                                             | bit                     | U = Unimpler                | mented bit, read          | d as '0'           |                    |

| -n = Value at       | POR                          | '1' = Bit is set                                         | t                       | '0' = Bit is cle            | ared                      | x = Bit is unkr    | nown               |

| bit 15              | 1 = Variable                 | le Exception Pro<br>exception proce                      | essing latency          | is enabled                  |                           |                    |                    |

| bit 14              |                              | nted: Read as '                                          |                         |                             |                           |                    |                    |

| bit 13-12           | -                            | SP Multiply Uns                                          |                         | Control bits <sup>(1)</sup> |                           |                    |                    |

|                     | 01 = DSP er<br>00 = DSP er   | ngine multiplies<br>ngine multiplies<br>ngine multiplies | are unsigned are signed |                             |                           |                    |                    |

| bit 11              | •                            | O Loop Terminatives executing Dot<br>t                   |                         |                             | iteration                 |                    |                    |

| bit 10-8            |                              | Loop Nesting<br>oops are active                          |                         | (1)                         |                           |                    |                    |

|                     | •                            |                                                          |                         |                             |                           |                    |                    |

|                     | •                            |                                                          |                         |                             |                           |                    |                    |

|                     | 001 = 1 DO k<br>000 = 0 DO k | oop is active<br>oops are active                         |                         |                             |                           |                    |                    |

| bit 7               | SATA: ACCA                   | A Saturation En                                          | able bit <sup>(1)</sup> |                             |                           |                    |                    |

|                     |                              | ator A saturatio<br>ator A saturatio                     |                         |                             |                           |                    |                    |

| bit 6               | SATB: ACCE                   | B Saturation En                                          | able bit <sup>(1)</sup> |                             |                           |                    |                    |

|                     |                              | ator B saturatio<br>ator B saturatio                     |                         |                             |                           |                    |                    |

| bit 5               | SATDW: Dat                   | ta Space Write                                           | from DSP Engi           | ne Saturation               | Enable bit <sup>(1)</sup> |                    |                    |

|                     |                              | ace write satura<br>ace write satura                     |                         | I                           |                           |                    |                    |

| bit 4               |                              | cumulator Satu                                           |                         | elect bit <sup>(1)</sup>    |                           |                    |                    |

|                     |                              | uration (super s<br>uration (normal                      | ,                       |                             |                           |                    |                    |

| bit 3               |                              | nterrupt Priority                                        |                         |                             |                           |                    |                    |

|                     |                              | errupt Priority Le<br>errupt Priority Le                 |                         |                             |                           |                    |                    |

|                     | nis bit is availabl          |                                                          | PXXXMC20X/              | 50X and dsPl                | C33EPXXXGP                | 50X devices on     | ly.                |

| 2: Th               | nis bit is always            | reau as 0.                                               |                         |                             |                           |                    |                    |

## REGISTER 3-2: CORCON: CORE CONTROL REGISTER

**3:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

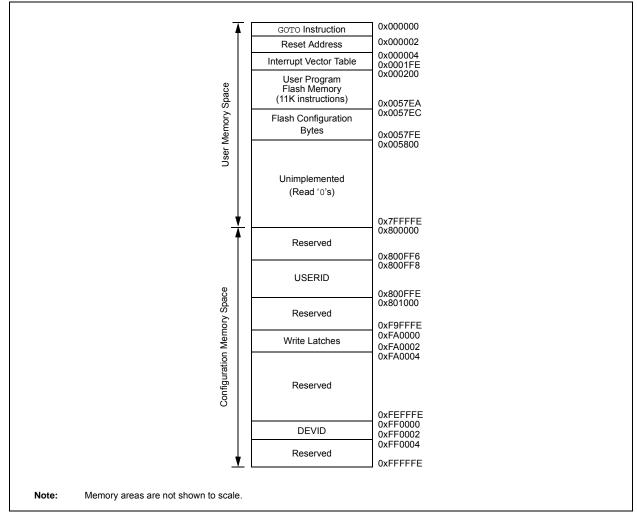

## 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Program Memory" (DS70613) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture features separate program and data memory spaces, and buses. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

#### 4.1 Program Address Space

The program address memory space of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit PC during program execution, or from table operation or Data Space remapping, as described in Section 4.8 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFF). The exception is the use of TBLRD operations, which use TBLPAG<7> to read Device ID sections of the configuration memory space.

The program memory maps, which are presented by device family and memory size, are shown in Figure 4-1 through Figure 4-5.

# FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33EP32GP50X, dsPIC33EP32MC20X/50X AND PIC24EP32GP/MC20X DEVICES

| TABLE 4         | -16:  | QEI1   | QEI1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY                                            |                                                                   |        |        |        |       |             |       |       |       |       |       |       |       |       |               |

|-----------------|-------|--------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------|--------|--------|-------|-------------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| File Name       | Addr. | Bit 15 | Bit 14                                                                                                                  | Bit 13                                                            | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8       | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| QEI1CON         | 01C0  | QEIEN  | —                                                                                                                       | - QEISIDL PIMOD<2:0> IMV<1:0> — INTDIV<2:0> CNTPOL GATEN CCM<1:0> |        |        |        |       |             |       | 0000  |       |       |       |       |       |       |               |

| QEI1IOC         | 01C2  | QCAPEN | IN FLTREN QFDIV<2:0> OUTFNC<1:0> SWPAB HOMPOL IDXPOL QEBPOL QEAPOL HOME INDEX QEB QEA 0                                 |                                                                   |        |        |        |       |             | 000x  |       |       |       |       |       |       |       |               |

| <b>QEI1STAT</b> | 01C4  | _      | - PCHEQIRQ PCHEQIEN PCLEQIRQ PCLEQIEN POSOVIRQ POSOVIEN PCIIRQ PCIIEN VELOVIRQ VELOVIEN HOMIRQ HOMIEN IDXIRQ IDXIEN 000 |                                                                   |        |        |        |       |             |       | 0000  |       |       |       |       |       |       |               |

| POS1CNTL        | 01C6  |        | POSCNT<15:0> 000                                                                                                        |                                                                   |        |        |        |       |             |       |       |       | 0000  |       |       |       |       |               |

| POS1CNTH        | 01C8  |        |                                                                                                                         |                                                                   |        |        |        | ł     | POSCNT<31:  | 16>   |       |       |       |       |       |       |       | 0000          |

| POS1HLD         | 01CA  |        |                                                                                                                         |                                                                   |        |        |        |       | POSHLD<15   | 0>    |       |       |       |       |       |       |       | 0000          |

| VEL1CNT         | 01CC  |        |                                                                                                                         |                                                                   |        |        |        |       | VELCNT<15   | 0>    |       |       |       |       |       |       |       | 0000          |

| INT1TMRL        | 01CE  |        | INTTMR<15:0> 0000                                                                                                       |                                                                   |        |        |        |       |             |       |       | 0000  |       |       |       |       |       |               |

| INT1TMRH        | 01D0  |        | INTTMR<31:16> 000                                                                                                       |                                                                   |        |        |        |       |             |       |       | 0000  |       |       |       |       |       |               |

| INT1HLDL        | 01D2  |        |                                                                                                                         |                                                                   |        |        |        |       | INTHLD<15:  | )>    |       |       |       |       |       |       |       | 0000          |

| INT1HLDH        | 01D4  |        |                                                                                                                         |                                                                   |        |        |        |       | INTHLD<31:1 | 6>    |       |       |       |       |       |       |       | 0000          |

| INDX1CNTL       | 01D6  |        |                                                                                                                         |                                                                   |        |        |        |       | INDXCNT<15  | :0>   |       |       |       |       |       |       |       | 0000          |

| INDX1CNTH       | 01D8  |        |                                                                                                                         |                                                                   |        |        |        |       | NDXCNT<31:  | 16>   |       |       |       |       |       |       |       | 0000          |

| INDX1HLD        | 01DA  |        |                                                                                                                         |                                                                   |        |        |        |       | INDXHLD<15  | :0>   |       |       |       |       |       |       |       | 0000          |

| QEI1GECL        | 01DC  |        |                                                                                                                         |                                                                   |        |        |        |       | QEIGEC<15   | 0>    |       |       |       |       |       |       |       | 0000          |

| <b>QEI1ICL</b>  | 01DC  |        | QEIIC<15:0> 000                                                                                                         |                                                                   |        |        |        |       |             |       | 0000  |       |       |       |       |       |       |               |

| QEI1GECH        | 01DE  |        | QEIGEC<31:16> 000                                                                                                       |                                                                   |        |        |        |       |             |       | 0000  |       |       |       |       |       |       |               |

| QEI1ICH         | 01DE  |        | QEIIC<31:16> 001                                                                                                        |                                                                   |        |        |        |       |             |       | 0000  |       |       |       |       |       |       |               |

| QEI1LECL        | 01E0  |        | QEILEC<15:0> 000                                                                                                        |                                                                   |        |        |        |       |             |       | 0000  |       |       |       |       |       |       |               |

| <b>QEI1LECH</b> | 01E2  |        | QEILEC<31:16> 0000                                                                                                      |                                                                   |        |        |        |       |             |       | 0000  |       |       |       |       |       |       |               |

TABLE 4-16: QEI1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-56: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | _      | _      | _      |        | _      | _     | TRISA8 | _     | —     | —     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 011F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     | RA8    | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     | LATA8  | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     | ODCA8  | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     | CNIEA8 | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     | CNPUA8 | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     | CNPDA8 | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | —      | _      | —      | _     | —      | _     | —     | —     | ANSA4  | —      | —      | ANSA1  | ANSA0  | 0013          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-57: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | -       | _       | -       | —       | -      | ANSB8  | _      | _      | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-58: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|-------|-------|-------|--------|--------|---------------|

| TRISC        | 0E20  | _      | _      | _      | _      | _      | —      | —     | TRISC8 | _     | -     |       | _     |       | -     | TRISC1 | TRISC0 | 0103          |

| PORTC        | 0E22  |        |        | -      | -      |        | —      | _     | RC8    | —     | -     |       | _     |       |       | RC1    | RC0    | xxxx          |

| LATC         | 0E24  |        |        | _      | _      | _      | _      | _     | LATC8  | _     | _     | _     | _     | _     | _     | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  |        |        | _      | _      | _      | _      | _     | ODCC8  | _     | _     | _     | _     | _     | _     | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | —      | _      | -      | _      |        | _      | _     | CNIEC8 | —     |       |       | _     |       |       | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  |        |        | _      | _      | _      | _      | _     | CNPUC8 | _     | _     | _     | _     | _     | _     | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  |        |        | _      | _      | _      | _      | _     | CNPDC8 | _     | _     | _     | _     | _     | _     | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | -      | _      | _      | _      | _      | —      | —     | _      | —     |       | _     | _     | _     |       | ANSC1  | ANSC0  | 0003          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| REGISTER 7-5: | INTCON3: INTERRUPT CONTROL REGISTER 3 |

|---------------|---------------------------------------|

| U-0          | U-0                                          | U-0                                          | U-0             | U-0              | U-0              | U-0                | U-0   |  |  |  |  |  |

|--------------|----------------------------------------------|----------------------------------------------|-----------------|------------------|------------------|--------------------|-------|--|--|--|--|--|

|              | —                                            | _                                            | —               | —                | —                | —                  | _     |  |  |  |  |  |

| bit 15       |                                              |                                              |                 |                  |                  | •                  | bit 8 |  |  |  |  |  |

|              |                                              |                                              |                 |                  |                  |                    |       |  |  |  |  |  |

| U-0          | U-0                                          | R/W-0                                        | R/W-0           | U-0              | U-0              | U-0                | U-0   |  |  |  |  |  |

| —            | —                                            | DAE                                          | DOOVR           | —                | —                | —                  | —     |  |  |  |  |  |

| bit 7        |                                              |                                              |                 |                  |                  |                    | bit 0 |  |  |  |  |  |

|              |                                              |                                              |                 |                  |                  |                    |       |  |  |  |  |  |

| Legend:      |                                              |                                              |                 |                  |                  |                    |       |  |  |  |  |  |

| R = Readab   | le bit                                       | W = Writable                                 | bit             | U = Unimplei     | mented bit, read | as '0'             |       |  |  |  |  |  |

| -n = Value a | It POR                                       | '1' = Bit is se                              | t               | '0' = Bit is cle | eared            | x = Bit is unknown |       |  |  |  |  |  |

|              |                                              |                                              |                 |                  |                  |                    |       |  |  |  |  |  |

| bit 15-6     | Unimplemen                                   | ted: Read as                                 | '0'             |                  |                  |                    |       |  |  |  |  |  |

| bit 5        | DAE: DMA A                                   | DAE: DMA Address Error Soft Trap Status bit  |                 |                  |                  |                    |       |  |  |  |  |  |

|              | 1 = DMA address error soft trap has occurred |                                              |                 |                  |                  |                    |       |  |  |  |  |  |

|              | 0 = DMA add                                  | ress error soft                              | trap has not o  | ccurred          |                  |                    |       |  |  |  |  |  |

| bit 4        | DOOVR: DO                                    | Stack Overflov                               | v Soft Trap Sta | tus bit          |                  |                    |       |  |  |  |  |  |

|              | 1 = DO stack                                 | 1 = DO stack overflow soft trap has occurred |                 |                  |                  |                    |       |  |  |  |  |  |

| I = D0 | Stack Overnow  | 3011 11 ap 11 a3 | occurred     |

|--------|----------------|------------------|--------------|

| 0 = DO | stack overflow | soft trap has    | not occurred |

| bit 3-0 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

#### REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|-----|-----|-----|-----|-----|-----|-------|

| —       | —   | —   | —   | —   | —   | —   | —     |

| bit 15  |     |     |     |     | •   |     | bit 8 |

|         |     |     |     |     |     |     |       |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

| _       | _   | —   |     | —   | —   | —   | SGHT  |

| bit 7   |     |     |     |     | •   |     | bit 0 |

|         |     |     |     |     |     |     |       |

| Legend: |     |     |     |     |     |     |       |

| 3                 |                               |                      |                    |

|-------------------|-------------------------------|----------------------|--------------------|

| R = Readable bit  | Readable bit W = Writable bit |                      | read as '0'        |

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown |

|                   |                               |                      |                    |

bit 0

SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

| Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment          | Peripheral Pir<br>Select Input<br>Register Value |     | Pin Assignment |

|--------------------------------------------------|------------------|-------------------------|--------------------------------------------------|-----|----------------|

| 000 0000                                         | I                | Vss                     | 010 1101                                         |     | RPI45          |

| 000 0001                                         | I                | C1OUT <sup>(1)</sup>    | 010 1110                                         | I   | RPI46          |

| 000 0010                                         | I                | C2OUT <sup>(1)</sup>    | 010 1111                                         | I   | RPI47          |

| 000 0011                                         | I                | C3OUT <sup>(1)</sup>    | 011 0000                                         | _   | _              |

| 000 0100                                         | I                | C4OUT <sup>(1)</sup>    | 011 0001                                         |     | _              |

| 000 0101                                         | —                | _                       | 011 0010                                         | _   | _              |

| 000 0110                                         | I                | PTGO30 <sup>(1)</sup>   | 011 0011                                         | I   | RPI51          |

| 000 0111                                         | I                | PTGO31 <sup>(1)</sup>   | 011 0100                                         | I   | RPI52          |

| 000 1000                                         | I                | FINDX1 <sup>(1,2)</sup> | 011 0101                                         | I   | RPI53          |

| 000 1001                                         | I                | FHOME1 <sup>(1,2)</sup> | 011 0110                                         | I/O | RP54           |

| 000 1010                                         | _                | _                       | 011 0111                                         | I/O | RP55           |

| 000 1011                                         | —                | _                       | 011 1000                                         | I/O | RP56           |

| 000 1100                                         | —                | —                       | 011 1001                                         | I/O | RP57           |

| 000 1101                                         | _                |                         | 011 1010                                         | I   | RPI58          |

| 000 1110                                         | —                | —                       | 011 1011                                         | _   | —              |

| 000 1111                                         | —                | —                       | 011 1100                                         | _   | —              |

| 001 0000                                         | —                | —                       | 011 1101                                         | —   | _              |

| 001 0001                                         | —                | —                       | 011 1110                                         | _   | —              |

| 001 0010                                         | —                | —                       | 011 1111                                         | —   | —              |

| 001 0011                                         | —                | —                       | 100 0000                                         | —   | _              |

| 001 0100                                         | I/O              | RP20                    | 100 0001                                         |     | —              |

| 001 0101                                         | —                | —                       | 100 0010                                         | —   | —              |

| 001 0110                                         | —                | —                       | 100 0011                                         | _   | —              |

| 001 0111                                         | —                | —                       | 100 0100                                         |     | —              |

| 001 1000                                         | I                | RPI24                   | 100 0101                                         | _   | —              |

| 001 1001                                         | I                | RPI25                   | 100 0110                                         | _   | —              |

| 001 1010                                         | —                | —                       | 100 0111                                         |     | —              |

| 001 1011                                         | I                | RPI27                   | 100 1000                                         | _   | _              |

| 001 1100                                         | I                | RPI28                   | 100 1001                                         | _   |                |

| 001 1101                                         | —                | _                       | 100 1010                                         | _   | _              |

| 001 1110                                         | —                |                         | 100 1011                                         | _   |                |

| 001 1111                                         | —                |                         | 100 1100                                         | —   | _              |

| 010 0000                                         | I                | RPI32                   | 100 1101                                         | —   | _              |

| 010 0001                                         | I                | RPI33                   | 100 1110                                         | _   | _              |

| 010 0010                                         | I                | RPI34                   | 100 1111                                         | _   |                |

| 010 0011                                         | I/O              | RP35                    | 101 0000                                         | _   | <u> </u>       |

| 010 0100                                         | I/O              | RP36                    | 101 0001                                         | —   | _              |

| 010 0101                                         | I/O              | RP37                    | 101 0010                                         | —   | _              |

| 010 0110                                         | I/O              | RP38                    | 101 0011                                         | —   | _              |

| 010 0111                                         | I/O              | RP39                    | 101 0100                                         | _   | _              |

#### TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES

Legend: Shaded rows indicate PPS Input register values that are unimplemented.

Note 1: See Section 11.4.4.1 "Virtual Connections" for more information on selecting this pin assignment.

2: These inputs are available on dsPIC33EPXXXGP/MC50X devices only.

| U-0    | U-0 | R/W-0      | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------|-----|------------|------------|-------|-------|-------|-------|--|

| —      | —   |            | RP43R<5:0> |       |       |       |       |  |

| bit 15 |     |            |            |       |       |       | bit 8 |  |

|        |     |            |            |       |       |       |       |  |

| U-0    | U-0 | R/W-0      | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

| —      | —   | RP42R<5:0> |            |       |       |       |       |  |

#### REGISTER 11-22: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

|   | bit | 7 |

|---|-----|---|

| 1 |     |   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP43R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP43 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP42R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-23: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------|-----|-------|------------|-------|-------|-------|-------|--|

| —      | —   |       | RP55R<5:0> |       |       |       |       |  |

| bit 15 |     |       |            |       |       |       | bit 8 |  |

| U-0   | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-----|-------|------------|-------|-------|-------|-------|--|

| —     | —   |       | RP54R<5:0> |       |       |       |       |  |

| bit 7 |     |       |            |       |       |       | bit 0 |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP55R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP55 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP54R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP54 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 0

NOTES:

| REGISTE       | R 16-7: PWMC                            | CONX: PWMX (                               | CONTROL R      | EGISTER          |                      |                      |                     |

|---------------|-----------------------------------------|--------------------------------------------|----------------|------------------|----------------------|----------------------|---------------------|

| HS/HC-        | 0 HS/HC-0                               | HS/HC-0                                    | R/W-0          | R/W-0            | R/W-0                | R/W-0                | R/W-0               |

| FLTSTAT       | -(1) CLSTAT <sup>(1)</sup>              | TRGSTAT                                    | FLTIEN         | CLIEN            | TRGIEN               | ITB <sup>(2)</sup>   | MDCS <sup>(2)</sup> |

| bit 15        | ·                                       | •                                          |                | ÷                |                      |                      | bit                 |

| R/W-0         | R/W-0                                   | R/W-0                                      | U-0            | R/W-0            | R/W-0                | R/W-0                | R/W-0               |

| DTC1          |                                         | DTCP <sup>(3)</sup>                        | 0-0            | MTBS             | CAM <sup>(2,4)</sup> | XPRES <sup>(5)</sup> | IUE <sup>(2)</sup>  |

| bit 7         | DICO                                    | DICE                                       | _              | INT DO           | CAIN                 | AFRES'               | bit                 |

|               |                                         |                                            |                |                  |                      |                      | <u> </u>            |

| Legend:       |                                         | HC = Hardware                              | Clearable bit  | HS = Hardwa      | are Settable bit     |                      |                     |

| R = Reada     | able bit                                | W = Writable bi                            | t              | U = Unimple      | mented bit, rea      | ıd as '0'            |                     |

| -n = Value    | at POR                                  | '1' = Bit is set                           |                | '0' = Bit is cle | eared                | x = Bit is unk       | nown                |

| bit 15        | ELTSTAT: ES                             | ult Interrupt Statu                        | is hit(1)      |                  |                      |                      |                     |

| DIL 15        |                                         | rrupt is pending                           |                |                  |                      |                      |                     |

|               |                                         | interrupt is pendi                         | ng             |                  |                      |                      |                     |

|               |                                         | ared by setting F                          |                |                  |                      |                      |                     |

| bit 14        |                                         | rent-Limit Interru                         | •              |                  |                      |                      |                     |

|               |                                         | mit interrupt is pe                        |                |                  |                      |                      |                     |

|               |                                         | nt-limit interrupt is<br>ared by setting C |                |                  |                      |                      |                     |

| bit 13        |                                         | igger Interrupt S                          |                |                  |                      |                      |                     |

|               |                                         | terrupt is pendin                          |                |                  |                      |                      |                     |

|               |                                         | r interrupt is pen                         |                |                  |                      |                      |                     |

|               |                                         | ared by setting T                          |                |                  |                      |                      |                     |

| bit 12        |                                         | t Interrupt Enable                         | e bit          |                  |                      |                      |                     |

|               |                                         | rrupt is enabled rrupt is disabled         | and the FLTS   | TAT bit is clear | ed                   |                      |                     |

| bit 11        |                                         | ent-Limit Interrup                         |                |                  | cu .                 |                      |                     |

|               |                                         | mit interrupt is er                        |                |                  |                      |                      |                     |

|               |                                         | mit interrupt is di                        |                | e CLSTAT bit is  | s cleared            |                      |                     |

| bit 10        | TRGIEN: Trig                            | ger Interrupt En                           | able bit       |                  |                      |                      |                     |

|               |                                         | event generates                            |                |                  | T hit is cleared     |                      |                     |

| bit 9         |                                         | vent interrupts ar<br>dent Time Base I     |                |                  | i bit is cleared     |                      |                     |

| DIL 9         |                                         | register provides                          |                | riad for this PM | VM generator         |                      |                     |

|               |                                         | egister provides f                         | •              |                  | •                    |                      |                     |

| bit 8         |                                         | er Duty Cycle Re                           |                |                  |                      |                      |                     |

|               |                                         | ister provides du<br>jister provides du    |                |                  |                      | r                    |                     |

| Note 1:       | Software must clea                      |                                            |                |                  | -                    |                      | t controller        |

| Note 1.<br>2: | These bits should                       | -                                          |                | -                | -                    | the interrup         |                     |

| 3:            | DTC<1:0> = 11 fo                        | -                                          |                | -                | -                    |                      |                     |

| 4:            | The Independent T<br>CAM bit is ignored | Time Base (ITB =                           |                | •                |                      | igned mode. If       | TTB = 0, the        |

| 5:            | To operate in Exter                     |                                            | t mode, the IT | B bit must be '  | 1' and the CLM       | 10D bit in the I     | FCLCONx             |

### REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER

5: To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

## 21.0 ENHANCED CAN (ECAN™) MODULE (dsPIC33EPXXXGP/ MC50X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Enhanced Controller Area Network (ECAN™)" (DS70353) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

## 21.1 Overview

The Enhanced Controller Area Network (ECAN) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/protocol was designed to allow communications within noisy environments. The dsPIC33EPXXXGP/MC50X devices contain one ECAN module.

The ECAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH CAN specification. The module supports CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader can refer to the BOSCH CAN specification for further details. The ECAN module features are as follows:

- Implementation of the CAN protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- · Standard and extended data frames

- 0-8 bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Automatic response to remote transmission requests

- Up to eight transmit buffers with application specified prioritization and abort capability (each buffer can contain up to 8 bytes of data)

- Up to 32 receive buffers (each buffer can contain up to 8 bytes of data)

- Up to 16 full (Standard/Extended Identifier) acceptance filters

- Three full acceptance filter masks

- DeviceNet<sup>™</sup> addressing support

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- · Programmable clock source

- Programmable link to Input Capture (IC2) module for time-stamping and network synchronization

- · Low-power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

| U-0                     | U-0                                  | U-0                                | R-0     | R-0              | R-0             | R-0             | R-0     |  |  |  |

|-------------------------|--------------------------------------|------------------------------------|---------|------------------|-----------------|-----------------|---------|--|--|--|

| _                       | _                                    |                                    | FILHIT4 | FILHIT3          | FILHIT2         | FILHIT1         | FILHIT0 |  |  |  |

| bit 15                  | <b>I</b>                             | •                                  |         |                  |                 |                 | bit 8   |  |  |  |

|                         |                                      |                                    |         |                  |                 |                 |         |  |  |  |

| U-0                     | R-1                                  | R-0                                | R-0     | R-0              | R-0             | R-0             | R-0     |  |  |  |

| _                       | ICODE6                               | ICODE5                             | ICODE4  | ICODE3           | ICODE2          | ICODE1          | ICODE0  |  |  |  |

| bit 7                   |                                      |                                    |         |                  |                 |                 | bit     |  |  |  |

| Logondi                 |                                      |                                    |         |                  |                 |                 |         |  |  |  |

| Legend:<br>R = Readable | - hit                                |                                    | hit.    |                  | nonted hit rea  | d aa 'O'        |         |  |  |  |

| -n = Value at           |                                      | W = Writable                       |         | '0' = Bit is cle | mented bit, rea |                 |         |  |  |  |

| -n = value at           | POR                                  | '1' = Bit is set                   |         | 0 = Bit is cie   | ared            | x = Bit is unkr | IOWN    |  |  |  |

| bit 15-13               | Unimplemen                           | ted: Read as '                     | 0'      |                  |                 |                 |         |  |  |  |

| bit 12-8                | =                                    | Filter Hit Num                     |         |                  |                 |                 |         |  |  |  |

|                         |                                      | 1 = Reserved                       |         |                  |                 |                 |         |  |  |  |

|                         | 01111 <b>= Filte</b>                 | r 15                               |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •<br>00001 = Filter 1                |                                    |         |                  |                 |                 |         |  |  |  |

|                         | 00001 = Filter 1<br>00000 = Filter 0 |                                    |         |                  |                 |                 |         |  |  |  |

| bit 7                   |                                      | ted: Read as '                     | 0'      |                  |                 |                 |         |  |  |  |

| bit 6-0                 | ICODE<6:0>: Interrupt Flag Code bits |                                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | 11111 = Rese                       |         |                  |                 |                 |         |  |  |  |

|                         |                                      | IFO almost full                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | eceiver overflo                    |         |                  |                 |                 |         |  |  |  |

|                         | 1000010 = K<br>1000001 = E           | /ake-up interru<br>rror interrupt  | μ       |                  |                 |                 |         |  |  |  |

|                         | 1000000 = N                          |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | 11111 = Rese                       |         |                  |                 |                 |         |  |  |  |

|                         | •                                    | B15 buffer inte                    | inupt   |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | 0001001 <b>= R</b>                   | B9 buffer inter                    | rupt    |                  |                 |                 |         |  |  |  |

|                         |                                      | B8 buffer inter                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | RB7 buffer inte<br>RB6 buffer inte |         |                  |                 |                 |         |  |  |  |

|                         |                                      | RB5 buffer inte                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | RB4 buffer inte                    |         |                  |                 |                 |         |  |  |  |

|                         | 0000011 <b>= T</b>                   | RB3 buffer inte                    | errupt  |                  |                 |                 |         |  |  |  |

|                         |                                      |                                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | RB2 buffer inte<br>RB1 buffer inte |         |                  |                 |                 |         |  |  |  |

#### REGISTER 21-3: CxVEC: ECANx INTERRUPT CODE REGISTER

| Legend:C = Writable bit, but onlyR = Readable bitW = Writable bit |       |       |      |        | n to clear the bit<br>mented bit, read |       |       |

|-------------------------------------------------------------------|-------|-------|------|--------|----------------------------------------|-------|-------|

|                                                                   |       |       |      |        |                                        |       |       |

| bit 7                                                             |       |       |      |        |                                        |       | bit 0 |

| IVRIF                                                             | WAKIF | ERRIF | _    | FIFOIF | RBOVIF                                 | RBIF  | TBIF  |

| R/C-0                                                             | R/C-0 | R/C-0 | U-0  | R/C-0  | R/C-0                                  | R/C-0 | R/C-0 |

|                                                                   |       |       |      |        |                                        |       |       |

| bit 15                                                            | •     |       |      |        |                                        |       | bit 8 |

| _                                                                 | —     | ТХВО  | TXBP | RXBP   | TXWAR                                  | RXWAR | EWARN |

| U-0                                                               | U-0   | R-0   | R-0  | R-0    | R-0                                    | R-0   | R-0   |

'0' = Bit is cleared

x = Bit is unknown

#### REGISTER 21-6: CxINTF: ECANx INTERRUPT FLAG REGISTER

'1' = Bit is set

| bit 15-14 | Unimplemented: Read as '0'                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------|

| bit 13    | <b>TXBO:</b> Transmitter in Error State Bus Off bit                                                    |

|           | 1 = Transmitter is in Bus Off state                                                                    |

|           | 0 = Transmitter is not in Bus Off state                                                                |

| bit 12    | <b>TXBP:</b> Transmitter in Error State Bus Passive bit                                                |

|           | 1 = Transmitter is in Bus Passive state                                                                |

|           | 0 = Transmitter is not in Bus Passive state                                                            |

| bit 11    | <b>RXBP:</b> Receiver in Error State Bus Passive bit                                                   |

|           | 1 = Receiver is in Bus Passive state                                                                   |

|           | 0 = Receiver is not in Bus Passive state                                                               |

| bit 10    | TXWAR: Transmitter in Error State Warning bit                                                          |

|           | 1 = Transmitter is in Error Warning state                                                              |

| h:+ 0     | 0 = Transmitter is not in Error Warning state                                                          |

| bit 9     | RXWAR: Receiver in Error State Warning bit                                                             |

|           | 1 = Receiver is in Error Warning state<br>0 = Receiver is not in Error Warning state                   |

| bit 8     | EWARN: Transmitter or Receiver in Error State Warning bit                                              |

| bit o     | 1 = Transmitter or receiver is in Error Warning state                                                  |

|           | 0 = Transmitter or receiver is not in Error Warning state                                              |

| bit 7     | IVRIF: Invalid Message Interrupt Flag bit                                                              |

|           | 1 = Interrupt request has occurred                                                                     |

|           | 0 = Interrupt request has not occurred                                                                 |

| bit 6     | WAKIF: Bus Wake-up Activity Interrupt Flag bit                                                         |

|           | 1 = Interrupt request has occurred                                                                     |

|           | 0 = Interrupt request has not occurred                                                                 |

| bit 5     | ERRIF: Error Interrupt Flag bit (multiple sources in CxINTF<13:8>)                                     |

|           | 1 = Interrupt request has occurred                                                                     |

|           | 0 = Interrupt request has not occurred                                                                 |

| bit 4     | Unimplemented: Read as '0'                                                                             |

| bit 3     | FIFOIF: FIFO Almost Full Interrupt Flag bit                                                            |

|           | 1 = Interrupt request has occurred                                                                     |

| hit O     | 0 = Interrupt request has not occurred                                                                 |

| bit 2     | RBOVIF: RX Buffer Overflow Interrupt Flag bit                                                          |

|           | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |

|           |                                                                                                        |

-n = Value at POR

#### REGISTER 25-4: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT CONTROL REGISTER (CONTINUED)

- bit 3-0 SELSRCA<3:0>: Mask A Input Select bits

- 1111 = FLT4 1110 = FLT2 1101 = PTGO19 1100 = PTGO18 1011 = Reserved 1010 = Reserved 1001 = Reserved 1000 = Reserved 0111 = Reserved 0110 = Reserved 0101 = PWM3H 0100 = PWM3L 0011 = PWM2H 0010 = PWM2L 0001 = PWM1H 0000 = PWM1L

#### REGISTER 27-1: DEVID: DEVICE ID REGISTER

|        | gend: R = Read-Only bit U = Unimplemented bit |   |         |                       |   |   |        |

|--------|-----------------------------------------------|---|---------|-----------------------|---|---|--------|

|        |                                               |   |         |                       |   |   |        |

| bit 7  |                                               |   |         |                       |   |   | bit 0  |

|        |                                               |   | DEVID   | <7:0> <sup>(1)</sup>  |   |   |        |

| R      | R                                             | R | R       | R                     | R | R | R      |

| bit 15 |                                               |   |         |                       |   |   | bit 8  |

|        |                                               |   | DEVID<  | :15:8> <sup>(1)</sup> |   |   |        |

| R      | R                                             | R | R       | R                     | R | R | R      |

| bit 23 |                                               |   |         |                       |   |   | bit 16 |

|        |                                               |   | DEVID<2 | 23:16>(1)             |   |   |        |

| R      | R                                             | R | R       | R                     | R | R | R      |

bit 23-0 **DEVID<23:0>:** Device Identifier bits<sup>(1)</sup>

**Note 1:** Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration *Bits*" (DS70663) for the list of device ID values.

#### **REGISTER 27-2: DEVREV: DEVICE REVISION REGISTER**

| R           | R             | R | R      | R                      | R          | R | R      |

|-------------|---------------|---|--------|------------------------|------------|---|--------|

|             |               |   | DEVREV | <23:16> <sup>(1)</sup> |            |   |        |

| bit 23      |               |   |        |                        |            |   | bit 16 |

|             |               |   |        |                        |            |   |        |

| R           | R             | R | R      | R                      | R          | R | R      |

|             |               |   | DEVREV | <15:8>(1)              |            |   |        |

| bit 15      |               |   |        |                        |            |   | bit 8  |

| R           | R             | R | R      | R                      | R          | R | R      |

|             |               |   | DEVRE\ | /<7:0> <sup>(1)</sup>  |            |   |        |

| bit 7       |               |   |        |                        |            |   | bit 0  |

|             |               |   |        |                        |            |   |        |

| Legend: R = | Read-only bit |   |        | U = Unimplem           | nented bit |   |        |

#### bit 23-0 **DEVREV<23:0>:** Device Revision bits<sup>(1)</sup>

**Note 1:** Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration *Bits*" (DS70663) for the list of device revision values.

#### **30.1 DC Characteristics**

|                |                             |                       | Maximum MIPS                                                          |

|----------------|-----------------------------|-----------------------|-----------------------------------------------------------------------|

| Characteristic | VDD Range<br>(in Volts)     | Temp Range<br>(in °C) | dsPIC33EPXXXGP50X,<br>dsPIC33EPXXXMC20X/50X and<br>PIC24EPXXXGP/MC20X |

|                | 3.0V to 3.6V <sup>(1)</sup> | -40°C to +85°C        | 70                                                                    |

| —              | 3.0V to 3.6V <sup>(1)</sup> | -40°C to +125°C       | 60                                                                    |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

#### TABLE 30-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                      | Symbol | Min. | Тур.        | Max. | Unit |

|---------------------------------------------------------------------------------------------|--------|------|-------------|------|------|

| Industrial Temperature Devices                                                              |        |      |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40  | —           | +125 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40  | _           | +85  | °C   |

| Extended Temperature Devices                                                                |        |      |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40  | —           | +140 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40  | —           | +125 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$ | PD     | I    | Pint + Pi/c | D    | W    |

| I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$     |        |      |             |      |      |

| Maximum Allowed Power Dissipation                                                           | PDMAX  | (    | TJ — TA)/θJ | IA   | W    |

#### TABLE 30-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                   | Symbol | Тур. | Max. | Unit | Notes |

|--------------------------------------------------|--------|------|------|------|-------|

| Package Thermal Resistance, 64-Pin QFN           | θJA    | 28.0 |      | °C/W | 1     |

| Package Thermal Resistance, 64-Pin TQFP 10x10 mm | θJA    | 48.3 | _    | °C/W | 1     |

| Package Thermal Resistance, 48-Pin UQFN 6x6 mm   | θJA    | 41   | -    | °C/W | 1     |

| Package Thermal Resistance, 44-Pin QFN           | θJA    | 29.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 44-Pin TQFP 10x10 mm | θJA    | 49.8 | _    | °C/W | 1     |

| Package Thermal Resistance, 44-Pin VTLA 6x6 mm   | θJA    | 25.2 | _    | °C/W | 1     |

| Package Thermal Resistance, 36-Pin VTLA 5x5 mm   | θJA    | 28.5 | —    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin QFN-S         | θJA    | 30.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SSOP          | θJA    | 71.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SOIC          | θJA    | 69.7 | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SPDIP         | θJA    | 60.0 | —    | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

| AC CHARACTERISTICS |               |                                                                                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |             |            |                               |  |