Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep128mc206t-i-mr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

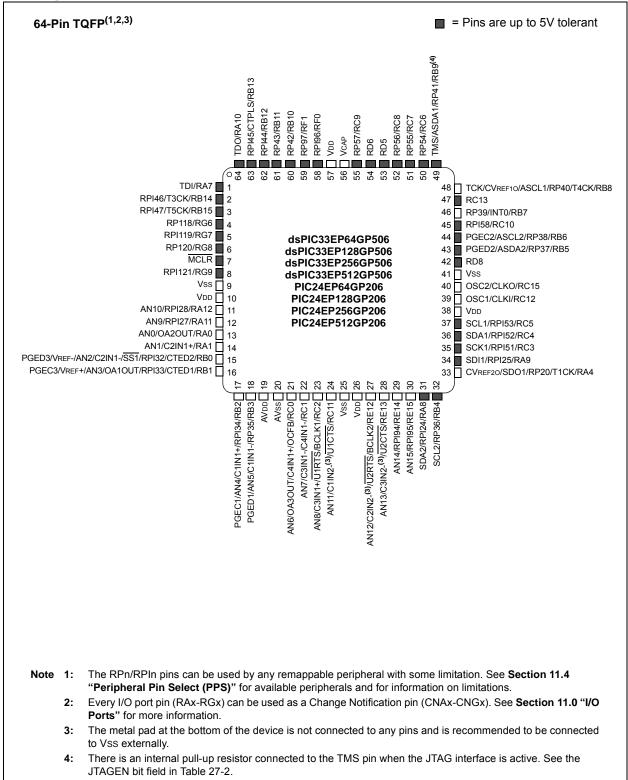

## Pin Diagrams (Continued)

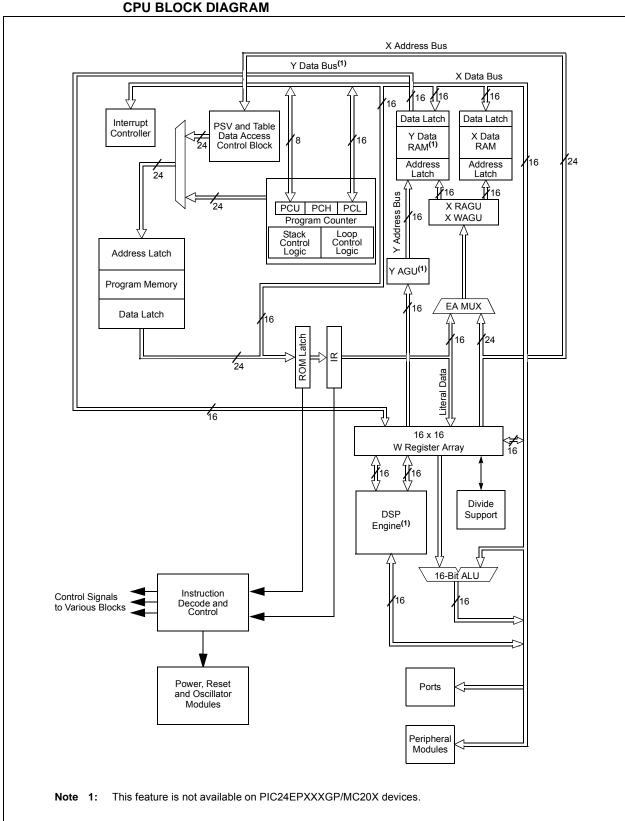

FIGURE 3-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X CPU BLOCK DIAGRAM

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

| R/W-0  | U-0 | R/W-0              | R/W-0              | R/W-0                | R-0                | R-0                | R-0                |

|--------|-----|--------------------|--------------------|----------------------|--------------------|--------------------|--------------------|

| VAR    | _   | US1 <sup>(1)</sup> | US0 <sup>(1)</sup> | EDT <sup>(1,2)</sup> | DL2 <sup>(1)</sup> | DL1 <sup>(1)</sup> | DL0 <sup>(1)</sup> |

| bit 15 |     |                    |                    |                      |                    |                    | bit 8              |

| R/W-0               | R/W-0               | R/W-1                | R/W-0                 | R/C-0               | R-0 | R/W-0              | R/W-0             |

|---------------------|---------------------|----------------------|-----------------------|---------------------|-----|--------------------|-------------------|

| SATA <sup>(1)</sup> | SATB <sup>(1)</sup> | SATDW <sup>(1)</sup> | ACCSAT <sup>(1)</sup> | IPL3 <sup>(3)</sup> | SFA | RND <sup>(1)</sup> | IF <sup>(1)</sup> |

| bit 7               |                     |                      |                       |                     |     |                    | bit 0             |

| Legend:           | C = Clearable bit |                             |                    |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 VAR: Variable Exception Processing Latency Control bit

1 = Variable exception processing latency is enabled

0 = Fixed exception processing latency is enabled

bit 14 **Unimplemented:** Read as '0'

bit 13-12 US<1:0>: DSP Multiply Unsigned/Signed Control bits<sup>(1)</sup>

11 = Reserved

10 = DSP engine multiplies are mixed-sign01 = DSP engine multiplies are unsigned

00 = DSP engine multiplies are signed

bit 11 **EDT:** Early DO Loop Termination Control bit<sup>(1,2)</sup>

1 = Terminates executing DO loop at end of current loop iteration

0 = No effect

bit 10-8 **DL<2:0>:** DO Loop Nesting Level Status bits<sup>(1)</sup>

111 = 7 DO loops are active

•

•

001 = 1 DO loop is active 000 = 0 DO loops are active

bit 7 SATA: ACCA Saturation Enable bit (1)

1 = Accumulator A saturation is enabled

0 = Accumulator A saturation is disabled

bit 6 SATB: ACCB Saturation Enable bit<sup>(1)</sup>

1 = Accumulator B saturation is enabled

0 = Accumulator B saturation is disabled

bit 5 SATDW: Data Space Write from DSP Engine Saturation Enable bit<sup>(1)</sup>

1 = Data Space write saturation is enabled

0 = Data Space write saturation is disabled

bit 4 ACCSAT: Accumulator Saturation Mode Select bit<sup>(1)</sup>

1 = 9.31 saturation (super saturation)

0 = 1.31 saturation (normal saturation)

bit 3 IPL3: CPU Interrupt Priority Level Status bit 3<sup>(3)</sup>

1 = CPU Interrupt Priority Level is greater than 7

0 = CPU Interrupt Priority Level is 7 or less

Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

2: This bit is always read as '0'.

3: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| Ō  |

|----|

| 7  |

| 0  |

| Ō  |

| ō  |

| ō  |

| ത  |

| čń |

| ≺i |

| ~  |

| ㅗ  |

|    |

| ਰ  |

| ā  |

| ū  |

| ⋇  |

| V  |

| ~1 |

| Ω, |

| U  |

|    |

|    |

#### **TABLE 4-8: TIMER1 THROUGH TIMER5 REGISTER MAP**

| SFR<br>Name | Addr. | Bit 15                                                     | Bit 14            | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8       | Bit 7         | Bit 6        | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|------------------------------------------------------------|-------------------|--------|--------|--------|--------|--------------|-------------|---------------|--------------|-------|--------|-------|-------|-------|-------|---------------|

| TMR1        | 0100  |                                                            |                   |        |        |        |        |              | Timer1      | Register      |              |       |        |       |       |       |       | xxxx          |

| PR1         | 0102  |                                                            |                   |        |        |        |        |              | Period F    | Register 1    |              |       |        |       |       |       |       | FFFF          |

| T1CON       | 0104  | TON - TSIDL TGATE TCKPS<1:0> - TSYNC TCS -                 |                   |        |        |        |        |              | 0000        |               |              |       |        |       |       |       |       |               |

| TMR2        | 0106  |                                                            | Timer2 Register : |        |        |        |        |              |             |               |              |       | xxxx   |       |       |       |       |               |

| TMR3HLD     | 0108  | Timer3 Holding Register (for 32-bit timer operations only) |                   |        |        |        |        |              |             |               |              | xxxx  |        |       |       |       |       |               |

| TMR3        | 010A  |                                                            | Timer3 Register   |        |        |        |        |              |             |               |              |       | xxxx   |       |       |       |       |               |

| PR2         | 010C  |                                                            | Period Register 2 |        |        |        |        |              |             |               |              |       | FFFF   |       |       |       |       |               |

| PR3         | 010E  | Period Register 3                                          |                   |        |        |        |        |              |             |               | FFFF         |       |        |       |       |       |       |               |

| T2CON       | 0110  | TON                                                        | _                 | TSIDL  | _      | _      | _      | _            | _           | _             | TGATE        | TCKPS | S<1:0> | T32   | _     | TCS   | _     | 0000          |

| T3CON       | 0112  | TON                                                        | _                 | TSIDL  | _      | _      | _      | _            | _           | _             | TGATE        | TCKPS | S<1:0> | _     | _     | TCS   | _     | 0000          |

| TMR4        | 0114  |                                                            |                   |        |        |        |        |              | Timer4      | Register      |              |       |        |       |       |       |       | xxxx          |

| TMR5HLD     | 0116  |                                                            |                   |        |        |        | Т      | imer5 Holdir | ng Register | (for 32-bit o | perations on | ly)   |        |       |       |       |       | xxxx          |

| TMR5        | 0118  |                                                            |                   |        |        |        |        |              | Timer5      | Register      |              |       |        |       |       |       |       | xxxx          |

| PR4         | 011A  |                                                            |                   |        |        |        |        |              | Period F    | Register 4    |              |       |        |       |       |       |       | FFFF          |

| PR5         | 011C  |                                                            |                   |        |        |        |        |              | Period F    | Register 5    |              |       |        |       |       |       |       | FFFF          |

| T4CON       | 011E  | TON                                                        | _                 | TSIDL  | _      | _      | _      | _            | _           | _             | TGATE        | TCKPS | S<1:0> | T32   | _     | TCS   | _     | 0000          |

| T5CON       | 0120  | TON                                                        | 1                 | TSIDL  | ı      | -      | _      | _            | _           | _             | TGATE        | TCKPS | S<1:0> | _     | _     | TCS   |       | 0000          |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**EXAMPLE 4-3:**

PAGED DATA MEMORY SPACE

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configuring the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages, by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address prior to modification addresses an EDS or PSV page

- The EA calculation uses Pre-Modified or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-61 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- · Modulo Addressing

- Bit-Reversed Addressing

TABLE 4-61: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS and PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

|             | •                         | OV SI ACE BOOK | D/ (( ( ) )  |                     |                |              |                     |  |

|-------------|---------------------------|----------------|--------------|---------------------|----------------|--------------|---------------------|--|

| 0/11        |                           |                | Before       |                     | After          |              |                     |  |

| O/U,<br>R/W | Operation                 | DSxPAG         | DS<br>EA<15> | Page<br>Description | DSxPAG         | DS<br>EA<15> | Page<br>Description |  |

| O,<br>Read  |                           | DSRPAG = 0x1FF | 1            | EDS: Last page      | DSRPAG = 0x1FF | 0            | See Note 1          |  |

| O,<br>Read  | [++Wn]                    | DSRPAG = 0x2FF | 1            | PSV: Last Isw page  | DSRPAG = 0x300 | 1            | PSV: First MSB page |  |

| O,<br>Read  | or<br>[Wn++]              | DSRPAG = 0x3FF | 1            | PSV: Last MSB page  | DSRPAG = 0x3FF | 0            | See Note 1          |  |

| O,<br>Write |                           | DSWPAG = 0x1FF | 1            | EDS: Last page      | DSWPAG = 0x1FF | 0            | See Note 1          |  |

| U,<br>Read  |                           | DSRPAG = 0x001 | 1            | PSV page            | DSRPAG = 0x001 | 0            | See Note 1          |  |

| U,<br>Read  | [Wn]<br><b>or</b><br>[Wn] | DSRPAG = 0x200 | 1            | PSV: First Isw page | DSRPAG = 0x200 | 0            | See Note 1          |  |

| U,<br>Read  | [ [ ]                     | DSRPAG = 0x300 | 1            | PSV: First MSB page | DSRPAG = 0x2FF | 1            | PSV: Last Isw page  |  |

**Legend:** O = Overflow, U = Underflow, R = Read, W = Write

- Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x8000).

- 2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

- **3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

- 4: Pseudo-Linear Addressing is not supported for large offsets.

## REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| R/W-0  | U-0 | R/W-0 | R/W-0 | R/W-0 | R-0 | R-0 | R-0   |

|--------|-----|-------|-------|-------|-----|-----|-------|

| VAR    | _   | US1   | US0   | EDT   | DL2 | DL1 | DL0   |

| bit 15 |     |       |       |       |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R-0 | R/W-0 | R/W-0 |

|-------|-------|-------|--------|---------------------|-----|-------|-------|

| SATA  | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | SFA | RND   | IF    |

| bit 7 |       |       |        |                     |     |       | bit 0 |

Legend:C = Clearable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1'= Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15 VAR: Variable Exception Processing Latency Control bit

1 = Variable exception processing is enabled0 = Fixed exception processing is enabled

bit 3 IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup>

1 = CPU Interrupt Priority Level is greater than 7 0 = CPU Interrupt Priority Level is 7 or less

Note 1: For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

#### 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the power-saving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the ECAN $^{\text{TM}}$  module has been configured for 500 kbps, based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the ECAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

#### 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC® DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

Note: If a PMD bit is set, the corresponding module is disabled after a delay of one instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of one instruction cycle (assuming the module control registers are already configured to enable module operation).

#### 10.5 Power-Saving Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/

Devices.aspx?dDocName=en555464

### 10.5.1 KEY RESOURCES

- "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES (CONTINUED)

| Peripheral Pin                 |                  |                | ] | Peripheral Pin                 | 1                | , , , , , , , , , , , , , , , , , , , |

|--------------------------------|------------------|----------------|---|--------------------------------|------------------|---------------------------------------|

| Select Input<br>Register Value | Input/<br>Output | Pin Assignment |   | Select Input<br>Register Value | Input/<br>Output | Pin Assignme                          |

| 010 1000                       | I/O              | RP40           |   | 101 0101                       | _                | _                                     |

| 010 1001                       | I/O              | RP41           |   | 101 0110                       | _                | _                                     |

| 010 1010                       | I/O              | RP42           |   | 101 0111                       | _                | _                                     |

| 010 1011                       | I/O              | RP43           |   | 101 1000                       | _                | _                                     |

| 010 1100                       | I                | RPI44          |   | 101 1001                       | _                | _                                     |

| 101 1010                       | _                | _              |   | 110 1101                       | _                | _                                     |

| 101 1011                       | _                | _              |   | 110 1110                       | _                |                                       |

| 101 1100                       | _                | _              |   | 110 1111                       | _                | _                                     |

| 101 1101                       | _                | _              |   | 111 0000                       | _                | _                                     |

| 101 1110                       | I                | RPI94          |   | 111 0001                       | _                |                                       |

| 101 1111                       | I                | RPI95          |   | 111 0010                       | _                | _                                     |

| 110 0000                       | I                | RPI96          |   | 111 0011                       | _                | _                                     |

| 110 0001                       | I/O              | RP97           |   | 111 0100                       | _                | _                                     |

| 110 0010                       | _                | _              |   | 111 0101                       | _                | _                                     |

| 110 0011                       | _                | _              |   | 111 0110                       | I/O              | RP118                                 |

| 110 0100                       | _                | _              |   | 111 0111                       | I                | RPI119                                |

| 110 0101                       | _                | _              |   | 111 1000                       | I/O              | RP120                                 |

| 110 0110                       | _                | _              |   | 111 1001                       | I                | RPI121                                |

| 110 0111                       | _                | _              |   | 111 1010                       | _                | _                                     |

| 110 1000                       | _                | _              |   | 111 1011                       | _                | _                                     |

| 110 1001                       | _                | _              |   | 111 1100                       | _                | _                                     |

| 110 1010                       | _                | _              |   | 111 1101                       | _                | _                                     |

| 110 1011                       | _                | _              |   | 111 1110                       |                  | _                                     |

| 110 1100                       | _                | <del>-</del>   |   | 111 1111                       |                  | _                                     |

**Legend:** Shaded rows indicate PPS Input register values that are unimplemented.

Note 1: See Section 11.4.4.1 "Virtual Connections" for more information on selecting this pin assignment.

**2:** These inputs are available on dsPIC33EPXXXGP/MC50X devices only.

# REGISTER 11-15: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------------|-------|-------|-------|

| _      |       |       |       | SYNCI1R<6:0 | )>    |       |       |

| bit 15 |       |       |       |             |       |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-8 SYNCI1R<6:0>: Assign PWM Synchronization Input 1 to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

.

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

bit 7-0 **Unimplemented:** Read as '0'

## 13.2 Timer Control Registers

### REGISTER 13-1: TxCON: (TIMER2 AND TIMER4) CONTROL REGISTER

| R/W-0        | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0 | U-0 |  |  |

|--------------|-----|-------|-----|-----|-----|-----|-----|--|--|

| TON          | _   | TSIDL | _   | _   | _   | _   | _   |  |  |

| bit 15 bit 8 |     |       |     |     |     |     |     |  |  |

| U-0   | R/W-0 | R/W-0  | R/W-0  | R/W-0 | U-0 | R/W-0 | U-0   |

|-------|-------|--------|--------|-------|-----|-------|-------|

| _     | TGATE | TCKPS1 | TCKPS0 | T32   | _   | TCS   | _     |

| bit 7 |       |        |        |       |     |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **TON:** Timerx On bit

When T32 = 1:

1 = Starts 32-bit Timerx/y 0 = Stops 32-bit Timerx/y

When T32 = 0:

1 = Starts 16-bit Timerx

0 = Stops 16-bit Timerx

bit 14 Unimplemented: Read as '0'

bit 13 TSIDL: Timerx Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12-7 Unimplemented: Read as '0'

bit 6 TGATE: Timerx Gated Time Accumulation Enable bit

When TCS = 1: This bit is ignored. When TCS = 0:

1 = Gated time accumulation is enabled 0 = Gated time accumulation is disabled

bit 5-4 TCKPS<1:0>: Timerx Input Clock Prescale Select bits

11 = 1:256 10 = 1:64 01 = 1:8

00 = 1:1

bit 3 T32: 32-Bit Timer Mode Select bit

1 = Timerx and Timery form a single 32-bit timer 0 = Timerx and Timery act as two 16-bit timers

bit 2 Unimplemented: Read as '0'

bit 1 TCS: Timerx Clock Source Select bit

1 = External clock is from pin, TxCK (on the rising edge)

0 = Internal clock (FP)

bit 0 Unimplemented: Read as '0'

#### 16.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FOSCSEL<6>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring, PWMLOCK = 0.

To gain write access to these locked registers, the user application must write two consecutive values of (0xABCD and 0x4321) to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 16-1.

#### **EXAMPLE 16-1: PWMx WRITE-PROTECTED REGISTER UNLOCK SEQUENCE**

```

; FLT32 pin must be pulled low externally in order to clear and disable the fault

; Writing to FCLCON1 register requires unlock sequence

; Load first unlock key to w10 register

; Load second unlock key to w11 register

mov #0xabcd,w10

mov #0x4321,w11

; Load desired value of FCLCON1 register in w0

mov #0x0000,w0

mov w10, PWMKEY

; Write first unlock key to PWMKEY register

mov w11, PWMKEY

; Write second unlock key to PWMKEY register

mov w0,FCLCON1

; Write desired value to FCLCON1 register

; Set PWM ownership and polarity using the IOCON1 register

; Writing to IOCON1 register requires unlock sequence

mov #0xabcd,w10

; Load first unlock key to w10 register

mov #0x4321,w11

; Load second unlock key to wll register

mov #0xF000,w0

; Load desired value of IOCON1 register in w0

mov w10, PWMKEY

; Write first unlock key to PWMKEY register

mov w11, PWMKEY

; Write second unlock key to PWMKEY register

mov w0,IOCON1

; Write desired value to IOCON1 register

```

## REGISTER 16-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER<sup>(1)</sup>

| U-0    | U-0 R/W-0 |        | R/W-0 R/W-0 |        | R/W-0 R/W-0 |                      | R/W-0 |

|--------|-----------|--------|-------------|--------|-------------|----------------------|-------|

| _      | CLSRC4    | CLSRC3 | CLSRC2      | CLSRC1 | CLSRC0      | CLPOL <sup>(2)</sup> | CLMOD |

| bit 15 |           |        |             |        |             |                      | bit 8 |

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-0                 | R/W-0   | R/W-0   |

|---------|---------|---------|---------|---------|-----------------------|---------|---------|

| FLTSRC4 | FLTSRC3 | FLTSRC2 | FLTSRC1 | FLTSRC0 | FLTPOL <sup>(2)</sup> | FLTMOD1 | FLTMOD0 |

| bit 7   |         |         |         |         |                       |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 Unimplemented: Read as '0'

bit 14-10 CLSRC<4:0>: Current-Limit Control Signal Source Select for PWM Generator # bits

11111 = Fault 32

11110 = Reserved

•

01100 = Reserved

01011 = Comparator 4

01010 = Op Amp/Comparator 3

01001 = Op Amp/Comparator 2

01000 = Op Amp/Comparator 1

00111 = Reserved

00110 = Reserved

00101 = Reserved

00100 = Reserved

00011 = Fault 4

00010 = Fault 3

00001 = Fault 2

00000 = Fault 1 (default)

bit 9 **CLPOL:** Current-Limit Polarity for PWM Generator # bit<sup>(2)</sup>

1 = The selected current-limit source is active-low

0 = The selected current-limit source is active-high

bit 8 **CLMOD:** Current-Limit Mode Enable for PWM Generator # bit

1 = Current-Limit mode is enabled

0 = Current-Limit mode is disabled

**Note 1:** If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

2: These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

#### REGISTER 17-15: QEI1GECH: QEI1 GREATER THAN OR EQUAL COMPARE HIGH WORD REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

|        |       |       |       |       |       |       |       |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|---------------|-------|-------|-------|-------|-------|-------|-------|--|

| QEIGEC<23:16> |       |       |       |       |       |       |       |  |

| bit 7 bit     |       |       |       |       |       |       |       |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 QEIGEC<31:16>: High Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

#### REGISTER 17-16: QEI1GECL: QEI1 GREATER THAN OR EQUAL COMPARE LOW WORD REGISTER

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|

| QEIGEC<15:8> |       |       |       |       |       |       |       |  |

| bit 15       |       |       |       | bit 8 |       |       |       |  |

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|

| QEIGEC<7:0> |       |       |       |       |       |       |       |  |

| bit 7       |       |       |       |       |       |       |       |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 QEIGEC<15:0>: Low Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

#### REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER

| R-0, HSC | R-0, HSC | U-0 | U-0 | U-0 | R/C-0, HS | R-0, HSC | R-0, HSC |

|----------|----------|-----|-----|-----|-----------|----------|----------|

| ACKSTAT  | TRSTAT   | _   | _   | _   | BCL       | GCSTAT   | ADD10    |

| bit 15   |          |     |     |     |           |          | bit 8    |

| R/C-0, HS | R/C-0, HS | R-0, HSC | R/C-0, HSC | R/C-0, HSC | R-0, HSC | R-0, HSC | R-0, HSC |

|-----------|-----------|----------|------------|------------|----------|----------|----------|

| IWCOL     | I2COV     | D_A      | Р          | S          | R_W      | RBF      | TBF      |

| bit 7     |           |          |            |            |          |          | bit 0    |

| Legend:           | C = Clearable bit | HS = Hardware Settable bit         | HSC = Hardware Settable/Clearable bit |  |  |

|-------------------|-------------------|------------------------------------|---------------------------------------|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                                       |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown                    |  |  |

- bit 15 **ACKSTAT:** Acknowledge Status bit (when operating as I<sup>2</sup>C<sup>™</sup> master, applicable to master transmit operation)

- 1 = NACK received from slave

- 0 = ACK received from slave

Hardware is set or clear at the end of slave Acknowledge.

- bit 14 TRSTAT: Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = Master transmit is in progress (8 bits + ACK)

- 0 = Master transmit is not in progress

Hardware is set at the beginning of master transmission. Hardware is clear at the end of slave Acknowledge.

- bit 13-11 Unimplemented: Read as '0'

- bit 10 BCL: Master Bus Collision Detect bit

- 1 = A bus collision has been detected during a master operation

- 0 = No bus collision detected

Hardware is set at detection of a bus collision.

- bit 9 GCSTAT: General Call Status bit

- 1 = General call address was received

- 0 = General call address was not received

Hardware is set when address matches general call address. Hardware is clear at Stop detection.

- bit 8 ADD10: 10-Bit Address Status bit

- 1 = 10-bit address was matched

- 0 = 10-bit address was not matched

Hardware is set at the match of the 2nd byte of the matched 10-bit address. Hardware is clear at Stop detection.

- bit 7 IWCOL: I2Cx Write Collision Detect bit

- 1 = An attempt to write to the I2CxTRN register failed because the I2C module is busy

- 0 = No collision

Hardware is set at the occurrence of a write to I2CxTRN while busy (cleared by software).

- bit 6 I2COV: I2Cx Receive Overflow Flag bit

- 1 = A byte was received while the I2CxRCV register was still holding the previous byte

- 0 = No overflow

Hardware is set at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

- bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was a device address

Hardware is clear at a device address match. Hardware is set by reception of a slave byte.

- bit 4 **P:** Stop bit

- 1 = Indicates that a Stop bit has been detected last

- 0 = Stop bit was not detected last

Hardware is set or clear when a Start, Repeated Start or Stop is detected.

TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

| DC CH        | DC CHARACTERISTICS |                                         |      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \leq \text{TA} \leq +125^{\circ}\text{C}$ for Extended |               |    |                                                                                                               |  |  |  |

|--------------|--------------------|-----------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----|---------------------------------------------------------------------------------------------------------------|--|--|--|

| Param<br>No. | Symbol             | Characteristic                          | Min. | Тур.                                                                                                                                                                                                                                                  | o. Max. Units |    | Conditions                                                                                                    |  |  |  |

|              | lı∟                | Input Leakage Current <sup>(1,2)</sup>  |      |                                                                                                                                                                                                                                                       |               |    |                                                                                                               |  |  |  |

| DI50         |                    | I/O Pins 5V Tolerant <sup>(3)</sup>     | -1   | _                                                                                                                                                                                                                                                     | +1            | μΑ | Vss ≤ Vpin ≤ Vdd,<br>Pin at high-impedance                                                                    |  |  |  |

| DI51         |                    | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1   | _                                                                                                                                                                                                                                                     | +1            | μΑ | $Vss \leq VPIN \leq VDD, \\ Pin at high-impedance, \\ -40^{\circ}C \leq TA \leq +85^{\circ}C$                 |  |  |  |

| DI51a        |                    | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1   | _                                                                                                                                                                                                                                                     | +1            | μΑ | Analog pins shared with external reference pins, -40°C ≤ TA ≤ +85°C                                           |  |  |  |

| DI51b        |                    | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1   | _                                                                                                                                                                                                                                                     | +1            | μΑ | $Vss \leq VPIN \leq VDD, \\ Pin at high-impedance, \\ -40^{\circ}C \leq TA \leq +125^{\circ}C$                |  |  |  |

| DI51c        |                    | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1   | _                                                                                                                                                                                                                                                     | +1            | μΑ | Analog pins shared with external reference pins, $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ |  |  |  |

| DI55         |                    | MCLR                                    | -5   | _                                                                                                                                                                                                                                                     | +5            | μΑ | $Vss \leq Vpin \leq Vdd$                                                                                      |  |  |  |

| DI56         |                    | OSC1                                    | -5   | _                                                                                                                                                                                                                                                     | +5            | μΑ | VSS ≤ VPIN ≤ VDD,<br>XT and HS modes                                                                          |  |  |  |

- Note 1: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 2: Negative current is defined as current sourced by the pin.

- 3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 4: VIL source < (Vss 0.3). Characterized but not tested.

- 5: Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

- **8:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

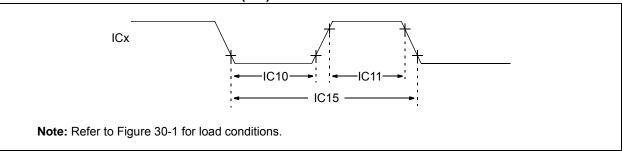

## FIGURE 30-6: INPUT CAPTURE x (ICx) TIMING CHARACTERISTICS

#### TABLE 30-26: INPUT CAPTURE x MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |      |       |                                  |                                  |  |

|--------------------|--------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------|----------------------------------|--|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup> | Min.                                                                                                                                                                                                                                             | Max. | Units | Conditions                       |                                  |  |

| IC10               | TccL   | ICx Input Low Time             | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                   | _    | ns    | Must also meet<br>Parameter IC15 |                                  |  |

| IC11               | TccH   | ICx Input High Time            | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                   | _    | ns    | Must also meet<br>Parameter IC15 | N = prescale value<br>(1, 4, 16) |  |

| IC15               | TccP   | ICx Input Period               | Greater of<br>25 + 50<br>or<br>(1 Tcy/N) + 50                                                                                                                                                                                                    | _    | ns    |                                  |                                  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

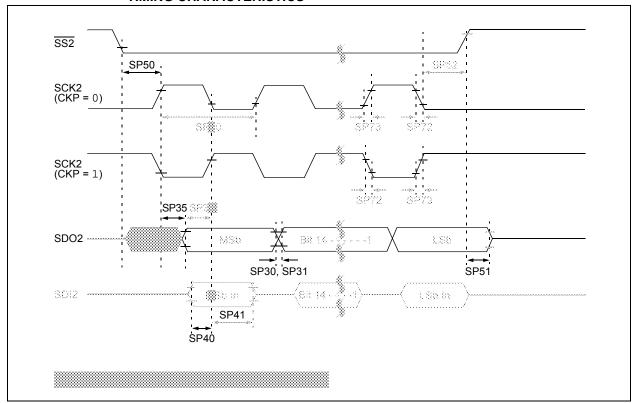

TABLE 30-38: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                            | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                     |                          |       |                             |  |

|--------------------|-----------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------|-------|-----------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>              | Min.                                                                                                                                                                                                                                             | Typ. <sup>(2)</sup> | Max.                     | Units | Conditions                  |  |

| SP70               | FscP                  | Maximum SCK2 Input<br>Frequency            | _                                                                                                                                                                                                                                                | _                   | Lesser<br>of FP<br>or 11 | MHz   | (Note 3)                    |  |

| SP72               | TscF                  | SCK2 Input Fall Time                       | _                                                                                                                                                                                                                                                | _                   | _                        | ns    | See Parameter DO32 (Note 4) |  |

| SP73               | TscR                  | SCK2 Input Rise Time                       | _                                                                                                                                                                                                                                                | _                   | _                        | ns    | See Parameter DO31 (Note 4) |  |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                 | _                                                                                                                                                                                                                                                | _                   | _                        | ns    | See Parameter DO32 (Note 4) |  |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                 | _                                                                                                                                                                                                                                                | _                   | _                        | ns    | See Parameter DO31 (Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after SCK2 Edge     | _                                                                                                                                                                                                                                                | 6                   | 20                       | ns    |                             |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to First SCK2 Edge  | 30                                                                                                                                                                                                                                               | _                   | _                        | ns    |                             |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge | 30                                                                                                                                                                                                                                               | _                   | _                        | ns    |                             |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge  | 30                                                                                                                                                                                                                                               | _                   | _                        | ns    |                             |  |

| SP50               | TssL2scH,<br>TssL2scL | SS2 ↓ to SCK2 ↑ or SCK2 ↓ Input            | 120                                                                                                                                                                                                                                              | _                   | _                        | ns    |                             |  |

| SP51               | TssH2doZ              | SS2 ↑ to SDO2 Output<br>High-Impedance     | 10                                                                                                                                                                                                                                               | _                   | 50                       | ns    | (Note 4)                    |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SS2 ↑ after SCK2 Edge                      | 1.5 Tcy + 40                                                                                                                                                                                                                                     | _                   | _                        | ns    | (Note 4)                    |  |

| SP60               | TssL2doV              | SDO2 Data Output Valid after SS2 Edge      | _                                                                                                                                                                                                                                                | _                   | 50                       | ns    |                             |  |

- **Note 1:** These parameters are characterized, but are not tested in manufacturing.

- **2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK2 is 91 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

- 4: Assumes 50 pF load on all SPI2 pins.

FIGURE 30-20: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

TABLE 31-8: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

| DC CHARACTERISTICS |        |                                                             | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)  Operating temperature -40°C ≤ TA ≤ +150°C |      |      |       |                                                |  |

|--------------------|--------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------|------|-------|------------------------------------------------|--|

| Param.             | Symbol | Characteristic                                              | Min.                                                                                                             | Тур. | Max. | Units | Conditions                                     |  |

| HDO10              | VoL    | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>    | _                                                                                                                | _    | 0.4  | V     | IOL ≤ 5 mA, VDD = 3.3V (Note 1)                |  |

|                    |        | Output Low Voltage<br>8x Sink Driver Pins <sup>(3)</sup>    | _                                                                                                                | _    | 0.4  | V     | IOL ≤ 8 mA, VDD = 3.3V (Note 1)                |  |

| HDO20              | Vон    | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 2.4                                                                                                              | _    | _    | V     | IOH ≥ -10 mA, VDD = 3.3V (Note 1)              |  |

|                    |        | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 2.4                                                                                                              | _    | _    | V     | IOH ≥ 15 mA, VDD = 3.3V (Note 1)               |  |

| HDO20A             | Vон1   | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 1.5                                                                                                              | _    | _    | V     | IOH ≥ -3.9 mA, VDD = 3.3V (Note 1)             |  |

|                    |        |                                                             | 2.0                                                                                                              | _    | _    |       | IOH ≥ -3.7 mA, VDD = 3.3V (Note 1)             |  |

|                    |        |                                                             | 3.0                                                                                                              | _    | _    |       | IOH ≥ -2 mA, VDD = 3.3V (Note 1)               |  |

|                    |        | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 1.5                                                                                                              | _    | _    | V     | IOH ≥ -7.5 mA, VDD = 3.3V (Note 1)             |  |

|                    |        |                                                             | 2.0                                                                                                              | _    | _    |       | $IOH \ge -6.8 \text{ mA}, VDD = 3.3V$ (Note 1) |  |

|                    |        |                                                             | 3.0                                                                                                              | _    | _    |       | $IOH \ge -3 \text{ mA}, VDD = 3.3V$ (Note 1)   |  |

Note 1: Parameters are characterized, but not tested.

2: Includes all I/O pins that are not 8x Sink Driver pins (see below).

3: Includes the following pins:

For devices with less than 64 pins: RA3, RA4, RA9, RB<15:7> and RC3

For 64-pin devices: RA4, RA9, RB<15:7>, RC3 and RC15