Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 256КВ (85.5К х 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256gp202-e-mm |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

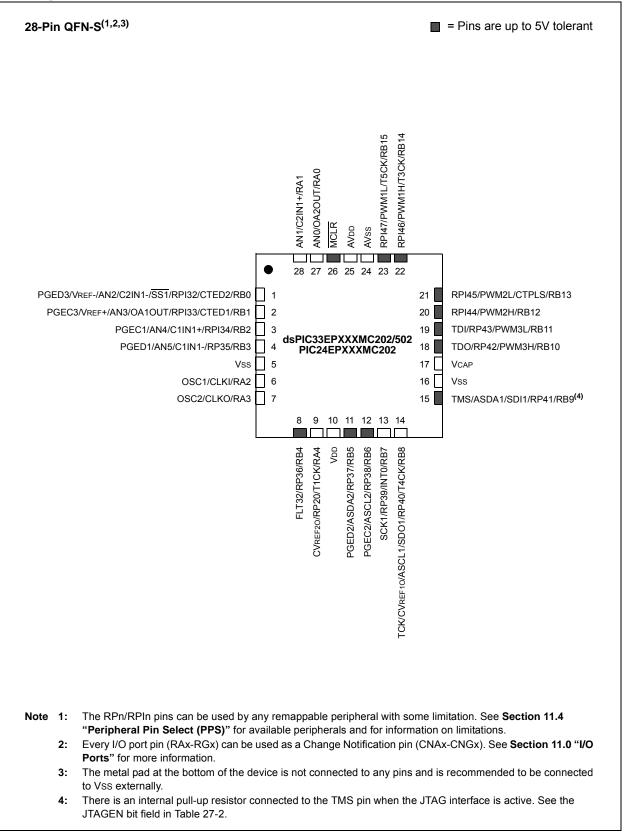

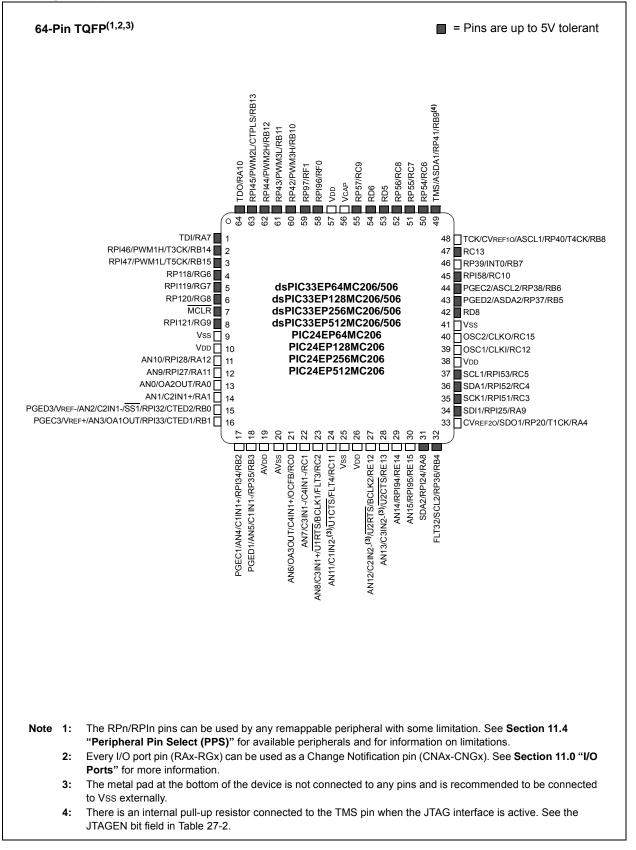

#### Pin Diagrams (Continued)

# Pin Diagrams (Continued)

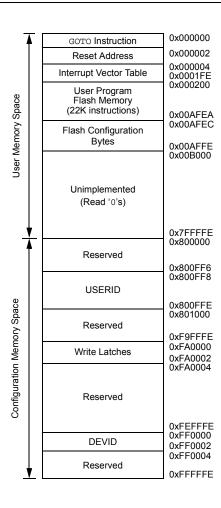

#### FIGURE 4-2: PROGRAM MEMORY MAP FOR dsPIC33EP64GP50X, dsPIC33EP64MC20X/50X AND PIC24EP64GP/MC20X DEVICES

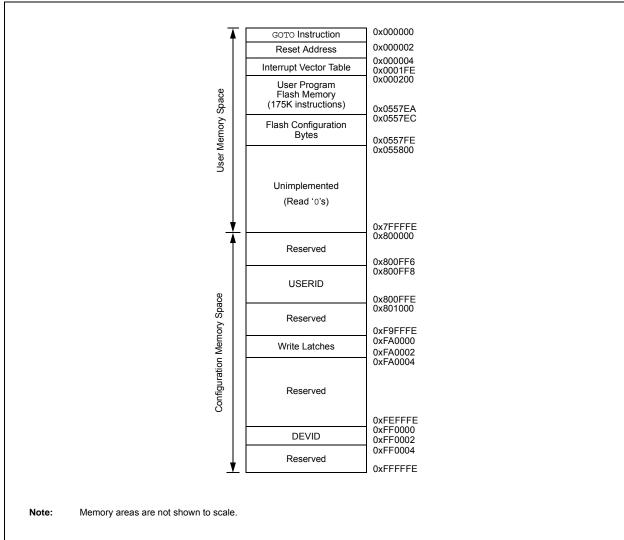

Note: Memory areas are not shown to scale.

#### FIGURE 4-5: PROGRAM MEMORY MAP FOR dsPIC33EP512GP50X, dsPIC33EP512MC20X/50X AND PIC24EP512GP/MC20X DEVICES

# 4.2 Data Address Space

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a separate 16-bit-wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps, which are presented by device family and memory size, are shown in Figure 4-7 through Figure 4-16.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes (32K words).

The base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space, which has a total address range of 16 Mbytes.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement up to 52 Kbytes of data memory (4 Kbytes of data memory for Special Function Registers and up to 48 Kbytes of data memory for RAM). If an EA points to a location outside of this area, an all-zero word or byte is returned.

# 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit-wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

# 4.2.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

# 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

|             |       |        |                   |                 |        |        |        | •            |              |               |              |       |        |       |       |       |       |               |

|-------------|-------|--------|-------------------|-----------------|--------|--------|--------|--------------|--------------|---------------|--------------|-------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14            | Bit 13          | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8        | Bit 7         | Bit 6        | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1        | 0100  |        |                   | Timer1 Register |        |        |        |              |              |               |              |       | xxxx   |       |       |       |       |               |

| PR1         | 0102  |        | Period Register 1 |                 |        |        |        |              |              |               | FFFF         |       |        |       |       |       |       |               |

| T1CON       | 0104  | TON    | _                 | TSIDL           | _      | _      | _      | _            | _            | _             | TGATE        | TCKP  | S<1:0> | —     | TSYNC | TCS   |       | 0000          |

| TMR2        | 0106  |        | Timer2 Register   |                 |        |        |        |              |              |               |              | xxxx  |        |       |       |       |       |               |

| TMR3HLD     | 0108  |        |                   |                 |        |        | Time   | er3 Holding  | Register (fo | r 32-bit time | r operations | only) |        |       |       |       |       | xxxx          |

| TMR3        | 010A  |        | Timer3 Register   |                 |        |        |        |              |              |               | xxxx         |       |        |       |       |       |       |               |

| PR2         | 010C  |        | Period Register 2 |                 |        |        |        |              |              | FFFF          |              |       |        |       |       |       |       |               |

| PR3         | 010E  |        |                   |                 |        |        |        |              | Period F     | Register 3    |              |       |        |       |       |       |       | FFFF          |

| T2CON       | 0110  | TON    | —                 | TSIDL           | —      | —      | —      | _            | —            | —             | TGATE        | TCKP  | S<1:0> | T32   | _     | TCS   |       | 0000          |

| T3CON       | 0112  | TON    | -                 | TSIDL           | _      | _      | _      | _            | -            | _             | TGATE        | TCKP  | S<1:0> | _     | _     | TCS   |       | 0000          |

| TMR4        | 0114  |        |                   | •               | •      | •      | •      | •            | Timer4       | Register      |              |       |        | •     | •     | •     |       | xxxx          |

| TMR5HLD     | 0116  |        |                   |                 |        |        | Т      | imer5 Holdir | ng Register  | (for 32-bit o | perations on | ly)   |        |       |       |       |       | xxxx          |

| TMR5        | 0118  |        |                   |                 |        |        |        |              | Timer5       | Register      |              |       |        |       |       |       |       | xxxx          |

| PR4         | 011A  |        | Period Register 4 |                 |        |        |        |              |              |               | FFFF         |       |        |       |       |       |       |               |

| PR5         | 011C  |        |                   |                 |        |        |        |              | Period F     | Register 5    |              |       |        |       |       |       |       | FFFF          |

| T4CON       | 011E  | TON    | —                 | TSIDL           | —      | —      | —      | —            | _            | —             | TGATE        | TCKP  | S<1:0> | T32   | —     | TCS   | —     | 0000          |

| T5CON       | 0120  | TON    | _                 | TSIDL           | _      | _      | _      | _            | _            | _             | TGATE        | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

# TABLE 4-8: TIMER1 THROUGH TIMER5 REGISTER MAP

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4 | 4-31: | PER | IPHERA | L PIN S | ELECT | INPUT F | REGISTI | ER MAP | FOR de | sPIC33E | EPXXXG | P50X D | EVICES | SONLY |  |

|---------|-------|-----|--------|---------|-------|---------|---------|--------|--------|---------|--------|--------|--------|-------|--|

|         |       |     |        |         |       |         |         |        |        |         |        |        |        |       |  |

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13                | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6       | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|-----------------------|--------|------------|--------|-------|-------|-------|-------------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR0       | 06A0  | —      |        | INT1R<6:0>            |        |            |        |       |       |       | _           | —     | —     | —          | —     | —     | _     | 0000          |

| RPINR1       | 06A2  |        | _      | _                     | _      | _          | _      | _     | _     | _     |             |       |       | INT2R<6:0> | •     |       |       | 0000          |

| RPINR3       | 06A6  |        | _      | _                     | _      | _          | _      | _     | _     | _     |             |       | ٦     | [2CKR<6:0  | >     |       |       | 0000          |

| RPINR7       | 06AE  |        |        | IC2R<6:0> — IC1R<6:0> |        |            |        |       |       |       |             | 0000  |       |            |       |       |       |               |

| RPINR8       | 06B0  |        |        | IC4R<6:0>             |        |            |        |       |       |       | IC3R<6:0>   |       |       |            |       |       | 0000  |               |

| RPINR11      | 06B6  |        | _      | _                     | _      | _          | _      | _     | _     | _     |             |       | (     | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR18      | 06C4  |        | _      | _                     | _      | _          | _      | _     | _     | _     |             |       | ι     | J1RXR<6:0  | >     |       |       | 0000          |

| RPINR19      | 06C6  |        | _      | _                     | _      | _          | _      | _     | _     | _     |             |       | ι     | J2RXR<6:0  | >     |       |       | 0000          |

| RPINR22      | 06CC  |        |        |                       | S      | CK2INR<6:0 | )>     |       |       | _     | SDI2R<6:0>  |       |       |            |       |       |       | 0000          |

| RPINR23      | 06CE  | _      | _      | _                     | —      | —          | _      | _     | —     | —     | - SS2R<6:0> |       |       |            |       |       | 0000  |               |

| RPINR26      | 06D4  | —      | _      | _                     | -      | _          | _      | —     |       | —     |             |       | (     | C1RXR<6:0  | >     |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **TABLE 4-32:** PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File Name | Addr. | Bit 15 | Bit 14     | Bit 13       | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6       | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|------------|--------------|--------|------------|--------|-------|-------|-------|-------------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR0    | 06A0  | _      |            | INT1R<6:0>   |        |            |        |       |       | —     | —           | —     | —     | —          | —     | —     | _     | 0000          |

| RPINR1    | 06A2  |        | _          |              |        |            |        |       |       | _     |             |       |       | INT2R<6:0> |       |       |       | 0000          |

| RPINR3    | 06A6  |        | _          | _            | _      | _          | _      | _     | _     | _     |             |       | -     | F2CKR<6:0  | >     |       |       | 0000          |

| RPINR7    | 06AE  |        |            |              |        | IC2R<6:0>  |        |       |       | _     |             |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8    | 06B0  |        |            |              |        | IC4R<6:0>  |        |       |       | _     |             |       |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11   | 06B6  |        | _          | _            | _      | _          | _      | _     | _     | _     |             |       | (     | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR12   | 06B8  |        |            | FLT2R<6:0>   |        |            |        |       |       | _     | FLT1R<6:0>  |       |       |            |       |       | 0000  |               |

| RPINR14   | 06BC  |        |            |              | (      | QEB1R<6:0  | >      |       |       | _     | QEA1R<6:0>  |       |       |            |       |       | 0000  |               |

| RPINR15   | 06BE  |        |            |              | Н      | OME1R<6:0  | )>     |       |       | _     | INDX1R<6:0> |       |       |            |       |       |       | 0000          |

| RPINR18   | 06C4  |        | _          | _            | _      | _          | _      | _     | _     | _     | U1RXR<6:0>  |       |       |            |       |       | 0000  |               |

| RPINR19   | 06C6  |        | _          | _            | _      | _          | _      | _     | _     | _     | U2RXR<6:0>  |       |       |            |       |       | 0000  |               |

| RPINR22   | 06CC  | _      |            |              | S      | CK2INR<6:( | )>     |       |       | —     |             |       |       | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23   | 06CE  | _      | —          | —            |        | —          | —      |       | —     | —     |             |       |       | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26   | 06D4  | _      | C1RXR<6:0> |              |        |            |        |       |       |       | 0000        |       |       |            |       |       |       |               |

| RPINR37   | 06EA  | _      |            | SYNCI1R<6:0> |        |            |        |       |       | —     | —           | —     | —     | —          |       |       |       | 0000          |

| RPINR38   | 06EC  | _      |            | DTCMP1R<6:0> |        |            |        |       |       | —     | —           | —     | —     | _          |       |       |       | 0000          |

| RPINR39   | 06EE  | _      |            | DTCMP3R<6:0> |        |            |        |       |       | _     |             |       | D     | CMP2R<6:   | 0>    |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

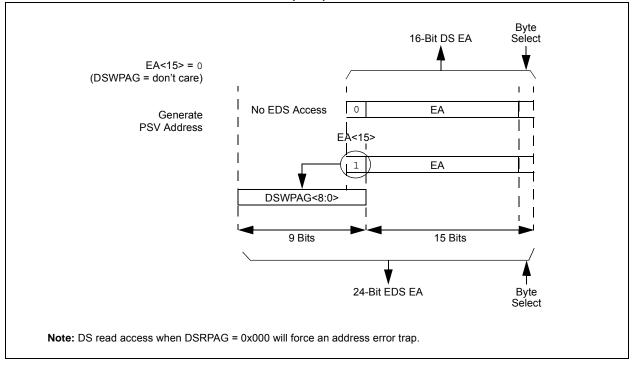

#### EXAMPLE 4-2: EXTENDED DATA SPACE (EDS) WRITE ADDRESS GENERATION

The paged memory scheme provides access to multiple 32-Kbyte windows in the EDS and PSV memory. The Data Space Page registers, DSxPAG, in combination with the upper half of the Data Space address, can provide up to 16 Mbytes of additional address space in the EDS and 8 Mbytes (DSRPAG only) of PSV address space. The paged data memory space is shown in Example 4-3.

The Program Space (PS) can be accessed with a DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG. Writes to PS are not supported, so DSWPAG is dedicated to DS, including EDS only. The Data Space and EDS can be read from, and written to, using DSRPAG and DSWPAG, respectively.

| U-0          | U-0                         | U-0                                          | U-0            | U-0              | U-0              | U-0             | U-0   |

|--------------|-----------------------------|----------------------------------------------|----------------|------------------|------------------|-----------------|-------|

| -            | —                           | —                                            | —              | —                | —                | —               | —     |

| bit 15       |                             |                                              |                |                  |                  |                 | bit 8 |

| U-0          | U-0                         | U-0                                          | U-0            | R-1              | R-1              | R-1             | R-1   |

| _            | _                           | _                                            | _              |                  | LSTC             | H<3:0>          |       |

| bit 7        |                             |                                              |                |                  |                  |                 | bit 0 |

| Legend:      |                             |                                              |                |                  |                  |                 |       |

| R = Readat   | ole bit                     | W = Writable                                 | bit            | U = Unimpler     | mented bit, read | 1 as '0'        |       |

| -n = Value a | at POR                      | '1' = Bit is set                             |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|              |                             |                                              |                |                  |                  |                 |       |

| bit 15-4     | Unimplemen                  | ted: Read as '                               | 0'             |                  |                  |                 |       |

| bit 3-0      | LSTCH<3:0>                  | : Last DMAC C                                | hannel Active  | e Status bits    |                  |                 |       |

|              | 1111 = No DI<br>1110 = Rese | MA transfer has<br>rved                      | s occurred sir | nce system Res   | set              |                 |       |

|              | •                           |                                              |                |                  |                  |                 |       |

|              | •                           |                                              |                |                  |                  |                 |       |

|              | •                           |                                              |                |                  |                  |                 |       |

|              |                             | rved<br>data transfer wa<br>data transfer wa |                |                  |                  |                 |       |

|              |                             | data transfer wa                             |                |                  |                  |                 |       |

# REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

0001 = Last data transfer was handled by Channel 0 0000 = Last data transfer was handled by Channel 0

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER     | <u>R 10-2: PMD</u> 2                                                                                           | 2: PERIPHER                                                                     | AL MODULE       | DISABLE C         | ONTROL RE       | GISTER 2        |       |  |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------|-------------------|-----------------|-----------------|-------|--|--|--|--|--|--|

| U-0          | U-0                                                                                                            | U-0                                                                             | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |  |

| _            |                                                                                                                | _                                                                               |                 | IC4MD             | IC3MD           | IC2MD           | IC1MD |  |  |  |  |  |  |

| bit 15       |                                                                                                                |                                                                                 |                 |                   |                 |                 | bit   |  |  |  |  |  |  |

| U-0          | U-0                                                                                                            | U-0                                                                             | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |  |

|              |                                                                                                                |                                                                                 |                 | OC4MD             | OC3MD           | OC2MD           | OC1MD |  |  |  |  |  |  |

| bit 7        |                                                                                                                |                                                                                 |                 |                   |                 |                 | bit   |  |  |  |  |  |  |

|              |                                                                                                                |                                                                                 |                 |                   |                 |                 |       |  |  |  |  |  |  |

| Legend:      | 1.1.1                                                                                                          |                                                                                 |                 |                   |                 |                 |       |  |  |  |  |  |  |

| R = Readab   |                                                                                                                | W = Writable b                                                                  | Dit             | •                 | nented bit, rea |                 |       |  |  |  |  |  |  |

| -n = Value a | at POR                                                                                                         | '1' = Bit is set                                                                |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |  |  |  |  |  |  |

| bit 15-12    | Unimplemen                                                                                                     | ted: Read as '0                                                                 | ,               |                   |                 |                 |       |  |  |  |  |  |  |

| bit 11       | -                                                                                                              | t Capture 4 Mod                                                                 |                 |                   |                 |                 |       |  |  |  |  |  |  |

|              | •                                                                                                              | oture 4 module is                                                               |                 |                   |                 |                 |       |  |  |  |  |  |  |

|              | 0 = Input Cap                                                                                                  | 0 = Input Capture 4 module is enabled                                           |                 |                   |                 |                 |       |  |  |  |  |  |  |

| bit 10       | IC3MD: Input Capture 3 Module Disable bit                                                                      |                                                                                 |                 |                   |                 |                 |       |  |  |  |  |  |  |

|              |                                                                                                                | 1 = Input Capture 3 module is disabled<br>0 = Input Capture 3 module is enabled |                 |                   |                 |                 |       |  |  |  |  |  |  |

|              |                                                                                                                |                                                                                 |                 |                   |                 |                 |       |  |  |  |  |  |  |

| bit 9        |                                                                                                                | t Capture 2 Mod                                                                 |                 |                   |                 |                 |       |  |  |  |  |  |  |

|              |                                                                                                                | oture 2 module is<br>oture 2 module is                                          |                 |                   |                 |                 |       |  |  |  |  |  |  |

| bit 8        | IC1MD: Input                                                                                                   | t Capture 1 Mod                                                                 | ule Disable bit |                   |                 |                 |       |  |  |  |  |  |  |

|              | 1 = Input Cap                                                                                                  | oture 1 module is<br>oture 1 module is                                          | s disabled      |                   |                 |                 |       |  |  |  |  |  |  |

| bit 7-4      |                                                                                                                | ted: Read as '0                                                                 |                 |                   |                 |                 |       |  |  |  |  |  |  |

| bit 3        | OC4MD: Out                                                                                                     | put Compare 4                                                                   | Module Disable  | e bit             |                 |                 |       |  |  |  |  |  |  |

|              |                                                                                                                | ompare 4 modul                                                                  |                 |                   |                 |                 |       |  |  |  |  |  |  |

|              | -                                                                                                              | ompare 4 modu                                                                   |                 |                   |                 |                 |       |  |  |  |  |  |  |

| bit 2        |                                                                                                                | put Compare 3                                                                   |                 | e bit             |                 |                 |       |  |  |  |  |  |  |

|              | 1 = Output Compare 3 module is disabled                                                                        |                                                                                 |                 |                   |                 |                 |       |  |  |  |  |  |  |

| L:1 4        | <ul> <li>0 = Output Compare 3 module is enabled</li> <li>OC2MD: Output Compare 2 Module Disable bit</li> </ul> |                                                                                 |                 |                   |                 |                 |       |  |  |  |  |  |  |

| bit 1        |                                                                                                                |                                                                                 |                 |                   |                 |                 |       |  |  |  |  |  |  |

|              | $\perp$ – Output Co                                                                                            | ompare 2 modu                                                                   |                 |                   |                 |                 |       |  |  |  |  |  |  |

|              | 0 = Output Co                                                                                                  | ompare 2 modul                                                                  | le is enabled   |                   |                 |                 |       |  |  |  |  |  |  |

| bit 0        |                                                                                                                | ompare 2 modul<br>put Compare 1                                                 |                 | e bit             |                 |                 |       |  |  |  |  |  |  |

| bit 0        | OC1MD: Out                                                                                                     | ompare 2 modul<br>put Compare 1 l<br>ompare 1 modul                             | Module Disable  | e bit             |                 |                 |       |  |  |  |  |  |  |

#### ~

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRIS setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRIS settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Pin Select registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Pin Select registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

### 11.6 I/O Ports Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 11.6.1 KEY RESOURCES

- "I/O Ports" (DS70598) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| REGISTER 16-2: | PTCON2: PWMx PRIMARY MASTER CLOCK DIVIDER SELECT REGISTER 2 |

|----------------|-------------------------------------------------------------|

|----------------|-------------------------------------------------------------|

| U-0             | U-0        | U-0              | U-0 | U-0              | U-0                     | U-0                     | U-0         |  |  |

|-----------------|------------|------------------|-----|------------------|-------------------------|-------------------------|-------------|--|--|

| —               | —          | —                | _   | —                | —                       | —                       | _           |  |  |

| bit 15          |            |                  |     |                  |                         |                         | bit 8       |  |  |

|                 |            |                  |     |                  |                         |                         |             |  |  |

| U-0             | U-0        | U-0              | U-0 | U-0              | R/W-0                   | R/W-0                   | R/W-0       |  |  |

| —               | —          | —                | -   | —                | PCLKDIV2 <sup>(1)</sup> | PCLKDIV1 <sup>(1)</sup> | PCLKDIV0(1) |  |  |

| bit 7           |            |                  |     |                  |                         |                         | bit 0       |  |  |

|                 |            |                  |     |                  |                         |                         |             |  |  |

| Legend:         |            |                  |     |                  |                         |                         |             |  |  |

| R = Readable    | bit        | W = Writable     | bit | U = Unimpler     | mented bit, read        | as '0'                  |             |  |  |

| -n = Value at F | POR        | '1' = Bit is set |     | '0' = Bit is cle | ared                    | x = Bit is unknown      |             |  |  |

|                 |            |                  |     |                  |                         |                         |             |  |  |

| bit 15-3        | Unimplemen | ted: Read as '   | י'  |                  |                         |                         |             |  |  |

#### bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved 110 = Divide-by-64 101 = Divide-by-32

- 100 = Divide-by-32100 = Divide-by-16

- 011 = Divide-by-8

- 010 = Divide-by-4

- 001 = Divide-by-2

- 000 = Divide-by-1, maximum PWMx timing resolution (power-on default)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

| REGISTER              | 16-7: PWMC                             | CONX: PWMX (                               | CONTROL R                    | EGISTER          |                      |                      |                     |  |

|-----------------------|----------------------------------------|--------------------------------------------|------------------------------|------------------|----------------------|----------------------|---------------------|--|

| HS/HC-0               | HS/HC-0                                | HS/HC-0                                    | R/W-0                        | R/W-0            | R/W-0                | R/W-0                | R/W-0               |  |

| FLTSTAT <sup>(1</sup> | ) CLSTAT <sup>(1)</sup>                | TRGSTAT                                    | FLTIEN                       | CLIEN            | TRGIEN               | ITB <sup>(2)</sup>   | MDCS <sup>(2)</sup> |  |

| bit 15                |                                        |                                            |                              |                  |                      |                      | bit 8               |  |

| R/W-0                 | R/W-0                                  | R/W-0                                      | U-0                          | R/W-0            | R/W-0                | R/W-0                | R/W-0               |  |

| DTC1                  |                                        | DTCP <sup>(3)</sup>                        | 0-0                          | MTBS             | CAM <sup>(2,4)</sup> | XPRES <sup>(5)</sup> | IUE <sup>(2)</sup>  |  |

|                       | DTC0                                   | DICPO                                      |                              | MIB3             | CAIM                 | APRES.               | -                   |  |

| bit 7                 |                                        |                                            |                              |                  |                      |                      | bit                 |  |

| Legend:               |                                        | HC = Hardware                              | Clearable bit                | HS = Hardwa      | are Settable bit     |                      |                     |  |

| R = Readab            | le bit                                 | W = Writable b                             | it                           | U = Unimple      | mented bit, rea      | d as '0'             |                     |  |

| -n = Value a          | t POR                                  | '1' = Bit is set                           |                              | '0' = Bit is cle | eared                | x = Bit is unk       | nown                |  |

|                       |                                        |                                            | (1)                          |                  |                      |                      |                     |  |

| bit 15                |                                        | ult Interrupt State                        | us bit"                      |                  |                      |                      |                     |  |

|                       |                                        | rrupt is pending<br>interrupt is pendi     | ina                          |                  |                      |                      |                     |  |

|                       |                                        | ared by setting F                          |                              |                  |                      |                      |                     |  |

| bit 14                | CLSTAT: Cur                            | rent-Limit Interru                         | pt Status bit <sup>(1)</sup> |                  |                      |                      |                     |  |

|                       | 1 = Current-limit interrupt is pending |                                            |                              |                  |                      |                      |                     |  |

|                       |                                        | nt-limit interrupt is                      | •                            |                  |                      |                      |                     |  |

| 1.11.40               |                                        | ared by setting C                          |                              |                  |                      |                      |                     |  |

| bit 13                |                                        | igger Interrupt S<br>terrupt is pendin     |                              |                  |                      |                      |                     |  |

|                       |                                        | r interrupt is pendin                      |                              |                  |                      |                      |                     |  |

|                       |                                        | ared by setting T                          |                              |                  |                      |                      |                     |  |

| bit 12                | FLTIEN: Faul                           | it Interrupt Enabl                         | e bit                        |                  |                      |                      |                     |  |

|                       |                                        | rrupt is enabled                           |                              |                  |                      |                      |                     |  |

|                       |                                        | rrupt is disabled                          |                              | TAT bit is clear | ed                   |                      |                     |  |

| bit 11                |                                        | ent-Limit Interrup                         |                              |                  |                      |                      |                     |  |

|                       |                                        | mit interrupt is er<br>mit interrupt is di |                              | e CI STAT bit is | s cleared            |                      |                     |  |

| bit 10                |                                        | ger Interrupt En                           |                              |                  |                      |                      |                     |  |

|                       | -                                      | event generates                            |                              | quest            |                      |                      |                     |  |

|                       | 0 = Trigger ev                         | vent interrupts ar                         | e disabled and               |                  | Γ bit is cleared     |                      |                     |  |

| bit 9                 | ITB: Indepen                           | dent Time Base                             | Mode bit <sup>(2)</sup>      |                  |                      |                      |                     |  |

|                       | 1 = PHASEx                             | register provides                          | s time base pe               |                  | 0                    |                      |                     |  |

| bit 8                 |                                        | er Duty Cycle Re                           |                              |                  |                      |                      |                     |  |

| bito                  |                                        | ister provides du                          | •                            |                  | WM generator         |                      |                     |  |

|                       |                                        | jister provides du                         |                              |                  |                      | ·                    |                     |  |

| Note 1: S             | oftware must clea                      | ar the interrupt s                         | tatus here and               | in the corresp   | onding IFSx bit      | in the interrup      | t controller.       |  |

| <b>2:</b> T           | hese bits should                       | not be changed                             | after the PWM                | x is enabled (F  | PTEN = 1).           |                      |                     |  |

|                       | DTC<1:0> = 11 fo                       |                                            |                              | •                |                      |                      |                     |  |

|                       | he Independent ∃<br>AM bit is ignored  |                                            | = 1) mode mus                | t be enabled to  | o use Center-Al      | igned mode. If       | TB = 0, the         |  |

|                       | o operate in Exte                      |                                            | et mode, the IT              | B bit must be '  | 1' and the CLM       | 10D bit in the I     | FCLCONx             |  |

# REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER

5: To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

#### REGISTER 20-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement is disabled or completed</li> </ul> |

| bit 4   | URXINV: UARTx Receive Polarity Inversion bit                                                                                                                                                                                              |

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                                                  |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                                                                           |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul>                                                        |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                                                                                |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                                                                             |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                                                                             |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                                                                                     |

|         | Refer to the " <b>UART</b> " (DS70582) section in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for receive or transmit operation.                                                             |

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

- 3: This feature is only available on 44-pin and 64-pin devices.

- 4: This feature is only available on 64-pin devices.

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax        |                               | Description                                                | # of<br>Words<br>1 | # of<br>Cycles <sup>(2)</sup><br>1 | Status Flags<br>Affected<br>OA,OB,OAB,<br>SA,SB,SAB |

|--------------------|----------------------|------------------------|-------------------------------|------------------------------------------------------------|--------------------|------------------------------------|-----------------------------------------------------|

| 53                 | NEG                  | NEG ACC <sup>(1)</sup> |                               | Negate Accumulator                                         |                    |                                    |                                                     |

|                    |                      | NEG                    | f                             | $f = \overline{f} + 1$                                     | 1                  | 1                                  | C,DC,N,OV,Z                                         |

|                    |                      | NEG                    | f,WREG                        | WREG = $\overline{f}$ + 1                                  | 1                  | 1                                  | C,DC,N,OV,Z                                         |

|                    |                      | NEG                    | Ws,Wd                         | $Wd = \overline{Ws} + 1$                                   | 1                  | 1                                  | C,DC,N,OV,Z                                         |

| 54                 | NOP                  | NOP                    |                               | No Operation                                               | 1                  | 1                                  | None                                                |

|                    |                      | NOPR                   |                               | No Operation                                               | 1                  | 1                                  | None                                                |

| 55                 | POP                  | POP                    | f                             | Pop f from Top-of-Stack (TOS)                              | 1                  | 1                                  | None                                                |

|                    |                      | POP                    | Wdo                           | Pop from Top-of-Stack (TOS) to Wdo                         | 1                  | 1                                  | None                                                |

|                    |                      | POP.D                  | Wnd                           | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1)          | 1                  | 2                                  | None                                                |

|                    |                      | POP.S                  |                               | Pop Shadow Registers                                       | 1                  | 1                                  | All                                                 |

| 56                 | PUSH                 | PUSH                   | f                             | Push f to Top-of-Stack (TOS)                               | 1                  | 1                                  | None                                                |

|                    |                      | PUSH                   | Wso                           | Push Wso to Top-of-Stack (TOS)                             | 1                  | 1                                  | None                                                |

|                    |                      | PUSH.D                 | Wns                           | Push W(ns):W(ns + 1) to Top-of-Stack<br>(TOS)              | 1                  | 2                                  | None                                                |

|                    |                      | PUSH.S                 |                               | Push Shadow Registers                                      | 1                  | 1                                  | None                                                |

| 57                 | PWRSAV               | PWRSAV                 | #lit1                         | Go into Sleep or Idle mode                                 | 1                  | 1                                  | WDTO,Sleep                                          |

| 58                 | RCALL                | RCALL                  | Expr                          | Relative Call                                              | 1                  | 4                                  | SFA                                                 |

|                    |                      | RCALL                  | Wn                            | Computed Call                                              | 1                  | 4                                  | SFA                                                 |

| 59                 | REPEAT               | REPEAT                 | #lit15                        | Repeat Next Instruction lit15 + 1 times                    | 1                  | 1                                  | None                                                |

|                    |                      | REPEAT                 | Wn                            | Repeat Next Instruction (Wn) + 1 times                     | 1                  | 1                                  | None                                                |

| 60                 | RESET                | RESET                  |                               | Software device Reset                                      | 1                  | 1                                  | None                                                |

| 61                 | RETFIE               | RETFIE                 |                               | Return from interrupt                                      | 1                  | 6 (5)                              | SFA                                                 |

| 62                 | RETLW                | RETLW                  | #lit10,Wn                     | Return with literal in Wn                                  | 1                  | 6 (5)                              | SFA                                                 |

| 63                 | RETURN               | RETURN                 |                               | Return from Subroutine                                     | 1                  | 6 (5)                              | SFA                                                 |

| 64                 | RLC                  | RLC                    | f                             | f = Rotate Left through Carry f                            | 1                  | 1                                  | C,N,Z                                               |

|                    |                      | RLC                    | f,WREG                        | WREG = Rotate Left through Carry f                         | 1                  | 1                                  | C,N,Z                                               |

|                    |                      | RLC                    | Ws,Wd                         | Wd = Rotate Left through Carry Ws                          | 1                  | 1                                  | C,N,Z                                               |

| 65                 | RLNC                 | RLNC                   | f                             | f = Rotate Left (No Carry) f                               | 1                  | 1                                  | N,Z                                                 |

|                    |                      | RLNC                   | f,WREG                        | WREG = Rotate Left (No Carry) f                            | 1                  | 1                                  | N,Z                                                 |

|                    |                      | RLNC                   | Ws,Wd                         | Wd = Rotate Left (No Carry) Ws                             | 1                  | 1                                  | N,Z                                                 |

| 66                 | RRC                  | RRC                    | f                             | f = Rotate Right through Carry f                           | 1                  | 1                                  | C,N,Z                                               |

|                    |                      | RRC                    | f,WREG                        | WREG = Rotate Right through Carry f                        | 1                  | 1                                  | C,N,Z                                               |

|                    |                      | RRC                    | Ws,Wd                         | Wd = Rotate Right through Carry Ws                         | 1                  | 1                                  | C,N,Z                                               |

| 67                 | RRNC                 | RRNC                   | f                             | f = Rotate Right (No Carry) f                              | 1                  | 1                                  | N,Z                                                 |

|                    |                      | RRNC                   | f,WREG                        | WREG = Rotate Right (No Carry) f                           | 1                  | 1                                  | N,Z                                                 |

| ~~                 |                      | RRNC                   | Ws,Wd                         | Wd = Rotate Right (No Carry) Ws                            | 1                  | 1                                  | N,Z                                                 |

| 68                 | SAC                  | SAC                    | Acc,#Slit4,Wdo <sup>(1)</sup> | Store Accumulator                                          | 1                  | 1                                  | None                                                |

| <u></u>            |                      | SAC.R                  | Acc,#Slit4,Wdo <sup>(1)</sup> | Store Rounded Accumulator                                  | 1                  | 1                                  | None                                                |

| 69                 | SE                   | SE                     | Ws,Wnd                        | Wnd = sign-extended Ws                                     | 1                  | 1                                  | C,N,Z                                               |

| 70                 | SETM                 | SETM                   | f                             | f = 0xFFFF                                                 | 1                  | 1                                  | None                                                |

|                    |                      | SETM                   | WREG                          | WREG = 0xFFFF                                              | 1                  | 1                                  | None                                                |

| 71                 | SFTAC                | SETM                   | Ws<br>Acc, Wn <sup>(1)</sup>  | Ws = 0xFFFF           Arithmetic Shift Accumulator by (Wn) | 1                  | 1<br>1                             | None<br>OA,OB,OAB                                   |

|                    |                      | SFTAC                  | Acc,#Slit6 <sup>(1)</sup>     | Arithmetic Shift Accumulator by Slit6                      | 1                  | 1                                  | SA,SB,SAB<br>OA,OB,OAB<br>SA,SB,SAB                 |

# TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

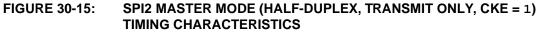

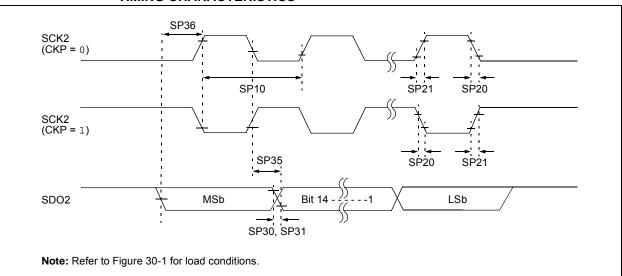

#### TABLE 30-34: SPI2 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |                                |

|--------------------|-----------------------|----------------------------------------------|-------------------------------------------------------|---------------------|------|-------|--------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                  | Typ. <sup>(2)</sup> | Max. | Units | Conditions                     |

| SP10               | FscP                  | Maximum SCK2 Frequency                       | _                                                     | _                   | 15   | MHz   | (Note 3)                       |

| SP20               | TscF                  | SCK2 Output Fall Time                        | —                                                     | —                   | _    | ns    | See Parameter DO32<br>(Note 4) |

| SP21               | TscR                  | SCK2 Output Rise Time                        | —                                                     | —                   | _    | ns    | See Parameter DO31<br>(Note 4) |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                   | —                                                     | —                   | _    | ns    | See Parameter DO32<br>(Note 4) |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                   | -                                                     | _                   |      | ns    | See Parameter DO31<br>(Note 4) |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge    | —                                                     | 6                   | 20   | ns    |                                |

| SP36               | TdiV2scH,<br>TdiV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge | 30                                                    | —                   | _    | ns    |                                |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPI2 pins.

| AC CHARA             | CTERISTICS                               |                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |     |  |  |

|----------------------|------------------------------------------|---------------------------------------------|-------------------------------------------------------|-----|-----|-----|--|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)            | CKE | СКР | SMP |  |  |

| 15 MHz               | Table 30-42                              | _                                           | _                                                     | 0,1 | 0,1 | 0,1 |  |  |

| 10 MHz               | _                                        | Table 30-43                                 | —                                                     | 1   | 0,1 | 1   |  |  |

| 10 MHz               | —                                        | Table 30-44                                 | —                                                     | 0   | 0,1 | 1   |  |  |

| 15 MHz               | —                                        | —                                           | Table 30-45                                           | 1   | 0   | 0   |  |  |

| 11 MHz               | —                                        | —                                           | Table 30-46                                           | 1   | 1   | 0   |  |  |

| 15 MHz               | _                                        | —                                           | Table 30-47                                           | 0   | 1   | 0   |  |  |

| 11 MHz               | _                                        | —                                           | Table 30-48                                           | 0   | 0   | 0   |  |  |

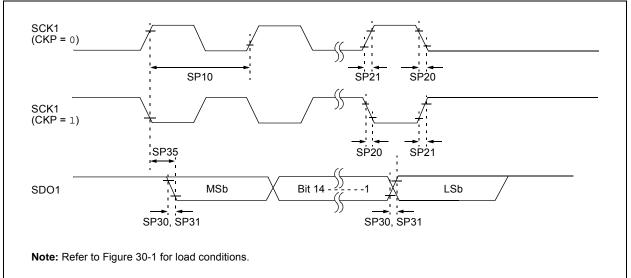

#### TABLE 30-41: SPI1 MAXIMUM DATA/CLOCK RATE SUMMARY

#### FIGURE 30-22: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

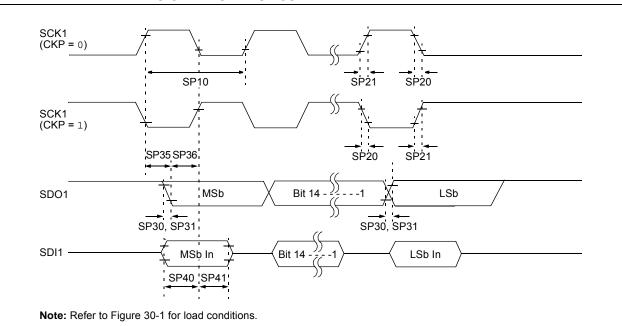

# TABLE 30-44:SPI1 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                             |  |

|--------------------|-----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                 | Min.                                                                                                                                                                                                                                                                                    | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |  |

| SP10               | FscP                  | Maximum SCK1 Frequency                        |                                                                                                                                                                                                                                                                                         | —                   | 10   | MHz   | -40°C to +125°C<br>(Note 3) |  |

| SP20               | TscF                  | SCK1 Output Fall Time                         | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP21               | TscR                  | SCK1 Output Rise Time                         | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                    | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                    | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge     | _                                                                                                                                                                                                                                                                                       | 6                   | 20   | ns    |                             |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge  | 30                                                                                                                                                                                                                                                                                      | —                   | _    | ns    |                             |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data<br>Input to SCK1 Edge | 30                                                                                                                                                                                                                                                                                      | —                   | _    | ns    |                             |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge     | 30                                                                                                                                                                                                                                                                                      | —                   | —    | ns    |                             |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK1 is 100 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI1 pins.

NOTES: