Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

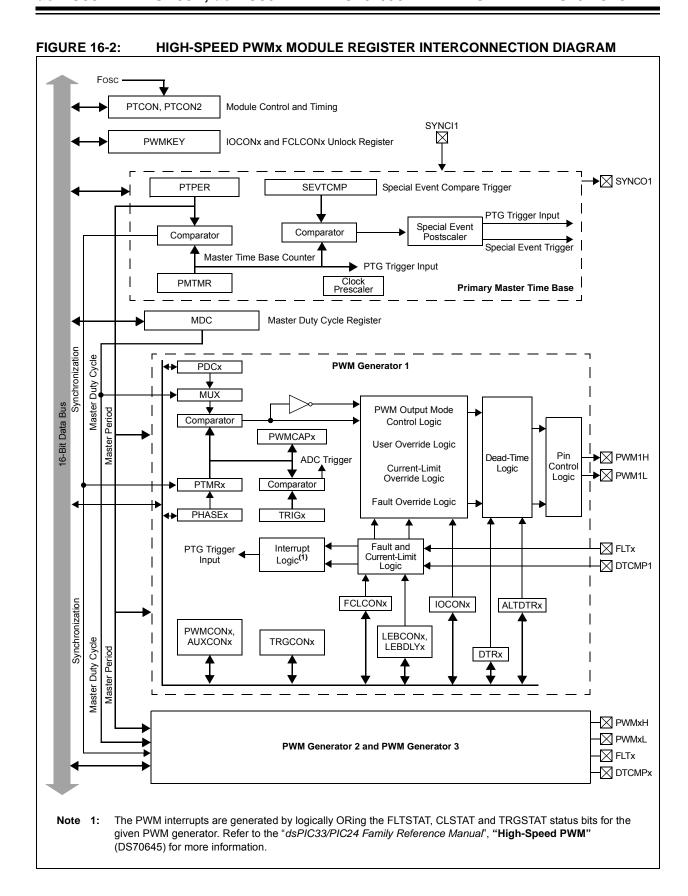

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256gp202-e-so |

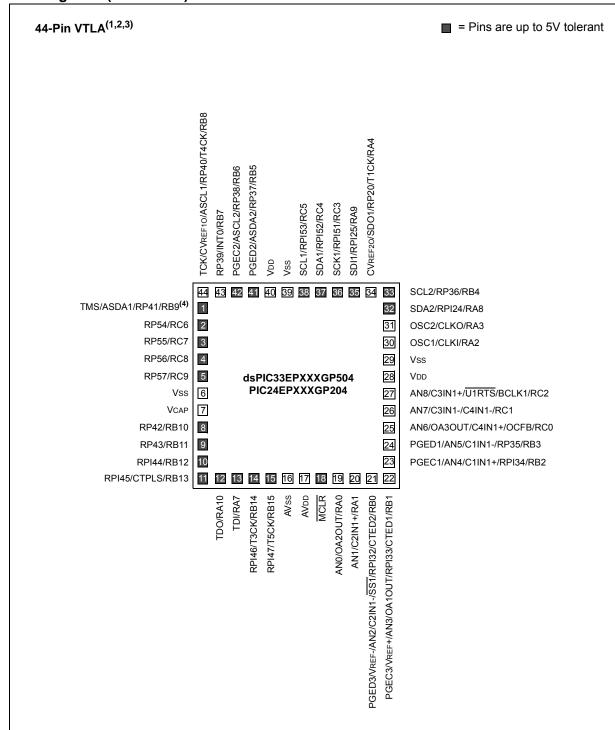

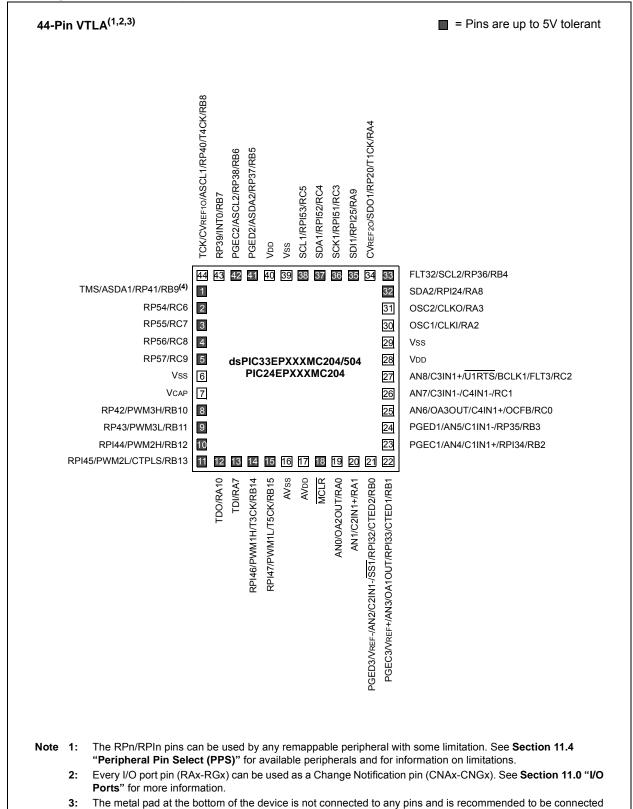

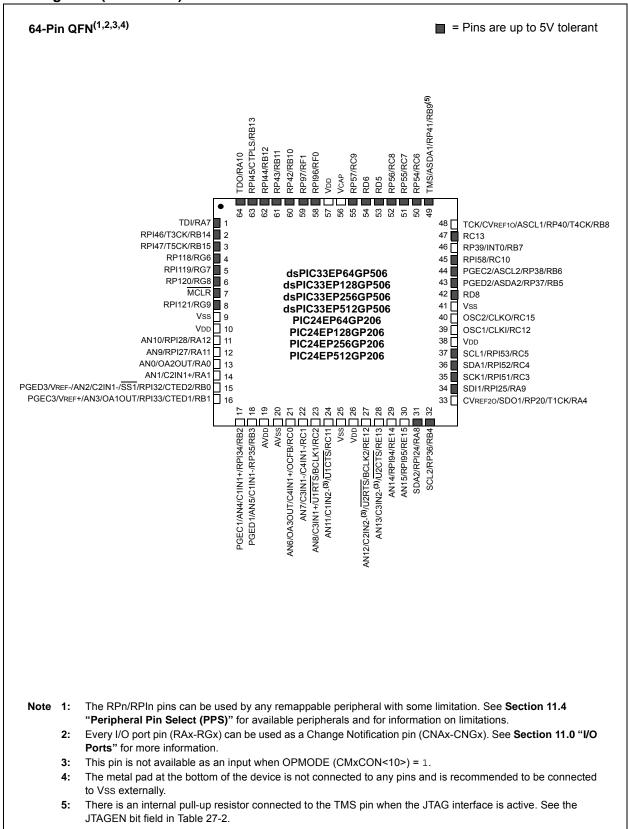

### **Pin Diagrams (Continued)**

- Note 1: The RPn/RPIn pins can be used by any remappable peripheral with some limitation. See Section 11.4 "Peripheral Pin Select (PPS)" for available peripherals and for information on limitations.

- 2: Every I/O port pin (RAx-RGx) can be used as a Change Notification pin (CNAx-CNGx). See **Section 11.0 "I/O Ports"** for more information.

- 3: The metal pad at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

#### Pin Diagrams (Continued)

There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the

to Vss externally.

JTAGEN bit field in Table 27-2.

### Pin Diagrams (Continued)

#### 2.7 **Oscillator Value Conditions on Device Start-up**

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz < Fin < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

#### 2.8 Unused I/Os

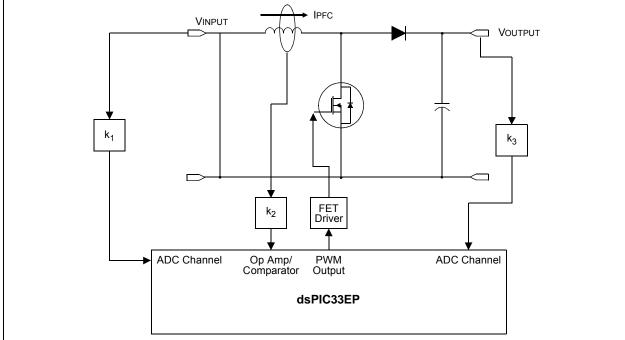

FIGURE 2-4:

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

#### 2.9 **Application Examples**

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- · DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- Automotive HVAC, cooling fans, fuel pumps

- · Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- · Speech (playback, hands-free kits, answering machines, VoIP)

- · Consumer audio

- · Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- · Data storage device management

- · Smart cards and smart card readers

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

**IPFC** VINPUT

**BOOST CONVERTER IMPLEMENTATION**

## 4.4 Special Function Register Maps

## TABLE 4-1: CPU CORE REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND dsPIC33EPXXXGP50X DEVICES ONLY

| IADLL     | ••    | 0, 0 0 |        |        | · ···· ·    | 011 001    | .000   | 7070701110 | _0/4/00/1  | 7 ti ti b | 0000  | ,,,,,,, | O. 0071  |          |          | •     |       |               |

|-----------|-------|--------|--------|--------|-------------|------------|--------|------------|------------|-----------|-------|---------|----------|----------|----------|-------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12      | Bit 11     | Bit 10 | Bit 9      | Bit 8      | Bit 7     | Bit 6 | Bit 5   | Bit 4    | Bit 3    | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

| W0        | 0000  |        |        |        |             |            |        |            | W0 (WRI    | EG)       |       |         |          |          |          |       |       | xxxx          |

| W1        | 0002  |        |        |        |             |            |        |            | W1         |           |       |         |          |          |          |       |       | xxxx          |

| W2        | 0004  |        |        |        |             |            |        |            | W2         |           |       |         |          |          |          |       |       | xxxx          |

| W3        | 0006  |        |        |        |             |            |        |            | W3         |           |       |         |          |          |          |       |       | xxxx          |

| W4        | 8000  |        |        |        |             |            |        |            | W4         |           |       |         |          |          |          |       |       | xxxx          |

| W5        | 000A  |        |        |        |             |            |        |            | W5         |           |       |         |          |          |          |       |       | xxxx          |

| W6        | 000C  |        |        |        |             |            |        |            | W6         |           |       |         |          |          |          |       |       | xxxx          |

| W7        | 000E  |        |        |        |             |            |        |            | W7         |           |       |         |          |          |          |       |       | xxxx          |

| W8        | 0010  |        |        |        |             |            |        |            | W8         |           |       |         |          |          |          |       |       | xxxx          |

| W9        | 0012  |        |        |        |             |            |        |            | W9         |           |       |         |          |          |          |       |       | xxxx          |

| W10       | 0014  |        |        |        |             |            |        |            | W10        |           |       |         |          |          |          |       |       | xxxx          |

| W11       | 0016  |        |        |        |             |            |        |            | W11        |           |       |         |          |          |          |       |       | xxxx          |

| W12       | 0018  |        |        |        |             |            |        |            | W12        |           |       |         |          |          |          |       |       | xxxx          |

| W13       | 001A  |        |        |        |             |            |        |            | W13        |           |       |         |          |          |          |       |       | xxxx          |

| W14       | 001C  |        |        |        |             |            |        |            | W14        |           |       |         |          |          |          |       |       | xxxx          |

| W15       | 001E  |        |        |        |             |            |        |            | W15        |           |       |         |          |          |          |       |       | xxxx          |

| SPLIM     | 0020  |        |        |        |             |            |        |            | SPLIN      | 1         |       |         |          |          |          |       |       | 0000          |

| ACCAL     | 0022  |        |        |        |             |            |        |            | ACCA       | L         |       |         |          |          |          |       |       | 0000          |

| ACCAH     | 0024  |        |        |        |             |            |        |            | ACCA       | Н         |       |         |          |          |          |       |       | 0000          |

| ACCAU     | 0026  |        |        | Sig    | gn Extensio | n of ACCA< | 39>    |            |            |           |       |         | AC       | CAU      |          |       |       | 0000          |

| ACCBL     | 0028  |        |        |        |             |            |        |            | ACCB       | L         |       |         |          |          |          |       |       | 0000          |

| ACCBH     | 002A  |        |        |        |             |            |        |            | ACCBI      | Н         |       |         |          |          |          |       |       | 0000          |

| ACCBU     | 002C  |        |        | Sig    | gn Extensio | n of ACCB< | 39>    |            |            |           |       |         | AC       | CBU      |          |       |       | 0000          |

| PCL       | 002E  |        |        |        |             |            |        | Р          | CL<15:0>   |           |       |         |          |          |          |       | _     | 0000          |

| PCH       | 0030  | _      | _      | _      | _           | _          | _      | _          | _          | _         |       |         |          | PCH<6:0> |          |       | •     | 0000          |

| DSRPAG    | 0032  | _      | _      | _      | _           | _          | _      |            |            |           |       | DSRPAC  | G<9:0>   |          |          |       |       | 0001          |

| DSWPAG    | 0034  | _      | _      | _      | _           | _          | _      | _          |            |           |       | DS      | SWPAG<8: | 0>       |          |       |       | 0001          |

| RCOUNT    | 0036  |        |        |        |             |            | •      | •          | RCOUNT<    | 15:0>     |       |         |          |          |          |       |       | 0000          |

| DCOUNT    | 0038  |        |        |        |             |            |        |            | DCOUNT<    | 15:0>     |       |         |          |          |          |       |       | 0000          |

| DOSTARTL  | 003A  |        |        |        |             |            |        | DOS        | TARTL<15:1 | >         |       |         |          |          |          |       | _     | 0000          |

| DOSTARTH  | 003C  | _      | _      | _      | _           | _          | _      | _          | _          | _         | _     |         |          | DOSTAR   | RTH<5:0> |       | •     | 0000          |

| DOENDL    | 003E  |        |        |        |             |            | •      | DOI        | ENDL<15:1> |           |       |         |          |          |          |       | _     | 0000          |

| DOENDH    | 0040  | _      | _      | _      | _           | _          | _      | _          | _          | _         | _     |         |          | DOEND    | )H<5:0>  |       |       | 0000          |

|           |       |        | D1     |        |             | (a) D      |        |            |            |           |       |         |          |          |          |       |       |               |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 88

TABLE 4-24: CRC REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14                   | Bit 13 | Bit 12 | Bit 11                    | Bit 10   | Bit 9 | Bit 8    | Bit 7        | Bit 6  | Bit 5   | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------------------------|--------|--------|---------------------------|----------|-------|----------|--------------|--------|---------|-------|---------|-------|-------|-------|---------------|

| CRCCON1   | 0640  | CRCEN  | _                        | CSIDL  |        | V                         | WORD<4:0 | )>    |          | CRCFUL       | CRCMPT | CRCISEL | CRCGO | LENDIAN | _     | _     | _     | 0000          |

| CRCCON2   | 0642  | _      | -                        | _      |        | DWIDTH<4:0> — — PLEN<4:0> |          |       |          |              |        |         |       |         | 0000  |       |       |               |

| CRCXORL   | 0644  |        |                          |        |        | X<15:1> 0                 |          |       |          |              |        |         |       | 0000    |       |       |       |               |

| CRCXORH   | 0646  |        |                          |        |        |                           |          |       | X<       | <31:16>      |        |         |       |         |       |       |       | 0000          |

| CRCDATL   | 0648  |        |                          |        |        |                           |          |       | CRC Data | Input Low V  | Vord   |         |       |         |       |       |       | 0000          |

| CRCDATH   | 064A  |        |                          |        |        |                           |          |       | CRC Data | Input High \ | Word   |         |       |         |       |       |       | 0000          |

| CRCWDATL  | 064C  |        | CRC Result Low Word 0    |        |        |                           |          |       |          |              |        | 0000    |       |         |       |       |       |               |

| CRCWDATH  | 064E  |        | CRC Result High Word 000 |        |        |                           |          |       |          |              |        | 0000    |       |         |       |       |       |               |

Legend: — = unimplemented, read as '0'. Shaded bits are not used in the operation of the programmable CRC module.

# TABLE 4-25: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC202/502 AND PIC24EPXXXGP/MC202 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|------------|--------|--------|-------|-------|-------|-------|-------|-------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  |        | _      |        |            | RP35F  | R<5:0> |       |       | -     | _     |       |       | RP20F | R<5:0> |       |       | 0000          |

| RPOR1        | 0682  | 1      | _      |        |            | RP37F  | R<5:0> |       |       | _     | -     |       |       | RP36F | R<5:0> |       |       | 0000          |

| RPOR2        | 0684  | 1      | _      |        |            | RP39F  | R<5:0> |       |       | _     | -     |       |       | RP38F | R<5:0> |       |       | 0000          |

| RPOR3        | 0686  | 1      | _      |        | RP41R<5:0> |        |        |       |       | _     | -     |       |       | RP40F | R<5:0> |       |       | 0000          |

| RPOR4        | 0688  | _      | _      |        |            | RP43F  | R<5:0> |       |       | _     | _     |       |       | RP42F | R<5:0> |       |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-26: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC203/503 AND PIC24EPXXXGP/MC203 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|------------|-------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  | _      | _      |        |        | RP35F  | R<5:0> |       |       | _     | _     |            |       | RP20F | R<5:0> |       |       | 0000          |

| RPOR1        | 0682  | 1      | 1      |        |        | RP37F  | R<5:0> |       |       | _     | _     | RP36R<5:0> |       |       |        | 0000  |       |               |

| RPOR2        | 0684  | 1      | 1      |        |        | RP39F  | R<5:0> |       |       | _     | _     | RP38R<5:0> |       |       |        | 0000  |       |               |

| RPOR3        | 0686  | 1      | 1      |        |        | RP41F  | R<5:0> |       |       | _     | _     |            |       | RP40F | R<5:0> |       |       | 0000          |

| RPOR4        | 0688  | 1      | 1      |        |        | RP43F  | R<5:0> |       |       | _     | _     | RP42R<5:0> |       |       |        | 0000  |       |               |

| RPOR5        | 068A  |        | _      | _      | _      | _      | _      | _     | _     | _     | _     | _          | _     | _     | _      | _     | _     | 0000          |

| RPOR6        | 068C  | 1      | 1      | _      | _      | _      | -      | _     | _     | _     | _     | RP56R<5:0> |       |       |        | 0000  |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **TIMER2/3 AND TIMER4/5** 13.0

Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

> 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 operate in three modes:

- · Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with all 16-Bit Operating modes (except Asynchronous Counter mode)

- · Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

They also support these features:

- · Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare Modules (Timer2 and Timer3 only)

- · ADC1 Event Trigger (32-bit timer pairs, and Timer3 and Timer5 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, and T4CON, T5CON registers. T2CON and T4CON are shown in generic form in Register 13-1. T3CON and T5CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word (lsw); Timer3 and Timer5 are the most significant word (msw) of the 32-bit timers.

For 32-bit operation, T3CON and T5CON

control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

A block diagram for an example 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 13-3.

Only Timer2, 3, 4 and 5 can trigger a DMA data transfer.

## REGISTER 17-2: QEI1IOC: QEI1 I/O CONTROL REGISTER (CONTINUED)

bit 2 INDEX: Status of INDXx Input Pin After Polarity Control

1 = Pin is at logic '1' 0 = Pin is at logic '0'

bit 1 QEB: Status of QEBx Input Pin After Polarity Control And SWPAB Pin Swapping

1 = Pin is at logic '1' 0 = Pin is at logic '0'

bit 0 QEA: Status of QEAx Input Pin After Polarity Control And SWPAB Pin Swapping

1 = Pin is at logic '1' 0 = Pin is at logic '0'

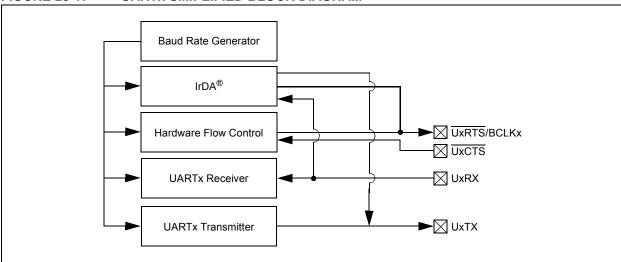

# 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "UART" (DS70582) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices contains two UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA® encoder and decoder.

Note: Hardware flow control using UxRTS and UxCTS is not available on all pin count devices. See the "Pin Diagrams" section for availability.

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- · 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UARTx Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- · Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 20-1. The UARTx module consists of these key hardware elements:

- · Baud Rate Generator

- · Asynchronous Transmitter

- · Asynchronous Receiver

#### 21.4 ECAN Control Registers

#### REGISTER 21-1: CxCTRL1: ECANx CONTROL REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-1  | R/W-0  | R/W-0  |

|--------|-----|-------|-------|--------|--------|--------|--------|

| _      | _   | CSIDL | ABAT  | CANCKS | REQOP2 | REQOP1 | REQOP0 |

| bit 15 |     |       |       |        |        |        | bit 8  |

| R-1     | R-0     | R-0     | U-0 | R/W-0  | U-0 | U-0 | R/W-0 |

|---------|---------|---------|-----|--------|-----|-----|-------|

| OPMODE2 | OPMODE1 | OPMODE0 | _   | CANCAP | _   | _   | WIN   |

| bit 7   |         |         |     |        |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13 CSIDL: ECANx Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12 ABAT: Abort All Pending Transmissions bit

1 = Signals all transmit buffers to abort transmission

0 = Module will clear this bit when all transmissions are aborted

bit 11 CANCKS: ECANx Module Clock (FCAN) Source Select bit

1 = FCAN is equal to 2 \* FP

0 = FCAN is equal to FP

bit 10-8 **REQOP<2:0>:** Request Operation Mode bits

111 = Set Listen All Messages mode

110 = Reserved

101 = Reserved

100 = Set Configuration mode

011 = Set Listen Only mode

010 = Set Loopback mode

001 = Set Disable mode

000 = Set Normal Operation mode

bit 7-5 **OPMODE<2:0>**: Operation Mode bits

111 = Module is in Listen All Messages mode

110 = Reserved

101 = Reserved

100 = Module is in Configuration mode

011 = Module is in Listen Only mode

010 = Module is in Loopback mode

001 = Module is in Disable mode

000 = Module is in Normal Operation mode

bit 4 Unimplemented: Read as '0'

bit 3 CANCAP: CAN Message Receive Timer Capture Event Enable bit

1 = Enables input capture based on CAN message receive

0 = Disables CAN capture

bit 2-1 **Unimplemented:** Read as '0'

bit 0 WIN: SFR Map Window Select bit

1 = Uses filter window

0 = Uses buffer window

# REGISTER 21-20: CxRXMnSID: ECANx ACCEPTANCE FILTER MASK n STANDARD IDENTIFIER REGISTER (n = 0-2)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| SID10  | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-x | R/W-x | R/W-x | U-0 | R/W-x | U-0 | R/W-x | R/W-x |

|-------|-------|-------|-----|-------|-----|-------|-------|

| SID2  | SID1  | SID0  | _   | MIDE  | _   | EID17 | EID16 |

| bit 7 |       |       |     |       |     |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-5 SID<10:0>: Standard Identifier bits

1 = Includes bit, SIDx, in filter comparison0 = SIDx bit is a don't care in filter comparison

bit 4 Unimplemented: Read as '0'

bit 3 MIDE: Identifier Receive Mode bit

1 = Matches only message types (standard or extended address) that correspond to EXIDE bit in the filter

0 = Matches either standard or extended address message if filters match (i.e., if (Filter SID) = (Message

SID) or if (Filter SID/EID) = (Message SID/EID))

bit 2 Unimplemented: Read as '0'

bit 1-0 EID<17:16>: Extended Identifier bits

1 = Includes bit, EIDx, in filter comparison

0 = EIDx bit is a don't care in filter comparison

# REGISTER 21-21: CxRXMnEID: ECANx ACCEPTANCE FILTER MASK n EXTENDED IDENTIFIER REGISTER (n = 0-2)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| EID15  | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 EID<15:0>: Extended Identifier bits

1 = Includes bit, EIDx, in filter comparison

0 = EIDx bit is a don't care in filter comparison

#### REGISTER 21-24: CxRXOVF1: ECANx RECEIVE BUFFER OVERFLOW REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXOVF7 | RXOVF6 | RXOVF5 | RXOVF4 | RXOVF3 | RXOVF2 | RXOVF1 | RXOVF0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

**Legend:** C = Writable bit, but only '0' can be written to clear the bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-0 **RXOVF<15:0>:** Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

#### REGISTER 21-25: CxRXOVF2: ECANx RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

**Legend:** C = Writable bit, but only '0' can be written to clear the bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-0 **RXOVF<31:16>:** Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

# REGISTER 21-26: CxTRmnCON: ECANx TX/RX BUFFER mn CONTROL REGISTER (m = 0,2,4,6; n = 1,3,5,7)

| R/W-0  | R-0    | R-0     | R-0    | R/W-0  | R/W-0  | R/W-0   | R/W-0   |

|--------|--------|---------|--------|--------|--------|---------|---------|

| TXENn  | TXABTn | TXLARBn | TXERRn | TXREQn | RTRENn | TXnPRI1 | TXnPRI0 |

| bit 15 |        |         |        |        |        |         | bit 8   |

| R/W-0 | R-0                   | R-0                    | R-0                   | R/W-0  | R/W-0  | R/W-0   | R/W-0   |

|-------|-----------------------|------------------------|-----------------------|--------|--------|---------|---------|

| TXENm | TXABTm <sup>(1)</sup> | TXLARBm <sup>(1)</sup> | TXERRm <sup>(1)</sup> | TXREQm | RTRENm | TXmPRI1 | TXmPRI0 |

| bit 7 |                       |                        |                       |        |        |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 See Definition for bits<7:0>, Controls Buffer n

bit 7 TXENm: TX/RX Buffer Selection bit

1 = Buffer TRBn is a transmit buffer0 = Buffer TRBn is a receive buffer

bit 6 **TXABTm:** Message Aborted bit<sup>(1)</sup>

1 = Message was aborted

0 = Message completed transmission successfully

bit 5 **TXLARBm:** Message Lost Arbitration bit<sup>(1)</sup>

1 = Message lost arbitration while being sent

0 = Message did not lose arbitration while being sent

bit 4 TXERRm: Error Detected During Transmission bit<sup>(1)</sup>

1 = A bus error occurred while the message was being sent

0 = A bus error did not occur while the message was being sent

bit 3 TXREQm: Message Send Request bit

1 = Requests that a message be sent; the bit automatically clears when the message is successfully

sent

0 = Clearing the bit to '0' while set requests a message abort

bit 2 RTRENm: Auto-Remote Transmit Enable bit

1 = When a remote transmit is received, TXREQ will be set

0 = When a remote transmit is received, TXREQ will be unaffected

bit 1-0 **TXmPRI<1:0>:** Message Transmission Priority bits

11 = Highest message priority

10 = High intermediate message priority

01 = Low intermediate message priority

00 = Lowest message priority

Note 1: This bit is cleared when TXREQ is set.

Note: The buffers, SID, EID, DLC, Data Field, and Receive Status registers are located in DMA RAM.

#### 23.2 ADC Helpful Tips

- 1. The SMPIx control bits in the AD1CON2 register:

- Determine when the ADC interrupt flag is set and an interrupt is generated, if enabled.

- b) When the CSCNA bit in the AD1CON2 registers is set to '1', this determines when the ADC analog scan channel list, defined in the AD1CSSL/AD1CSSH registers, starts over from the beginning.

- c) When the DMA peripheral is not used (ADDMAEN = 0), this determines when the ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0.

- d) When the DMA peripheral is used (ADDMAEN = 1), this determines when the DMA Address Pointer is incremented after a sample/conversion operation. ADC1BUF0 is the only ADC buffer used in this mode. The ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0. The DMA address is incremented after completion of every 32nd sample/conversion operation. Conversion results are stored in the ADC1BUF0 register for transfer to RAM using DMA.

- 2. When the DMA module is disabled (ADDMAEN = 0), the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF, regardless of which analog inputs are being used subject to the SMPIx bits and the condition described in 1c) above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- 3. When the DMA module is enabled (ADDMAEN = 1), the ADC module has only 1 ADC result buffer (i.e., ADC1BUF0) per ADC peripheral and the ADC conversion result must be read, either by the CPU or DMA Controller, before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (AD1CON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely, even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in Manual Sample mode, particularly where the user's code is setting the SAMP bit (AD1CON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

5. Enabling op amps, comparator inputs and external voltage references can limit the availability of analog inputs (ANx pins). For example, when Op Amp 2 is enabled, the pins for AN0, AN1 and AN2 are used by the op amp's inputs and output. This negates the usefulness of Alternate Input mode since the MUXA selections use AN0-AN2. Carefully study the ADC block diagram to determine the configuration that will best suit your application. Configuration examples are available in the "Analog-to-Digital Converter (ADC)" (DS70621) section in the "dsPIC33/PIC24 Family Reference Manual".

#### 23.3 ADC Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/Devices.aspx?dDocName=en555464

#### 23.3.1 KEY RESOURCES

- "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

| DC CHARACTERISTICS |        |                                                                 | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |   |                     |    |                                                                                                                           |  |

|--------------------|--------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------|----|---------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                                  | Min. Typ. Max. Units Conditions                                                                                                                                                                                                                  |   |                     |    |                                                                                                                           |  |

| DI60a              | licl   | Input Low Injection Current                                     | 0                                                                                                                                                                                                                                                | _ | <sub>-5</sub> (4,7) | mA | All pins except VDD, VSS, AVDD, AVSS, MCLR, VCAP and RB7                                                                  |  |

| DI60b              | lich   | Input High Injection Current                                    | 0                                                                                                                                                                                                                                                | _ | +5(5,6,7)           | mA | All pins except VDD, VSS,<br>AVDD, AVSS, MCLR, VCAP,<br>RB7 and all 5V tolerant<br>pins <sup>(6)</sup>                    |  |

| DI60c              | ∑lict  | Total Input Injection Current (sum of all I/O and control pins) | -20 <sup>(8)</sup>                                                                                                                                                                                                                               | _ | +20(8)              | mA | Absolute instantaneous sum of all $\pm$ input injection currents from all I/O pins (   IICL +   IICH   ) $\leq \sum$ IICT |  |

- Note 1: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 2: Negative current is defined as current sourced by the pin.

- 3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 4: VIL source < (Vss 0.3). Characterized but not tested.

- 5: Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

- **8:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

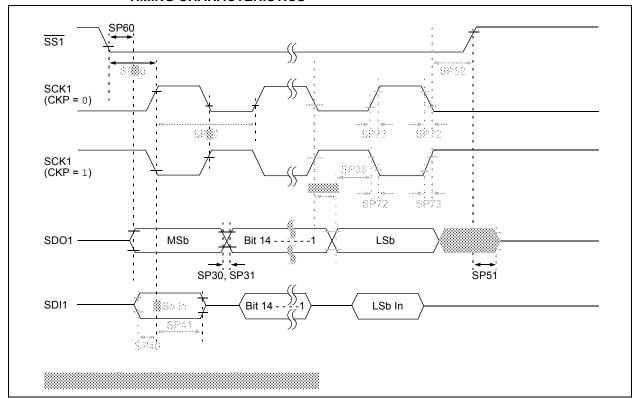

TABLE 30-38: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING REQUIREMENTS

| AC CHA | \RACTERIS <sup>*</sup> | псѕ                                        | Standard Op<br>(unless othe<br>Operating ter | rwise st            | <b>ated)</b><br>e -40°   | C ≤ Ta ≤ | V to 3.6V<br>+85°C for Industrial<br>+125°C for Extended |

|--------|------------------------|--------------------------------------------|----------------------------------------------|---------------------|--------------------------|----------|----------------------------------------------------------|

| Param. | Symbol                 | Characteristic <sup>(1)</sup>              | Min.                                         | Typ. <sup>(2)</sup> | Max.                     | Units    | Conditions                                               |

| SP70   | FscP                   | Maximum SCK2 Input<br>Frequency            | _                                            | _                   | Lesser<br>of FP<br>or 11 | MHz      | (Note 3)                                                 |

| SP72   | TscF                   | SCK2 Input Fall Time                       | _                                            | _                   | _                        | ns       | See Parameter DO32 (Note 4)                              |

| SP73   | TscR                   | SCK2 Input Rise Time                       | _                                            | _                   | _                        | ns       | See Parameter DO31 (Note 4)                              |

| SP30   | TdoF                   | SDO2 Data Output Fall Time                 | _                                            | _                   | _                        | ns       | See Parameter DO32 (Note 4)                              |

| SP31   | TdoR                   | SDO2 Data Output Rise Time                 | _                                            | _                   | _                        | ns       | See Parameter DO31 (Note 4)                              |

| SP35   | TscH2doV,<br>TscL2doV  | SDO2 Data Output Valid after SCK2 Edge     | _                                            | 6                   | 20                       | ns       |                                                          |

| SP36   | TdoV2scH,<br>TdoV2scL  | SDO2 Data Output Setup to First SCK2 Edge  | 30                                           | _                   | _                        | ns       |                                                          |

| SP40   | TdiV2scH,<br>TdiV2scL  | Setup Time of SDI2 Data Input to SCK2 Edge | 30                                           | _                   | _                        | ns       |                                                          |

| SP41   | TscH2diL,<br>TscL2diL  | Hold Time of SDI2 Data Input to SCK2 Edge  | 30                                           | _                   | _                        | ns       |                                                          |

| SP50   | TssL2scH,<br>TssL2scL  | SS2 ↓ to SCK2 ↑ or SCK2 ↓ Input            | 120                                          | _                   | _                        | ns       |                                                          |

| SP51   | TssH2doZ               | SS2 ↑ to SDO2 Output<br>High-Impedance     | 10                                           | _                   | 50                       | ns       | (Note 4)                                                 |

| SP52   | TscH2ssH<br>TscL2ssH   | SS2 ↑ after SCK2 Edge                      | 1.5 Tcy + 40                                 | _                   | _                        | ns       | (Note 4)                                                 |

| SP60   | TssL2doV               | SDO2 Data Output Valid after<br>SS2 Edge   | _                                            | _                   | 50                       | ns       |                                                          |

- **Note 1:** These parameters are characterized, but are not tested in manufacturing.

- **2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK2 is 91 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

- 4: Assumes 50 pF load on all SPI2 pins.

FIGURE 30-26: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

| TyCON (Timer3 and Timer5 Control)                              | 211     | Input Capture x (ICx)                         | 420 |

|----------------------------------------------------------------|---------|-----------------------------------------------|-----|

| UxMODE (UARTx Mode)                                            | 283     | OCx/PWMx                                      |     |

| UxSTA (UARTx Status and Control)                               |         | Output Compare x (OCx)                        |     |

| VEL1CNT (Velocity Counter 1)                                   |         | QEA/QEB Input                                 |     |

| Resets                                                         |         | QEI Module Index Pulse                        |     |

| Brown-out Reset (BOR)                                          |         | SPI1 Master Mode (Full-Duplex, CKE = 0,       |     |

| Configuration Mismatch Reset (CM)                              |         | CKP = x, SMP = 1)                             | 441 |

| Illegal Condition Reset (IOPUWR)                               |         | SPI1 Master Mode (Full-Duplex, CKE = 1,       |     |

| Illegal Opcode                                                 |         | CKP = x, SMP = 1)                             | 440 |

| Security                                                       |         | SPI1 Master Mode (Half-Duplex, Transmit Only, |     |

| Uninitialized W Register                                       |         | CKE = 0)                                      | 438 |

| Master Clear (MCLR) Pin Reset                                  |         | SPI1 Master Mode (Half-Duplex, Transmit Only, |     |

| Power-on Reset (POR)                                           |         | CKE = 1)                                      | 439 |

| RESET Instruction (SWR)                                        |         | SPI1 Slave Mode (Full-Duplex, CKE = 0,        | 100 |

| Resources                                                      |         | CKP = 0, SMP = 0)                             | 448 |

| Trap Conflict Reset (TRAPR)                                    |         | SPI1 Slave Mode (Full-Duplex, CKE = 0,        | ++0 |

| Watchdog Timer Time-out Reset (WDTO)                           |         | CKP = 1, SMP = 0)                             | 446 |

| Resources Required for Digital PFC                             |         | SPI1 Slave Mode (Full-Duplex, CKE = 1,        | 440 |

| Revision History                                               |         | CKP = 0, SMP = 0)                             | 112 |

| TREVISION FIRSTORY                                             | 507     | SPI1 Slave Mode (Full-Duplex, CKE = 1,        | 442 |

| S                                                              |         | CKP = 1, SMP = 0)                             | 111 |

| Serial Peripheral Interface (SPI)                              | 265     | SPI2 Master Mode (Full-Duplex, CKE = 0,       | 444 |

| Software Stack Pointer (SSP)                                   |         | CKP = x, SMP = 1)                             | 420 |

| Special Features of the CPU                                    |         | SPI2 Master Mode (Full-Duplex, CKE = 1,       | 429 |

| SPI                                                            | 379     |                                               | 400 |

| Control Registers                                              | 269     | CKP = x, SMP = 1)                             | 420 |

| Helpful Tips                                                   |         | SPI2 Master Mode (Half-Duplex, Transmit Only, | 400 |

|                                                                |         | CKE = 0)                                      | 426 |

| Resources                                                      | 201     | SPI2 Master Mode (Half-Duplex, Transmit Only, | 407 |

| Т                                                              |         | CKE = 1)                                      | 427 |

| Temperature and Voltage Specifications                         |         | SPI2 Slave Mode (Full-Duplex, CKE = 0,        | 400 |

| AC                                                             | 112 171 | CKP = 0, SMP = 0)                             | 436 |

|                                                                |         | SPI2 Slave Mode (Full-Duplex, CKE = 0,        |     |

| Thermal Operating Conditions Thermal Packaging Characteristics |         | CKP = 1, SMP = 0)                             | 434 |

|                                                                |         | SPI2 Slave Mode (Full-Duplex, CKE = 1,        |     |

| Timer1                                                         |         | CKP = 0, SMP = 0)                             | 430 |

| Control Register                                               |         | SPI2 Slave Mode (Full-Duplex, CKE = 1,        |     |

| Resources                                                      |         | CKP = 1, SMP = 0)                             |     |

| Timer2/3 and Timer4/5                                          |         | Timer1-Timer5 External Clock                  |     |

| Control Registers                                              |         | TimerQ (QEI Module) External Clock            |     |

| Resources                                                      | 209     | UARTx I/O                                     | 454 |

| Timing Diagrams                                                |         | U                                             |     |

| 10-Bit ADC Conversion (CHPS<1:0> = 01,                         | 000     | _                                             |     |

| SIMSAM = 0, ASAM = 0, SSRC<2:0> =                              |         | Universal Asynchronous Receiver               |     |

| SSRCG = 0)                                                     | 464     | Transmitter (UART)                            |     |

| 10-Bit ADC Conversion (CHPS<1:0> = 01,                         |         | Control Registers                             |     |

| SIMSAM = 0, $ASAM = 1$ , $SSRC < 2:0 > =$                      | ,       | Helpful Tips                                  |     |

| SSRCG = 0, SAMC<4:0> = 00010)                                  | 464     | Resources                                     |     |

| 12-Bit ADC Conversion (ASAM = 0,                               |         | User ID Words                                 | 384 |

| SSRC<2:0> = 000, SSRCG = 0)                                    |         | V                                             |     |

| BOR and Master Clear Reset                                     |         |                                               |     |

| ECANx I/O                                                      |         | Voltage Regulator (On-Chip)                   | 384 |

| External Clock                                                 | 414     | W                                             |     |

| High-Speed PWMx Fault                                          | 422     |                                               |     |

| High-Speed PWMx Module                                         |         | Watchdog Timer (WDT)                          |     |

| I/O Characteristics                                            |         | Programming Considerations                    |     |

| I2Cx Bus Data (Master Mode)                                    | 450     | WWW Address                                   |     |

| I2Cx Bus Data (Slave Mode)                                     |         | WWW, On-Line Support                          | 23  |

| I2Cx Bus Start/Stop Bits (Master Mode)                         |         |                                               |     |

| . ` ` ,                                                        | 452     |                                               |     |

| DSPIC33EPXXXGP50X, DSPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X |

|-----------------------------------------------------------------|

| NOTES:                                                          |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |