#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | ·                                                                              |

| RAM Size                   | 16K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 28-SPDIP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256gp202-e-sp |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section of the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X Digital Signal Controller (DSC) and Microcontroller (MCU) devices.

dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

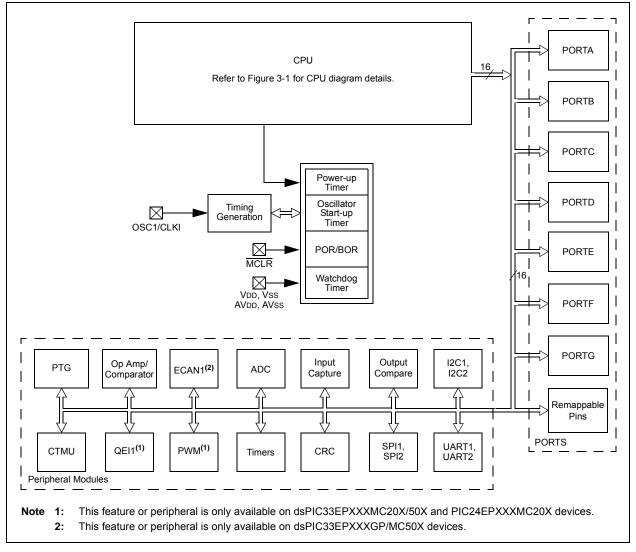

Figure 1-1 shows a general block diagram of the core and peripheral modules. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

### FIGURE 1-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X BLOCK DIAGRAM

| <b>TABLE 4-33</b> : | PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY |

|---------------------|-----------------------------------------------------------------------------|

|---------------------|-----------------------------------------------------------------------------|

|              |       |        |              | -            | -      | -          |        |       |       |       |              |       |       |            |          |       |       |               |

|--------------|-------|--------|--------------|--------------|--------|------------|--------|-------|-------|-------|--------------|-------|-------|------------|----------|-------|-------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14       | Bit 13       | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6        | Bit 5 | Bit 4 | Bit 3      | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

| RPINR0       | 06A0  | _      |              |              |        | NT1R<6:0>  |        |       |       |       | _            | _     | _     | _          |          | _     | _     | 0000          |

| RPINR1       | 06A2  |        | —            | —            | -      |            | -      |       | -     | -     | INT2R<6:0>   |       |       |            |          |       | 0000  |               |

| RPINR3       | 06A6  |        | _            | _            | _      | _          | _      | _     | _     | _     | T2CKR<6:0>   |       |       |            |          |       |       | 0000          |

| RPINR7       | 06AE  | _      |              |              |        | IC2R<6:0>  |        |       |       | —     | IC1R<6:0>    |       |       |            |          |       |       | 0000          |

| RPINR8       | 06B0  | _      |              | IC4R<6:0>    |        |            |        |       |       | —     | IC3R<6:0>    |       |       |            |          |       |       | 0000          |

| RPINR11      | 06B6  | _      | _            |              |        |            |        |       |       | —     | OCFAR<6:0>   |       |       |            |          |       |       | 0000          |

| RPINR12      | 06B8  | _      |              |              | l      | =LT2R<6:0> |        |       |       | —     |              |       |       | FLT1R<6:0> | <b>`</b> |       |       | 0000          |

| RPINR14      | 06BC  | _      |              |              | (      | QEB1R<6:0  | >      |       |       | —     |              |       | (     | QEA1R<6:0> | >        |       |       | 0000          |

| RPINR15      | 06BE  | _      |              |              | Н      | OME1R<6:0  | )>     |       |       | —     | INDX1R<6:0>  |       |       |            |          |       | 0000  |               |

| RPINR18      | 06C4  | _      | _            | _            | —      | _          | _      | _     | _     | —     | U1RXR<6:0>   |       |       |            |          |       | 0000  |               |

| RPINR19      | 06C6  | _      | _            | _            | _      | _          | _      | _     | _     | —     | U2RXR<6:0>   |       |       |            |          |       |       | 0000          |

| RPINR22      | 06CC  | _      |              | SCK2INR<6:0> |        |            |        |       |       | _     |              |       |       | SDI2R<6:0> | •        |       |       | 0000          |

| RPINR23      | 06CE  | _      |              |              |        |            |        |       | _     | _     |              |       |       | SS2R<6:0>  |          |       |       | 0000          |

| RPINR37      | 06EA  | _      | SYNCI1R<6:0> |              |        |            |        |       |       | _     | _            | _     | _     | _          | _        | _     | _     | 0000          |

| RPINR38      | 06EC  | _      | DTCMP1R<6:0> |              |        |            |        |       |       | _     |              |       |       |            |          | _     | 0000  |               |

| RPINR39      | 06EE  | _      |              |              | DT     | CMP3R<6:   | 0>     |       |       | —     | DTCMP2R<6:0> |       |       |            |          |       | 0000  |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-56: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | _      | _      | _      |        | _      | _     | TRISA8 | _     | —     | —     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 011F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     | RA8    | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     | LATA8  | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     | ODCA8  | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     | CNIEA8 | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     | CNPUA8 | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     | CNPDA8 | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | —      | _      | —      | _     | —      | _     | —     | —     | ANSA4  | —      | —      | ANSA1  | ANSA0  | 0013          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-57: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | -       | _       | -       | —       | -      | ANSB8  | _      | _      | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-58: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|-------|-------|-------|--------|--------|---------------|

| TRISC        | 0E20  | _      | _      | _      | _      | _      | —      | —     | TRISC8 | _     | -     |       | _     |       | -     | TRISC1 | TRISC0 | 0103          |

| PORTC        | 0E22  |        |        | -      | -      | -      | —      | _     | RC8    | —     | -     |       | _     |       |       | RC1    | RC0    | xxxx          |

| LATC         | 0E24  |        |        | _      | _      | _      | _      | _     | LATC8  | _     | _     | _     | _     | _     | _     | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  |        |        | _      | _      | _      | _      | _     | ODCC8  | _     | _     | _     | _     | _     | _     | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | —      | _      | -      | _      |        | _      | _     | CNIEC8 | —     |       |       | _     |       |       | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  |        |        | _      | _      | _      | _      | _     | CNPUC8 | _     | _     | _     | _     | _     | _     | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  |        |        | _      | _      | _      | _      | _     | CNPDC8 | _     | _     | _     | _     | _     | _     | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | -      | _      | _      | _      | _      | —      | —     | —      | —     |       | _     | _     | _     |       | ANSC1  | ANSC0  | 0003          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0    | U-0 | U-0 | U-0 | U-0   | U-0   | U-0   | U-0   |

|--------|-----|-----|-----|-------|-------|-------|-------|

| _      |     |     |     | _     | —     |       | —     |

| bit 15 |     |     |     |       |       |       | bit 8 |

|        |     |     |     |       |       |       |       |

| U-0    | U-0 | U-0 | U-0 | R-0   | R-0   | R-0   | R-0   |

| —      | —   | —   | _   | PPST3 | PPST2 | PPST1 | PPST0 |

| bit 7  |     |     |     |       |       |       | bit 0 |

## REGISTER 8-14: DMAPPS: DMA PING-PONG STATUS REGISTER

| Legend:      |         |                                                                                       |                                    |                    |  |  |  |  |

|--------------|---------|---------------------------------------------------------------------------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readat   | ole bit | W = Writable bit                                                                      | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value a | at POR  | '1' = Bit is set                                                                      | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

| bit 15-4     | Unimplo | mented: Read as '0'                                                                   |                                    |                    |  |  |  |  |

|              | •       | DMA Channel 3 Ping-Pong I                                                             | Modo Status Elag bit               |                    |  |  |  |  |

| 1 = DMAS     |         | ASTB3 register is selected<br>ASTA3 register is selected                              | vioue Status Flag bit              |                    |  |  |  |  |

| bit 2        | 1 = DMA | DMA Channel 2 Ping-Pong I<br>ASTB2 register is selected<br>ASTA2 register is selected | Mode Status Flag bit               |                    |  |  |  |  |

| bit 1        | PPST1:  | DMA Channel 1 Ping-Pong I                                                             | Mode Status Flag bit               |                    |  |  |  |  |

|              |         | CTD1 register is calested                                                             |                                    |                    |  |  |  |  |

- 1 = DMASTB1 register is selected0 = DMASTA1 register is selected

- bit 0 PPST0: DMA Channel 0 Ping-Pong Mode Status Flag bit

- 1 = DMASTB0 register is selected

- 0 = DMASTA0 register is selected

## 13.0 TIMER2/3 AND TIMER4/5

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 operate in three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with all 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

- They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare Modules (Timer2 and Timer3 only)

- ADC1 Event Trigger (32-bit timer pairs, and Timer3 and Timer5 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, and T4CON, T5CON registers. T2CON and T4CON are shown in generic form in Register 13-1. T3CON and T5CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word (lsw); Timer3 and Timer5 are the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

A block diagram for an example 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 13-3.

**Note:** Only Timer2, 3, 4 and 5 can trigger a DMA data transfer.

## REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER (CONTINUED)

| bit 6-4 | SYNCSRC<2:0>: Synchronous Source Selection bits <sup>(1)</sup><br>111 = Reserved<br>100 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-0 | 100 = Reserved<br>011 = PTGO17 <sup>(2)</sup><br>010 = PTGO16 <sup>(2)</sup><br>001 = Reserved<br>000 = SYNCI1 input from PPS<br>SEVTPS<3:0>: PWMx Special Event Trigger Output Postscaler Select bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1111 = 1:16 Postscaler generates Special Event Trigger on every sixteenth compare match event</li> <li>.</li> <l< td=""></l<></ul> |

|         | 0000 = 1:1 Postscaler generates Special Event Trigger on every second compare match event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

- **Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

| REGISTE       | R 16-7: PWMC                                                                     | CONX: PWMX (                                                                                                                                                | CONTROL R     | EGISTER          |                      |                      |                     |  |  |

|---------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------|----------------------|----------------------|---------------------|--|--|

| HS/HC-        | 0 HS/HC-0                                                                        | HS/HC-0                                                                                                                                                     | R/W-0         | R/W-0            | R/W-0                | R/W-0                | R/W-0               |  |  |

| FLTSTAT       | -(1) CLSTAT <sup>(1)</sup>                                                       | TRGSTAT                                                                                                                                                     | FLTIEN        | CLIEN            | TRGIEN               | ITB <sup>(2)</sup>   | MDCS <sup>(2)</sup> |  |  |

| bit 15        | ·                                                                                | •                                                                                                                                                           |               | ÷                |                      |                      | bit                 |  |  |

| R/W-0         | R/W-0                                                                            | R/W-0                                                                                                                                                       | U-0           | R/W-0            | R/W-0                | R/W-0                | R/W-0               |  |  |

| DTC1          |                                                                                  | DTCP <sup>(3)</sup>                                                                                                                                         | 0-0           | MTBS             | CAM <sup>(2,4)</sup> | XPRES <sup>(5)</sup> | IUE <sup>(2)</sup>  |  |  |

| bit 7         | DICO                                                                             | DICE                                                                                                                                                        | _             | INT DO           | CAIM                 | AFRES'               | bit                 |  |  |

|               |                                                                                  |                                                                                                                                                             |               |                  |                      |                      | <u> </u>            |  |  |

| Legend:       |                                                                                  | HC = Hardware                                                                                                                                               | Clearable bit | HS = Hardwa      | are Settable bit     |                      |                     |  |  |

| R = Reada     | able bit                                                                         | W = Writable bi                                                                                                                                             | t             | U = Unimple      | mented bit, rea      | ıd as '0'            |                     |  |  |

| -n = Value    | at POR                                                                           | '1' = Bit is set                                                                                                                                            |               | '0' = Bit is cle | eared                | x = Bit is unk       | nown                |  |  |

| bit 15        | ELTSTAT: ES                                                                      | ult Interrupt Statu                                                                                                                                         | is hit(1)     |                  |                      |                      |                     |  |  |

| DIL 15        |                                                                                  | rrupt is pending                                                                                                                                            |               |                  |                      |                      |                     |  |  |

|               |                                                                                  | interrupt is pendi                                                                                                                                          | ng            |                  |                      |                      |                     |  |  |

|               |                                                                                  | ared by setting F                                                                                                                                           |               |                  |                      |                      |                     |  |  |

| bit 14        |                                                                                  | rent-Limit Interru                                                                                                                                          | •             |                  |                      |                      |                     |  |  |

|               |                                                                                  | mit interrupt is pe                                                                                                                                         |               |                  |                      |                      |                     |  |  |

|               |                                                                                  | nt-limit interrupt is<br>ared by setting C                                                                                                                  |               |                  |                      |                      |                     |  |  |

| bit 13        |                                                                                  |                                                                                                                                                             |               |                  |                      |                      |                     |  |  |

|               | <b>TRGSTAT:</b> Trigger Interrupt Status bit<br>1 = Trigger interrupt is pending |                                                                                                                                                             |               |                  |                      |                      |                     |  |  |

|               |                                                                                  | r interrupt is pen                                                                                                                                          |               |                  |                      |                      |                     |  |  |

|               |                                                                                  | ared by setting T                                                                                                                                           |               |                  |                      |                      |                     |  |  |

| bit 12        |                                                                                  | t Interrupt Enable                                                                                                                                          | e bit         |                  |                      |                      |                     |  |  |

|               |                                                                                  | rrupt is enabled rrupt is disabled                                                                                                                          | and the FLTS  | TAT bit is clear | ed                   |                      |                     |  |  |

| bit 11        |                                                                                  | ent-Limit Interrup                                                                                                                                          |               |                  | cu .                 |                      |                     |  |  |

|               |                                                                                  | mit interrupt is er                                                                                                                                         |               |                  |                      |                      |                     |  |  |

|               |                                                                                  | mit interrupt is di                                                                                                                                         |               | e CLSTAT bit is  | s cleared            |                      |                     |  |  |

| bit 10        | TRGIEN: Trig                                                                     | ger Interrupt En                                                                                                                                            | able bit      |                  |                      |                      |                     |  |  |

|               |                                                                                  | event generates                                                                                                                                             |               |                  | T hit is cleared     |                      |                     |  |  |

| bit 9         |                                                                                  | vent interrupts ar<br>dent Time Base I                                                                                                                      |               |                  | i bit is cleared     |                      |                     |  |  |

| DIL 9         |                                                                                  |                                                                                                                                                             |               | riad for this PM | VM generator         |                      |                     |  |  |

|               |                                                                                  | <ul> <li>1 = PHASEx register provides time base period for this PWM generator</li> <li>0 = PTPER register provides timing for this PWM generator</li> </ul> |               |                  |                      |                      |                     |  |  |

| bit 8         | <b>MDCS:</b> Master Duty Cycle Register Select bit <sup>(2)</sup>                |                                                                                                                                                             |               |                  |                      |                      |                     |  |  |

|               |                                                                                  | ister provides du<br>jister provides du                                                                                                                     |               |                  |                      | r                    |                     |  |  |

| Note 1:       | Software must clea                                                               |                                                                                                                                                             |               |                  | -                    |                      | t controller        |  |  |

| Note 1.<br>2: | These bits should                                                                | -                                                                                                                                                           |               | -                | -                    | the interrup         |                     |  |  |

| 3:            | DTC<1:0> = 11 fo                                                                 | -                                                                                                                                                           |               | -                | -                    |                      |                     |  |  |

| 4:            | The Independent T<br>CAM bit is ignored                                          | Time Base (ITB =                                                                                                                                            |               | •                |                      | igned mode. If       | TTB = 0, the        |  |  |

| 5:            |                                                                                  |                                                                                                                                                             |               |                  |                      |                      |                     |  |  |

## REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER

5: To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

## 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "UART" (DS70582) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

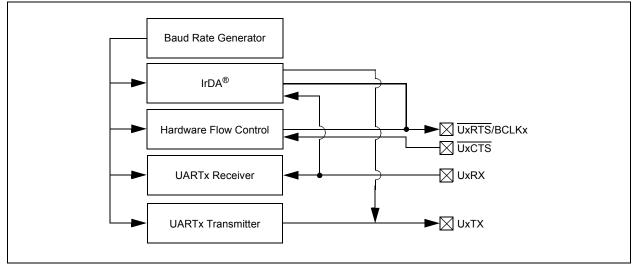

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices contains two UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

Note: <u>Hardware</u> flow control using UxRTS and UxCTS is not available on all pin count devices. See the "**Pin Diagrams**" section for availability.

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UARTx Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 20-1. The UARTx module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

### FIGURE 20-1: UARTx SIMPLIFIED BLOCK DIAGRAM

© 2011-2013 Microchip Technology Inc.

| <b>Legend:</b><br>R = Readable | bit   | C = Writable b<br>W = Writable l |      |        | n to clear the bit<br>mented bit, read |       |       |

|--------------------------------|-------|----------------------------------|------|--------|----------------------------------------|-------|-------|

| bit 7                          |       |                                  |      |        |                                        |       | bit 0 |

| IVRIF                          | WAKIF | ERRIF                            | _    | FIFOIF | RBOVIF                                 | RBIF  | TBIF  |

| R/C-0                          | R/C-0 | R/C-0                            | U-0  | R/C-0  | R/C-0                                  | R/C-0 | R/C-0 |

|                                |       |                                  |      |        |                                        |       | 2 0   |

| bit 15                         |       |                                  |      |        |                                        |       | bit 8 |

| _                              | —     | ТХВО                             | TXBP | RXBP   | TXWAR                                  | RXWAR | EWARN |

| U-0                            | U-0   | R-0                              | R-0  | R-0    | R-0                                    | R-0   | R-0   |

'0' = Bit is cleared

x = Bit is unknown

## REGISTER 21-6: CxINTF: ECANx INTERRUPT FLAG REGISTER

'1' = Bit is set

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                   |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | <b>TXBO:</b> Transmitter in Error State Bus Off bit                                                                                          |

|           | 1 = Transmitter is in Bus Off state                                                                                                          |

|           | 0 = Transmitter is not in Bus Off state                                                                                                      |

| bit 12    | <b>TXBP:</b> Transmitter in Error State Bus Passive bit                                                                                      |

|           | <ul><li>1 = Transmitter is in Bus Passive state</li><li>0 = Transmitter is not in Bus Passive state</li></ul>                                |

| bit 11    | <b>RXBP:</b> Receiver in Error State Bus Passive bit                                                                                         |

|           | 1 = Receiver is in Bus Passive state<br>0 = Receiver is not in Bus Passive state                                                             |

| bit 10    | TXWAR: Transmitter in Error State Warning bit                                                                                                |

|           | 1 = Transmitter is in Error Warning state<br>0 = Transmitter is not in Error Warning state                                                   |

| bit 9     | RXWAR: Receiver in Error State Warning bit                                                                                                   |

|           | 1 = Receiver is in Error Warning state<br>0 = Receiver is not in Error Warning state                                                         |

| bit 8     | EWARN: Transmitter or Receiver in Error State Warning bit                                                                                    |

|           | <ul> <li>1 = Transmitter or receiver is in Error Warning state</li> <li>0 = Transmitter or receiver is not in Error Warning state</li> </ul> |

| bit 7     | IVRIF: Invalid Message Interrupt Flag bit                                                                                                    |

|           | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul>                                       |

| bit 6     | WAKIF: Bus Wake-up Activity Interrupt Flag bit                                                                                               |

|           | 1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred                                                                 |

| bit 5     | ERRIF: Error Interrupt Flag bit (multiple sources in CxINTF<13:8>)                                                                           |

|           | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul>                                       |

| bit 4     | Unimplemented: Read as '0'                                                                                                                   |

| bit 3     | FIFOIF: FIFO Almost Full Interrupt Flag bit                                                                                                  |

|           | 1 = Interrupt request has occurred                                                                                                           |

|           | 0 = Interrupt request has not occurred                                                                                                       |

| bit 2     | RBOVIF: RX Buffer Overflow Interrupt Flag bit                                                                                                |

|           | 1 = Interrupt request has occurred                                                                                                           |

-n = Value at POR

|               | 23-2: Al                       | DICONZ. ADCI                                         | CONTROL REG           | ISIER Z         |                   |                  |                 |  |  |  |

|---------------|--------------------------------|------------------------------------------------------|-----------------------|-----------------|-------------------|------------------|-----------------|--|--|--|

| R/W-0         | R/W-                           | 0 R/W-0                                              | U-0                   | U-0             | R/W-0             | R/W-0            | R/W-0           |  |  |  |

| VCFG2         | VCFO                           | G1 VCFG0                                             | —                     | —               | CSCNA             | CHPS1            | CHPS0           |  |  |  |

| bit 15        |                                |                                                      |                       |                 |                   |                  | bit             |  |  |  |

| R-0           | R/W-                           | 0 R/W-0                                              | R/W-0                 | R/W-0           | R/W-0             | R/W-0            | R/W-0           |  |  |  |

| BUFS          | SMP                            |                                                      | SMPI2                 | SMPI1           | SMPI0             | BUFM             | ALTS            |  |  |  |

| bit 7         | OWIT                           |                                                      |                       |                 |                   | Borim            | bit             |  |  |  |

| Legend:       |                                |                                                      |                       |                 |                   |                  |                 |  |  |  |

| R = Readable  | , hit                          | W = Writable                                         | bit I                 | l – Llnimolo    | monted hit rea    | d oo 'O'         |                 |  |  |  |

|               |                                |                                                      |                       |                 | mented bit, read  |                  |                 |  |  |  |

| -n = Value at | POR                            | '1' = Bit is se                                      | t 't                  | )' = Bit is cle | eared             | x = Bit is unkr  | nown            |  |  |  |

| bit 15-13     | VCFG<2                         | 2:0>: Converter Vol                                  | tage Reference C      | onfiguration    | bits              |                  |                 |  |  |  |

|               | Value                          | VREFH                                                | VREFL                 |                 |                   |                  |                 |  |  |  |

|               | 000                            | Avdd                                                 | Avss                  |                 |                   |                  |                 |  |  |  |

|               | 001                            | External VREF+                                       | Avss                  |                 |                   |                  |                 |  |  |  |

|               | 010                            | Avdd                                                 | External VREF-        |                 |                   |                  |                 |  |  |  |

|               | 011                            | External VREF+                                       | External VREF-        |                 |                   |                  |                 |  |  |  |

|               | 1xx                            | Avdd                                                 | Avss                  |                 |                   |                  |                 |  |  |  |

| bit 12-11     | Unimple                        | emented: Read as                                     | ʻ0'                   |                 |                   |                  |                 |  |  |  |

| bit 10        | CSCNA                          | Input Scan Select                                    | bit                   |                 |                   |                  |                 |  |  |  |

|               |                                | ns inputs for CH0+                                   |                       | JXA             |                   |                  |                 |  |  |  |

|               | 0 = Does                       | s not scan inputs                                    | <b>C</b> .            |                 |                   |                  |                 |  |  |  |

| bit 9-8       | CHPS<1:0>: Channel Select bits |                                                      |                       |                 |                   |                  |                 |  |  |  |

|               |                                | mode (AD21B = 1)                                     |                       | bits are Uni    | mplemented ar     | id are Read as   | <u>'0':</u>     |  |  |  |

|               |                                | nverts CH0, CH1, C                                   |                       |                 |                   |                  |                 |  |  |  |

|               |                                | nverts CH0 and CH<br>nverts CH0                      | 11                    |                 |                   |                  |                 |  |  |  |

| bit 7         |                                | Buffer Fill Status bit                               | (oply valid when F    |                 |                   |                  |                 |  |  |  |

|               |                                | C is currently filling t                             |                       |                 | ne user applicat  | ion should acco  | ee data in th   |  |  |  |

|               |                                | half of the buffer                                   |                       | ule bullet, u   | ie usei applicat  |                  | 555 Uala III li |  |  |  |

|               |                                | C is currently filling                               | the first half of the | e buffer; the   | e user applicatio | on should acce   | ss data in th   |  |  |  |

|               | seco                           | ond half of the buffe                                | er                    |                 |                   |                  |                 |  |  |  |

| bit 6-2       | SMPI<4                         | :0>: Increment Rate                                  | e bits                |                 |                   |                  |                 |  |  |  |

|               |                                | DDMAEN = 0:                                          |                       |                 |                   |                  |                 |  |  |  |

|               |                                | Generates interrup                                   |                       |                 |                   |                  |                 |  |  |  |

|               | x1110 =                        | Generates interrup                                   | ot after completion   | of every 18     | oth sample/conv   | ersion operation | on              |  |  |  |

|               | •                              |                                                      |                       |                 |                   |                  |                 |  |  |  |

|               | •                              |                                                      |                       |                 |                   |                  |                 |  |  |  |

|               |                                | Generates interrup                                   |                       |                 |                   |                  | n               |  |  |  |

|               |                                | Generates interrup                                   | ot after completion   | of every sa     | imple/conversion  | on operation     |                 |  |  |  |

|               |                                | $\frac{\text{DDMAEN} = 1}{\text{Increments the DN}}$ | 1A address after a    | omplotion o     | of overy 32nd s   | mplo/convorsi    | on operation    |  |  |  |

|               |                                | Increments the DN                                    |                       |                 |                   |                  |                 |  |  |  |

|               | •                              |                                                      |                       |                 |                   |                  |                 |  |  |  |

|               | •                              |                                                      |                       |                 |                   |                  |                 |  |  |  |

|               | •                              |                                                      |                       |                 |                   | ., .             |                 |  |  |  |

|               | 00001 -                        | Increments the DI                                    | "A address offer a    | omplation o     | t avany 2nd aar   |                  |                 |  |  |  |

#### . . ACOND. ADCA CONTROL DECISTED 2

## REGISTER 23-5: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER (CONTINUED)

bit 0

**CH123SA:** Channel 1, 2, 3 Positive Input Select for Sample MUXA bit In 12-bit mode (AD21B = 1), CH123SA is Unimplemented and is Read as '0':

| Value          | ADC Channel |         |         |  |  |  |  |

|----------------|-------------|---------|---------|--|--|--|--|

| value          | CH1         | CH2     | CH3     |  |  |  |  |

| 1 <b>(2)</b>   | OA1/AN3     | OA2/AN0 | OA3/AN6 |  |  |  |  |

| 0 <b>(1,2)</b> | OA2/AN0     | AN1     | AN2     |  |  |  |  |

**Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

| R/W-0      | U-0                                                                                                                | U-0                                                                                                              | R/W-0                           | R/W-0                 | R/W-0                    | R/W-0                 | R/W-0                 |  |  |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------|--------------------------|-----------------------|-----------------------|--|--|--|--|

| CH0NB      |                                                                                                                    | _                                                                                                                | CH0SB4 <sup>(1)</sup>           | CH0SB3 <sup>(1)</sup> | CH0SB2 <sup>(1)</sup>    | CH0SB1 <sup>(1)</sup> | CH0SB0 <sup>(1)</sup> |  |  |  |  |

| bit 15     |                                                                                                                    | -                                                                                                                |                                 |                       |                          |                       | bit 8                 |  |  |  |  |

|            |                                                                                                                    |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |  |

| R/W-0      | U-0                                                                                                                | U-0                                                                                                              | R/W-0                           | R/W-0                 | R/W-0                    | R/W-0                 | R/W-0                 |  |  |  |  |

| CH0NA      |                                                                                                                    | _                                                                                                                | CH0SA4 <sup>(1)</sup>           | CH0SA3 <sup>(1)</sup> | CH0SA2 <sup>(1)</sup>    | CH0SA1 <sup>(1)</sup> | CH0SA0 <sup>(1)</sup> |  |  |  |  |

| bit 7      |                                                                                                                    |                                                                                                                  |                                 |                       |                          |                       | bit C                 |  |  |  |  |

|            |                                                                                                                    |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |  |

| Legend:    |                                                                                                                    |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |  |

| R = Reada  |                                                                                                                    | W = Writable                                                                                                     |                                 |                       | nented bit, read         |                       |                       |  |  |  |  |

| -n = Value | e at POR                                                                                                           | '1' = Bit is set                                                                                                 |                                 | '0' = Bit is clea     | ared                     | x = Bit is unkn       | own                   |  |  |  |  |

| hit 15     |                                                                                                                    | annal O Nagativa                                                                                                 | Input Coloct for                | r Comple MUX          |                          |                       |                       |  |  |  |  |

| bit 15     |                                                                                                                    | nannel 0 Negative<br>el 0 negative input                                                                         |                                 |                       |                          |                       |                       |  |  |  |  |

|            |                                                                                                                    | el 0 negative input                                                                                              |                                 |                       |                          |                       |                       |  |  |  |  |

| bit 14-13  | Unimpleme                                                                                                          | ented: Read as '0                                                                                                | )'                              |                       |                          |                       |                       |  |  |  |  |

| bit 12-8   | CH0SB<4:0                                                                                                          | 0>: Channel 0 Po:                                                                                                | sitive Input Sele               | ect for Sample I      | MUXB bits <sup>(1)</sup> |                       |                       |  |  |  |  |

|            |                                                                                                                    | pen; use this sele                                                                                               |                                 |                       |                          | ement                 |                       |  |  |  |  |

|            | 11110 <b>= Ch</b>                                                                                                  | nannel 0 positive in                                                                                             | put is connected                | to the CTMU te        | mperature meas           | surement diode        | (CTMU TEMP            |  |  |  |  |

|            |                                                                                                                    | 11101 = Reserved                                                                                                 |                                 |                       |                          |                       |                       |  |  |  |  |

|            |                                                                                                                    | 11100 = Reserved                                                                                                 |                                 |                       |                          |                       |                       |  |  |  |  |

|            |                                                                                                                    | 11011 = Reserved<br>11010 = Channel 0 positive input is the output of OA3/AN6 <sup>(2,3)</sup>                   |                                 |                       |                          |                       |                       |  |  |  |  |

|            |                                                                                                                    | nannel 0 positive i                                                                                              |                                 |                       |                          |                       |                       |  |  |  |  |

|            |                                                                                                                    | nannel 0 positive i                                                                                              | input is the outp               | out of OA1/AN3        | (2)                      |                       |                       |  |  |  |  |

|            | 10111 <b>= Re</b>                                                                                                  | served                                                                                                           |                                 |                       |                          |                       |                       |  |  |  |  |

|            | •                                                                                                                  |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |  |

|            | •                                                                                                                  |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |  |

|            | 10000 <b>= Re</b>                                                                                                  |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |  |

|            | 01111 = Ch                                                                                                         | nannel 0 positive i                                                                                              | input is AN15 <sup>(3)</sup>    |                       |                          |                       |                       |  |  |  |  |

|            | 01110 = Channel 0 positive input is AN14 <sup>(3)</sup><br>01101 = Channel 0 positive input is AN13 <sup>(3)</sup> |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |  |

|            | •                                                                                                                  |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |  |

|            | •                                                                                                                  |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |  |

|            | •                                                                                                                  |                                                                                                                  | (2)                             |                       |                          |                       |                       |  |  |  |  |

|            | 00010 = Ch                                                                                                         | 00010 = Channel 0 positive input is $AN2^{(3)}$                                                                  |                                 |                       |                          |                       |                       |  |  |  |  |

|            |                                                                                                                    | 00001 = Channel 0 positive input is AN1 <sup>(3)</sup><br>00000 = Channel 0 positive input is AN0 <sup>(3)</sup> |                                 |                       |                          |                       |                       |  |  |  |  |

| bit 7      |                                                                                                                    | nannel 0 Negative                                                                                                | •                               | r Samnle MI IX        | Δ hit                    |                       |                       |  |  |  |  |

|            | CINIA. OI                                                                                                          | lanner o Negative                                                                                                | •                               |                       | A DIL                    |                       |                       |  |  |  |  |

|            | 1 = Channell                                                                                                       | 1 0 negative input                                                                                               | is AN1(1)                       |                       |                          |                       |                       |  |  |  |  |