Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 256КВ (85.5К х 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256gp202-h-mm |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| ABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED) |             |                |     |                                                                                  |  |  |  |  |

|-----------------------------------------------|-------------|----------------|-----|----------------------------------------------------------------------------------|--|--|--|--|

| Pin Name <sup>(4)</sup>                       | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                      |  |  |  |  |

| U2CTS                                         | Ι           | ST             | No  | UART2 Clear-To-Send.                                                             |  |  |  |  |

| U2RTS                                         | 0           | —              | No  | UART2 Ready-To-Send.                                                             |  |  |  |  |

| U2RX                                          | Ι           | ST             | Yes | UART2 receive.                                                                   |  |  |  |  |

| U2TX                                          | 0           | —              | Yes | UART2 transmit.                                                                  |  |  |  |  |

| BCLK2                                         | 0           | ST             | No  | UART2 IrDA <sup>®</sup> baud clock output.                                       |  |  |  |  |

| SCK1                                          | I/O         | ST             | No  | Synchronous serial clock input/output for SPI1.                                  |  |  |  |  |

| SDI1                                          | I           | ST             | No  | SPI1 data in.                                                                    |  |  |  |  |

| SDO1                                          | 0           | —              | No  | SPI1 data out.                                                                   |  |  |  |  |

| SS1                                           | I/O         | ST             | No  | SPI1 slave synchronization or frame pulse I/O.                                   |  |  |  |  |

| SCK2                                          | I/O         | ST             | Yes | Synchronous serial clock input/output for SPI2.                                  |  |  |  |  |

| SDI2                                          | I           | ST             | Yes | SPI2 data in.                                                                    |  |  |  |  |

| SDO2                                          | 0           | _              | Yes | s SPI2 data out.                                                                 |  |  |  |  |

| SS2                                           | I/O         | ST             | Yes | es SPI2 slave synchronization or frame pulse I/O.                                |  |  |  |  |

| SCL1                                          | I/O         | ST             | No  | Synchronous serial clock input/output for I2C1.                                  |  |  |  |  |

| SDA1                                          | I/O         | ST             | No  | Synchronous serial data input/output for I2C1.                                   |  |  |  |  |

| ASCL1                                         | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C1.                        |  |  |  |  |

| ASDA1                                         | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C1.                         |  |  |  |  |

| SCL2                                          | I/O         | ST             | No  | Synchronous serial clock input/output for I2C2.                                  |  |  |  |  |

| SDA2                                          | I/O         | ST             | No  | Synchronous serial data input/output for I2C2.                                   |  |  |  |  |

| ASCL2                                         | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C2.                        |  |  |  |  |

| ASDA2                                         | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C2.                         |  |  |  |  |

| TMS <sup>(5)</sup>                            | Ι           | ST             | No  | JTAG Test mode select pin.                                                       |  |  |  |  |

| TCK                                           | Ι           | ST             | No  | JTAG test clock input pin.                                                       |  |  |  |  |

| TDI                                           | I           | ST             | No  | JTAG test data input pin.                                                        |  |  |  |  |

| TDO                                           | 0           | _              | No  | JTAG test data output pin.                                                       |  |  |  |  |

| C1RX <sup>(2)</sup>                           | Ι           | ST             | Yes | ECAN1 bus receive pin.                                                           |  |  |  |  |

| C1TX <sup>(2)</sup>                           | 0           | _              | Yes | ECAN1 bus transmit pin.                                                          |  |  |  |  |

| FLT1 <sup>(1)</sup> , FLT2 <sup>(1)</sup>     | Ι           | ST             | Yes | PWM Fault Inputs 1 and 2.                                                        |  |  |  |  |

| FLT3 <sup>(1)</sup> , FLT4 <sup>(1)</sup>     | Ι           | ST             | No  | PWM Fault Inputs 3 and 4.                                                        |  |  |  |  |

| FLT32 <sup>(1,3)</sup>                        | Ι           | ST             | No  | PWM Fault Input 32 (Class B Fault).                                              |  |  |  |  |

| DTCMP1-DTCMP3 <sup>(1)</sup>                  | Ι           | ST             | Yes | PWM Dead-Time Compensation Inputs 1 through 3.                                   |  |  |  |  |

| PWM1L-PWM3L <sup>(1)</sup>                    | 0           | —              | No  | PWM Low Outputs 1 through 3.                                                     |  |  |  |  |

| PWM1H-PWM3H <sup>(1)</sup>                    | 0           | —              | No  | PWM High Outputs 1 through 3.                                                    |  |  |  |  |

| SYNCI1 <sup>(1)</sup>                         | Ι           | ST             |     | PWM Synchronization Input 1.                                                     |  |  |  |  |

| SYNCO1 <sup>(1)</sup>                         | 0           |                | Yes | PWM Synchronization Output 1.                                                    |  |  |  |  |

| INDX1 <sup>(1)</sup>                          | Ι           | ST             | Yes | Quadrature Encoder Index1 pulse input.                                           |  |  |  |  |

| HOME1 <sup>(1)</sup>                          | Ι           | ST             | Yes | Quadrature Encoder Home1 pulse input.                                            |  |  |  |  |

| QEA1 <sup>(1)</sup>                           | Ι           | ST             | Yes | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer                   |  |  |  |  |

| QEB1 <sup>(1)</sup>                           | ,           | ст             | Vee | external clock/gate input in Timer mode.                                         |  |  |  |  |

|                                               | Ι           | ST             | Yes | Quadrature Encoder Phase B input in QEI1 mode. Auxiliary timer                   |  |  |  |  |

| CNTCMP1 <sup>(1)</sup>                        | 0           |                | Yes | external clock/gate input in Timer mode.<br>Quadrature Encoder Compare Output 1. |  |  |  |  |

|                                               | 0           | <br>ompatible  | 162 |                                                                                  |  |  |  |  |

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend:

CMOS = CMOS compatible input or output

Analog = Analog input

ST = Schmitt Trigger input with CMOS levels

O = Output

PPS = Peripheral Pin Select

TTL = TTL input buffer

P = Power I = Input

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

5: There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

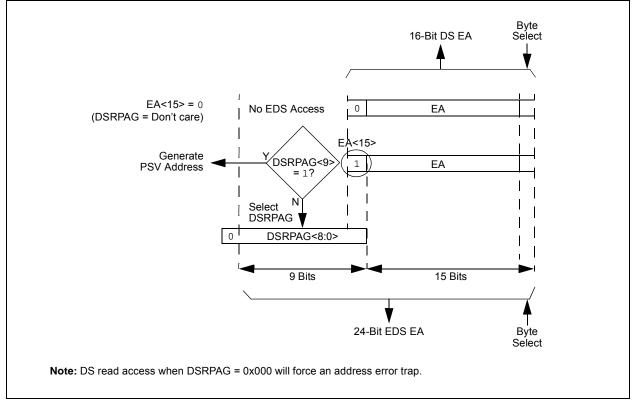

#### 4.4.1 PAGED MEMORY SCHEME

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre-modified and post-modified Effective Addresses (EA). The upper half of the base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Read Page register (DSRPAG) or the 9-bit Write Page register (DSWPAG), to form an Extended Data Space (EDS) address or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

Construction of the EDS address is shown in Example 4-1. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when base address bit, EA<15> = 1, DSWPAG<8:0> are concatenated onto EA<14:0> to form the 24-bit EDS write address.

| R/W-0         | R/W-0        | R/W-0                                                 | R/W-0   | R/W-0             | R/W-0                 | R/W-0                | U-0   |

|---------------|--------------|-------------------------------------------------------|---------|-------------------|-----------------------|----------------------|-------|

| T5MD          | T4MD         | T3MD                                                  | T2MD    | T1MD              | QEI1MD <sup>(1)</sup> | PWMMD <sup>(1)</sup> | _     |

| bit 15        |              |                                                       |         |                   |                       |                      | bit   |

|               |              |                                                       |         |                   |                       |                      |       |

| R/W-0         | R/W-0        | R/W-0                                                 | R/W-0   | R/W-0             | U-0                   | R/W-0                | R/W-0 |

| I2C1MD        | U2MD         | U1MD                                                  | SPI2MD  | SPI1MD            | —                     | C1MD <sup>(2)</sup>  | AD1MD |

| bit 7         |              |                                                       |         |                   |                       |                      | bit   |

| Legend:       |              |                                                       |         |                   |                       |                      |       |

| R = Readabl   | e bit        | W = Writable                                          | bit     | U = Unimplen      | nented bit, read      | d as '0'             |       |

| -n = Value at | POR          | '1' = Bit is set                                      |         | '0' = Bit is clea | ared                  | x = Bit is unkno     | own   |

| bit 15        | 1 = Timer5 m | 5 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 14        | 1 = Timer4 m | 4 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 13        | 1 = Timer3 m | 3 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 12        | 1 = Timer2 m | 2 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 11        | 1 = Timer1 m | 1 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 10        | 1 = QEI1 mod | 11 Module Disa<br>Iule is disablec<br>Iule is enabled |         |                   |                       |                      |       |

| bit 9         | 1 = PWM mod  | /M Module Dis<br>dule is disabled<br>dule is enabled  | 1       |                   |                       |                      |       |

| bit 8         | Unimplemen   | ted: Read as '                                        | כי      |                   |                       |                      |       |

| bit 7         | 1 = I2C1 mod | 1 Module Disal<br>ule is disabled<br>ule is enabled   | ble bit |                   |                       |                      |       |

| bit 6         | 1 = UART2 m  | 2 Module Disa<br>odule is disabl<br>odule is enable   | ed      |                   |                       |                      |       |

| bit 5         | 1 = UART1 m  | 1 Module Disa<br>odule is disabl<br>odule is enable   | ed      |                   |                       |                      |       |

| bit 4         | 1 = SPI2 mod | 2 Module Disa<br>lule is disabled<br>lule is enabled  | ole bit |                   |                       |                      |       |

### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This bit is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

| U-0    | U-0 | R/W-0      | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------|-----|------------|------------|-------|-------|-------|-------|--|--|

| —      | —   |            | RP43R<5:0> |       |       |       |       |  |  |

| bit 15 |     |            | bit 8      |       |       |       |       |  |  |

|        |     |            |            |       |       |       |       |  |  |

| U-0    | U-0 | R/W-0      | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

| —      | —   | RP42R<5:0> |            |       |       |       |       |  |  |

#### REGISTER 11-22: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

|   | bit | 7 |

|---|-----|---|

| 1 |     |   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP43R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP43 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP42R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-23: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------|-----|-------|------------|-------|-------|-------|-------|--|--|

| —      | —   |       | RP55R<5:0> |       |       |       |       |  |  |

| bit 15 |     |       |            |       |       |       | bit 8 |  |  |

| U-0   | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-----|-------|------------|-------|-------|-------|-------|--|

| —     | —   |       | RP54R<5:0> |       |       |       |       |  |

| bit 7 |     |       |            |       |       |       | bit 0 |  |

| Legend:           |                                                             |                      |                    |  |

|-------------------|-------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | ble bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                            | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP55R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP55 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP54R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP54 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 0

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0    | R/W-0             | R/W-0                                   | R/W-0 | R/W-0 |

|----------------------------------------------------------------------|-------|------------------|----------|-------------------|-----------------------------------------|-------|-------|

|                                                                      |       |                  | TRGC     | MP<15:8>          |                                         |       |       |

| bit 15                                                               |       |                  |          |                   |                                         |       | bit 8 |

|                                                                      |       |                  |          |                   |                                         |       |       |

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0    | R/W-0             | R/W-0                                   | R/W-0 | R/W-0 |

|                                                                      |       |                  | TRGC     | MP<7:0>           |                                         |       |       |

| bit 7                                                                |       |                  |          |                   |                                         |       | bit 0 |

| Legend:                                                              |       |                  |          |                   |                                         |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                  | d as '0' |                   |                                         |       |       |

| -n = Value at P                                                      | OR    | '1' = Bit is set |          | '0' = Bit is clea | '0' = Bit is cleared x = Bit is unknown |       |       |

### REGISTER 16-14: TRIGX: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER

bit 15-0 TRGCMP<15:0>: Trigger Control Value bits

When the primary PWMx functions in local time base, this register contains the compare values that can trigger the ADC module.

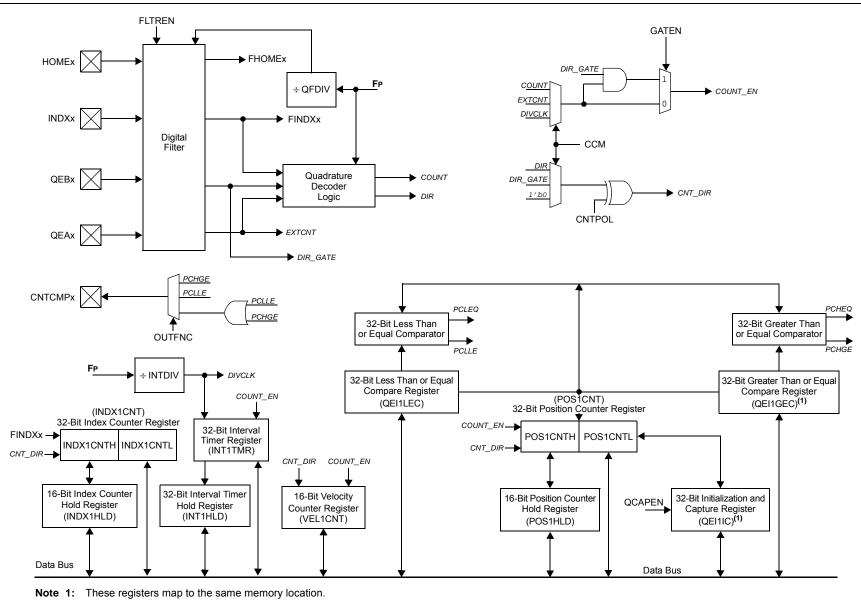

#### FIGURE 17-1: QEI BLOCK DIAGRAM

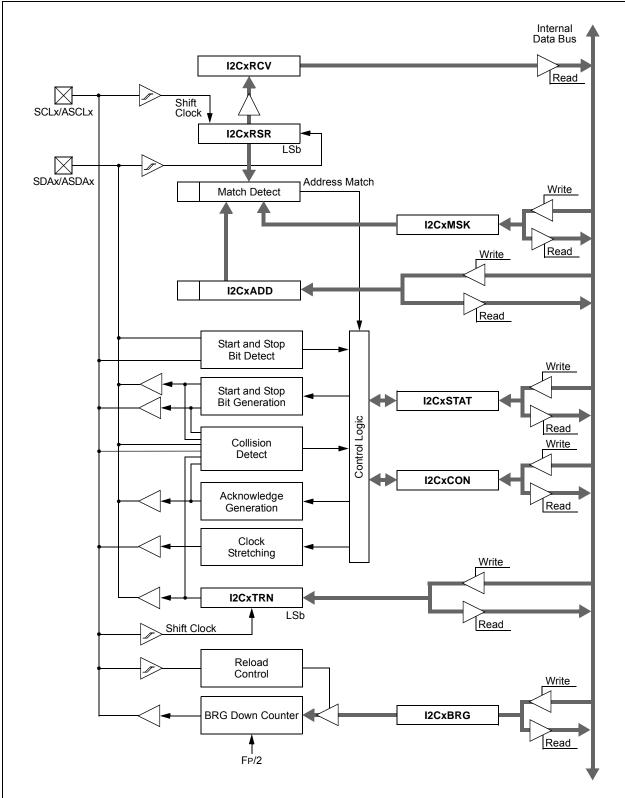

FIGURE 19-1: I2Cx BLOCK DIAGRAM (X = 1 OR 2)

| R-0, HSC                          | R-0, HSC  | U-0               | U-0                                | U-0                        | R/C-0, HS | R-0, HSC                              | R-0, HSC |  |

|-----------------------------------|-----------|-------------------|------------------------------------|----------------------------|-----------|---------------------------------------|----------|--|

| ACKSTAT                           | TRSTAT    | _                 | _                                  | —                          | BCL       | GCSTAT                                | ADD10    |  |

| bit 15 bi                         |           |                   |                                    |                            |           |                                       |          |  |

|                                   |           |                   |                                    |                            |           |                                       |          |  |

| R/C-0, HS                         | R/C-0, HS | R-0, HSC          | R/C-0, HSC                         | R/C-0, HSC                 | R-0, HSC  | R-0, HSC                              | R-0, HSC |  |

| IWCOL                             | I2COV     | D_A               | Р                                  | S                          | R_W       | RBF                                   | TBF      |  |

| bit 7                             |           |                   |                                    |                            |           |                                       | bit 0    |  |

|                                   |           |                   |                                    |                            |           |                                       |          |  |

| Legend: C                         |           | C = Clearable bit |                                    | HS = Hardware Settable bit |           | HSC = Hardware Settable/Clearable bit |          |  |

| R = Readable bit W = Writable bit |           | e bit             | U = Unimplemented bit, read as '0' |                            |           |                                       |          |  |

| -n = Value at POR                 |           | '1' = Bit is se   | et                                 | '0' = Bit is cleared       |           | x = Bit is unknown                    |          |  |

#### REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER

| bit 15       | <b>ACKSTAT:</b> Acknowledge Status bit (when operating as $I^2C^{TM}$ master, applicable to master transmit operation)                         |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10       | 1 = NACK received from slave                                                                                                                   |

|              | 0 = ACK received from slave                                                                                                                    |

|              | Hardware is set or clear at the end of slave Acknowledge.                                                                                      |

| bit 14       | TRSTAT: Transmit Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                               |

|              | 1 = Master transmit is in progress (8 bits + ACK)                                                                                              |

|              | 0 = Master transmit is not in progress                                                                                                         |

|              | Hardware is set at the beginning of master transmission. Hardware is clear at the end of slave Acknowledge.                                    |

| bit 13-11    | Unimplemented: Read as '0'                                                                                                                     |

| bit 10       | BCL: Master Bus Collision Detect bit                                                                                                           |

|              | 1 = A bus collision has been detected during a master operation                                                                                |

|              | 0 = No bus collision detected<br>Hardware is set at detection of a bus collision.                                                              |

| <b>h</b> # 0 |                                                                                                                                                |

| bit 9        | GCSTAT: General Call Status bit                                                                                                                |

|              | 1 = General call address was received<br>0 = General call address was not received                                                             |

|              | Hardware is set when address matches general call address. Hardware is clear at Stop detection.                                                |

| bit 8        | ADD10: 10-Bit Address Status bit                                                                                                               |

|              | 1 = 10-bit address was matched                                                                                                                 |

|              | 0 = 10-bit address was not matched                                                                                                             |

|              | Hardware is set at the match of the 2nd byte of the matched 10-bit address. Hardware is clear at Stop                                          |

|              | detection.                                                                                                                                     |

| bit 7        | IWCOL: I2Cx Write Collision Detect bit                                                                                                         |

|              | <ul> <li>1 = An attempt to write to the I2CxTRN register failed because the I<sup>2</sup>C module is busy</li> <li>0 = No collision</li> </ul> |

|              | Hardware is set at the occurrence of a write to I2CxTRN while busy (cleared by software).                                                      |

| bit 6        | <b>I2COV:</b> I2Cx Receive Overflow Flag bit                                                                                                   |

|              | 1 = A byte was received while the I2CxRCV register was still holding the previous byte                                                         |

|              | 0 = No overflow                                                                                                                                |

|              | Hardware is set at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                            |

| bit 5        | <b>D_A:</b> Data/Address bit (when operating as I <sup>2</sup> C slave)                                                                        |

|              | 1 = Indicates that the last byte received was data                                                                                             |

|              | 0 = Indicates that the last byte received was a device address                                                                                 |

|              | Hardware is clear at a device address match. Hardware is set by reception of a slave byte.                                                     |

| bit 4        | P: Stop bit                                                                                                                                    |

|              | 1 = Indicates that a Stop bit has been detected last                                                                                           |

|              | 0 = Stop bit was not detected last<br>Hardware is set or clear when a Start, Repeated Start or Stop is detected.                               |

|              |                                                                                                                                                |

|              |                                                                                                                                                |

#### REGISTER 21-19: CxFMSKSEL2: ECANx FILTER 15-8 MASK SELECTION REGISTER 2

| R/W-0                                          | R/W-0                                                                                                                | R/W-0                                                                                                                 | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                   | R/W-0                        | R/W-0  |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------|--------|

| F15M                                           | ISK<1:0>                                                                                                             | F14MS                                                                                                                 | F14MSK<1:0>                                                                                                                                          |                                                                                                                           | F13MSK<1:0>                                                             |                              | K<1:0> |

| bit 15                                         |                                                                                                                      |                                                                                                                       |                                                                                                                                                      |                                                                                                                           |                                                                         |                              | bit 8  |

|                                                |                                                                                                                      | 54446                                                                                                                 | 5444                                                                                                                                                 |                                                                                                                           |                                                                         | 5444.0                       |        |

| R/W-0                                          | R/W-0                                                                                                                | R/W-0                                                                                                                 | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                   | R/W-0                        | R/W-0  |

| F11M                                           | ISK<1:0>                                                                                                             | F10MS                                                                                                                 | K<1:0>                                                                                                                                               | F9MS                                                                                                                      | K<1:0>                                                                  | F8MSI                        | <<1:0> |

| bit 7                                          |                                                                                                                      |                                                                                                                       |                                                                                                                                                      |                                                                                                                           |                                                                         |                              | bit C  |

|                                                |                                                                                                                      |                                                                                                                       |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |        |

| Legend:                                        |                                                                                                                      |                                                                                                                       |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |        |

| R = Readable                                   | e bit                                                                                                                | W = Writable                                                                                                          | bit                                                                                                                                                  | U = Unimplem                                                                                                              | nented bit, read                                                        | l as '0'                     |        |

| -n = Value at                                  | POR                                                                                                                  | '1' = Bit is set                                                                                                      |                                                                                                                                                      | '0' = Bit is clea                                                                                                         | ared                                                                    | x = Bit is unkr              | nown   |

| bit 15 14                                      | ELEMOK A                                                                                                             | n. Maak Saura                                                                                                         | o for Filtor 15                                                                                                                                      | hita                                                                                                                      |                                                                         |                              |        |

|                                                | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta                                                          | ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg                                                                 | gisters contair<br>gisters contair<br>gisters contair                                                                                                | n mask<br>n mask<br>n mask                                                                                                |                                                                         |                              |        |

|                                                | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta                                                          | ed<br>ance Mask 2 reg<br>ance Mask 1 reg                                                                              | gisters contair<br>gisters contair<br>gisters contair                                                                                                | n mask<br>n mask<br>n mask                                                                                                | ies as bits<15:                                                         | 14>)                         |        |

| bit 13-12                                      | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0                                            | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg                                                           | gisters contair<br>gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14                                                          | n mask<br>n mask<br>n mask<br>n mask<br>bits (same valu                                                                   |                                                                         |                              |        |

| bit 15-14<br>bit 13-12<br>bit 11-10<br>bit 9-8 | 11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0                             | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Source                              | gisters contair<br>gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13                                       | n mask<br>n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu                                                | ies as bits<15:                                                         | 14>)                         |        |

| bit 13-12<br>bit 11-10                         | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0<br>F12MSK<1:0                | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Source<br><b>0&gt;:</b> Mask Source | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12                                       | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu                                       | ies as bits<15:<br>ies as bits<15:                                      | 14>)<br>14>)                 |        |

| bit 13-12<br>bit 11-10<br>bit 9-8              | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0<br>F12MSK<1:0<br>F11MSK<1:0  | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br>0>: Mask Source<br>0>: Mask Source<br>0>: Mask Source  | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12<br>e for Filter 11                    | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu                    | ies as bits<15:<br>ies as bits<15:<br>es as bits<15:′                   | 14>)<br>14>)<br>14>)         |        |

| bit 13-12<br>bit 11-10<br>bit 9-8<br>bit 7-6   | 11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0<br>F11MSK<1:0<br>F11MSK<1:0 | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br>0>: Mask Source<br>0>: Mask Source<br>0>: Mask Source  | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12<br>e for Filter 11<br>e for Filter 10 | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu | ies as bits<15:<br>ies as bits<15:<br>es as bits<15:<br>ies as bits<15: | 14>)<br>14>)<br>14>)<br>14>) |        |

| REGISTER 21-26: | CxTRmnCON: ECANx TX/RX BUFFER mn CONTROL REGISTER |

|-----------------|---------------------------------------------------|

|                 | (m = 0,2,4,6; n = 1,3,5,7)                        |

|               | <b>`</b>                                                       |                                  |                                |                          |                  |                 |                 |  |  |  |

|---------------|----------------------------------------------------------------|----------------------------------|--------------------------------|--------------------------|------------------|-----------------|-----------------|--|--|--|

| R/W-0         | R-0                                                            | R-0                              | R-0                            | R/W-0                    | R/W-0            | R/W-0           | R/W-0           |  |  |  |

| TXENn         | TXABTn                                                         | TXLARBn                          | TXERRn                         | TXREQn                   | RTRENn           | TXnPRI1         | TXnPRI0         |  |  |  |

| bit 15        |                                                                |                                  |                                |                          |                  |                 | bit 8           |  |  |  |

| R/W-0         | R-0                                                            | R-0                              | R-0                            | R/W-0                    | R/W-0            | R/W-0           | R/W-0           |  |  |  |

| TXENm         | TXABTm <sup>(1)</sup>                                          | TXLARBm <sup>(1)</sup>           | TXERRm <sup>(1)</sup>          | TXREQm                   | RTRENm           | TXmPRI1         | TXmPRI0         |  |  |  |

| bit 7         |                                                                | 1                                | 1                              |                          |                  |                 | bit (           |  |  |  |

| Legend:       |                                                                |                                  |                                |                          |                  |                 |                 |  |  |  |

| R = Readable  | e bit                                                          | W = Writable                     | bit                            | U = Unimpler             | mented bit, read | d as '0'        |                 |  |  |  |

| -n = Value at | POR                                                            | '1' = Bit is set                 |                                | '0' = Bit is cle         | ared             | x = Bit is unkr | nown            |  |  |  |

| bit 15-8      | See Dofinition                                                 | n for bits<7:0>,                 | Controls Ruffs                 | ar n                     |                  |                 |                 |  |  |  |

| bit 7         |                                                                | RX Buffer Sele                   |                                |                          |                  |                 |                 |  |  |  |

|               |                                                                | RA Buller Sele                   |                                |                          |                  |                 |                 |  |  |  |

|               |                                                                | RBn is a receive                 |                                |                          |                  |                 |                 |  |  |  |

| bit 6         | TXABTm: M                                                      | essage Aborted                   | 1 bit <sup>(1)</sup>           |                          |                  |                 |                 |  |  |  |

|               | 1 = Message                                                    | •                                |                                |                          |                  |                 |                 |  |  |  |

|               | •                                                              | completed trar                   | nsmission succ                 | essfully                 |                  |                 |                 |  |  |  |

| bit 5         | TXLARBm: N                                                     | Message Lost A                   | Arbitration bit <sup>(1)</sup> | )                        |                  |                 |                 |  |  |  |

|               |                                                                | lost arbitration                 |                                |                          |                  |                 |                 |  |  |  |

|               | 0 = Message                                                    | did not lose ar                  | bitration while                | being sent               |                  |                 |                 |  |  |  |

| bit 4         | TXERRm: Er                                                     | ror Detected D                   | uring Transmis                 | ssion bit <sup>(1)</sup> |                  |                 |                 |  |  |  |

|               |                                                                | or occurred wh                   | •                              | •                        |                  |                 |                 |  |  |  |

|               | 0 = A bus error did not occur while the message was being sent |                                  |                                |                          |                  |                 |                 |  |  |  |

| bit 3         |                                                                | essage Send F                    | -                              |                          |                  |                 |                 |  |  |  |

|               | sent                                                           |                                  | -                              |                          | -                | n the message   | is successfully |  |  |  |

|               |                                                                | the bit to '0' wh                | •                              | 0                        | abort            |                 |                 |  |  |  |

| bit 2         |                                                                | uto-Remote Tra                   |                                |                          |                  |                 |                 |  |  |  |

|               |                                                                | emote transmit<br>emote transmit |                                |                          |                  |                 |                 |  |  |  |

| bit 1-0       | TXmPRI<1:0                                                     | >: Message Tra                   | ansmission Pri                 | ority bits               |                  |                 |                 |  |  |  |

|               |                                                                | message prior                    |                                |                          |                  |                 |                 |  |  |  |

|               |                                                                | ermediate mes                    |                                |                          |                  |                 |                 |  |  |  |

|               |                                                                | ermediate mess<br>message priori |                                |                          |                  |                 |                 |  |  |  |

|               | 00 – Lowesi                                                    | messaye priori                   | ıy                             |                          |                  |                 |                 |  |  |  |

| Note 1: Th    | nis bit is cleared                                             | when TXREQ i                     | s set.                         |                          |                  |                 |                 |  |  |  |

|               |                                                                |                                  |                                |                          |                  |                 |                 |  |  |  |

Note: The buffers, SID, EID, DLC, Data Field, and Receive Status registers are located in DMA RAM.

#### FIGURE 22-1: CTMU BLOCK DIAGRAM

5: The switch connected to ADC CH0 is closed when IDISSEN (CTMUCON1<9>) = 1, and opened when IDISSEN = 0.

#### 22.1 CTMU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 22.1.1 KEY RESOURCES

- "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

#### REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER (CONTINUED)

- PTGITM<1:0>: PTG Input Trigger Command Operating Mode bits<sup>(1)</sup>

- 11 = Single level detect with Step delay not executed on exit of command (regardless of the PTGCTRL command)

- 10 = Single level detect with Step delay executed on exit of command

- 01 = Continuous edge detect with Step delay not executed on exit of command (regardless of the PTGCTRL command)

- 00 = Continuous edge detect with Step delay executed on exit of command

- Note 1: These bits apply to the PTGWHI and PTGWLO commands only.

bit 1-0

- **2:** This bit is only used with the PTGCTRL step command software trigger option.

- **3:** Use of the PTG Single-Step mode is reserved for debugging tools only.

NOTES:

#### 27.2 User ID Words

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices contain four User ID Words, located at addresses, 0x800FF8 through 0x800FFE. The User ID Words can be used for storing product information such as serial numbers, system manufacturing dates, manufacturing lot numbers and other application-specific information.

The User ID Words register map is shown in Table 27-3.

TABLE 27-3:USER ID WORDS REGISTER<br/>MAP

| File Name | Address  | Bits 23-16 | Bits 15-0 |

|-----------|----------|------------|-----------|

| FUID0     | 0x800FF8 | _          | UID0      |

| FUID1     | 0x800FFA | _          | UID1      |

| FUID2     | 0x800FFC | _          | UID2      |

| FUID3     | 0x800FFE | _          | UID3      |

**Legend:** — = unimplemented, read as '1'.

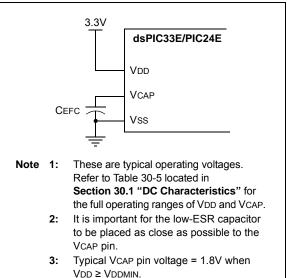

#### 27.3 On-Chip Voltage Regulator

All of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X devices power their core digital logic at a nominal 1.8V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family incorporate an onchip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. A low-ESR (less than 1 Ohm) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 30-5 located in **Section 30.0 "Electrical Characteristics"**.

Note: It is important for the low-ESR capacitor to be placed as close as possible to the VCAP pin.

# FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE

REGULATOR<sup>(1,2,3)</sup>

### 27.4 Brown-out Reset (BOR)

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated supply voltage, VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT Time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM is applied. The total delay in this case is TFSCM. Refer to Parameter SY35 in Table 30-22 of **Section 30.0 "Electrical Characteristics"** for specific TFSCM values.

The BOR status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

#### 29.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

#### 29.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

| TABLE 30-23: TIME | R1 EXTERNAL CLOCK TIMING REQUIREMENTS <sup>(1)</sup> | ) |

|-------------------|------------------------------------------------------|---|

|-------------------|------------------------------------------------------|---|

| AC CHARACTERISTICS |           |                                                                                                    | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                        |      |               |       |                                                                             |

|--------------------|-----------|----------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------|------|---------------|-------|-----------------------------------------------------------------------------|

| Param<br>No.       | Symbol    | Charao                                                                                             | cteristic <sup>(2)</sup>                             | Min.                                   | Тур. | Max.          | Units | Conditions                                                                  |

| TA10               | ТтхН      | T1CK High<br>Time                                                                                  | Synchronous<br>mode                                  | Greater of:<br>20 or<br>(Tcy + 20)/N   |      | _             | ns    | Must also meet<br>Parameter TA15,<br>N = prescaler value<br>(1, 8, 64, 256) |

|                    |           |                                                                                                    | Asynchronous                                         | 35                                     | _    | —             | ns    |                                                                             |

| TA11               | ΤτχL      | T1CK Low<br>Time                                                                                   | Synchronous<br>mode                                  | Greater of:<br>20 or<br>(Tcy + 20)/N   | _    | _             | ns    | Must also meet<br>Parameter TA15,<br>N = prescaler value<br>(1, 8, 64, 256) |

|                    |           |                                                                                                    | Asynchronous                                         | 10                                     |      | —             | ns    |                                                                             |

| TA15               | ΤτχΡ      | T1CK Input<br>Period                                                                               | Synchronous mode                                     | Greater of:<br>40 or<br>(2 Tcy + 40)/N | _    | —             | ns    | N = prescale value<br>(1, 8, 64, 256)                                       |

| OS60               | Ft1       | T1CK Oscillator Input<br>Frequency Range (oscillator<br>enabled by setting bit, TCS<br>(T1CON<1>)) |                                                      | DC                                     |      | 50            | kHz   |                                                                             |

| TA20               | TCKEXTMRL |                                                                                                    | Delay from External T1CK<br>Clock Edge to Timer      |                                        | _    | 1.75 Tcy + 40 | ns    |                                                                             |

Note 1: Timer1 is a Type A.

2: These parameters are characterized, but are not tested in manufacturing.

# TABLE 30-37:SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| AC CHA | ARACTERIS             | $\label{eq:standard} \begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |              |                     |                          |       |                                |

|--------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------|--------------------------|-------|--------------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                                               | Min.         | Тур. <sup>(2)</sup> | Max.                     | Units | Conditions                     |

| SP70   | FscP                  | Maximum SCK2 Input<br>Frequency                                                                                                                                                                                                                                                                             | -            | -                   | Lesser<br>of FP<br>or 15 | MHz   | (Note 3)                       |

| SP72   | TscF                  | SCK2 Input Fall Time                                                                                                                                                                                                                                                                                        | _            |                     |                          | ns    | See Parameter DO32<br>(Note 4) |

| SP73   | TscR                  | SCK2 Input Rise Time                                                                                                                                                                                                                                                                                        | —            |                     |                          | ns    | See Parameter DO31 (Note 4)    |

| SP30   | TdoF                  | SDO2 Data Output Fall Time                                                                                                                                                                                                                                                                                  | —            |                     |                          | ns    | See Parameter DO32<br>(Note 4) |

| SP31   | TdoR                  | SDO2 Data Output Rise Time                                                                                                                                                                                                                                                                                  | —            | _                   | _                        | ns    | See Parameter DO31 (Note 4)    |

| SP35   | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge                                                                                                                                                                                                                                                                   | —            | 6                   | 20                       | ns    |                                |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge                                                                                                                                                                                                                                                                | 30           | _                   | _                        | ns    |                                |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge                                                                                                                                                                                                                                                                  | 30           |                     |                          | ns    |                                |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge                                                                                                                                                                                                                                                                   | 30           |                     |                          | ns    |                                |

| SP50   | TssL2scH,<br>TssL2scL | $\overline{SS2}$ ↓ to SCK2 ↑ or SCK2 ↓<br>Input                                                                                                                                                                                                                                                             | 120          | _                   | _                        | ns    |                                |

| SP51   | TssH2doZ              | SS2 ↑ to SDO2 Output<br>High-Impedance                                                                                                                                                                                                                                                                      | 10           | _                   | 50                       | ns    | (Note 4)                       |

| SP52   | TscH2ssH<br>TscL2ssH  | SS2 ↑ after SCK2 Edge                                                                                                                                                                                                                                                                                       | 1.5 TCY + 40 | _                   | _                        | ns    | (Note 4)                       |

| SP60   | TssL2doV              | SDO2 Data Output Valid after<br>SS2 Edge                                                                                                                                                                                                                                                                    | —            |                     | 50                       | ns    |                                |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 66.7 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI2 pins.

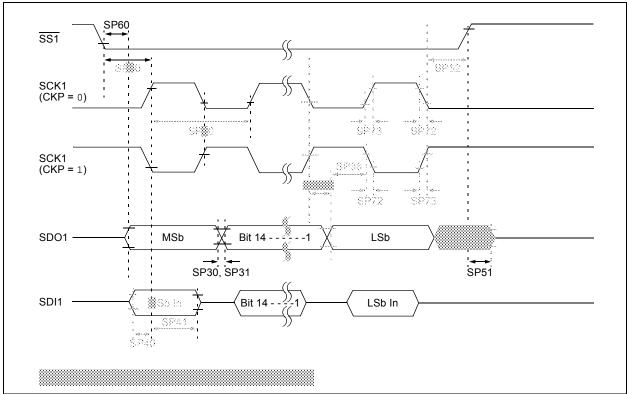

FIGURE 30-26: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

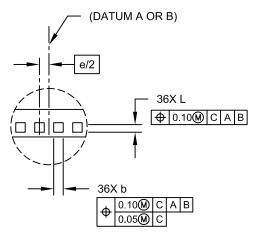

# 36-Terminal Very Thin Thermal Leadless Array Package (TL) – 5x5x0.9 mm Body with Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL A

|                         | MILLIMETERS |          |          |       |

|-------------------------|-------------|----------|----------|-------|

| Dimension               | MIN         | NOM      | MAX      |       |

| Number of Pins          | Ν           |          | 36       |       |

| Number of Pins per Side | ND          |          | 10       |       |

| Number of Pins per Side | NE          |          | 8        |       |

| Pitch                   | е           | 0.50 BSC |          |       |

| Overall Height          | Α           | 0.80     | 0.90     | 1.00  |

| Standoff                | A1          | 0.025    | -        | 0.075 |

| Overall Width           | E           |          | 5.00 BSC |       |

| Exposed Pad Width       | E2          | 3.60     | 3.75     | 3.90  |

| Overall Length          | D           |          | 5.00 BSC |       |

| Exposed Pad Length      | D2          | 3.60     | 3.75     | 3.90  |

| Contact Width           | b           | 0.20     | 0.25     | 0.30  |

| Contact Length          | L           | 0.20     | 0.25     | 0.30  |

| Contact-to-Exposed Pad  | К           | 0.20     | -        | -     |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-187C Sheet 2 of 2

#### 64-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |           |      |

|--------------------------|-------------|----------|-----------|------|

| E                        | MIN         | NOM      | MAX       |      |

| Number of Leads          | N           |          | 64        |      |

| Lead Pitch               | е           |          | 0.50 BSC  |      |

| Overall Height           | А           | -        | -         | 1.20 |

| Molded Package Thickness | A2          | 0.95     | 1.00      | 1.05 |

| Standoff                 | A1          | 0.05     | -         | 0.15 |

| Foot Length              | L           | 0.45     | 0.60      | 0.75 |

| Footprint                | L1          | 1.00 REF |           |      |

| Foot Angle               | φ           | 0°       | 3.5°      | 7°   |

| Overall Width            | E           |          | 12.00 BSC |      |

| Overall Length           | D           |          | 12.00 BSC |      |

| Molded Package Width     | E1          |          | 10.00 BSC |      |

| Molded Package Length    | D1          |          | 10.00 BSC |      |

| Lead Thickness           | С           | 0.09     | _         | 0.20 |

| Lead Width               | b           | 0.17     | 0.22      | 0.27 |

| Mold Draft Angle Top     | α           | 11°      | 12°       | 13°  |

| Mold Draft Angle Bottom  | β           | 11°      | 12°       | 13°  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085B