Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 28-SPDIP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256gp202-h-sp |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name <sup>(4)</sup>                        | Pin<br>Type         | Buffer<br>Type          | PPS              | Description                                                                                                                                                                        |

|------------------------------------------------|---------------------|-------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN15                                       | I                   | Analog                  | No               | Analog input channels.                                                                                                                                                             |

| CLKI                                           | I                   | ST/<br>CMOS             | No               | External clock source input. Always associated with OSC1 pin function                                                                                                              |

| CLKO                                           | 0                   | —                       | No               | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |

| OSC1                                           | I                   | ST/                     | No               | Oscillator crystal input. ST buffer when configured in RC mode; CMOS                                                                                                               |

| OSC2                                           | I/O                 | CMOS<br>—               | No               | otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.                          |

| REFCLKO                                        | 0                   |                         | Yes              | Reference clock output.                                                                                                                                                            |

| IC1-IC4                                        | Ι                   | ST                      | Yes              | Capture Inputs 1 through 4.                                                                                                                                                        |

| OCFA<br>OCFB<br>OC1-OC4                        | <br> <br> <br>0     | ST<br>ST                | Yes<br>No<br>Yes | Compare Fault A input (for Compare channels).<br>Compare Fault B input (for Compare channels).<br>Compare Outputs 1 through 4.                                                     |

| INT0                                           | I                   | ST                      | No               | External Interrupt 0.                                                                                                                                                              |

| INT1<br>INT2                                   |                     | ST<br>ST                | Yes<br>Yes       | External Interrupt 1.<br>External Interrupt 2.                                                                                                                                     |

| RA0-RA4, RA7-RA12                              | I/O                 | ST                      | No               | PORTA is a bidirectional I/O port.                                                                                                                                                 |

| RB0-RB15                                       | I/O                 | ST                      | No               | PORTB is a bidirectional I/O port.                                                                                                                                                 |

| RC0-RC13, RC15                                 | I/O                 | ST                      | No               | PORTC is a bidirectional I/O port.                                                                                                                                                 |

| RD5, RD6, RD8                                  | I/O                 | ST                      | No               | PORTD is a bidirectional I/O port.                                                                                                                                                 |

| RE12-RE15                                      | I/O                 | ST                      | No               | PORTE is a bidirectional I/O port.                                                                                                                                                 |

| RF0, RF1                                       | I/O                 | ST                      | No               | PORTF is a bidirectional I/O port.                                                                                                                                                 |

| RG6-RG9                                        | I/O                 | ST                      | No               | PORTG is a bidirectional I/O port.                                                                                                                                                 |

| T1CK                                           | Ι                   | ST                      | No               | Timer1 external clock input.                                                                                                                                                       |

| T2CK<br>T3CK                                   |                     | ST<br>ST                | Yes              | Timer2 external clock input.                                                                                                                                                       |

| T4CK                                           |                     | ST                      | No<br>No         | Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                       |

| T5CK                                           | i                   | ST                      | No               | Timer5 external clock input.                                                                                                                                                       |

| CTPLS                                          | 0                   | ST                      | No               | CTMU pulse output.                                                                                                                                                                 |

| CTED1                                          | Ι                   | ST                      | No               | CTMU External Edge Input 1.                                                                                                                                                        |

| CTED2                                          | Ι                   | ST                      | No               | CTMU External Edge Input 2.                                                                                                                                                        |

| U1CTS                                          | Ι                   | ST                      | No               | UART1 Clear-To-Send.                                                                                                                                                               |

| U1RTS                                          | 0                   |                         | No               | UART1 Ready-To-Send.                                                                                                                                                               |

| U1RX                                           |                     | ST                      | Yes              | UART1 receive.<br>UART1 transmit.                                                                                                                                                  |

| U1TX<br>BCLK1                                  | 0                   | ST                      | Yes<br>No        | UART1 Iransmit.<br>UART1 IrDA <sup>®</sup> baud clock output.                                                                                                                      |

| Legend: CMOS = CM<br>ST = Schmi<br>PPS = Perip | MOS co<br>itt Trigg | ompatible<br>er input v | input<br>with CN | or output Analog = Analog input P = Power                                                                                                                                          |

## TABLE 1-1:PINOUT I/O DESCRIPTIONS

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

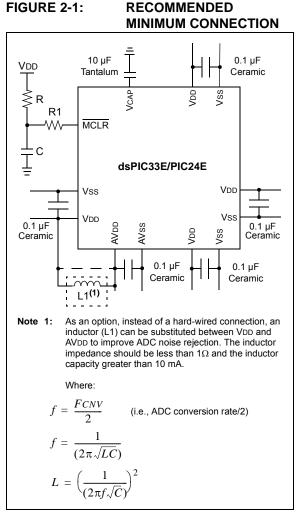

## 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

## 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 1 Ohm) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor greater than 4.7  $\mu$ F (10  $\mu$ F is recommended), 16V connected to ground. The type can be ceramic or tantalum. See **Section 30.0** "**Electrical Characteristics**" for additional information.

The placement of this capacitor should be close to the VCAP pin. It is recommended that the trace length not exceeds one-quarter inch (6 mm). See **Section 27.3 "On-Chip Voltage Regulator"** for details.

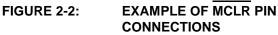

## 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor, C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components as shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

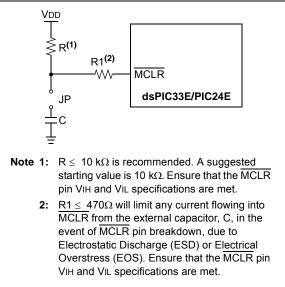

## 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-6).

Program memory addresses are always word-aligned on the lower word and addresses are incremented, or decremented by two, during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

## 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices reserve the addresses between 0x000000 and 0x000200 for hardcoded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of Flash memory, with the actual address for the start of code at address, 0x000002, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in **Section 7.1** "Interrupt Vector Table".

## FIGURE 4-6: PROGRAM MEMORY ORGANIZATION

| R/W-0                  | R/W-0                                                                            | R/W-0                                                                                                                                    | R/W-0                                | R/W-0                                | R/W-0                | R/W-0                | R/W-0                |  |  |  |

|------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------|----------------------|----------------------|----------------------|--|--|--|

| NSTDIS                 | OVAERR <sup>(1)</sup>                                                            | OVBERR <sup>(1)</sup>                                                                                                                    | COVAERR <sup>(1)</sup>               | COVBERR <sup>(1)</sup>               | OVATE <sup>(1)</sup> | OVBTE <sup>(1)</sup> | COVTE <sup>(1)</sup> |  |  |  |

| pit 15                 |                                                                                  |                                                                                                                                          |                                      |                                      |                      |                      | bit 8                |  |  |  |

|                        |                                                                                  |                                                                                                                                          |                                      |                                      |                      |                      |                      |  |  |  |

| R/W-0                  | R/W-0                                                                            | R/W-0                                                                                                                                    | R/W-0                                | R/W-0                                | R/W-0                | R/W-0                | U-0                  |  |  |  |

| SFTACERR <sup>(1</sup> | ) DIV0ERR                                                                        | DMACERR                                                                                                                                  | MATHERR                              | ADDRERR                              | STKERR               | OSCFAIL              | —                    |  |  |  |

| pit 7                  |                                                                                  |                                                                                                                                          |                                      |                                      |                      |                      | bit 0                |  |  |  |

|                        |                                                                                  |                                                                                                                                          |                                      |                                      |                      |                      |                      |  |  |  |

| _egend:                |                                                                                  |                                                                                                                                          |                                      |                                      |                      |                      |                      |  |  |  |

| R = Readable           |                                                                                  | W = Writable                                                                                                                             |                                      | U = Unimpleme                        |                      |                      |                      |  |  |  |

| n = Value at           | POR                                                                              | '1' = Bit is set                                                                                                                         |                                      | '0' = Bit is clear                   | ed                   | x = Bit is unk       | nown                 |  |  |  |

| bit 15                 | NSTDIS: Inte                                                                     | errupt Nesting                                                                                                                           | Disable hit                          |                                      |                      |                      |                      |  |  |  |

|                        |                                                                                  | nesting is disa                                                                                                                          |                                      |                                      |                      |                      |                      |  |  |  |

|                        | •                                                                                | nesting is ena                                                                                                                           |                                      |                                      |                      |                      |                      |  |  |  |

| pit 14                 | -                                                                                | -                                                                                                                                        | Overflow Trap F                      | lag bit <sup>(1)</sup>               |                      |                      |                      |  |  |  |

|                        |                                                                                  |                                                                                                                                          | erflow of Accur                      |                                      |                      |                      |                      |  |  |  |

|                        | =                                                                                |                                                                                                                                          | overflow of A                        |                                      |                      |                      |                      |  |  |  |

| pit 13                 |                                                                                  | <b>OVBERR:</b> Accumulator B Overflow Trap Flag bit <sup>(1)</sup><br>1 = Trap was caused by overflow of Accumulator B                   |                                      |                                      |                      |                      |                      |  |  |  |

|                        |                                                                                  |                                                                                                                                          | erflow of Accur  v overflow of Accur |                                      |                      |                      |                      |  |  |  |

| pit 12                 | <b>COVAERR:</b> Accumulator A Catastrophic Overflow Trap Flag bit <sup>(1)</sup> |                                                                                                                                          |                                      |                                      |                      |                      |                      |  |  |  |

|                        | 1 = Trap was                                                                     | caused by ca                                                                                                                             | tastrophic over                      | flow of Accumula                     | ator A               |                      |                      |  |  |  |

| pit 11                 |                                                                                  | Trap was not caused by catastrophic overflow of Accumulator A<br>VBERR: Accumulator B Catastrophic Overflow Trap Flag bit <sup>(1)</sup> |                                      |                                      |                      |                      |                      |  |  |  |

|                        |                                                                                  |                                                                                                                                          | •                                    | flow of Accumula                     | •                    |                      |                      |  |  |  |

|                        | =                                                                                |                                                                                                                                          | -                                    | overflow of Accur                    | nulator B            |                      |                      |  |  |  |

| pit 10                 |                                                                                  |                                                                                                                                          | erflow Trap Ena                      | able bit <sup>(1)</sup>              |                      |                      |                      |  |  |  |

|                        | 1 = Trap ove<br>0 = Trap is d                                                    | rflow of Accum                                                                                                                           | ulator A                             |                                      |                      |                      |                      |  |  |  |

| pit 9                  | OVBTE: Acc                                                                       | umulator B Ov                                                                                                                            | erflow Trap En                       | able bit <sup>(1)</sup>              |                      |                      |                      |  |  |  |

|                        | 1 = Trap ove<br>0 = Trap is d                                                    | rflow of Accum<br>isabled                                                                                                                | ulator B                             |                                      |                      |                      |                      |  |  |  |

| oit 8                  | COVTE: Cat                                                                       | astrophic Over                                                                                                                           | flow Trap Enat                       | ole bit <sup>(1)</sup>               |                      |                      |                      |  |  |  |

|                        | 1 = Trap on o<br>0 = Trap is d                                                   |                                                                                                                                          | erflow of Accu                       | mulator A or B is                    | enabled              |                      |                      |  |  |  |

| oit 7                  | SFTACERR:                                                                        | Shift Accumul                                                                                                                            | ator Error Statu                     | us bit <sup>(1)</sup>                |                      |                      |                      |  |  |  |

|                        |                                                                                  | •                                                                                                                                        | •                                    | alid accumulator<br>invalid accumula |                      |                      |                      |  |  |  |

| oit 6                  | DIV0ERR: D                                                                       | ivide-by-Zero I                                                                                                                          | Error Status bit                     |                                      |                      |                      |                      |  |  |  |

|                        |                                                                                  |                                                                                                                                          | used by a divide<br>caused by a d    |                                      |                      |                      |                      |  |  |  |

|                        | DMACERR:                                                                         |                                                                                                                                          |                                      | -                                    |                      |                      |                      |  |  |  |

| oit 5                  |                                                                                  |                                                                                                                                          |                                      |                                      |                      |                      |                      |  |  |  |

## REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

## **REGISTER 8-7:** DMAXPAD: DMA CHANNEL X PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0                                                                     | R/W-0 | R/W-0        | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

|---------------------------------------------------------------------------|-------|--------------|-------|------------------------------------|-------|-------|-------|--|

|                                                                           |       |              | PAD   | <15:8>                             |       |       |       |  |

| bit 15                                                                    |       |              |       |                                    |       |       | bit 8 |  |

|                                                                           |       |              |       |                                    |       |       |       |  |

| R/W-0                                                                     | R/W-0 | R/W-0        | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

|                                                                           |       |              | PAE   | )<7:0>                             |       |       |       |  |

| bit 7                                                                     |       |              |       |                                    |       |       | bit 0 |  |

|                                                                           |       |              |       |                                    |       |       |       |  |

| Legend:                                                                   |       |              |       |                                    |       |       |       |  |

| R = Readable                                                              | bit   | W = Writable | bit   | U = Unimplemented bit, read as '0' |       |       |       |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow |       |              |       |                                    | nown  |       |       |  |

### bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

## REGISTER 8-8: DMAXCNT: DMA CHANNEL X TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0                                                                | U-0   | R/W-0 | R/W-0                    | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------------------------------------------------------------------|-------|-------|--------------------------|------------------------------------|-------|-------|-------|--|--|--|

| —                                                                  |       |       | CNT<13:8> <sup>(2)</sup> |                                    |       |       |       |  |  |  |

| bit 15                                                             |       |       |                          |                                    |       |       | bit 8 |  |  |  |

| R/W-0                                                              | R/W-0 | R/W-0 | R/W-0                    | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|                                                                    |       |       | CNT<                     | <7:0> <b>(2)</b>                   |       |       |       |  |  |  |

| bit 7                                                              |       |       |                          |                                    |       |       | bit 0 |  |  |  |

| Legend:                                                            |       |       |                          |                                    |       |       |       |  |  |  |

| R = Readable bit W = Writable bit                                  |       |       |                          | U = Unimplemented bit, read as '0' |       |       |       |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is |       |       |                          | x = Bit is unkr                    | nown  |       |       |  |  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

**2:** The number of DMA transfers = CNT<13:0> + 1.

## REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER (CONTINUED)

| bit 6-4 | SYNCSRC<2:0>: Synchronous Source Selection bits <sup>(1)</sup><br>111 = Reserved<br>100 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-0 | 100 = Reserved<br>011 = PTGO17 <sup>(2)</sup><br>010 = PTGO16 <sup>(2)</sup><br>001 = Reserved<br>000 = SYNCI1 input from PPS<br>SEVTPS<3:0>: PWMx Special Event Trigger Output Postscaler Select bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1111 = 1:16 Postscaler generates Special Event Trigger on every sixteenth compare match event</li> <li>.</li> <l< td=""></l<></ul> |

|         | 0000 = 1:1 Postscaler generates Special Event Trigger on every second compare match event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

- **Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

| U-0       R/W-0       R/W       R/W       R/W </th <th>R/W-0</th> <th>R/W-0</th> <th>R/W-0</th> <th>R/W-0</th> <th>R/W-0</th> <th>R/W-0</th> <th>U-0</th> <th>U-0</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0         | R/W-0                                 | R/W-0                             | R/W-0                            | R/W-0                   | R/W-0            | U-0               | U-0           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------|-----------------------------------|----------------------------------|-------------------------|------------------|-------------------|---------------|

| U-0       U-0       RW-0       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PHR           | PHF                                   | PLR                               | PLF                              | FLTLEBEN                | CLLEBEN          | —                 | _             |

| -         BCH <sup>(1)</sup> BCL <sup>(1)</sup> BPH         BPHL         BPLH         BPHH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 15        |                                       |                                   |                                  |                         |                  |                   | bit           |

| bit 7       t         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PHR: PWMxH Rising Edge Trigger Enable bit       1 = Rising edge of PWMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PWMxH         bit 14       PHF: PWMxH Falling Edge Trigger Enable bit       1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores rising edge of PWMxL       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL       1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking is applied to selected Fault input       1 = Leading-Edge Blanking is applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected Current-limit input       0 = Leading-Edge Blanking is applied to selected current-limit input         0 = Leading-Edge Blanking is applied to selected current-limit input       0 = Leading-Edge Blanking is applied to selected current-limit input         0 = Leading-Edge Blanking is applied to selected Current-limit input       0 = Leading-Edge Blanking is applied to sel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0           | U-0                                   | R/W-0                             | R/W-0                            | R/W-0                   | R/W-0            | R/W-0             | R/W-0         |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>nn = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 PHR: PWMxH Rising Edge Trigger Enable bit<br>1 = Rising edge of PWMxH will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxH<br>1 = Falling edge of PWMxH will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxH<br>1 = Falling edge of PWMxH will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores falling edge of PWMxH<br>1 = Rising edge of PWMxH will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxL<br>1 = Rising edge of PWMxL will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxL<br>1 = Falling edge of PWMxL will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxL<br>1 = Falling edge of PWMxL will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores falling edge of PWMxL<br>1 = Falling edge of PWMxL will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores falling edge of PWMxL<br>1 = Leading-Edge Blanking is applied to selected Fault input<br>0 = Leading-Edge Blanking is applied to selected Fault input<br>1 = Leading-Edge Blanking is applied to selected Current-limit input<br>1 = Leading-Edge Blanking is not applied to selected current-limit input<br>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high<br>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low<br>0 = No blanking when selected blanking signal Low Enable bit<br>1 = State blanking (of current-limit and/or Fault input signals) when Selected blanking signal is low<br>0 = No blanking when PWMxH dupt is high<br>0 = No blanking when PWMxH dupt signals) when PWMxH output is high<br>0 = No blanking when PWMxH tow Enable bit<br>1 = State blanking (of current-limit and/ | _             | _                                     | BCH <sup>(1)</sup>                | BCL <sup>(1)</sup>               | BPHH                    | BPHL             | BPLH              | BPLL          |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PHR: PWMxH Rising Edge Trigger Enable bit       1 = Rising edge of PWMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PWMxH         bit 14       PHF: PWMxH Falling Edge Trigger Enable bit       1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores falling edge of PWMxH         bit 13       PLR: PWMxL Rising Edge Trigger Enable bit       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PWMxL         bit 13       PLR: PWMxL Falling Edge Trigger Enable bit       1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking is not applied to selected Fault input         bit 11       FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit       1 = Leading-Edge Blanking is not applied to selected current-limit input         bit 5       BCH: Blanking is not applied to selected current-limit input       0 = Leading-Edge Blanking is not applied to selected current-limit input         bit 9-6       Unimplemented: Read as '0'       1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high         bit 4       BCL: Blanking in Selected Blanking signal is high       1 = State blanking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 7         |                                       |                                   |                                  |                         |                  |                   | bit           |

| n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PHR: PWMxH Rising Edge Trigger Enable bit       1 = Rising edge of PWMxH will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores rising edge of PWMxH       11 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxH       11 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores fising edge of PWMxL       0 = Leading-Edge Blanking ignores falling edge of PWMxL         bit 12       PLF: PWMxL Falling Edge Trigger Enable bit       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL       0 = Leading-Edge Blanking ignores falling edge of PWMxL         bit 11       FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit       1 = Leading-Edge Blanking is not applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected Fault input       0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input       0 = Leading-Edge Blanking signal Figh Enable bit         1 = State blanking in Selected Blanking Singal High Enable bit       1 = State blanking (of current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Legend:       |                                       |                                   |                                  |                         |                  |                   |               |

| <ul> <li>PHR: PWMxH Rising Edge Trigger Enable bit         <ol> <li>Rising edge of PWMxH will trigger Leading-Edge Blanking counter</li></ol></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R = Readabl   | e bit                                 | W = Writable                      | bit                              | U = Unimpler            | mented bit, read | as '0'            |               |

| <ul> <li>1 = Rising edge of PWMxH will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxH</li> <li>PHF: PWMxH Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxH</li> <li>PLR: PVMxL Rising Edge Trigger Enable bit</li> <li>1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>PLF: PWMxL Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>Det Leading-Edge Blanking ignores ralling edge of PWMxL</li> <li>D = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking Signal High Enable bit</li> <li>1 = Leading-Edge Blanking Signal Liph Enable bit<sup>(1)</sup></li> <li>1 = State blanking (or current-limit and/or Fault input signals) when selected blanking signal is high</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> <li>0 = No b</li></ul>                                                                                                                                                                | -n = Value at | POR                                   | '1' = Bit is set                  | :                                | '0' = Bit is cle        | ared             | x = Bit is unkr   | nown          |

| <ul> <li>1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxH</li> <li>bit 13 PLR: PWMxL Rising Edge Trigger Enable bit</li> <li>1 = Rising edge of PWMxL. will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>bit 12 PLF: PWMxL Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxL. will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxL</li> <li>bit 12 FLTLEBEN: Fault Input Leading-Edge Blanking Counter</li> <li>0 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when PWMxH output is nigh</li> <li>0 = No bla</li></ul>                                                                                                                                                                 | bit 15        | 1 = Rising ed                         | ge of PWMxH                       | will trigger Le                  | ading-Edge Bla          |                  |                   |               |

| <ul> <li>1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>pLF: PWMxL Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxL</li> <li>bit 11</li> <li>FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit</li> <li>1 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = No blanking when selected Blanking Signal Low Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when PWMxH dutput is high</li> <li>0 = No blanking when PWMxH Low Enable bit</li> <li>1 = State blanking (of</li></ul>                                                                                                                                                         | bit 14        | 1 = Falling ed                        | lge of PWMxH                      | will trigger Le                  | eading-Edge Bla         | 0                |                   |               |

| bit 12       PLF: PWMxL Falling Edge Trigger Enable bit         1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL         bit 11       FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit         1 = Leading-Edge Blanking is not applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected Fault input         0 = Leading-Edge Blanking is applied to selected Fault input         0 = Leading-Edge Blanking is applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = No blanking when selected Blanking signal Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low         0 = No blanking when P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 13        | 1 = Rising ed                         | ge of PWMxL                       | will trigger Le                  | ading-Edge Bla          |                  |                   |               |

| <ul> <li>1 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>1 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxL output is low</li> <li>0 = No blanking when PWMxL output is low</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li></ul>                                                                                                                                                             | bit 12        | 1 = Falling ed                        | lge of PWMxL                      | will trigger Le                  | ading-Edge Bla          |                  |                   |               |

| <ul> <li>1 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>bit 9-6</li> <li>Unimplemented: Read as '0'</li> <li>bit 5</li> <li>BCH: Blanking in Selected Blanking Signal High Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is hig</li> <li>0 = No blanking when selected blanking Signal Low Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is hig</li> <li>bit 4</li> <li>BCL: Blanking in Selected Blanking Signal Low Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is low</li> <li>0 = No blanking when PWMxL output is low</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxL Ligh Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking in PWMxL Low Enable bit</li> <li>1 = State blanking in PWMxL Low Enable bit</li> <li>1 = State blanking in PWMxL output is high</li> </ul>                                                                                                                                                                                                 | bit 11        | 1 = Leading-E                         | Edge Blanking                     | is applied to                    | selected Fault in       | nput             |                   |               |

| bit 5       BCH: Blanking in Selected Blanking Signal High Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high         bit 4       BCL: Blanking in Selected Blanking Signal Low Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low         bit 4       BCL: Blanking in Selected Blanking Signal Low Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low         bit 3       BPHH: Blanking in PWMxH High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high         0 = No blanking when PWMxH output is high         bit 2       BPHL: Blanking in PWMxH Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low         0 = No blanking when PWMxH output is low         bit 1       State blanking in PWMxH Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low         0 = No blanking when PWMxL output is low         bit 1       BPLH: Blanking in PWMxL High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high         0 = No blanking when PWMxL output is high         bit 0       BPLL: Blanking in PWMxL Low Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 10        | 1 = Leading-E                         | Edge Blanking                     | is applied to                    | selected current        | t-limit input    |                   |               |