Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256gp202-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

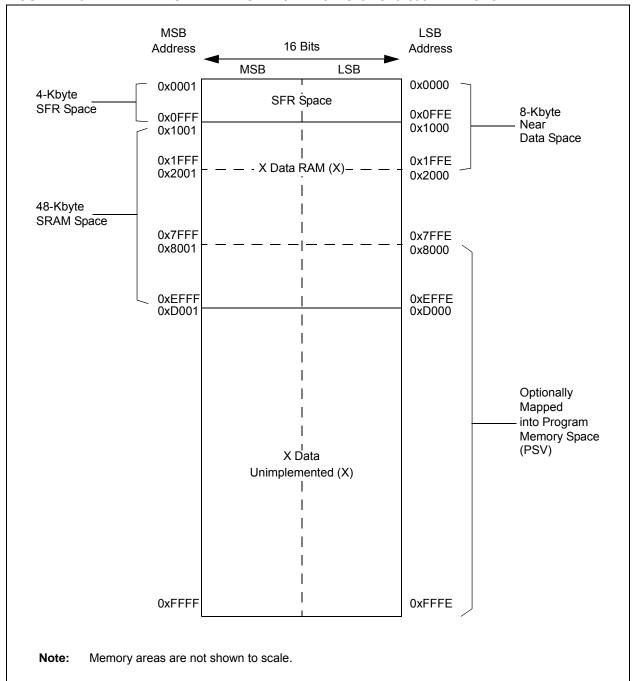

FIGURE 4-16: DATA MEMORY MAP FOR PIC24EP512GP/MC20X/50X DEVICES

#### 4.4.1 PAGED MEMORY SCHEME

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre-modified and post-modified Effective Addresses (EA). The upper half of the base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Read Page register (DSRPAG) or the 9-bit Write Page register (DSWPAG), to form an Extended Data Space (EDS)

address or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

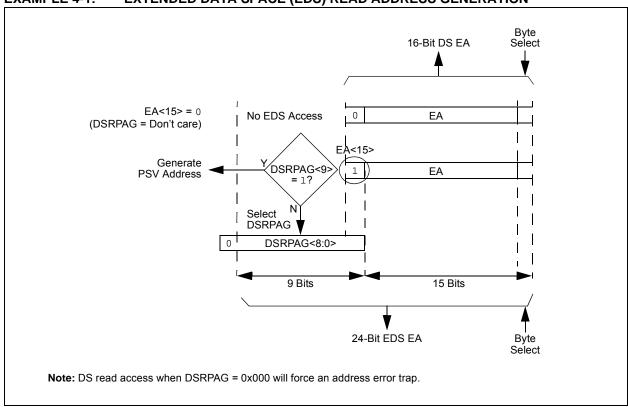

Construction of the EDS address is shown in Example 4-1. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when base address bit, EA<15> = 1, DSWPAG<8:0> are concatenated onto EA<14:0> to form the 24-bit EDS write address.

EXAMPLE 4-1: EXTENDED DATA SPACE (EDS) READ ADDRESS GENERATION

# 4.6 Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

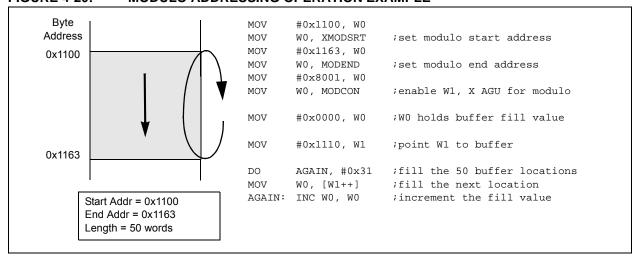

#### 4.6.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified, and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

**Note:** Y space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear).

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

# 4.6.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W register (YWM), to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit is set at MODCON<14>.

FIGURE 4-20: MODULO ADDRESSING OPERATION EXAMPLE

# REGISTER 11-5: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-----------|-------|-------|-------|

| _      |       |       |       | IC4R<6:0> |       |       |       |

| bit 15 |       |       |       |           |       |       | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-----------|-------|-------|-------|

| _     |       |       |       | IC3R<6:0> |       |       |       |

| bit 7 |       |       |       |           |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-8 IC4R<6:0>: Assign Input Capture 4 (IC4) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

.

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

bit 7 Unimplemented: Read as '0'

bit 6-0 IC3R<6:0>: Assign Input Capture 3 (IC3) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

:

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

| dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X |

|-----------------------------------------------------------------|

| NOTES:                                                          |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

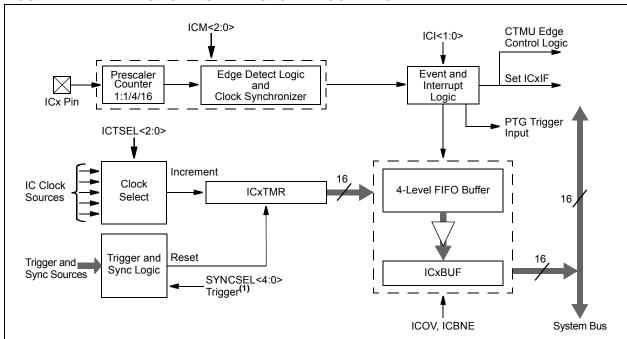

# 14.0 INPUT CAPTURE

Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70352) in the "dsPIC33/dsPIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices support four input capture channels.

Key features of the input capture module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 19 user-selectable Trigger/Sync sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- · Configurable interrupt generation

- Up to six clock sources available for each module, driving a separate internal 16-bit counter

#### FIGURE 14-1: INPUT CAPTURE x MODULE BLOCK DIAGRAM

Note 1: The Trigger/Sync source is enabled by default and is set to Timer3 as a source. This timer must be enabled for proper ICx module operation or the Trigger/Sync source must be changed to another source option.

# REGISTER 16-12: TRGCONx: PWMx TRIGGER CONTROL REGISTER

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------------|-------|-------|-------|-----|-----|-----|-------|

| TRGDIV<3:0> |       |       |       | _   | _   | _   |       |

| bit 15      |       |       |       |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0                  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|--------|------------------------|-------|-------|

| _     | _   |       |       | TRGSTF | RT<5:0> <sup>(1)</sup> |       |       |

| bit 7 |     |       |       |        |                        |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-12 **TRGDIV<3:0>:** Trigger # Output Divider bits

1111 = Trigger output for every 16th trigger event

1110 = Trigger output for every 15th trigger event

1101 = Trigger output for every 14th trigger event

1100 = Trigger output for every 13th trigger event

1011 = Trigger output for every 12th trigger event

1010 = Trigger output for every 11th trigger event

1001 = Trigger output for every 10th trigger event

1000 = Trigger output for every 9th trigger event

0111 = Trigger output for every 8th trigger event

0110 = Trigger output for every 7th trigger event

0101 = Trigger output for every 6th trigger event

0100 = Trigger output for every 5th trigger event

0011 = Trigger output for every 4th trigger event

0010 = Trigger output for every 3rd trigger event

0001 = Trigger output for every 2nd trigger event

0000 = Trigger output for every trigger event

bit 11-6 **Unimplemented:** Read as '0'

bit 5-0 TRGSTRT<5:0>: Trigger Postscaler Start Enable Select bits<sup>(1)</sup>

111111 = Waits 63 PWM cycles before generating the first trigger event after the module is enabled

•

000010 = Waits 2 PWM cycles before generating the first trigger event after the module is enabled 000001 = Waits 1 PWM cycle before generating the first trigger event after the module is enabled 000000 = Waits 0 PWM cycles before generating the first trigger event after the module is enabled

**Note 1:** The secondary PWM generator cannot generate PWMx trigger interrupts.

# REGISTER 18-3: SPIXCON2: SPIX CONTROL REGISTER 2

| R/W-0  | R/W-0  | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|--------|--------|-----|-----|-----|-----|-------|

| FRMEN  | SPIFSD | FRMPOL | _   | _   | _   | _   | _     |

| bit 15 |        |        |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  |

|-------|-----|-----|-----|-----|-----|--------|--------|

| _     | _   | _   | _   | _   | _   | FRMDLY | SPIBEN |

| bit 7 |     |     |     |     |     |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 FRMEN: Framed SPIx Support bit

1 = Framed SPIx support is enabled ( $\overline{SSx}$  pin is used as Frame Sync pulse input/output)

0 = Framed SPIx support is disabled

bit 14 SPIFSD: Frame Sync Pulse Direction Control bit

1 = Frame Sync pulse input (slave)0 = Frame Sync pulse output (master)

bit 13 FRMPOL: Frame Sync Pulse Polarity bit

1 = Frame Sync pulse is active-high

0 = Frame Sync pulse is active-low

bit 12-2 **Unimplemented:** Read as '0'

bit 1 FRMDLY: Frame Sync Pulse Edge Select bit

1 = Frame Sync pulse coincides with first bit clock0 = Frame Sync pulse precedes first bit clock

bit 0 SPIBEN: Enhanced Buffer Enable bit

1 = Enhanced buffer is enabled

0 = Enhanced buffer is disabled (Standard mode)

# REGISTER 21-6: CXINTF: ECANX INTERRUPT FLAG REGISTER (CONTINUED)

bit 1 RBIF: RX Buffer Interrupt Flag bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 0 TBIF: TX Buffer Interrupt Flag bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

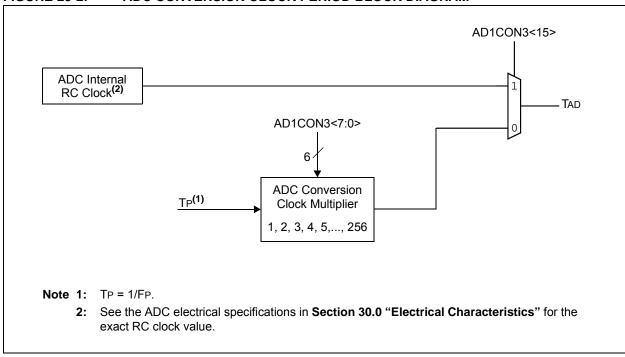

#### REGISTER 23-4: AD1CON4: ADC1 CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0   |

|--------|-----|-----|-----|-----|-----|-----|---------|

| _      | _   | _   | _   | _   | _   | _   | ADDMAEN |

| bit 15 |     |     |     |     |     |     | bit 8   |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|-----|-----|--------|--------|--------|

| _     | _   | _   | _   | _   | DMABL2 | DMABL1 | DMABL0 |

| bit 7 |     |     |     |     |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-9 **Unimplemented:** Read as '0'

bit 8 ADDMAEN: ADC1 DMA Enable bit

1 = Conversion results are stored in the ADC1BUF0 register for transfer to RAM using DMA

0 = Conversion results are stored in ADC1BUF0 through ADC1BUFF registers; DMA will not be used

bit 7-3 **Unimplemented:** Read as '0'

bit 2-0 DMABL<2:0>: Selects Number of DMA Buffer Locations per Analog Input bits

111 = Allocates 128 words of buffer to each analog input

110 = Allocates 64 words of buffer to each analog input

101 = Allocates 32 words of buffer to each analog input

100 = Allocates 16 words of buffer to each analog input

011 = Allocates 8 words of buffer to each analog input

010 = Allocates 4 words of buffer to each analog input

001 = Allocates 2 words of buffer to each analog input

000 = Allocates 1 word of buffer to each analog input

# REGISTER 23-6: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER (CONTINUED)

```

CH0SA<4:0>: Channel 0 Positive Input Select for Sample MUXA bits(1)

bit 4-0

11111 = Open; use this selection with CTMU capacitive and time measurement

11110 = Channel 0 positive input is connected to the CTMU temperature measurement diode (CTMU TEMP)

11101 = Reserved

11100 = Reserved

11011 = Reserved

11010 = Channel 0 positive input is the output of OA3/AN6<sup>(2,3)</sup>

11001 = Channel 0 positive input is the output of OA2/AN0<sup>(2)</sup>

11000 = Channel 0 positive input is the output of OA1/AN3<sup>(2)</sup>

10110 = Reserved

10000 = Reserved

01111 = Channel 0 positive input is AN15<sup>(1,3)</sup>

01110 = Channel 0 positive input is AN14<sup>(1,3)</sup>

01101 = Channel 0 positive input is AN13<sup>(1,3)</sup>

00010 = Channel 0 positive input is AN2(1,3)

00001 = Channel 0 positive input is AN1<sup>(1,3)</sup>

00000 = Channel 0 positive input is AN0^{(1,3)}

```

- Note 1: AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

- **3:** See the "Pin Diagrams" section for the available analog channels for each device.

#### REGISTER 27-1: DEVID: DEVICE ID REGISTER

| R      | R                           | R | R      | R                     | R | R | R      |  |  |  |

|--------|-----------------------------|---|--------|-----------------------|---|---|--------|--|--|--|

|        | DEVID<23:16> <sup>(1)</sup> |   |        |                       |   |   |        |  |  |  |

| bit 23 |                             |   |        |                       |   |   | bit 16 |  |  |  |

|        |                             |   |        |                       |   |   |        |  |  |  |

| R      | R                           | R | R      | R                     | R | R | R      |  |  |  |

|        |                             |   | DEVID< | :15:8> <sup>(1)</sup> |   |   |        |  |  |  |

| bit 15 |                             |   |        |                       |   |   | bit 8  |  |  |  |

|        |                             |   |        |                       |   |   | _      |  |  |  |

| R      | R                           | R | R      | R                     | R | R | R      |  |  |  |

|        |                             |   | DEVID  | <7·0>(1)              |   |   |        |  |  |  |

Legend: R = Read-Only bit U = Unimplemented bit

bit 23-0 **DEVID<23:0>:** Device Identifier bits<sup>(1)</sup>

bit 7

**Note 1:** Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration Bits" (DS70663) for the list of device ID values.

#### **REGISTER 27-2: DEVREV: DEVICE REVISION REGISTER**

| bit 16 |

|--------|

| bit 16 |

|        |

|        |

| R      |

|        |

| bit 8  |

|        |

| R      |

|        |

| bit 0  |

|        |

**Legend:** R = Read-only bit U = Unimplemented bit

bit 23-0 **DEVREV<23:0>:** Device Revision bits<sup>(1)</sup>

**Note 1:** Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration Bits" (DS70663) for the list of device revision values.

bit 0

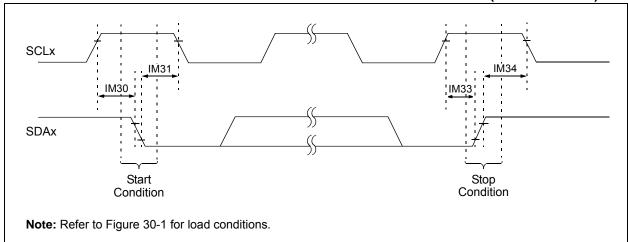

# FIGURE 30-30: I2Cx BUS START/STOP BITS TIMING CHARACTERISTICS (MASTER MODE)

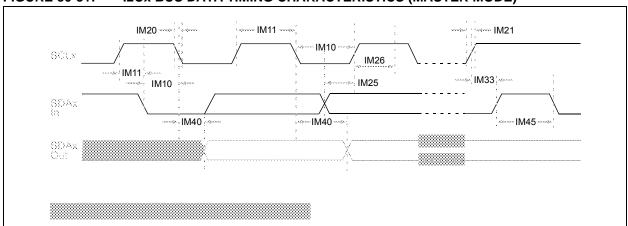

# FIGURE 30-31: I2Cx BUS DATA TIMING CHARACTERISTICS (MASTER MODE)

# 33.1 Package Marking Information (Continued)

36-Lead VTLA (TLA)

Example

44-Lead VTLA (TLA)

Example

44-Lead TQFP

Example

44-Lead QFN (8x8x0.9 mm)

Example

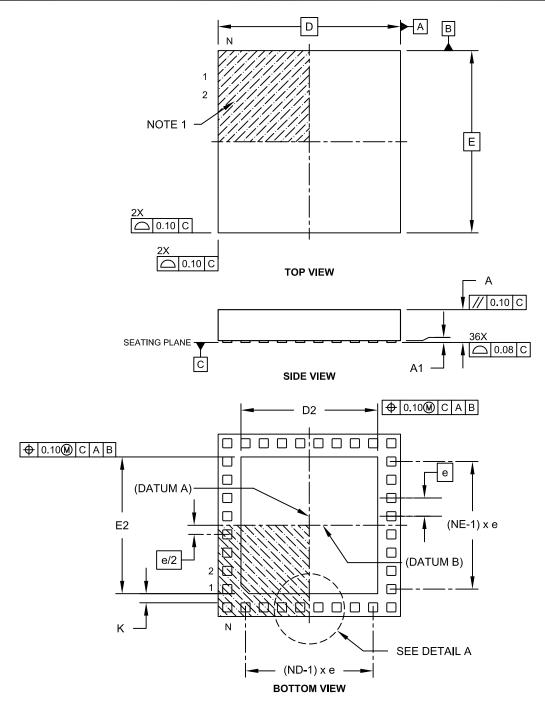

# 36-Terminal Very Thin Thermal Leadless Array Package (TL) – 5x5x0.9 mm Body with Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-187C Sheet 1 of 2

# **Revision C (December 2011)**

This revision includes typographical and formatting changes throughout the data sheet text.

In addition, where applicable, new sections were added to each peripheral chapter that provide information and links to related resources, as well as helpful tips. For examples, see Section 20.1 "UART Helpful Tips" and Section 3.6 "CPU Resources".

All occurrences of TLA were updated to VTLA throughout the document, with the exception of the pin diagrams (updated diagrams were not available at time of publication).

A new chapter, Section 31.0 "DC and AC Device Characteristics Graphs", was added.

All other major changes are referenced by their respective section in Table A-2.

TABLE A-2: MAJOR SECTION UPDATES

| Section Name                                                                                                                                                            | Update Description                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "16-bit Microcontrollers<br>and Digital Signal<br>Controllers (up to<br>256-Kbyte Flash and<br>32-Kbyte SRAM) with High-<br>Speed PWM, Op amps, and<br>Advanced Analog" | The content on the first page of this section was extensively reworked to provide the reader with the key features and functionality of this device family in an "at-a-glance" format.                                                                                |

| Section 1.0 "Device<br>Overview"                                                                                                                                        | Updated the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X, and PIC24EPXXXGP/MC20X Block Diagram (see Figure 1-1), which now contains a CPU block and a reference to the CPU diagram.  Updated the description and Note references in the Pinout I/O Descriptions for these |

|                                                                                                                                                                         | pins: C1IN2-, C2IN2-, C3IN2-, OA1OUT, OA2OUT, and OA3OUT (see Table 1-1).                                                                                                                                                                                             |

| Section 2.0 "Guidelines for<br>Getting Started with 16-bit<br>Digital Signal Controllers<br>and Microcontrollers"                                                       | Updated the Recommended Minimum Connection diagram (see Figure 2-1).                                                                                                                                                                                                  |

| Section 3.0 "CPU"                                                                                                                                                       | Updated the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X, and PIC24EPXXXGP/MC20X CPU Block Diagram (see Figure 3-1).                                                                                                                                                      |

|                                                                                                                                                                         | Updated the Status register definition in the Programmer's Model (see Figure 3-2).                                                                                                                                                                                    |

| Section 4.0 "Memory                                                                                                                                                     | Updated the Data Memory Maps (see Figure 4-6 and Figure 4-11).                                                                                                                                                                                                        |

| Organization"                                                                                                                                                           | Removed the DCB<1:0> bits from the OC1CON2, OC2CON2, OC3CON2, and OC4CON2 registers in the Output Compare 1 Through Output Compare 4 Register Map (see Table 4-10).                                                                                                   |

|                                                                                                                                                                         | Added the TRIG1 and TRGCON1 registers to the PWM Generator 1 Register Map (see Table 4-13).                                                                                                                                                                           |

|                                                                                                                                                                         | Added the TRIG2 and TRGCON2 registers to the PWM Generator 2 Register Map (see Table 4-14).                                                                                                                                                                           |

|                                                                                                                                                                         | Added the TRIG3 and TRGCON3 registers to the PWM Generator 3 Register Map (see Table 4-15).                                                                                                                                                                           |

|                                                                                                                                                                         | Updated the second note in <b>Section 4.7.1</b> "Bit-Reversed Addressing Implementation".                                                                                                                                                                             |

| Section 8.0 "Direct Memory<br>Access (DMA)"                                                                                                                             | Updated the DMA Controller diagram (see Figure 8-1).                                                                                                                                                                                                                  |

| Section 14.0 "Input<br>Capture"                                                                                                                                         | Updated the bit values for the ICx clock source of the ICTSEL<12:10> bits in the ICxCON1 register (see Register 14-1).                                                                                                                                                |

| Section 15.0 "Output<br>Compare"                                                                                                                                        | Updated the bit values for the OCx clock source of the OCTSEL<2:0> bits in the OCxCON1 register (see Register 15-1).                                                                                                                                                  |

|                                                                                                                                                                         | Removed the DCB<1:0> bits from the Output Compare x Control Register 2 (see Register 15-2).                                                                                                                                                                           |

TABLE A-5: MAJOR SECTION UPDATES (CONTINUED)

| Section Name                                           | Update Description                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 30.0 "Electrical                               | Throughout: qualifies all footnotes relating to the operation of analog modules below                                                                                                                                                                                                            |

| Characteristics"                                       | VDDMIN (replaces "will have" with "may have")                                                                                                                                                                                                                                                    |

|                                                        | Throughout: changes all references of SPI timing parameter symbol "TscP" to "FscP"                                                                                                                                                                                                               |

|                                                        | Table 30-1: changes VDD range to 3.0V to 3.6V                                                                                                                                                                                                                                                    |

|                                                        | Table 30-4: removes Parameter DC12 (RAM Retention Voltage)                                                                                                                                                                                                                                       |

|                                                        | Table 30-7: updates Maximum values at 10 and 20 MIPS                                                                                                                                                                                                                                             |

|                                                        | • Table 30-8: adds Maximum IPD values, and removes all ΔIWDT entries                                                                                                                                                                                                                             |

|                                                        | <ul> <li>Adds new Table 30-9 (Watchdog Timer Delta Current) with consolidated values<br/>removed from Table 30-8. All subsequent tables are renumbered accordingly.</li> </ul>                                                                                                                   |

|                                                        | <ul> <li>Table 30-10: adds footnote for all parameters for 1:2 Doze ratio</li> <li>Table 30-11:</li> </ul>                                                                                                                                                                                       |

|                                                        | - changes Minimum and Maximum values for D120 and D130                                                                                                                                                                                                                                           |

|                                                        | - adds Minimum and Maximum values for D131                                                                                                                                                                                                                                                       |

|                                                        | <ul> <li>adds Minimum and Maximum values for D150 through D156, and removes</li> <li>Typical values</li> </ul>                                                                                                                                                                                   |

|                                                        | • Table 30-12:                                                                                                                                                                                                                                                                                   |

|                                                        | - reformats table for readability                                                                                                                                                                                                                                                                |

|                                                        | - changes IoL conditions for DO10                                                                                                                                                                                                                                                                |

|                                                        | Table 30-14: adds footnote to D135                                                                                                                                                                                                                                                               |

|                                                        | Table 30-17: changes Minimum and Maximum values for OS30  Table 30-17: changes Minimum and Maximum values for OS30  Table 30-17: changes Minimum and Maximum values for OS30  Table 30-17: changes Minimum and Maximum values for OS30  Table 30-17: changes Minimum and Maximum values for OS30 |

|                                                        | • Table 30-19:                                                                                                                                                                                                                                                                                   |

|                                                        | - splits temperature range and adds new values for F20a                                                                                                                                                                                                                                          |

|                                                        | <ul> <li>reduces temperature range for F20b to extended temperatures only</li> <li>Table 30-20:</li> </ul>                                                                                                                                                                                       |

|                                                        | - splits temperature range and adds new values for F21a                                                                                                                                                                                                                                          |

|                                                        | - reduces temperature range for F20b to extended temperatures only                                                                                                                                                                                                                               |

|                                                        | • Table 30-53:                                                                                                                                                                                                                                                                                   |

|                                                        | - adds Maximum value to CM30                                                                                                                                                                                                                                                                     |

|                                                        | <ul> <li>adds footnote ("Parameter characterized") to multiple parameters</li> <li>Table 30-55: adds Minimum and Maximum values for all CTMUI specifications, and</li> </ul>                                                                                                                     |

|                                                        | removes Typical values                                                                                                                                                                                                                                                                           |

|                                                        | Table 30-57: adds new footnote to AD09                                                                                                                                                                                                                                                           |

|                                                        | • Table 30-58:                                                                                                                                                                                                                                                                                   |

|                                                        | <ul> <li>removes all specifications for accuracy with external voltage references</li> <li>removes Typical values for AD23a and AD24a</li> </ul>                                                                                                                                                 |

|                                                        | - replaces Minimum and Maximum values for AD21a, AD22a, AD23a and AD24a                                                                                                                                                                                                                          |

|                                                        | with new values, split by Industrial and Extended temperatures - removes Maximum value of AD30                                                                                                                                                                                                   |

|                                                        | - removes Minimum values from AD31a and AD32a                                                                                                                                                                                                                                                    |

|                                                        | - adds or changes Typical values for AD30, AD31a, AD32a and AD33a                                                                                                                                                                                                                                |

|                                                        | • Table 30-59:                                                                                                                                                                                                                                                                                   |

|                                                        | - removes all specifications for accuracy with external voltage references                                                                                                                                                                                                                       |

|                                                        | - removes Maximum value of AD30                                                                                                                                                                                                                                                                  |

|                                                        | - removes Typical values for AD23b and AD24b                                                                                                                                                                                                                                                     |

|                                                        | - replaces Minimum and Maximum values for AD21b, AD22b, AD23b and AD24b                                                                                                                                                                                                                          |

|                                                        | with new values, split by Industrial and Extended temperatures                                                                                                                                                                                                                                   |

|                                                        | - removes Minimum and Maximum values from AD31b, AD32b, AD33b and AD34b                                                                                                                                                                                                                          |

|                                                        | - adds or changes Typical values for AD30, AD31a, AD32a and AD33a                                                                                                                                                                                                                                |

|                                                        | Table 30-61: Adds footnote to AD51                                                                                                                                                                                                                                                               |

| Section 32.0 "DC and AC Device Characteristics Graphs" | <ul> <li>Updates Figure 32-6 (Typical IDD @ 3.3V) with individual current vs. processor speed<br/>curves for the different program memory sizes</li> </ul>                                                                                                                                       |

| Section 33.0 "Packaging Information"                   | <ul> <li>Replaces drawing C04-149C (64-pin QFN, 7.15 x 7.15 exposed pad) with C04-154A<br/>(64-pin QFN, 5.4 x 5.4 exposed pad)</li> </ul>                                                                                                                                                        |

| TyCON (Timer3 and Timer5 Control)      | 211     | Input Capture x (ICx)                         | 420 |

|----------------------------------------|---------|-----------------------------------------------|-----|

| UxMODE (UARTx Mode)                    |         | OCx/PWMx                                      |     |

| UxSTA (UARTx Status and Control)       |         | Output Compare x (OCx)                        |     |

| VEL1CNT (Velocity Counter 1)           |         | QEA/QEB Input                                 |     |

| Resets                                 |         | QEI Module Index Pulse                        |     |

| Brown-out Reset (BOR)                  | 123     | SPI1 Master Mode (Full-Duplex, CKE = 0,       |     |

| Configuration Mismatch Reset (CM)      | 123     | CKP = x, SMP = 1)                             | 441 |

| Illegal Condition Reset (IOPUWR)       |         | SPI1 Master Mode (Full-Duplex, CKE = 1,       |     |

| Illegal Opcode                         |         | CKP = x, SMP = 1)                             | 440 |

| Security                               |         | SPI1 Master Mode (Half-Duplex, Transmit Only, |     |

| Uninitialized W Register               |         | CKE = 0)                                      | 438 |

| Master Clear (MCLR) Pin Reset          |         | SPI1 Master Mode (Half-Duplex, Transmit Only, |     |

| Power-on Reset (POR)                   |         | CKE = 1)                                      | 439 |

| RESET Instruction (SWR)                |         | SPI1 Slave Mode (Full-Duplex, CKE = 0,        |     |

| Resources                              |         | CKP = 0, SMP = 0)                             | 448 |

| Trap Conflict Reset (TRAPR)            |         | SPI1 Slave Mode (Full-Duplex, CKE = 0,        |     |

| Watchdog Timer Time-out Reset (WDTO)   |         | CKP = 1, SMP = 0)                             | 446 |

| Resources Required for Digital PFC     |         | SPI1 Slave Mode (Full-Duplex, CKE = 1,        | ++0 |

| Revision History                       |         | CKP = 0, SMP = 0)                             | 112 |

| TCVISION FIRSTORY                      |         | SPI1 Slave Mode (Full-Duplex, CKE = 1,        | 772 |

| S                                      |         | CKP = 1, SMP = 0)                             | 111 |

| Serial Peripheral Interface (SPI)      | 265     | SPI2 Master Mode (Full-Duplex, CKE = 0,       | 444 |

| Software Stack Pointer (SSP)           |         | •                                             | 420 |

| Special Features of the CPU            |         | CKP = x, SMP = 1)                             | 429 |

| SPI                                    | 319     | SPI2 Master Mode (Full-Duplex, CKE = 1,       | 400 |

| Control Registers                      | 269     | CKP = x, SMP = 1)                             | 420 |

| Helpful Tips                           |         | SPI2 Master Mode (Half-Duplex, Transmit Only, | 400 |

| Resources                              |         | CKE = 0)                                      | 426 |

| Resources                              | 207     | SPI2 Master Mode (Half-Duplex, Transmit Only, | 407 |

| Т                                      |         | CKE = 1)                                      | 427 |

| Temperature and Voltage Specifications |         | SPI2 Slave Mode (Full-Duplex, CKE = 0,        | 400 |

| AC                                     | 112 171 | CKP = 0, SMP = 0)                             | 436 |

|                                        |         | SPI2 Slave Mode (Full-Duplex, CKE = 0,        |     |

| Thermal Declaring Conditions           |         | CKP = 1, SMP = 0)                             | 434 |

| Thermal Packaging Characteristics      |         | SPI2 Slave Mode (Full-Duplex, CKE = 1,        |     |

| Timer1                                 |         | CKP = 0, SMP = 0)                             | 430 |

| Control Register                       |         | SPI2 Slave Mode (Full-Duplex, CKE = 1,        |     |

| Resources                              |         | CKP = 1, SMP = 0)                             |     |

| Timer2/3 and Timer4/5                  |         | Timer1-Timer5 External Clock                  |     |

| Control Registers                      |         | TimerQ (QEI Module) External Clock            |     |

| Resources                              | 209     | UARTx I/O                                     | 454 |

| Timing Diagrams                        |         | U                                             |     |

| 10-Bit ADC Conversion (CHPS<1:0> = 01, |         |                                               |     |

| SIMSAM = 0, ASAM = 0, SSRC<2:0> =      |         | Universal Asynchronous Receiver               |     |

| SSRCG = 0)                             | 464     | Transmitter (UART)                            |     |

| 10-Bit ADC Conversion (CHPS<1:0> = 01, |         | Control Registers                             | 283 |

| SIMSAM = 0, $ASAM = 1$ , $SSRC<2:0> =$ | *       | Helpful Tips                                  | 282 |

| SSRCG = 0, SAMC<4:0> = 00010)          | 464     | Resources                                     | 282 |

| 12-Bit ADC Conversion (ASAM = 0,       |         | User ID Words                                 | 384 |

| SSRC<2:0> = 000, SSRCG = 0)            | 462     | V                                             |     |

| BOR and Master Clear Reset             | 416     | V                                             |     |

| ECANx I/O                              | 454     | Voltage Regulator (On-Chip)                   | 384 |

| External Clock                         | 414     | \W                                            |     |

| High-Speed PWMx Fault                  | 422     | W                                             |     |

| High-Speed PWMx Module                 |         | Watchdog Timer (WDT)379                       |     |

| I/O Characteristics                    |         | Programming Considerations                    |     |

| I2Cx Bus Data (Master Mode)            |         | WWW Address                                   |     |

| I2Cx Bus Data (Slave Mode)             |         | WWW, On-Line Support                          |     |

| I2Cx Bus Start/Stop Bits (Master Mode) |         | , , , , , , , , , , , , , , , , , , , ,       |     |

| I2Cx Bus Start/Stop Bits (Slave Mode)  |         |                                               |     |

| dsPIC33EPXXXGP50 | )X, dsPIC33EPXXXM( | C20X/50X AND PIC2 | 4EPXXXGP/MC20X |  |

|------------------|--------------------|-------------------|----------------|--|

| NOTES:           |                    |                   |                |  |

|                  |                    |                   |                |  |

|                  |                    |                   |                |  |

|                  |                    |                   |                |  |

|                  |                    |                   |                |  |

|                  |                    |                   |                |  |

|                  |                    |                   |                |  |

|                  |                    |                   |                |  |

|                  |                    |                   |                |  |

|                  |                    |                   |                |  |

|                  |                    |                   |                |  |

|                  |                    |                   |                |  |

|                  |                    |                   |                |  |