Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 28-SPDIP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256gp202-i-sp |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

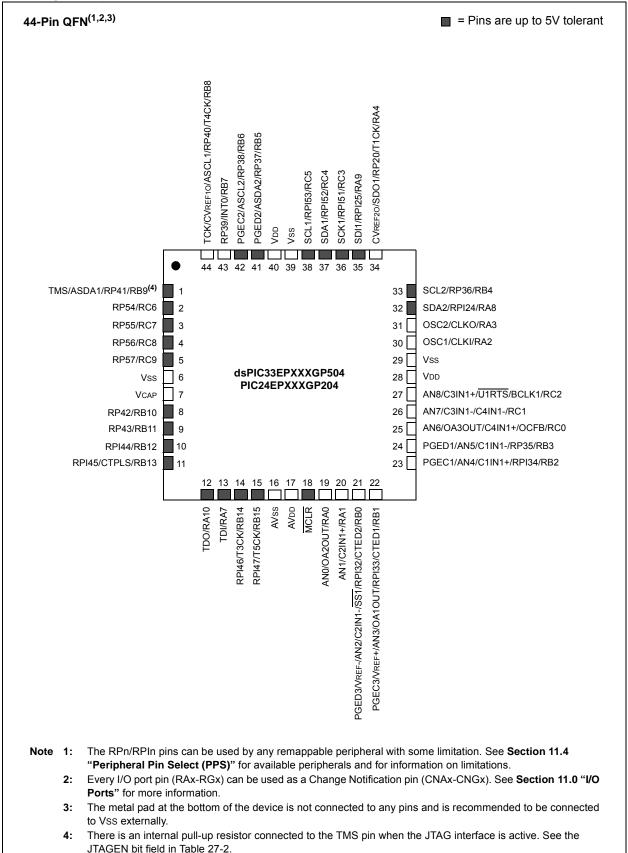

#### **Pin Diagrams (Continued)**

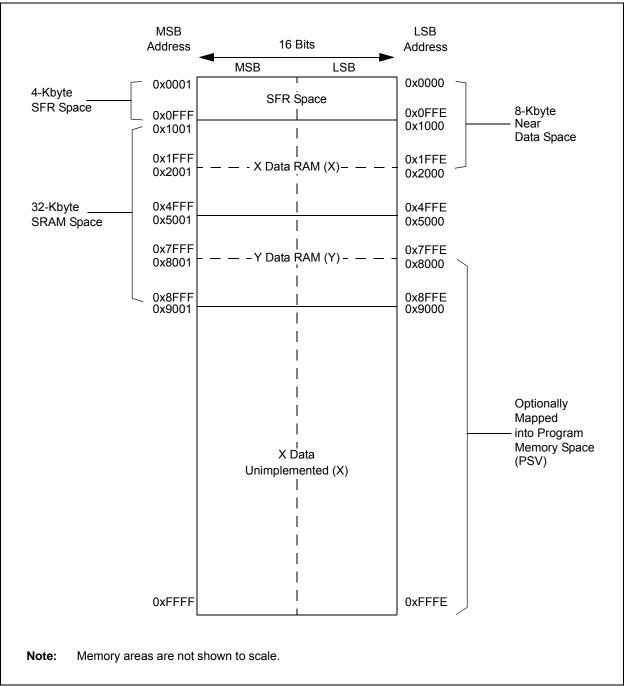

# FIGURE 4-10: DATA MEMORY MAP FOR dsPIC33EP256MC20X/50X AND dsPIC33EP256GP50X DEVICES

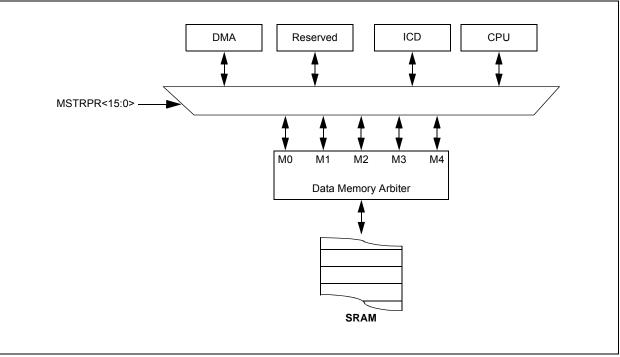

# 4.4.3 DATA MEMORY ARBITRATION AND BUS MASTER PRIORITY

EDS accesses from bus masters in the system are arbitrated.

The arbiter for data memory (including EDS) arbitrates between the CPU, the DMA and the ICD module. In the event of coincidental access to a bus by the bus masters, the arbiter determines which bus master access has the highest priority. The other bus masters are suspended and processed after the access of the bus by the bus master with the highest priority.

By default, the CPU is Bus Master 0 (M0) with the highest priority and the ICD is Bus Master 4 (M4) with the lowest priority. The remaining bus master (DMA Controller) is allocated to M3 (M1 and M2 are reserved and cannot be used). The user application may raise or lower the priority of the DMA Controller to be above that of the CPU by setting the appropriate bits in the EDS Bus Master Priority Control (MSTRPR) register. All bus masters with raised priorities will maintain the same priority relationship relative to each other (i.e., M1 being highest and M3 being lowest, with M2 in between). Also, all the bus masters with priorities below

### FIGURE 4-18: ARBITER ARCHITECTURE

that of the CPU maintain the same priority relationship relative to each other. The priority schemes for bus masters with different MSTRPR values are tabulated in Table 4-62.

This bus master priority control allows the user application to manipulate the real-time response of the system, either statically during initialization or dynamically in response to real-time events.

| TABLE 4-62: | DATA MEMORY BUS  |

|-------------|------------------|

|             | ARBITER PRIORITY |

| Drierity     | MSTRPR<15:0> Bit Setting <sup>(1)</sup> |          |  |  |

|--------------|-----------------------------------------|----------|--|--|

| Priority     | 0x0000                                  | 0x0020   |  |  |

| M0 (highest) | CPU                                     | DMA      |  |  |

| M1           | Reserved                                | CPU      |  |  |

| M2           | Reserved                                | Reserved |  |  |

| M3           | DMA                                     | Reserved |  |  |

| M4 (lowest)  | ICD                                     | ICD      |  |  |

**Note 1:** All other values of MSTRPR<15:0> are reserved.

## **10.0 POWER-SAVING FEATURES**

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of peripherals being clocked constitutes lower consumed power.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices can manage power consumption in four ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- Software-Controlled Doze mode

- · Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

| PWRSAV | #SLEEP_MODE | ; | Put | the | device | into | Sleep mode |  |

|--------|-------------|---|-----|-----|--------|------|------------|--|

| PWRSAV | #IDLE_MODE  | ; | Put | the | device | into | Idle mode  |  |

### 10.1 Clock Frequency and Clock Switching

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or highprecision oscillators by simply changing the NOSCx bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0 "Oscillator Configuration"**.

### 10.2 Instruction-Based Power-Saving Modes

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 10-1.

**Note:** SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

#### 10.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into Standby when Sleep mode is entered by clearing the VREGS (RCON<8>) and VREGSF (RCON<11>) bits (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) and VREGSF (RCON<11>) bits can be set to keep the internal regulator and the Flash regulator active during Sleep mode.

#### 10.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- · A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the Interrupt Service Routine (ISR).

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral; for example, the TSIDL bit in the Timer1 Control register (T1CON<13>).

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

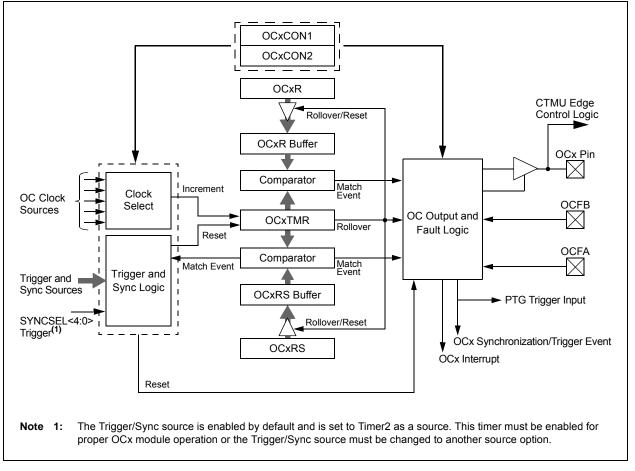

## 15.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Output Compare" (DS70358) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The output compare module can select one of seven available clock sources for its time base. The module compares the value of the timer with the value of one or two compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the compare register value. The output compare module generates either a single output pulse or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events and trigger DMA data transfers.

Note: See "Output Compare" (DS70358) in the "dsPIC33/PIC24 Family Reference Manual" for OCxR and OCxRS register restrictions.

| REGISTER 16-2: | PTCON2: PWMx PRIMARY MASTER CLOCK DIVIDER SELECT REGISTER 2 |

|----------------|-------------------------------------------------------------|

|----------------|-------------------------------------------------------------|

| U-0                               | U-0        | U-0              | U-0 | U-0                  | U-0                     | U-0                     | U-0         |

|-----------------------------------|------------|------------------|-----|----------------------|-------------------------|-------------------------|-------------|

| —                                 | —          | —                | _   | —                    | —                       | —                       | _           |

| bit 15                            |            |                  |     |                      |                         |                         | bit 8       |

|                                   |            |                  |     |                      |                         |                         |             |

| U-0                               | U-0        | U-0              | U-0 | U-0                  | R/W-0                   | R/W-0                   | R/W-0       |

| —                                 | —          | —                | -   | —                    | PCLKDIV2 <sup>(1)</sup> | PCLKDIV1 <sup>(1)</sup> | PCLKDIV0(1) |

| bit 7                             |            |                  |     |                      |                         |                         | bit 0       |

|                                   |            |                  |     |                      |                         |                         |             |

| Legend:                           |            |                  |     |                      |                         |                         |             |

| R = Readable bit W = Writable bit |            |                  | bit | U = Unimpler         | mented bit, read        | as '0'                  |             |

| -n = Value at POR '1              |            | '1' = Bit is set |     | '0' = Bit is cleared |                         | x = Bit is unknown      |             |

|                                   |            |                  |     |                      |                         |                         |             |

| bit 15-3                          | Unimplemen | ted: Read as '   | י'  |                      |                         |                         |             |

#### bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved 110 = Divide-by-64 101 = Divide-by-32

- 100 = Divide-by-32100 = Divide-by-16

- 011 = Divide-by-8

- 010 = Divide-by-4

- 001 = Divide-by-2

- 000 = Divide-by-1, maximum PWMx timing resolution (power-on default)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

NOTES:

## 19.0 INTER-INTEGRATED CIRCUIT<sup>™</sup> (I<sup>2</sup>C<sup>™</sup>)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70330) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

- 3: There are minimum bit rates of approximately FCY/512. As a result, high processor speeds may not support 100 Kbit/second operation. See timing specifications, IM10 and IM11, and the "Baud Rate Generator" in the "dsPIC33/PIC24 Family Reference Manual".

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices contains two Inter-Integrated Circuit (I<sup>2</sup>C) modules: I2C1 and I2C2.

The  $l^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $l^2C$  serial communication standard, with a 16-bit interface.

The  $I^2C$  module has a 2-pin interface:

- · The SCLx pin is clock

- The SDAx pin is data

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both Master and Slave modes of operation

- I<sup>2</sup>C Slave mode supports 7 and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7 and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation, detects bus collision and arbitrates accordingly

- Intelligent Platform Management Interface (IPMI)

support

- System Management Bus (SMBus) support

| R-0, HSC                                                    | R-0, HSC  | U-0                                                          | U-0        | U-0        | R/C-0, HS | R-0, HSC | R-0, HSC |

|-------------------------------------------------------------|-----------|--------------------------------------------------------------|------------|------------|-----------|----------|----------|

| ACKSTAT                                                     | TRSTAT    | _                                                            | _          | —          | BCL       | GCSTAT   | ADD10    |

| bit 15                                                      |           |                                                              |            |            |           |          | bit 8    |

|                                                             |           |                                                              |            |            |           |          |          |

| R/C-0, HS                                                   | R/C-0, HS | R-0, HSC                                                     | R/C-0, HSC | R/C-0, HSC | R-0, HSC  | R-0, HSC | R-0, HSC |

| IWCOL                                                       | I2COV     | D_A                                                          | Р          | S          | R_W       | RBF      | TBF      |

| bit 7                                                       |           |                                                              |            |            |           |          | bit 0    |

|                                                             |           |                                                              |            |            |           |          |          |

| Legend: C = Clearable bit                                   |           | HS = Hardware Settable bit HSC = Hardware Settable/Clearable |            |            |           |          |          |

| R = Readable bit W = Writable bit                           |           | U = Unimplemented bit, read as '0'                           |            |            |           |          |          |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = |           | x = Bit is unknown                                           |            |            |           |          |          |

### REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER

| bit 15       | <b>ACKSTAT:</b> Acknowledge Status bit (when operating as $I^2C^{TM}$ master, applicable to master transmit operation)                         |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10       | 1 = NACK received from slave                                                                                                                   |

|              | 0 = ACK received from slave                                                                                                                    |

|              | Hardware is set or clear at the end of slave Acknowledge.                                                                                      |

| bit 14       | TRSTAT: Transmit Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                               |

|              | 1 = Master transmit is in progress (8 bits + ACK)                                                                                              |

|              | 0 = Master transmit is not in progress                                                                                                         |

|              | Hardware is set at the beginning of master transmission. Hardware is clear at the end of slave Acknowledge.                                    |

| bit 13-11    | Unimplemented: Read as '0'                                                                                                                     |

| bit 10       | BCL: Master Bus Collision Detect bit                                                                                                           |

|              | 1 = A bus collision has been detected during a master operation                                                                                |

|              | 0 = No bus collision detected<br>Hardware is set at detection of a bus collision.                                                              |

| <b>h</b> # 0 |                                                                                                                                                |

| bit 9        | GCSTAT: General Call Status bit                                                                                                                |

|              | 1 = General call address was received<br>0 = General call address was not received                                                             |

|              | Hardware is set when address matches general call address. Hardware is clear at Stop detection.                                                |

| bit 8        | ADD10: 10-Bit Address Status bit                                                                                                               |

|              | 1 = 10-bit address was matched                                                                                                                 |

|              | 0 = 10-bit address was not matched                                                                                                             |

|              | Hardware is set at the match of the 2nd byte of the matched 10-bit address. Hardware is clear at Stop                                          |

|              | detection.                                                                                                                                     |

| bit 7        | IWCOL: I2Cx Write Collision Detect bit                                                                                                         |

|              | <ul> <li>1 = An attempt to write to the I2CxTRN register failed because the I<sup>2</sup>C module is busy</li> <li>0 = No collision</li> </ul> |

|              | Hardware is set at the occurrence of a write to I2CxTRN while busy (cleared by software).                                                      |

| bit 6        | <b>I2COV:</b> I2Cx Receive Overflow Flag bit                                                                                                   |

|              | 1 = A byte was received while the I2CxRCV register was still holding the previous byte                                                         |

|              | 0 = No overflow                                                                                                                                |

|              | Hardware is set at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                            |

| bit 5        | <b>D_A:</b> Data/Address bit (when operating as I <sup>2</sup> C slave)                                                                        |

|              | 1 = Indicates that the last byte received was data                                                                                             |

|              | 0 = Indicates that the last byte received was a device address                                                                                 |

|              | Hardware is clear at a device address match. Hardware is set by reception of a slave byte.                                                     |

| bit 4        | P: Stop bit                                                                                                                                    |

|              | 1 = Indicates that a Stop bit has been detected last                                                                                           |

|              | 0 = Stop bit was not detected last<br>Hardware is set or clear when a Start, Repeated Start or Stop is detected.                               |

|              |                                                                                                                                                |

|              |                                                                                                                                                |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                          | U-0               | U-0                                   | U-0            | U-0          | U-0              | U-0             | U-0   |  |

|------------------------------|-------------------|---------------------------------------|----------------|--------------|------------------|-----------------|-------|--|

| _                            | —                 | —                                     |                | —            | —                | —               | _     |  |

| bit 15                       |                   |                                       |                |              |                  |                 | bit   |  |

|                              |                   |                                       |                |              |                  |                 |       |  |

| R/W-0                        | R/W-0             | R/W-0                                 | U-0            | R/W-0        | R/W-0            | R/W-0           | R/W-0 |  |

| IVRIE                        | WAKIE             | ERRIE                                 | —              | FIFOIE       | RBOVIE           | RBIE            | TBIE  |  |

| bit 7                        |                   |                                       |                |              |                  |                 | bit   |  |

|                              |                   |                                       |                |              |                  |                 |       |  |

| <b>Legend:</b><br>R = Readab | la hit            | W = Writable b                        | .it            |              | montod bit rook  | l oo 'O'        |       |  |

| n = Value a                  |                   | '1' = Bit is set                      | אנ             | 0 = Onimpler | mented bit, read | x = Bit is unkr |       |  |

|                              | IL POR            | I = DILIS SEL                         |                |              | areu             |                 | IOWI  |  |

| bit 15-8                     | Unimplemen        | ted: Read as '0                       | ,              |              |                  |                 |       |  |

| bit 7                        | -                 | Message Inter                         |                | bit          |                  |                 |       |  |

|                              |                   | request is enabl                      | •              | ~            |                  |                 |       |  |

|                              |                   | request is not er                     |                |              |                  |                 |       |  |

| bit 6                        | WAKIE: Bus        | Wake-up Activit                       | y Interrupt E  | nable bit    |                  |                 |       |  |

|                              |                   | equest is enabl                       |                |              |                  |                 |       |  |

|                              |                   | request is not er                     |                |              |                  |                 |       |  |

| bit 5                        |                   | Interrupt Enabl                       |                |              |                  |                 |       |  |

|                              |                   | request is enabl<br>request is not er |                |              |                  |                 |       |  |

| bit 4                        |                   | ted: Read as '0                       |                |              |                  |                 |       |  |

| bit 3                        | -                 | Almost Full Int                       |                | o hit        |                  |                 |       |  |

| DIL J                        |                   | request is enabl                      | •              | ebit         |                  |                 |       |  |

|                              |                   | request is not er                     |                |              |                  |                 |       |  |

| bit 2                        | <b>RBOVIE:</b> RX | Buffer Overflow                       | / Interrupt Er | nable bit    |                  |                 |       |  |

|                              | 1 = Interrupt     | 1 = Interrupt request is enabled      |                |              |                  |                 |       |  |

|                              | 0 = Interrupt i   | request is not er                     | nabled         |              |                  |                 |       |  |

| bit 1                        |                   | ffer Interrupt En                     |                |              |                  |                 |       |  |

|                              |                   | equest is enabl                       |                |              |                  |                 |       |  |

|                              |                   | request is not er                     | nabled         |              |                  |                 |       |  |

|                              | •                 | •                                     |                |              |                  |                 |       |  |

| bit 0                        | TBIE: TX Buf      | fer Interrupt Ena<br>request is enabl | able bit       |              |                  |                 |       |  |

#### REGISTER 21-7: CXINTE: ECANX INTERRUPT ENABLE REGISTER

#### FIGURE 22-1: CTMU BLOCK DIAGRAM

5: The switch connected to ADC CH0 is closed when IDISSEN (CTMUCON1<9>) = 1, and opened when IDISSEN = 0.

### 22.1 CTMU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 22.1.1 KEY RESOURCES

- "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

#### 24.4 Step Commands and Format

#### TABLE 24-1: PTG STEP COMMAND FORMAT

| Step Command Byte: |             |             |  |  |

|--------------------|-------------|-------------|--|--|

|                    | STEPx<7:0>  |             |  |  |

| CMD<3:0>           |             | OPTION<3:0> |  |  |

| bit 7              | bit 4 bit 3 | bit 0       |  |  |

| bit 7-4 | CMD<3:0> | Step<br>Command | Command Description                                                                                                                                                                      |

|---------|----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 0000     | PTGCTRL         | Execute control command as described by OPTION<3:0>.                                                                                                                                     |

|         | 0001     | PTGADD          | Add contents of PTGADJ register to target register as described by<br>OPTION<3:0>.                                                                                                       |

|         |          | PTGCOPY         | Copy contents of PTGHOLD register to target register as described by<br>OPTION<3:0>.                                                                                                     |

|         | 001x     | PTGSTRB         | Copy the value contained in CMD<0>:OPTION<3:0> to the CH0SA<4:0> bits (AD1CHS0<4:0>).                                                                                                    |

|         | 0100     | PTGWHI          | Wait for a low-to-high edge input from the selected PTG trigger input as described by OPTION<3:0>.                                                                                       |

|         | 0101     | PTGWLO          | Wait for a high-to-low edge input from the selected PTG trigger input as described by OPTION<3:0>.                                                                                       |

|         | 0110     | Reserved        | Reserved.                                                                                                                                                                                |

|         | 0111     | PTGIRQ          | Generate individual interrupt request as described by OPTION3<:0>.                                                                                                                       |

|         | 100x     | PTGTRIG         | Generate individual trigger output as described by < <cmd<0>:OPTION&lt;3:0&gt;&gt;.</cmd<0>                                                                                              |

|         | 101x     | PTGJMP          | Copy the value indicated in < <cmd<0>:OPTION&lt;3:0&gt;&gt; to the Queue Pointer (PTGQPTR) and jump to that Step queue.</cmd<0>                                                          |

|         | 110x     | PTGJMPC0        | PTGC0 = PTGC0LIM: Increment the Queue Pointer (PTGQPTR).                                                                                                                                 |

|         |          |                 | $PTGC0 \neq PTGC0LIM$ : Increment Counter 0 (PTGC0) and copy the value indicated in < <cmd<0>:OPTION&lt;3:0&gt;&gt; to the Queue Pointer (PTGQPTR), and jump to that Step queue</cmd<0>  |

|         | 111x     | PTGJMPC1        | PTGC1 = PTGC1LIM: Increment the Queue Pointer (PTGQPTR).                                                                                                                                 |

|         |          |                 | $PTGC1 \neq PTGC1LIM$ : Increment Counter 1 (PTGC1) and copy the value indicated in < <cmd<0>:OPTION&lt;3:0&gt;&gt; to the Queue Pointer (PTGQPTR), and jump to that Step queue.</cmd<0> |

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

2: Refer to Table 24-2 for the trigger output descriptions.

3: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

#### 26.1 Overview

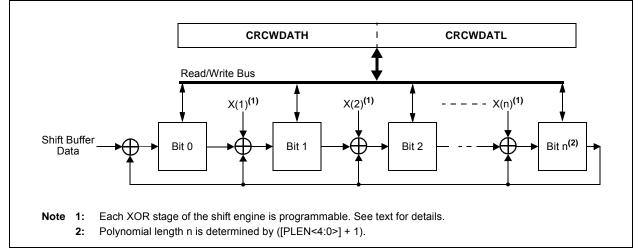

The CRC module can be programmed for CRC polynomials of up to the 32nd order, using up to 32 bits. Polynomial length, which reflects the highest exponent in the equation, is selected by the PLEN<4:0> bits (CRCCON2<4:0>).

The CRCXORL and CRCXORH registers control which exponent terms are included in the equation. Setting a particular bit includes that exponent term in the equation; functionally, this includes an XOR operation on the corresponding bit in the CRC engine. Clearing the bit disables the XOR.

For example, consider two CRC polynomials, one a 16-bit equation and the other a 32-bit equation:

$$\begin{array}{c} x16+x12+x5+1\\ \text{and}\\ x32+x26+x23+x22+x16+x12+x11+x10+x8+x7\\ +x5+x4+x2+x+1 \end{array}$$

To program these polynomials into the CRC generator, set the register bits as shown in Table 26-1.

Note that the appropriate positions are set to '1' to indicate that they are used in the equation (for example, X26 and X23). The 0 bit required by the equation is always XORed; thus, X0 is a don't care. For a polynomial of length N, it is assumed that the *N*th bit will always be used, regardless of the bit setting. Therefore, for a polynomial length of 32, there is no 32nd bit in the CRCxOR register.

# TABLE 26-1:CRC SETUP EXAMPLES FOR16 AND 32-BIT POLYNOMIAL

| CRC Control | Bit Values             |                        |  |  |

|-------------|------------------------|------------------------|--|--|

| Bits        | 16-bit<br>Polynomial   | 32-bit<br>Polynomial   |  |  |

| PLEN<4:0>   | 01111                  | 11111                  |  |  |

| X<31:16>    | 0000 0000<br>0000 000x | 0000 0100<br>1100 0001 |  |  |

| X<15:0>     | 0001 0000<br>0010 000x | 0001 1101<br>1011 011x |  |  |

### 26.2 Programmable CRC Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 26.2.1 KEY RESOURCES

- "Programmable Cyclic Redundancy Check (CRC)" (DS70346) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax                                  | Description                                 | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|--------|--------------------------------------------------|---------------------------------------------|---------------|-------------------------------|--------------------------|

| 25                 | DAW                  | DAW    | Wn                                               | Wn = decimal adjust Wn                      |               | 1                             | С                        |

| 26                 | DEC                  | DEC    | f                                                | f = f - 1                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | DEC    | f,WREG                                           | WREG = f – 1                                | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | DEC    | Ws,Wd                                            | Wd = Ws - 1                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 27                 | DEC2                 | DEC2   | f                                                | f = f - 2                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | DEC2   | f,WREG                                           | WREG = f – 2                                | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | DEC2   | Ws,Wd                                            | Wd = Ws - 2                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 28                 | DISI                 | DISI   | #lit14                                           | Disable Interrupts for k instruction cycles | 1             | 1                             | None                     |

| 29                 | DIV                  | DIV.S  | Wm,Wn                                            | Signed 16/16-bit Integer Divide             | 1             | 18                            | N,Z,C,OV                 |

|                    |                      | DIV.SD | Wm,Wn                                            | Signed 32/16-bit Integer Divide             | 1             | 18                            | N,Z,C,OV                 |

|                    |                      | DIV.U  | Wm,Wn                                            | Unsigned 16/16-bit Integer Divide           | 1             | 18                            | N,Z,C,OV                 |

|                    |                      | DIV.UD | Wm,Wn                                            | Unsigned 32/16-bit Integer Divide           | 1             | 18                            | N,Z,C,OV                 |

| 30                 | DIVF                 | DIVF   | Wm , Wn <sup>(1)</sup>                           | Signed 16/16-bit Fractional Divide          | 1             | 18                            | N,Z,C,OV                 |

| 31                 | DO                   | DO     | #lit15,Expr <sup>(1)</sup>                       | Do code to PC + Expr, lit15 + 1 times       | 2             | 2                             | None                     |

|                    |                      | DO     | Wn, Expr(1)                                      | Do code to PC + Expr, (Wn) + 1 times        | 2             | 2                             | None                     |

| 32                 | ED                   | ED     | Wm*Wm,Acc,Wx,Wy,Wxd <sup>(1)</sup>               | Euclidean Distance (no accumulate)          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 33                 | EDAC                 | EDAC   | Wm*Wm,Acc,Wx,Wy,Wxd <sup>(1)</sup>               | Euclidean Distance                          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 34                 | EXCH                 | EXCH   | Wns,Wnd                                          | Swap Wns with Wnd                           | 1             | 1                             | None                     |

| 35                 | FBCL                 | FBCL   | Ws,Wnd                                           | Find Bit Change from Left (MSb) Side        | 1             | 1                             | С                        |

| 36                 | FF1L                 | FF1L   | Ws,Wnd                                           | Find First One from Left (MSb) Side         | 1             | 1                             | С                        |

| 37                 | FF1R                 | FF1R   | Ws,Wnd                                           | Find First One from Right (LSb) Side        | 1             | 1                             | С                        |

| 38                 | GOTO                 | GOTO   | Expr                                             | Go to address                               | 2             | 4                             | None                     |

|                    |                      | GOTO   | Wn                                               | Go to indirect                              | 1             | 4                             | None                     |

|                    |                      | GOTO.L | Wn                                               | Go to indirect (long address)               | 1             | 4                             | None                     |

| 39                 | INC                  | INC    | f                                                | f = f + 1                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | INC    | f,WREG                                           | WREG = f + 1                                | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | INC    | Ws,Wd                                            | Wd = Ws + 1                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 40                 | INC2                 | INC2   | f                                                | f = f + 2                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | INC2   | f,WREG                                           | WREG = f + 2                                | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | INC2   | Ws,Wd                                            | Wd = Ws + 2                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 41                 | IOR                  | IOR    | f                                                | f = f .IOR. WREG                            | 1             | 1                             | N,Z                      |

|                    |                      | IOR    | f,WREG                                           | WREG = f .IOR. WREG                         | 1             | 1                             | N,Z                      |

|                    |                      | IOR    | #lit10,Wn                                        | Wd = lit10 .IOR. Wd                         | 1             | 1                             | N,Z                      |

|                    |                      | IOR    | Wb,Ws,Wd                                         | Wd = Wb .IOR. Ws                            | 1             | 1                             | N,Z                      |

|                    |                      | IOR    | Wb,#lit5,Wd                                      | Wd = Wb .IOR. lit5                          | 1             | 1                             | N,Z                      |

| 42                 | LAC                  | LAC    | Wso,#Slit4,Acc                                   | Load Accumulator                            | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 43                 | LNK                  | LNK    | #lit14                                           | Link Frame Pointer                          | 1             | 1                             | SFA                      |

| 44                 | LSR                  | LSR    | f                                                | f = Logical Right Shift f                   | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | LSR    | f,WREG                                           | WREG = Logical Right Shift f                | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | LSR    | Ws,Wd                                            | Wd = Logical Right Shift Ws                 | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | LSR    | Wb,Wns,Wnd                                       | Wnd = Logical Right Shift Wb by Wns         | 1             | 1                             | N,Z                      |

|                    |                      | LSR    | Wb,#lit5,Wnd                                     | Wnd = Logical Right Shift Wb by lit5        | 1             | 1                             | N,Z                      |

| 45                 | MAC                  | MAC    | Wm*Wn, Acc, Wx, Wxd, Wy, Wyd, AWB <sup>(1)</sup> | Multiply and Accumulate                     | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MAC    | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd(1)                       | Square and Accumulate                       | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax    | Description                        | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|--------|--------------------|------------------------------------|---------------|-------------------------------|--------------------------|

| 72                 | SL                   | SL     | f                  | f = Left Shift f                   | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | SL     | f,WREG             | WREG = Left Shift f                | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | SL     | Ws,Wd              | Wd = Left Shift Ws                 | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | SL     | Wb,Wns,Wnd         | Wnd = Left Shift Wb by Wns         | 1             | 1                             | N,Z                      |

|                    |                      | SL     | Wb,#lit5,Wnd       | Wnd = Left Shift Wb by lit5        | 1             | 1                             | N,Z                      |

| 73                 | SUB                  | SUB    | <sub>ACC</sub> (1) | Subtract Accumulators              | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | SUB    | £                  | f = f – WREG                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUB    | f,WREG             | WREG = f – WREG                    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUB    | #lit10,Wn          | Wn = Wn - lit10                    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUB    | Wb,Ws,Wd           | Wd = Wb – Ws                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUB    | Wb,#lit5,Wd        | Wd = Wb - lit5                     | 1             | 1                             | C,DC,N,OV,Z              |

| 74                 | SUBB                 | SUBB   | f                  | $f = f - WREG - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBB   | f,WREG             | WREG = $f - WREG - (\overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBB   | #lit10,Wn          | $Wn = Wn - lit10 - (\overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBB   | Wb,Ws,Wd           | $Wd = Wb - Ws - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBB   | Wb,#lit5,Wd        | $Wd = Wb - lit5 - (\overline{C})$  | 1             | 1                             | C,DC,N,OV,Z              |

| 75                 | SUBR                 | SUBR   | f                  | f = WREG – f                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBR   | f,WREG             | WREG = WREG – f                    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBR   | Wb,Ws,Wd           | Wd = Ws – Wb                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBR   | Wb,#lit5,Wd        | Wd = lit5 – Wb                     | 1             | 1                             | C,DC,N,OV,Z              |

| 76                 | SUBBR                | SUBBR  | f                  | $f = WREG - f - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBBR  | f,WREG             | WREG = WREG – f – $(\overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBBR  | Wb,Ws,Wd           | $Wd = Ws - Wb - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBBR  | Wb,#lit5,Wd        | $Wd = lit5 - Wb - (\overline{C})$  | 1             | 1                             | C,DC,N,OV,Z              |

| 77                 | SWAP                 | SWAP.b | Wn                 | Wn = nibble swap Wn                | 1             | 1                             | None                     |

|                    |                      | SWAP   | Wn                 | Wn = byte swap Wn                  | 1             | 1                             | None                     |

| 78                 | TBLRDH               | TBLRDH | Ws,Wd              | Read Prog<23:16> to Wd<7:0>        | 1             | 5                             | None                     |

| 79                 | TBLRDL               | TBLRDL | Ws,Wd              | Read Prog<15:0> to Wd              | 1             | 5                             | None                     |

| 80                 | TBLWTH               | TBLWTH | Ws,Wd              | Write Ws<7:0> to Prog<23:16>       | 1             | 2                             | None                     |

| 81                 | TBLWTL               | TBLWTL | Ws,Wd              | Write Ws to Prog<15:0>             | 1             | 2                             | None                     |

| 82                 | ULNK                 | ULNK   |                    | Unlink Frame Pointer               | 1             | 1                             | SFA                      |

| 83                 | XOR                  | XOR    | f                  | f = f .XOR. WREG                   | 1             | 1                             | N,Z                      |

|                    |                      | XOR    | f,WREG             | WREG = f .XOR. WREG                | 1             | 1                             | N,Z                      |

|                    |                      | XOR    | #lit10,Wn          | Wd = lit10 .XOR. Wd                | 1             | 1                             | N,Z                      |

|                    |                      | XOR    | Wb,Ws,Wd           | Wd = Wb .XOR. Ws                   | 1             | 1                             | N,Z                      |

|                    |                      | XOR    | Wb,#lit5,Wd        | Wd = Wb .XOR. lit5                 | 1             | 1                             | N,Z                      |

| 84                 | ZE                   | ZE     | Ws,Wnd             | Wnd = Zero-extend Ws               | 1             | 1                             | C,Z,N                    |

### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

## 31.0 HIGH-TEMPERATURE ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X electrical characteristics for devices operating in an ambient temperature range of -40°C to +150°C.

The specifications between  $-40^{\circ}$ C to  $+150^{\circ}$ C are identical to those shown in **Section 30.0** "**Electrical Characteristics**" for operation between  $-40^{\circ}$ C to  $+125^{\circ}$ C, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, Parameter DC10 in **Section 30.0 "Electrical Characteristics"** is the Industrial and Extended temperature equivalent of HDC10.

Absolute maximum ratings for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X high-temperature devices are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias <sup>(2)</sup>                                     | 40°C to +150°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +160°C       |

| Voltage on VDD with respect to Vss                                                | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(3)</sup>     | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(3)</sup> | 0.3V to 3.6V         |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(3)}$      | 0.3V to 5.5V         |

| Maximum current out of Vss pin                                                    | 60 mA                |

| Maximum current into Vod pin <sup>(4)</sup>                                       | 60 mA                |

| Maximum junction temperature                                                      | +155°C               |

| Maximum current sourced/sunk by any 4x I/O pin                                    | 10 mA                |

| Maximum current sourced/sunk by any 8x I/O pin                                    | 15 mA                |

| Maximum current sunk by all ports combined                                        | 70 mA                |

| Maximum current sourced by all ports combined <sup>(4)</sup>                      | 70 mA                |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

- 2: AEC-Q100 reliability testing for devices intended to operate at +150°C is 1,000 hours. Any design in which the total operating time from +125°C to +150°C will be greater than 1,000 hours is not warranted without prior written approval from Microchip Technology Inc.

- 3: Refer to the "Pin Diagrams" section for 5V tolerant pins.

- 4: Maximum allowable current is a function of device maximum power dissipation (see Table 31-2).

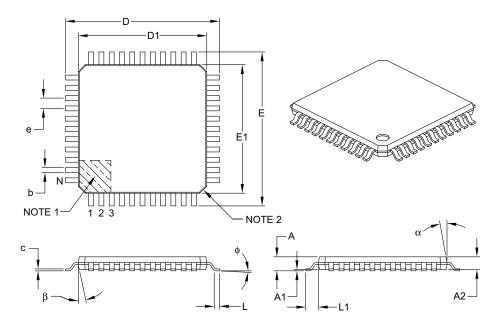

#### 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units       |           | MILLIMETERS | 6    |

|--------------------------|-------------|-----------|-------------|------|

| Dimens                   | sion Limits | MIN       | NOM         | MAX  |

| Number of Leads          | Ν           |           | 44          |      |

| Lead Pitch               | е           |           | 0.80 BSC    |      |

| Overall Height           | А           | -         | -           | 1.20 |

| Molded Package Thickness | A2          | 0.95      | 1.00        | 1.05 |

| Standoff                 | A1          | 0.05      | -           | 0.15 |

| Foot Length              | L           | 0.45      | 0.60        | 0.75 |

| Footprint                | L1          | 1.00 REF  |             |      |

| Foot Angle               | φ           | 0°        | 3.5°        | 7°   |

| Overall Width            | E           | 12.00 BSC |             |      |

| Overall Length           | D           | 12.00 BSC |             |      |

| Molded Package Width     | E1          | 10.00 BSC |             |      |

| Molded Package Length    | D1          | 10.00 BSC |             |      |

| Lead Thickness           | с           | 0.09      | -           | 0.20 |

| Lead Width               | b           | 0.30      | 0.37        | 0.45 |

| Mold Draft Angle Top     | α           | 11°       | 12°         | 13°  |

| Mold Draft Angle Bottom  | β           | 11°       | 12°         | 13°  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units  | N         | <b>ILLIMETER</b> | S    |  |

|------------------------|--------|-----------|------------------|------|--|

| Dimension              | Limits | MIN       | NOM              | MAX  |  |

| Number of Pins         | N      |           | 48               |      |  |

| Pitch                  | е      |           | 0.40 BSC         |      |  |

| Overall Height         | Α      | 0.45      | 0.50             | 0.55 |  |

| Standoff               | A1     | 0.00      | 0.02             | 0.05 |  |

| Contact Thickness      | A3     | 0.127 REF |                  |      |  |

| Overall Width          | E      | 6.00 BSC  |                  |      |  |

| Exposed Pad Width      | E2     | 4.45      | 4.60             | 4.75 |  |

| Overall Length         | D      |           | 6.00 BSC         |      |  |

| Exposed Pad Length     | D2     | 4.45      | 4.60             | 4.75 |  |

| Contact Width          | b      | 0.15      | 0.20             | 0.25 |  |

| Contact Length         | L      | 0.30      | 0.40             | 0.50 |  |

| Contact-to-Exposed Pad | K      | 0.20      | -                | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-153A Sheet 2 of 2

#### Ρ

| Packaging                                  |     |

|--------------------------------------------|-----|

| Details                                    |     |

| Marking                                    |     |

| Peripheral Module Disable (PMD)            |     |

| Peripheral Pin Select (PPS)                |     |

| Available Peripherals                      | 175 |

| Available Pins                             | 175 |

| Control                                    |     |

| Control Registers                          |     |

| Input Mapping                              |     |

| Output Selection for Remappable Pins       |     |

| Pin Selection for Selectable Input Sources |     |

| Selectable Input Sources                   |     |

| Peripheral Trigger Generator (PTG) Module  |     |

| PICkit 3 In-Circuit Debugger/Programmer    |     |

| Pinout I/O Descriptions (table)            |     |

| Power-Saving Features                      |     |

| Clock Frequency                            |     |

| Clock Switching                            |     |

| Instruction-Based Modes                    |     |

| Idle                                       |     |

| Interrupts Coincident with Power           |     |

| Save Instructions                          |     |

| Sleep                                      |     |

| Resources                                  |     |

| Program Address Space                      | 45  |

| Construction                               | 117 |

| Data Access from Program Memory Using      |     |

| Table Instructions                         | 118 |

| Memory Map (dsPIC33EP128GP50X,             |     |

| dsPIC33EP128MC20X/50X,                     |     |

| PIC24EP128GP/MC20X Devices)                | 47  |

| Memory Map (dsPIC33EP256GP50X,             |     |

| dsPIC33EP256MC20X/50X,                     |     |

| PIC24EP256GP/MC20X Devices)                | 48  |

| Memory Map (dsPIC33EP32GP50X,              |     |

| dsPIC33EP32MC20X/50X,                      |     |

| PIC24EP32GP/MC20X Devices)                 | 45  |

| Memory Map (dsPIC33EP512GP50X,             |     |

| dsPIC33EP512MC20X/50X,                     |     |

| PIC24EP512GP/MC20X Devices)                |     |

| Memory Map (dsPIC33EP64GP50X,              |     |

| dsPIC33EP64MC20X/50X,                      |     |

| PIC24EP64GP/MC20X Devices)                 |     |

| Table Read High Instructions               |     |

| TBLRDH                                     |     |

| Table Read Low Instructions (TBLRDL)       |     |

| Program Memory                             |     |

| Organization                               |     |

| Reset Vector                               | 50  |

| Programmable CRC Generator                 |     |

| Control Registers                          |     |

| Overview                                   |     |

| Resources                                  |     |

| Programmer's Model                         |     |

| Register Descriptions                      |     |

| PTG                                        |     |

| Control Registers                          |     |

| Introduction                               |     |

| Output Descriptions                        |     |

| Resources                                  |     |

| Step Commands and Format                   |     |

|                                            |     |

#### **Q** OFI

| QLI  |                                 |     |

|------|---------------------------------|-----|

|      | Control Registers               | 252 |

|      | Resources                       | 251 |

| Quad | Irature Encoder Interface (QEI) | 249 |

# R

| Register Maps                                     |     |

|---------------------------------------------------|-----|

| ADC1                                              | 84  |

| CPU Core (dsPIC33EPXXXMC20X/50X,                  |     |

| dsPIC33EPXXXGP50X Devices)                        | 63  |

| CPU Core (PIC24EPXXXGP/MC20X Devices)             |     |

| CRC                                               |     |

| CTMU                                              |     |

| DMAC                                              |     |

| ECAN1 (When WIN (C1CTRL1) = 0 or 1)               |     |

| for dsPIC33EPXXXMC/GP50X Devices                  | 85  |

| ECAN1 (When WIN (C1CTRL1) = 0) for                |     |

| dsPIC33EPXXXMC/GP50X Devices                      | 85  |

| ECAN1 (WIN (C1CTRL1) = 1) for                     |     |

| dsPIC33EPXXXMC/GP50X Devices                      | 86  |

| I2C1 and I2C2                                     |     |

| Input Capture 1 through Input Capture 4           |     |

| Interrupt Controller                              | 70  |

| (dsPIC33EPXXXGP50X Devices)                       | 69  |

| Interrupt Controller                              | 00  |

| (dsPIC33EPXXXMC20X Devices)                       | 71  |

| Interrupt Controller                              | / 1 |

| (dsPIC33EPXXXMC50X Devices)                       | 73  |

|                                                   | 75  |

| Interrupt Controller<br>(PIC24EPXXXGP20X Devices) | 66  |

| Interrupt Controller                              | 00  |

| (PIC24EPXXXMC20X Devices)                         | 67  |

| JTAG Interface                                    |     |

| NVM                                               |     |

|                                                   |     |

| Op Amp/Comparator                                 |     |

| Output Compare 1 through Output Compare 4         | //  |

| Peripheral Pin Select Input                       | 04  |

| (dsPIC33EPXXXGP50X Devices)                       | 91  |

| Peripheral Pin Select Input                       | 00  |

| (dsPIC33EPXXXMC20X Devices)                       | 92  |

| Peripheral Pin Select Input                       | 01  |

| (dsPIC33EPXXXMC50X Devices)                       | 91  |

| Peripheral Pin Select Input                       | ~~~ |

| (PIC24EPXXXGP20X Devices)                         | 90  |

| Peripheral Pin Select Input                       | ~~  |

| (PIC24EPXXXMC20X Devices)                         | 90  |

| Peripheral Pin Select Output                      |     |

| (dsPIC33EPXXXGP/MC202/502,                        | 00  |

| PIC24EPXXXGP/MC202 Devices)                       | 88  |

| Peripheral Pin Select Output                      |     |

| (dsPIC33EPXXXGP/MC203/503,                        | ~~  |

| PIC24EPXXXGP/MC203 Devices)                       | 88  |

| Peripheral Pin Select Output                      |     |

| (dsPIC33EPXXXGP/MC204/504,                        | ~~~ |

| PIC24EPXXXGP/MC204 Devices)                       | 89  |

| Peripheral Pin Select Output                      |     |

| (dsPIC33EPXXXGP/MC206/506,                        | ~~  |

| PIC24EPXXGP/MC206 Devices)                        |     |

| PMD (dsPIC33EPXXXGP50X Devices)                   |     |

| PMD (dsPIC33EPXXXMC20X Devices)                   |     |

| PMD (dsPIC33EPXXXMC50X Devices)                   |     |

| PMD (PIC24EPXXXGP20X Devices)                     | 94  |