#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 256КВ (85.5К х 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 16K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256gp202t-i-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 2: dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X MOTOR CONTROL FAMILIES

| F <i>P</i>        | MIL                            | ES                            |              |                      |               |                |                                                |                              |        |                    |                  |                                    | _    | _                    | _                            | _                   |      |     | _        | _         |                                |

|-------------------|--------------------------------|-------------------------------|--------------|----------------------|---------------|----------------|------------------------------------------------|------------------------------|--------|--------------------|------------------|------------------------------------|------|----------------------|------------------------------|---------------------|------|-----|----------|-----------|--------------------------------|

|                   | ()                             | es)                           |              |                      |               | Rei            | mappa                                          | ble P                        | eriphe | erals              |                  |                                    |      |                      | -                            |                     |      |     |          |           |                                |

| Device            | Page Erase Size (Instructions) | Program Flash Memory (Kbytes) | RAM (Kbytes) | 16-Bit/32-Bit Timers | Input Capture | Output Compare | Motor Control PWM <sup>(4)</sup><br>(Channels) | Quadrature Encoder Interface | UART   | SPI <sup>(2)</sup> | ECAN™ Technology | External Interrupts <sup>(3)</sup> | I²C™ | <b>CRC Generator</b> | 10-Bit/12-Bit ADC (Channels) | Op Amps/Comparators | CTMU | PTG | I/O Pins | Pins      | Packages                       |

| PIC24EP32MC202    | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| PIC24EP64MC202    | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | SPDIP,                         |

| PIC24EP128MC202   | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 6                            | 2/3(1)              | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(5)</sup> , |

| PIC24EP256MC202   | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | QFN-S                          |

| PIC24EP512MC202   | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| PIC24EP32MC203    | 512                            | 32                            | 4            | -                    |               |                | <u> </u>                                       | ,                            | 6      | 6                  |                  | <u> </u>                           | 6    |                      | _                            |                     | v    | ~   | 0-       |           | ) (T) A                        |

| PIC24EP64MC203    | 1024                           | 64                            | 8            | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 8                            | 3/4                 | Yes  | Yes | 25       | 36        | VTLA                           |

| PIC24EP32MC204    | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      | 1   |          |           |                                |

| PIC24EP64MC204    | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | VTLA <sup>(5)</sup> ,          |

| PIC24EP128MC204   | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,                  |

| PIC24EP256MC204   | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          | 40        | UQFN                           |

| PIC24EP512MC204   | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| PIC24EP64MC206    | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| PIC24EP128MC206   | 1024                           | 128                           | 16           | F                    | 4             | 4              | 6                                              | 4                            | 2      | 2                  |                  | 2                                  | 2    | 1                    | 10                           | 2/4                 | Vaa  | Vaa | 50       | 64        | TQFP,                          |

| PIC24EP256MC206   | 1024                           | 256                           | 32           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 16                           | 3/4                 | Yes  | Yes | 53       | 64        | QFN                            |

| PIC24EP512MC206   | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC202  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC202  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | SPDIP,                         |

| dsPIC33EP128MC202 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 6                            | 2/3 <b>(1)</b>      | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(5)</sup> , |

| dsPIC33EP256MC202 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | QFN-S                          |

| dsPIC33EP512MC202 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC203  | 512                            | 32                            | 4            | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  |                  | 3                                  | 2    | 1                    | 8                            | 3/4                 | Yes  | Yes | 25       | 36        | VTLA                           |

| dsPIC33EP64MC203  | 1024                           | 64                            | 8            | э                    | 4             | 4              | 0                                              | -                            | 2      | 2                  |                  | ა                                  | 2    | I                    | 0                            | 3/4                 | res  | tes | 25       | 30        | VILA                           |

| dsPIC33EP32MC204  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC204  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | VTLA <sup>(5)</sup> ,          |

| dsPIC33EP128MC204 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | —                | 3                                  | 2    | 1                    | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,                  |

| dsPIC33EP256MC204 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | UQFN                           |

| dsPIC33EP512MC204 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC206  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP128MC206 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 16                           | 3/4                 | Yes  | Yes | 53       | 64        | TQFP,                          |

| dsPIC33EP256MC206 | 1024                           | 256                           | 32           | 5                    | +             | 1              | 0                                              | 1                            | 2      | 2                  |                  | 5                                  | 2    | · ·                  | 10                           | 5/4                 | 165  | 163 | 55       | 04        | QFN                            |

| dsPIC33EP512MC206 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC502  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC502  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | SPDIP,<br>SOIC,                |

| dsPIC33EP128MC502 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2    | 1                    | 6                            | 2/3(1)              | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(5)</sup> , |

| dsPIC33EP256MC502 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | QFN-S                          |

| dsPIC33EP512MC502 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC503  | 512                            | 32                            | 4            | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2    | 1                    | 8                            | 3/4                 | Yes  | Yes | 25       | 36        | VTLA                           |

| dsPIC33EP64MC503  | 1024                           | 64                            | 8            | ~                    |               |                |                                                |                              | _      | _                  |                  |                                    | _    |                      | Ĵ                            | <i></i>             |      |     |          |           |                                |

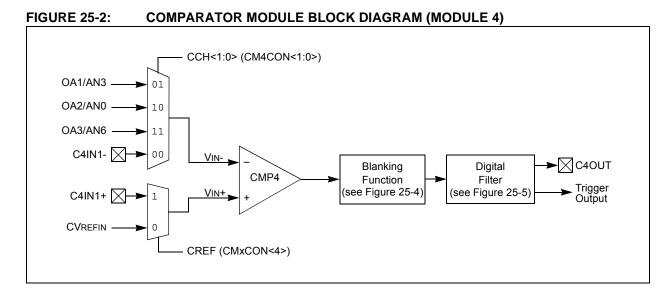

Note 1: On 28-pin devices, Comparator 4 does not have external connections. Refer to Section 25.0 "Op Amp/Comparator Module" for details. 2: Only SPI2 is remappable.

**3:** INTO is not remappable.

4: Only the PWM Faults are remappable.

5: The SSOP and VTLA packages are not available for devices with 512 Kbytes of memory.

#### **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33EP64MC506 product page of the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

> In addition to parameters, features and other documentation, the resulting page provides links to the related family reference manual sections.

- "Introduction" (DS70573)

- "CPU" (DS70359)

- "Data Memory" (DS70595)

- "Program Memory" (DS70613)

- "Flash Programming" (DS70609)

- "Interrupts" (DS70600)

- "Oscillator" (DS70580)

- "Reset" (DS70602)

- "Watchdog Timer and Power-Saving Modes" (DS70615)

- "I/O Ports" (DS70598)

- "Timers" (DS70362)

- "Input Capture" (DS70352)

- "Output Compare" (DS70358)

- "High-Speed PWM" (DS70645)

- "Quadrature Encoder Interface (QEI)" (DS70601)

- "Analog-to-Digital Converter (ADC)" (DS70621)

- "UART" (DS70582)

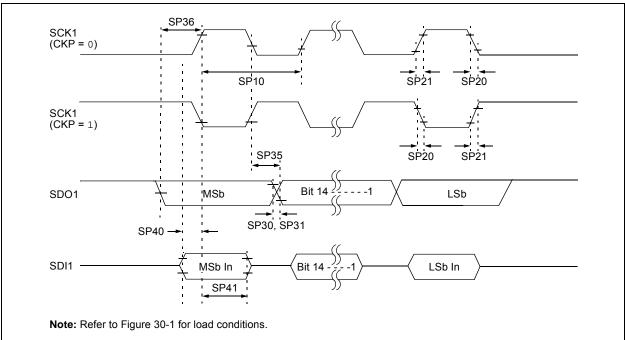

- "Serial Peripheral Interface (SPI)" (DS70569)

- "Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)" (DS70330)

- "Enhanced Controller Area Network (ECAN™)" (DS70353)

- "Direct Memory Access (DMA)" (DS70348)

- "CodeGuard™ Security" (DS70634)

- "Programming and Diagnostics" (DS70608)

- "Op Amp/Comparator" (DS70357)

- "Programmable Cyclic Redundancy Check (CRC)" (DS70346)

- "Device Configuration" (DS70618)

- "Peripheral Trigger Generator (PTG)" (DS70669)

- "Charge Time Measurement Unit (CTMU)" (DS70661)

| R/W-0               | U-0                          | R/W-0                                                    | R/W-0                   | R/W-0                       | R-0                       | R-0                | R-0                |

|---------------------|------------------------------|----------------------------------------------------------|-------------------------|-----------------------------|---------------------------|--------------------|--------------------|

| VAR                 | —                            | US1 <sup>(1)</sup>                                       | US0 <sup>(1)</sup>      | EDT <sup>(1,2)</sup>        | DL2 <sup>(1)</sup>        | DL1 <sup>(1)</sup> | DL0 <sup>(1)</sup> |

| bit 15              |                              |                                                          |                         |                             |                           |                    | bit                |

| R/W-0               | R/W-0                        | R/W-1                                                    | R/W-0                   | R/C-0                       | R-0                       | R/W-0              | R/W-0              |

| SATA <sup>(1)</sup> | SATB <sup>(1)</sup>          | SATDW <sup>(1)</sup>                                     | ACCSAT <sup>(1)</sup>   | IPL3(3)                     | SFA                       | RND <sup>(1)</sup> | IF(1)              |

| bit 7               | I                            |                                                          |                         |                             | 1                         | 1                  | bit                |

| Legend:             |                              | C = Clearable                                            | e bit                   |                             |                           |                    |                    |

| R = Readabl         | e bit                        | W = Writable                                             | bit                     | U = Unimpler                | mented bit, read          | d as '0'           |                    |

| -n = Value at       | POR                          | '1' = Bit is set                                         | t                       | '0' = Bit is cle            | ared                      | x = Bit is unkr    | nown               |

| bit 15              | 1 = Variable                 | le Exception Pro<br>exception proce                      | essing latency          | is enabled                  |                           |                    |                    |

| bit 14              |                              | nted: Read as '                                          |                         |                             |                           |                    |                    |

| bit 13-12           | -                            | SP Multiply Uns                                          |                         | Control bits <sup>(1)</sup> |                           |                    |                    |

|                     | 01 = DSP er<br>00 = DSP er   | ngine multiplies<br>ngine multiplies<br>ngine multiplies | are unsigned are signed |                             |                           |                    |                    |

| bit 11              | •                            | O Loop Terminatives executing Dot<br>t                   |                         |                             | iteration                 |                    |                    |

| bit 10-8            |                              | Loop Nesting<br>oops are active                          |                         | (1)                         |                           |                    |                    |

|                     | •                            |                                                          |                         |                             |                           |                    |                    |

|                     | •                            |                                                          |                         |                             |                           |                    |                    |

|                     | 001 = 1 DO k<br>000 = 0 DO k | oop is active<br>oops are active                         |                         |                             |                           |                    |                    |

| bit 7               | SATA: ACCA                   | A Saturation En                                          | able bit <sup>(1)</sup> |                             |                           |                    |                    |

|                     |                              | ator A saturatio<br>ator A saturatio                     |                         |                             |                           |                    |                    |

| bit 6               | SATB: ACCE                   | B Saturation En                                          | able bit <sup>(1)</sup> |                             |                           |                    |                    |

|                     |                              | ator B saturatio<br>ator B saturatio                     |                         |                             |                           |                    |                    |

| bit 5               | SATDW: Dat                   | ta Space Write                                           | from DSP Engi           | ne Saturation               | Enable bit <sup>(1)</sup> |                    |                    |

|                     |                              | ace write satura<br>ace write satura                     |                         | I                           |                           |                    |                    |

| bit 4               |                              | cumulator Satu                                           |                         | elect bit <sup>(1)</sup>    |                           |                    |                    |

|                     |                              | uration (super s<br>uration (normal                      | ,                       |                             |                           |                    |                    |

| bit 3               |                              | nterrupt Priority                                        |                         |                             |                           |                    |                    |

|                     |                              | errupt Priority Le<br>errupt Priority Le                 |                         |                             |                           |                    |                    |

|                     | nis bit is availabl          |                                                          | PXXXMC20X/              | 50X and dsPl                | C33EPXXXGP                | 50X devices on     | ly.                |

| 2: Th               | nis bit is always            | reau as 0.                                               |                         |                             |                           |                    |                    |

## REGISTER 3-2: CORCON: CORE CONTROL REGISTER

**3:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

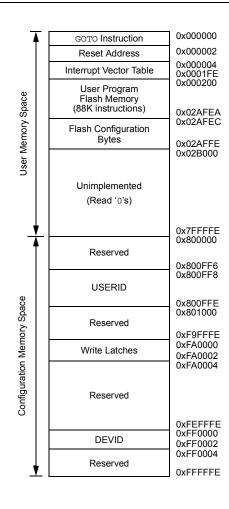

#### FIGURE 4-4: PROGRAM MEMORY MAP FOR dsPIC33EP256GP50X, dsPIC33EP256MC20X/50X AND PIC24EP256GP/MC20X DEVICES

Note: Memory areas are not shown to scale.

#### 4.4.1 PAGED MEMORY SCHEME

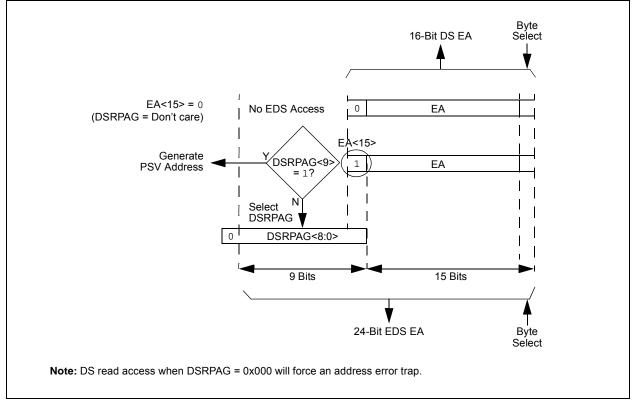

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre-modified and post-modified Effective Addresses (EA). The upper half of the base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Read Page register (DSRPAG) or the 9-bit Write Page register (DSWPAG), to form an Extended Data Space (EDS) address or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

Construction of the EDS address is shown in Example 4-1. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when base address bit, EA<15> = 1, DSWPAG<8:0> are concatenated onto EA<14:0> to form the 24-bit EDS write address.

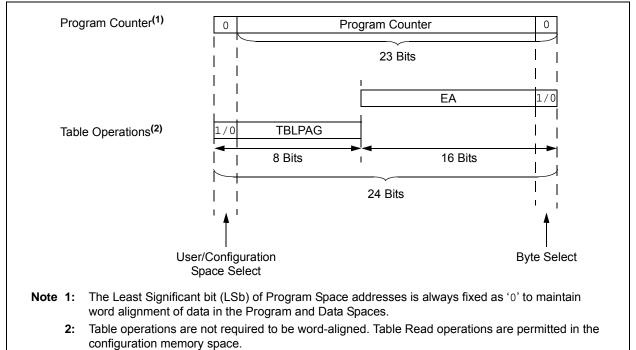

### 4.8 Interfacing Program and Data Memory Spaces

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture uses a 24-bit-wide Program Space (PS) and a 16-bit-wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

#### TABLE 4-65: PROGRAM SPACE ADDRESS CONSTRUCTION

|                        | Access        | Program Space Address                 |              |               |                     |     |  |  |  |

|------------------------|---------------|---------------------------------------|--------------|---------------|---------------------|-----|--|--|--|

| Access Type            | Space         | <23>                                  | <22:16>      | <15>          | <14:1>              | <0> |  |  |  |

| Instruction Access     | User          | 0 PC<22:1><br>0xx xxxx xxxx xxxx xxx0 |              |               |                     | 0   |  |  |  |

| (Code Execution)       |               |                                       |              |               |                     |     |  |  |  |

| TBLRD/TBLWT            | User          | TB                                    | LPAG<7:0>    | Data EA<15:0> |                     |     |  |  |  |

| (Byte/Word Read/Write) |               | 0                                     | 0xxx xxxx xx |               | xxxx xxxx xxxx xxxx |     |  |  |  |

|                        | Configuration | TBLPAG<7:0>                           |              |               | Data EA<15:0>       |     |  |  |  |

|                        |               | 1                                     | xxx xxxx     | XXXX XX       | ***                 |     |  |  |  |

#### FIGURE 4-22: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

#### REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER (CONTINUED)

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- $\label{eq:constraint} \textbf{2:} \quad \text{This bit is cleared when the ROI bit is set and an interrupt occurs.}$

- **3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

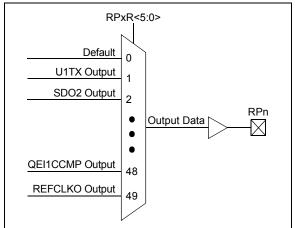

#### 11.4.4.2 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 11-18 through Register 11-27). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-3 and Figure 11-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 11-3: MULTIPLEXING REMAPPABLE OUTPUT FOR RPn

#### 11.4.4.3 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn pins is possible. This includes both many-toone and one-to-many mappings of peripheral inputs and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

#### TABLE 11-3: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

| Function                | RPxR<5:0> | Output Name                                   |

|-------------------------|-----------|-----------------------------------------------|

| Default PORT            | 000000    | RPn tied to Default Pin                       |

| U1TX                    | 000001    | RPn tied to UART1 Transmit                    |

| U2TX                    | 000011    | RPn tied to UART2 Transmit                    |

| SDO2                    | 001000    | RPn tied to SPI2 Data Output                  |

| SCK2                    | 001001    | RPn tied to SPI2 Clock Output                 |

| SS2                     | 001010    | RPn tied to SPI2 Slave Select                 |

| C1TX <sup>(2)</sup>     | 001110    | RPn tied to CAN1 Transmit                     |

| OC1                     | 010000    | RPn tied to Output Compare 1 Output           |

| OC2                     | 010001    | RPn tied to Output Compare 2 Output           |

| OC3                     | 010010    | RPn tied to Output Compare 3 Output           |

| OC4                     | 010011    | RPn tied to Output Compare 4 Output           |

| C1OUT                   | 011000    | RPn tied to Comparator Output 1               |

| C2OUT                   | 011001    | RPn tied to Comparator Output 2               |

| C3OUT                   | 011010    | RPn tied to Comparator Output 3               |

| SYNCO1 <sup>(1)</sup>   | 101101    | RPn tied to PWM Primary Time Base Sync Output |

| QEI1CCMP <sup>(1)</sup> | 101111    | RPn tied to QEI 1 Counter Comparator Output   |

| REFCLKO                 | 110001    | RPn tied to Reference Clock Output            |

| C4OUT                   | 110010    | RPn tied to Comparator Output 4               |

Note 1: This function is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This function is available in dsPIC33EPXXXGP/MC50X devices only.

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| FLTEN15 | FLTEN14 | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10 | FLTEN9 | FLTEN8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

| FLTEN7  | FLTEN6  | FLTEN5  | FLTEN4  | FLTEN3  | FLTEN2  | FLTEN1 | FLTEN0 |

| bit 7   |         |         |         |         |         |        | bit 0  |

|         |         |         |         |         |         |        |        |

| Legend: |         |         |         |         |         |        |        |

#### REGISTER 21-11: CxFEN1: ECANx ACCEPTANCE FILTER ENABLE REGISTER 1

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0

FLTEN<15:0>: Enable Filter n to Accept Messages bits

1 = Enables Filter n

0 = Disables Filter n

# REGISTER 21-12: CxBUFPNT1: ECANx FILTER 0-3 BUFFER POINTER REGISTER 1

| R/W-0         | R/W-0             | R/W-0                                                          | R/W-0            | R/W-0                                   | R/W-0           | R/W-0  | R/W-0 |  |  |  |

|---------------|-------------------|----------------------------------------------------------------|------------------|-----------------------------------------|-----------------|--------|-------|--|--|--|

|               | F3BF              | ><3:0>                                                         |                  | F2BP<3:0>                               |                 |        |       |  |  |  |

| bit 15        |                   |                                                                |                  |                                         |                 |        | bit 8 |  |  |  |

| R/W-0         | R/W-0             | R/W-0                                                          | R/W-0            | R/W-0                                   | R/W-0           | R/W-0  | R/W-0 |  |  |  |

|               | F1BF              | ><3:0>                                                         |                  |                                         | F0BF            | P<3:0> |       |  |  |  |

| bit 7         |                   |                                                                |                  |                                         |                 |        | bit C |  |  |  |

| Legend:       |                   |                                                                |                  |                                         |                 |        |       |  |  |  |

| R = Readabl   | e bit             | W = Writable                                                   | bit              | U = Unimplemented bit, read as '0'      |                 |        |       |  |  |  |

| -n = Value at | POR               | '1' = Bit is set                                               |                  | '0' = Bit is cleared x = Bit is unknown |                 |        |       |  |  |  |

| bit 15-12     | F3BP<3:0>         | : RX Buffer Mas                                                | k for Filter 3 b | oits                                    |                 |        |       |  |  |  |

|               | 1110 = Filte<br>• | r hits received in<br>r hits received in<br>r hits received in | n RX Buffer 14   |                                         |                 |        |       |  |  |  |

|               | 0001              | er hits received in<br>er hits received in                     |                  |                                         |                 |        |       |  |  |  |

| bit 11-8      | F2BP<3:0>         | RX Buffer Mas                                                  | k for Filter 2 b | oits (same value                        | s as bits<15:1  | 2>)    |       |  |  |  |

| bit 7-4       | F1BP<3:0>         | RX Buffer Mas                                                  | k for Filter 1 b | oits (same value                        | s as bits<15:12 | 2>)    |       |  |  |  |

|               |                   |                                                                |                  |                                         |                 |        |       |  |  |  |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 21-19: CxFMSKSEL2: ECANx FILTER 15-8 MASK SELECTION REGISTER 2

| R/W-0                                          | R/W-0                                                                                                                | R/W-0                                                                                                                 | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                   | R/W-0                        | R/W-0  |  |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------|--------|--|

| F15M                                           | ISK<1:0>                                                                                                             | F14MS                                                                                                                 | K<1:0>                                                                                                                                               | F13MS                                                                                                                     | SK<1:0>                                                                 | F12MS                        | K<1:0> |  |

| bit 15                                         |                                                                                                                      |                                                                                                                       |                                                                                                                                                      |                                                                                                                           |                                                                         |                              | bit 8  |  |

|                                                |                                                                                                                      | 54446                                                                                                                 | 5444                                                                                                                                                 |                                                                                                                           |                                                                         | 5444.0                       |        |  |

| R/W-0                                          |                                                                                                                      |                                                                                                                       | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                   | R/W-0 R/W-0                  |        |  |

| F11M                                           | ISK<1:0>                                                                                                             | F10MS                                                                                                                 | K<1:0>                                                                                                                                               | F9MS                                                                                                                      | K<1:0>                                                                  | F8MSI                        | <<1:0> |  |

| bit 7                                          |                                                                                                                      |                                                                                                                       |                                                                                                                                                      |                                                                                                                           |                                                                         |                              | bit C  |  |

|                                                |                                                                                                                      |                                                                                                                       |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |        |  |

| Legend:                                        |                                                                                                                      |                                                                                                                       |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |        |  |

| R = Readable bit W = Writable bit              |                                                                                                                      | bit                                                                                                                   | U = Unimplem                                                                                                                                         | nented bit, read                                                                                                          | l as '0'                                                                |                              |        |  |

| -n = Value at                                  | POR                                                                                                                  | '1' = Bit is set                                                                                                      |                                                                                                                                                      | '0' = Bit is clea                                                                                                         | ared                                                                    | x = Bit is unknown           |        |  |

| bit 15 14                                      | ELEMOK A                                                                                                             | n. Maak Saura                                                                                                         | o for Filtor 15                                                                                                                                      | hita                                                                                                                      |                                                                         |                              |        |  |

|                                                | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta                                                          | ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg                                                                 | gisters contair<br>gisters contair<br>gisters contair                                                                                                | n mask<br>n mask<br>n mask                                                                                                |                                                                         |                              |        |  |

|                                                | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta                                                          | ed<br>ance Mask 2 reg<br>ance Mask 1 reg                                                                              | gisters contair<br>gisters contair<br>gisters contair                                                                                                | n mask<br>n mask<br>n mask                                                                                                | ies as bits<15:                                                         | 14>)                         |        |  |

| bit 13-12                                      | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0                                            | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg                                                           | gisters contair<br>gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14                                                          | n mask<br>n mask<br>n mask<br>n mask<br>bits (same valu                                                                   |                                                                         |                              |        |  |

| bit 15-14<br>bit 13-12<br>bit 11-10<br>bit 9-8 | 11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0                             | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Source                              | gisters contair<br>gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13                                       | n mask<br>n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu                                                | ies as bits<15:                                                         | 14>)                         |        |  |

| bit 13-12<br>bit 11-10                         | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0<br>F12MSK<1:0                | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Source<br><b>0&gt;:</b> Mask Source | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12                                       | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu                                       | ies as bits<15:<br>ies as bits<15:                                      | 14>)<br>14>)                 |        |  |

| bit 13-12<br>bit 11-10<br>bit 9-8              | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0<br>F12MSK<1:0<br>F11MSK<1:0  | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br>0>: Mask Source<br>0>: Mask Source<br>0>: Mask Source  | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12<br>e for Filter 11                    | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu                    | ies as bits<15:<br>ies as bits<15:<br>es as bits<15:′                   | 14>)<br>14>)<br>14>)         |        |  |

| bit 13-12<br>bit 11-10<br>bit 9-8<br>bit 7-6   | 11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0<br>F11MSK<1:0<br>F11MSK<1:0 | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br>0>: Mask Source<br>0>: Mask Source<br>0>: Mask Source  | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12<br>e for Filter 11<br>e for Filter 10 | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu | ies as bits<15:<br>ies as bits<15:<br>es as bits<15:<br>ies as bits<15: | 14>)<br>14>)<br>14>)<br>14>) |        |  |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 21-22: CxRXFUL1: ECANx RECEIVE BUFFER FULL REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9 | RXFUL8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXFUL7 | RXFUL6 | RXFUL5 | RXFUL4 | RXFUL3 | RXFUL2 | RXFUL1 | RXFUL0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           | C = Writable bit, but on | C = Writable bit, but only '0' can be written to clear the bit |                    |  |  |  |  |

|-------------------|--------------------------|----------------------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit                                          | , read as '0'      |  |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared                                           | x = Bit is unknown |  |  |  |  |

bit 15-0 **RXFUL<15:0>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

#### REGISTER 21-23: CxRXFUL2: ECANx RECEIVE BUFFER FULL REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL31 | RXFUL30 | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL23 | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writable bit, but only ' | C = Writable bit, but only '0' can be written to clear the bit |                    |  |  |  |  |

|-------------------|------------------------------|----------------------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit             | U = Unimplemented bit, rea                                     | ad as '0'          |  |  |  |  |

| -n = Value at POR | '1' = Bit is set             | '0' = Bit is cleared                                           | x = Bit is unknown |  |  |  |  |

bit 15-0 **RXFUL<31:16>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

#### 21.5 ECAN Message Buffers

ECAN Message Buffers are part of RAM memory. They are not ECAN Special Function Registers. The user application must directly write into the RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

#### BUFFER 21-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0           | U-0                                           | U-0               | R/W-x         | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |

|---------------|-----------------------------------------------|-------------------|---------------|------------------------------------|-------|--------------------|-------|--|

|               | —                                             | _                 | SID10         | SID9                               | SID8  | SID7               | SID6  |  |

| bit 15        |                                               |                   |               |                                    |       |                    | bit 8 |  |

| R/W-x         | R/W-x                                         | R/W-x             | R/W-x         | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |

| SID5          | SID4                                          | SID3              | SID2          | SID1                               | SID0  | SRR                | IDE   |  |

| bit 7         |                                               |                   |               |                                    | •     |                    | bit 0 |  |

| Legend:       |                                               |                   |               |                                    |       |                    |       |  |

| R = Readabl   | e bit                                         | W = Writable      | bit           | U = Unimplemented bit, read as '0' |       |                    |       |  |

| -n = Value at | POR                                           | '1' = Bit is set  |               | '0' = Bit is cleared               |       | x = Bit is unknown |       |  |

|               |                                               |                   |               |                                    |       |                    |       |  |

| bit 15-13     | Unimplemen                                    | ted: Read as '    | כי            |                                    |       |                    |       |  |

| bit 12-2      | <b>SID&lt;10:0&gt;:</b> S                     | Standard Identifi | ier bits      |                                    |       |                    |       |  |

| bit 1         | SRR: Substitu                                 | ute Remote Re     | quest bit     |                                    |       |                    |       |  |

|               | When IDE =                                    | 0:                |               |                                    |       |                    |       |  |

|               | 1 = Message                                   | will request rer  | note transmis | ssion                              |       |                    |       |  |

|               | 0 = Normal m                                  | nessage           |               |                                    |       |                    |       |  |

|               | When IDE = 1:                                 |                   |               |                                    |       |                    |       |  |

|               | The SRR bit must be set to '1'.               |                   |               |                                    |       |                    |       |  |

| bit 0         | IDE: Extended Identifier bit                  |                   |               |                                    |       |                    |       |  |

|               | 1 = Message will transmit Extended Identifier |                   |               |                                    |       |                    |       |  |

|               | 0 = Message will transmit Standard Identifier |                   |               |                                    |       |                    |       |  |

|               |                                               |                   |               |                                    |       |                    |       |  |

#### BUFFER 21-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0               | U-0   | U-0              | U-0   | R/W-x                      | R/W-x | R/W-x              | R/W-x |

|-------------------|-------|------------------|-------|----------------------------|-------|--------------------|-------|

| —                 | —     | —                |       | EID17                      | EID16 | EID15              | EID14 |

| bit 15            |       |                  |       |                            |       |                    | bit 8 |

|                   |       |                  |       |                            |       |                    |       |

| R/W-x             | R/W-x | R/W-x            | R/W-x | R/W-x                      | R/W-x | R/W-x              | R/W-x |

| EID13             | EID12 | EID11            | EID10 | EID9                       | EID8  | EID7               | EID6  |

| bit 7             |       |                  |       |                            |       |                    | bit 0 |

|                   |       |                  |       |                            |       |                    |       |

| Legend:           |       |                  |       |                            |       |                    |       |

| R = Readable bit  |       | W = Writable bit |       | U = Unimplemented bit, rea |       | ad as '0'          |       |

| -n = Value at POR |       | '1' = Bit is set |       | '0' = Bit is cleared       |       | x = Bit is unknown |       |

| L                 |       |                  |       |                            |       |                    |       |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

#### 22.2 CTMU Control Registers

| REGISTER 2    | 22-1: CTM                                                                                                                                                    | UCON1: CTMU      | J CONTROL                            | REGISTER | 1                    |                        |        |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------|----------|----------------------|------------------------|--------|--|--|

| R/W-0         | U-0                                                                                                                                                          | R/W-0            | R/W-0                                | R/W-0    | R/W-0                | R/W-0                  | R/W-0  |  |  |

| CTMUEN        | _                                                                                                                                                            | CTMUSIDL         | TGEN                                 | EDGEN    | EDGSEQEN             | IDISSEN <sup>(1)</sup> | CTTRIG |  |  |

| bit 15        |                                                                                                                                                              |                  |                                      |          |                      |                        | bit 8  |  |  |

|               |                                                                                                                                                              |                  |                                      |          |                      |                        |        |  |  |

| U-0           | U-0                                                                                                                                                          | U-0              | U-0                                  | U-0      | U-0                  | U-0                    | U-0    |  |  |

|               |                                                                                                                                                              | —                | _                                    |          | <u> </u>             |                        | _      |  |  |

| bit 7         |                                                                                                                                                              |                  |                                      |          |                      |                        | bit 0  |  |  |

|               |                                                                                                                                                              |                  |                                      |          |                      |                        |        |  |  |

| Legend:       |                                                                                                                                                              |                  |                                      |          |                      |                        |        |  |  |

| R = Readable  | e bit                                                                                                                                                        | W = Writable b   | t U = Unimplemented bit, read as '0' |          |                      |                        |        |  |  |

| -n = Value at | POR                                                                                                                                                          | '1' = Bit is set | '1' = Bit is set                     |          | '0' = Bit is cleared |                        | own    |  |  |

| bit 15        | bit 15 CTMUEN: CTMU Enable bit<br>1 = Module is enabled<br>0 = Module is disabled                                                                            |                  |                                      |          |                      |                        |        |  |  |

| bit 14        | bit 14 Unimplemented: Read as '0'                                                                                                                            |                  |                                      |          |                      |                        |        |  |  |

| bit 13        | bit 13 CTMUSIDL: CTMU Stop in Idle Mode bit<br>1 = Discontinues module operation when device enters Idle mode<br>0 = Continues module operation in Idle mode |                  |                                      |          |                      |                        |        |  |  |

| bit 12        | TGEN: Time Generation Enable bit                                                                                                                             |                  |                                      |          |                      |                        |        |  |  |

#### REGISTER 22-1: CTMUCON1: CTMU CONTROL REGISTER 1

|         | <ul> <li>1 = Hardware modules are used to trigger edges (TMRx, CTEDx, etc.)</li> <li>0 = Software is used to trigger edges (manual set of EDGxSTAT)</li> </ul> |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10  | EDGSEQEN: Edge Sequence Enable bit                                                                                                                             |

|         | <ul> <li>1 = Edge 1 event must occur before Edge 2 event can occur</li> <li>0 = No edge sequence is needed</li> </ul>                                          |

| bit 9   | IDISSEN: Analog Current Source Control bit <sup>(1)</sup>                                                                                                      |

|         | <ul> <li>1 = Analog current source output is grounded</li> <li>0 = Analog current source output is not grounded</li> </ul>                                     |

| bit 8   | CTTRIG: ADC Trigger Control bit                                                                                                                                |

|         | 1 = CTMU triggers ADC start of conversion                                                                                                                      |

|         | 0 = CTMU does not trigger ADC start of conversion                                                                                                              |

| bit 7-0 | Unimplemented: Read as '0'                                                                                                                                     |

1 = Enables edge delay generation0 = Disables edge delay generation

**EDGEN:** Edge Enable bit

bit 11

**Note 1:** The ADC module Sample-and-Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitance measurement must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

# 27.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a То comprehensive reference source. complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual', which is available from the Microchip web site (www.microchip.com).

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

## 27.1 Configuration Bits

In dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices, the Configuration bytes are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored in at the top of the on-chip program memory space, known as the Flash Configuration bytes. Their specific locations are shown in Table 27-1. The configuration data is automatically loaded from the Flash Configuration bytes to the proper Configuration Shadow registers during device Resets.

| Note: | Configuration data is reloaded on all types |

|-------|---------------------------------------------|