Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 256КВ (85.5К х 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256gp204-i-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 4-3**: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| TADLL        | τу.   |        |        |            |        |        |        |            |        |              |              |             |         |             |             |              |         |               |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|--------------|--------------|-------------|---------|-------------|-------------|--------------|---------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7        | Bit 6        | Bit 5       | Bit 4   | Bit 3       | Bit 2       | Bit 1        | Bit 0   | All<br>Resets |

| IFS0         | 0800  |        | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF         | OC2IF        | IC2IF       | DMA0IF  | T1IF        | OC1IF       | IC1IF        | INTOIF  | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _            | _            | —           | INT1IF  | CNIF        | CMIF        | MI2C1IF      | SI2C1IF | 0000          |

| IFS2         | 0804  |        | _      | _          | -      |        | _      | —          | _      | _            | IC4IF        | IC3IF       | DMA3IF  | _           | —           | SPI2IF       | SPI2EIF | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | _      | _      | _          | _      | _            | _            | _           | _       | _           | MI2C2IF     | SI2C2IF      | _       | 0000          |

| IFS4         | 0808  | _      | _      | CTMUIF     | _      | _      | _      | _          | _      | _            | _            | _           | _       | CRCIF       | U2EIF       | U1EIF        | _       | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  |            | _      | _      | _      | —          | —      | _            | _            | _           | _       | _           | —           | —            | _       | 0000          |

| IFS9         | 0812  | _      | _      | _          | _      | _      | _      | —          | —      | _            | PTG3IF       | PTG2IF      | PTG1IF  | PTG0IF      | PTGWDTIF    | PTGSTEPIF    | —       | 0000          |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE         | OC2IE        | IC2IE       | DMA0IE  | T1IE        | OC1IE       | IC1IE        | INT0IE  | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | _            | _            | _           | INT1IE  | CNIE        | CMIE        | MI2C1IE      | SI2C1IE | 0000          |

| IEC2         | 0824  | _      | _      | _          | _      | _      | _      | _          | _      | _            | IC4IE        | IC3IE       | DMA3IE  | _           | _           | SPI2IE       | SPI2EIE | 0000          |

| IEC3         | 0826  | _      | _      | _          | _      | _      | _      | —          | —      | _            | _            | _           | _       | _           | MI2C2IE     | SI2C2IE      | —       | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     | _      | _      | _      | _          | _      | _            | _            | _           | _       | CRCIE       | U2EIE       | U1EIE        | _       | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | _      | _      | _      | _          | _      | _            | _            | _           | _       | _           | _           | _            | _       | 0000          |

| IEC9         | 0832  | _      | _      | _          | _      | _      | _      | —          | —      | _            | PTG3IE       | PTG2IE      | PTG1IE  | PTG0IE      | PTGWDTIE    | PTGSTEPIE    | —       | 0000          |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      | (      | OC1IP<2:0  | >      | — IC1IP<2:0> |              | —           |         | INT0IP<2:0> |             | 4444         |         |               |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |        | _      | (      | OC2IP<2:0  | >      | _            | IC2IP<2:0>   |             | _       | C           | 0MA0IP<2:0> |              | 4444    |               |

| IPC2         | 0844  | _      | U      | J1RXIP<2:0 | >      | _      | ;      | SPI1IP<2:0 | >      | _            | SPI1EIP<2:0> |             | _       |             | T3IP<2:0>   |              | 4444    |               |

| IPC3         | 0846  | _      | _      | _          | _      | _      | D      | )MA1IP<2:  | 0>     | _            |              | AD1IP<2:0>  |         | _           | ι           | J1TXIP<2:0>  |         | 0444          |

| IPC4         | 0848  |        |        | CNIP<2:0>  |        |        |        | CMIP<2:0   | >      | _            |              | MI2C1IP<2:0 | >       | _           | S           | SI2C1IP<2:0> |         | 4444          |

| IPC5         | 084A  | _      | _      | _          | _      | _      | _      | _          | _      | _            | _            | —           | _       | _           | I           | INT1IP<2:0>  |         | 0004          |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      | (      | OC4IP<2:0  | >      | _            |              | OC3IP<2:0>  |         | _           | C           | )ma2IP<2:0>  |         | 4444          |

| IPC7         | 084E  |        | I      | U2TXIP<2:0 | >      |        | L      | J2RXIP<2:  | )>     | _            |              | INT2IP<2:0> |         | _           |             | T5IP<2:0>    |         | 4444          |

| IPC8         | 0850  |        | _      | _          | _      |        | _      | —          | —      | _            |              | SPI2IP<2:0> |         | _           | S           | SPI2EIP<2:0> |         | 0044          |

| IPC9         | 0852  |        | _      | _          | _      |        |        | IC4IP<2:0  | >      | _            |              | IC3IP<2:0>  |         | _           | C           | 0MA3IP<2:0>  |         | 0444          |

| IPC12        | 0858  |        | _      | _          | _      |        | N      | 112C2IP<2: | 0>     | _            |              | SI2C2IP<2:0 | >       | _           | _           | _            | _       | 0440          |

| IPC16        | 0860  |        |        | CRCIP<2:0> | >      |        |        | U2EIP<2:0  | >      | _            |              | U1EIP<2:0>  |         | _           | _           | _            | _       | 4440          |

| IPC19        | 0866  |        | _      | _          | _      | _      | _      | _          | _      | _            |              | CTMUIP<2:0  | >       | _           | _           | _            | _       | 0040          |

| IPC35        | 0886  |        |        | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >      | _            | _            | _           | _       | _           | _           | _            | _       | 4400          |

| IPC36        | 0888  | _      |        | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<    | 2:0>   | _            | P            | TGSTEPIP<2  | :0>     | _           | _           | —            | _       | 4440          |

| IPC37        | 088A  | _      | _      | _          | _      | _      | F      | PTG3IP<2:  | )>     | _            |              | PTG2IP<2:0  | >       | _           | F           | PTG1IP<2:0>  |         | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | _      |        |        |            | —      | _            | DIV0ERR      | DMACERR     | MATHERR | ADDRERR     | STKERR      | OSCFAIL      |         | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      |        |        |            | _      | _            |              | —           | —       | _           | INT2EP      | INT1EP       | INT0EP  | 8000          |

| INTCON3      | 08C4  | _      | _      |            | _      |        |        | _          | _      | _            | _            | DAE         | DOOVR   | _           | _           | —            |         | 0000          |

| INTCON4      | 08C6  |        | _      | _          | _      | _      | _      | —          | _      | _            | _            | _           | _       | _           | _           |              | SGHT    | 0000          |

| INTTREG      | 08C8  | _      |        |            | _      |        | ILR<   | 3:0>       |        |              |              |             | VECN    | UM<7:0>     |             |              |         | 0000          |

|              |       |        |        |            |        |        |        |            |        |              |              |             |         |             |             |              |         |               |

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

#### TABLE 4-24: CRC REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14                  | Bit 13 | Bit 12 | 12         Bit 11         Bit 2         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1 |  |  |          |              |      |  |      | Bit 0 | All<br>Resets |  |      |

|-----------|-------|--------|-------------------------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|----------|--------------|------|--|------|-------|---------------|--|------|

| CRCCON1   | 0640  | CRCEN  | —                       | CSIDL  |        | VWORD<4:0> CRCFUL CRCMPT CRCISEL CRCGO LENDIAN                                                                                                  |  |  |          |              |      |  |      | —     | 0000          |  |      |

| CRCCON2   | 0642  |        | DWIDTH<4:0> PLEN<4:0> ( |        |        |                                                                                                                                                 |  |  |          |              |      |  |      | 0000  |               |  |      |

| CRCXORL   | 0644  |        | X<15:1> — (             |        |        |                                                                                                                                                 |  |  |          |              |      |  |      | 0000  |               |  |      |

| CRCXORH   | 0646  |        |                         |        |        |                                                                                                                                                 |  |  | X·       | <31:16>      |      |  |      |       |               |  | 0000 |

| CRCDATL   | 0648  |        |                         |        |        |                                                                                                                                                 |  |  | CRC Data | Input Low V  | Vord |  |      |       |               |  | 0000 |

| CRCDATH   | 064A  |        |                         |        |        |                                                                                                                                                 |  |  | CRC Data | Input High \ | Vord |  |      |       |               |  | 0000 |

| CRCWDATL  | 064C  |        | CRC Result Low Word 00  |        |        |                                                                                                                                                 |  |  |          |              |      |  | 0000 |       |               |  |      |

| CRCWDATH  | 064E  |        | CRC Result High Word 00 |        |        |                                                                                                                                                 |  |  |          |              |      |  | 0000 |       |               |  |      |

Legend: — = unimplemented, read as '0'. Shaded bits are not used in the operation of the programmable CRC module.

# TABLE 4-25: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC202/502 AND PIC24EPXXXGP/MC202 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|------------|--------|--------|-------|-------|-------|-------|------------|-------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  | —      | —      |        | RP35R<5:0> |        |        |       |       |       | _     | RP20R<5:0> |       |       |        |       |       |               |

| RPOR1        | 0682  | _      | _      |        | RP37R<5:0> |        |        |       |       | _     | Ι     | RP36R<5:0> |       |       |        |       |       |               |

| RPOR2        | 0684  | _      | _      |        |            | RP39F  | <5:0>  |       |       | _     | Ι     | RP38R<5:0> |       |       |        |       |       | 0000          |

| RPOR3        | 0686  | _      | _      |        | RP41R<5:0> |        |        |       |       | _     | Ι     | RP40R<5:0> |       |       |        |       | 0000  |               |

| RPOR4        | 0688  | _      | _      |        | RP43R<5:0> |        |        |       |       |       | _     |            |       | RP42F | R<5:0> |       |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-26: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC203/503 AND PIC24EPXXXGP/MC203 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |  |

|--------------|-------|--------|--------|--------|------------|--------|--------|-------|-------|-------|-------|-------|------------|-------|--------|-------|-------|---------------|--|

| RPOR0        | 0680  |        | —      |        | RP35R<5:0> |        |        |       |       | _     | _     |       | RP20R<5:0> |       |        |       |       |               |  |

| RPOR1        | 0682  | _      | _      |        | RP37R<5:0> |        |        |       |       | _     | _     |       | RP36R<5:0> |       |        |       |       |               |  |

| RPOR2        | 0684  | _      | _      |        |            | RP39F  | २<5:0> |       |       | _     | —     |       | RP38R<5:0> |       |        |       |       | 0000          |  |

| RPOR3        | 0686  | _      | _      |        |            | RP41F  | २<5:0> |       |       | _     | —     |       | RP40R<5:0> |       |        |       |       | 0000          |  |

| RPOR4        | 0688  | _      | _      |        |            | RP43F  | ۲<5:0> |       |       | _     | _     |       |            | RP42F | २<5:0> |       |       | 0000          |  |

| RPOR5        | 068A  | _      | _      | _      |            |        |        |       |       | _     | _     |       |            |       |        | _     | 0000  |               |  |

| RPOR6        | 068C  | _      | —      |        |            |        |        |       |       |       | 0000  |       |            |       |        |       |       |               |  |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-0                | R/W-0                   | R/W-0                | R/W-0 | R/C-0 | R/C-0 | R-0   | R/W-0 |

|----------------------|-------------------------|----------------------|-------|-------|-------|-------|-------|

| OA                   | OB                      | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| bit 15               |                         |                      |       |       |       |       | bit 8 |

|                      |                         |                      |       |       |       |       |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>    | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|                      | IPL<2:0> <sup>(2)</sup> |                      | RA    | Ν     | OV    | Z     | С     |

| bit 7                |                         |                      |       |       |       |       | bit 0 |

|                      |                         |                      |       |       |       |       |       |

## REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>        |

|---------|----------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                               |

|         | 101 = CPU Interrupt Priority Level is 5 (13)                               |

|         | 100 = CPU Interrupt Priority Level is 4 (12)                               |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                               |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                               |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                |

- **Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

| Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment          | Peripheral Pir<br>Select Input<br>Register Value |     | Pin Assignment |

|--------------------------------------------------|------------------|-------------------------|--------------------------------------------------|-----|----------------|

| 000 0000                                         | I                | Vss                     | 010 1101                                         |     | RPI45          |

| 000 0001                                         | I                | C1OUT <sup>(1)</sup>    | 010 1110                                         | I   | RPI46          |

| 000 0010                                         | I                | C2OUT <sup>(1)</sup>    | 010 1111                                         | I   | RPI47          |

| 000 0011                                         | I                | C3OUT <sup>(1)</sup>    | 011 0000                                         | _   | _              |

| 000 0100                                         | I                | C4OUT <sup>(1)</sup>    | 011 0001                                         |     | _              |

| 000 0101                                         | —                | _                       | 011 0010                                         | _   | _              |

| 000 0110                                         | I                | PTGO30 <sup>(1)</sup>   | 011 0011                                         | I   | RPI51          |

| 000 0111                                         | I                | PTGO31 <sup>(1)</sup>   | 011 0100                                         | I   | RPI52          |

| 000 1000                                         | I                | FINDX1 <sup>(1,2)</sup> | 011 0101                                         | I   | RPI53          |

| 000 1001                                         | I                | FHOME1 <sup>(1,2)</sup> | 011 0110                                         | I/O | RP54           |

| 000 1010                                         | _                | _                       | 011 0111                                         | I/O | RP55           |

| 000 1011                                         | —                | _                       | 011 1000                                         | I/O | RP56           |

| 000 1100                                         | —                | —                       | 011 1001                                         | I/O | RP57           |

| 000 1101                                         | _                |                         | 011 1010                                         | I   | RPI58          |

| 000 1110                                         | —                | —                       | 011 1011                                         | _   | —              |

| 000 1111                                         | —                | —                       | 011 1100                                         | _   | —              |

| 001 0000                                         | —                | —                       | 011 1101                                         | —   | _              |

| 001 0001                                         | —                | —                       | 011 1110                                         | _   | —              |

| 001 0010                                         | —                | —                       | 011 1111                                         | —   | —              |

| 001 0011                                         | —                | —                       | 100 0000                                         | —   | _              |

| 001 0100                                         | I/O              | RP20                    | 100 0001                                         |     | —              |

| 001 0101                                         | —                | —                       | 100 0010                                         | —   | —              |

| 001 0110                                         | —                | —                       | 100 0011                                         | _   | —              |

| 001 0111                                         | —                | —                       | 100 0100                                         |     | —              |

| 001 1000                                         | I                | RPI24                   | 100 0101                                         | _   | —              |

| 001 1001                                         | I                | RPI25                   | 100 0110                                         | _   | —              |

| 001 1010                                         | —                | —                       | 100 0111                                         |     | —              |

| 001 1011                                         | I                | RPI27                   | 100 1000                                         | _   | _              |

| 001 1100                                         | I                | RPI28                   | 100 1001                                         | _   |                |

| 001 1101                                         | —                | _                       | 100 1010                                         | _   | _              |

| 001 1110                                         | —                |                         | 100 1011                                         | _   |                |

| 001 1111                                         | —                |                         | 100 1100                                         | —   | _              |

| 010 0000                                         | I                | RPI32                   | 100 1101                                         | —   | _              |

| 010 0001                                         | I                | RPI33                   | 100 1110                                         | _   | _              |

| 010 0010                                         | I                | RPI34                   | 100 1111                                         | _   |                |

| 010 0011                                         | I/O              | RP35                    | 101 0000                                         | _   | <u> </u>       |

| 010 0100                                         | I/O              | RP36                    | 101 0001                                         | —   | _              |

| 010 0101                                         | I/O              | RP37                    | 101 0010                                         | —   | _              |

| 010 0110                                         | I/O              | RP38                    | 101 0011                                         | —   | _              |

| 010 0111                                         | I/O              | RP39                    | 101 0100                                         | _   | _              |

#### TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES

Legend: Shaded rows indicate PPS Input register values that are unimplemented.

Note 1: See Section 11.4.4.1 "Virtual Connections" for more information on selecting this pin assignment.

2: These inputs are available on dsPIC33EPXXXGP/MC50X devices only.

## 11.5 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 30-11, under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD - 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 2.4V @ IOH = -8 mA and VDD = 3.3VThe maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 30.0 "Electrical Characteristics" for additional information.

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input provided there is no external analog input, such as for a built-in self-test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

| U-0          | R/W-0                                    | R/W-0                                                                        | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0  |  |  |  |  |  |

|--------------|------------------------------------------|------------------------------------------------------------------------------|---------------|-------------------|---------------|-----------------|--------|--|--|--|--|--|

| —            |                                          |                                                                              |               | SCK2INR<6:0       | >             |                 |        |  |  |  |  |  |

| bit 15       |                                          |                                                                              |               |                   |               |                 | bit 8  |  |  |  |  |  |

|              |                                          |                                                                              |               |                   | 5444.6        | <b>D</b> 444 A  | 5444.6 |  |  |  |  |  |

| U-0          | R/W-0                                    | R/W-0                                                                        | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0  |  |  |  |  |  |

|              |                                          |                                                                              |               | SDI2R<6:0>        |               |                 |        |  |  |  |  |  |

| bit 7        |                                          |                                                                              |               |                   |               |                 | bit 0  |  |  |  |  |  |

|              |                                          |                                                                              |               |                   |               |                 |        |  |  |  |  |  |

| Legend:      |                                          |                                                                              |               |                   |               |                 |        |  |  |  |  |  |

| R = Readab   |                                          | W = Writable                                                                 |               | U = Unimplen      |               |                 |        |  |  |  |  |  |

| -n = Value a | t POR                                    | '1' = Bit is set                                                             |               | '0' = Bit is clea | ared          | x = Bit is unkr | nown   |  |  |  |  |  |

|              | 1111001 = Input tied to RPI121           |                                                                              |               |                   |               |                 |        |  |  |  |  |  |

| bit 7        | Unimpleme                                | nted: Read as 'o                                                             | כי            |                   |               |                 |        |  |  |  |  |  |

| bit 6-0      | (see Table 1 <sup>^</sup><br>1111001 = I | : Assign SPI2 D<br>1-2 for input pin<br>nput tied to RPI<br>nput tied to CMI | selection num | ,                 | esponding RPi | ר Pin bits      |        |  |  |  |  |  |

## REGISTER 11-12: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

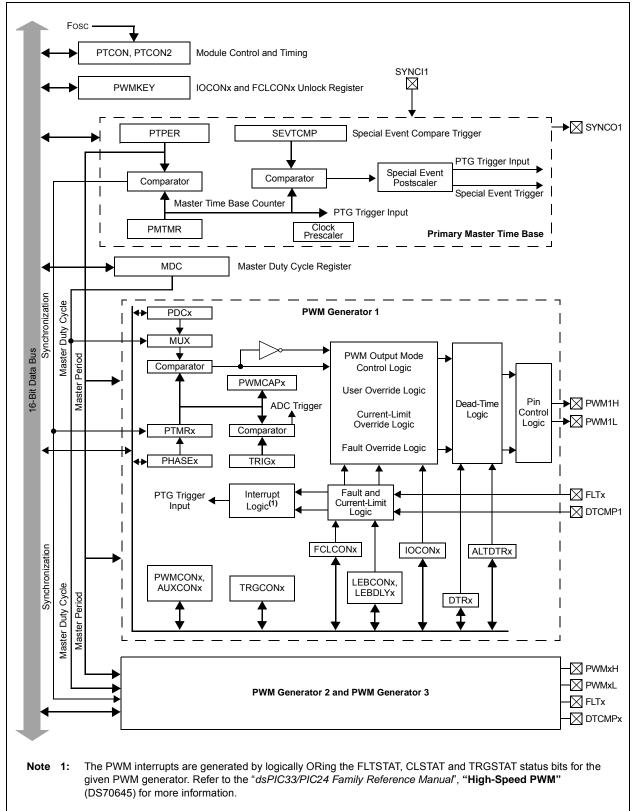

#### FIGURE 16-2: HIGH-SPEED PWMx MODULE REGISTER INTERCONNECTION DIAGRAM

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0           | U-0                                                                                          | U-0                                 | U-0            | U-0              | U-0              | U-0             | U-0    |  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------|-------------------------------------|----------------|------------------|------------------|-----------------|--------|--|--|--|--|--|

| —             | —                                                                                            | —                                   | _              | —                | —                | —               | —      |  |  |  |  |  |

| bit 15        |                                                                                              |                                     |                |                  |                  |                 | bit 8  |  |  |  |  |  |

|               |                                                                                              |                                     |                |                  |                  |                 |        |  |  |  |  |  |

| U-0           | U-0                                                                                          | U-0                                 | R-0            | R-0              | R-0              | R-0             | R-0    |  |  |  |  |  |

| —             | —                                                                                            | —                                   | DNCNT4         | DNCNT3           | DNCNT2           | DNCNT1          | DNCNT0 |  |  |  |  |  |

| bit 7         |                                                                                              |                                     |                |                  |                  |                 | bit 0  |  |  |  |  |  |

|               |                                                                                              |                                     |                |                  |                  |                 |        |  |  |  |  |  |

| Legend:       |                                                                                              |                                     |                |                  |                  |                 |        |  |  |  |  |  |

| R = Readable  | e bit                                                                                        | W = Writable                        | bit            | U = Unimpler     | mented bit, read | as '0'          |        |  |  |  |  |  |

| -n = Value at | POR                                                                                          | '1' = Bit is set                    |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |  |  |  |  |  |

|               |                                                                                              |                                     |                |                  |                  |                 |        |  |  |  |  |  |

| bit 15-5      | Unimplemen                                                                                   | ted: Read as '                      | 0'             |                  |                  |                 |        |  |  |  |  |  |

| bit 4-0       | DNCNT<4:0>                                                                                   | : DeviceNet™                        | Filter Bit Num | iber bits        |                  |                 |        |  |  |  |  |  |

|               |                                                                                              | 1 = Invalid sele<br>npares up to Da |                | 6 with EID<17    | >                |                 |        |  |  |  |  |  |

|               | •                                                                                            |                                     |                |                  |                  |                 |        |  |  |  |  |  |

|               | •                                                                                            |                                     |                |                  |                  |                 |        |  |  |  |  |  |

|               | •                                                                                            |                                     |                |                  |                  |                 |        |  |  |  |  |  |

|               | 00001 = Compares up to Data Byte 1, bit 7 with EID<0><br>00000 = Does not compare data bytes |                                     |                |                  |                  |                 |        |  |  |  |  |  |

## 21.5 ECAN Message Buffers

ECAN Message Buffers are part of RAM memory. They are not ECAN Special Function Registers. The user application must directly write into the RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

#### BUFFER 21-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0                               | U-0                                          | U-0                            | R/W-x        | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |  |

|-----------------------------------|----------------------------------------------|--------------------------------|--------------|-----------------------------------------|-------|-------|-------|--|--|

|                                   | —                                            |                                | SID10        | SID9                                    | SID8  | SID7  | SID6  |  |  |

| bit 15                            |                                              |                                |              |                                         |       |       | bit 8 |  |  |

| R/W-x                             | R/W-x                                        | R/W-x                          | R/W-x        | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |  |

| SID5                              | SID4                                         | SID3                           | SID2         | SID1                                    | SID0  | SRR   | IDE   |  |  |

| bit 7                             |                                              |                                |              |                                         |       |       | bit 0 |  |  |

| Legend:                           |                                              |                                |              |                                         |       |       |       |  |  |

| R = Readable bit W = Writable bit |                                              |                                |              | U = Unimplemented bit, read as '0'      |       |       |       |  |  |

| -n = Value at                     | POR                                          | '1' = Bit is set               |              | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |  |  |

|                                   |                                              |                                |              |                                         |       |       |       |  |  |

| bit 15-13                         | Unimplemen                                   | ted: Read as '                 | כי           |                                         |       |       |       |  |  |

| bit 12-2                          | <b>SID&lt;10:0&gt;:</b> S                    | tandard Identifi               | ier bits     |                                         |       |       |       |  |  |

| bit 1                             | SRR: Substitu                                | ute Remote Re                  | quest bit    |                                         |       |       |       |  |  |

|                                   | When IDE =                                   |                                |              |                                         |       |       |       |  |  |

|                                   | 1 = Message will request remote transmission |                                |              |                                         |       |       |       |  |  |

|                                   | 0 = Normal m                                 | = Normal message               |              |                                         |       |       |       |  |  |

|                                   | When IDE = 1                                 | L:                             |              |                                         |       |       |       |  |  |

|                                   | The SRR bit r                                | ne SRR bit must be set to '1'. |              |                                         |       |       |       |  |  |

| bit 0                             | IDE: Extende                                 | d Identifier bit               |              |                                         |       |       |       |  |  |

|                                   | 1 = Message                                  | will transmit Ex               | tended Ident | ifier                                   |       |       |       |  |  |

|                                   |                                              | will transmit St               |              |                                         |       |       |       |  |  |

|                                   |                                              |                                |              |                                         |       |       |       |  |  |

#### BUFFER 21-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0               | U-0   | U-0              | U-0   | R/W-x                              | R/W-x | R/W-x              | R/W-x |

|-------------------|-------|------------------|-------|------------------------------------|-------|--------------------|-------|

| —                 | —     | —                | _     | EID17                              | EID16 | EID15              | EID14 |

| bit 15            |       |                  |       |                                    |       |                    | bit 8 |

|                   |       |                  |       |                                    |       |                    |       |

| R/W-x             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x              | R/W-x |

| EID13             | EID12 | EID11            | EID10 | EID9                               | EID8  | EID7               | EID6  |

| bit 7             |       |                  |       |                                    |       |                    | bit 0 |

|                   |       |                  |       |                                    |       |                    |       |

| Legend:           |       |                  |       |                                    |       |                    |       |

| R = Readable bit  |       | W = Writable bit |       | U = Unimplemented bit, read as '0' |       |                    |       |

| -n = Value at POR |       | '1' = Bit is set |       | '0' = Bit is cleared               |       | x = Bit is unknown |       |

|                   |       |                  |       |                                    |       |                    |       |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

## 23.2 ADC Helpful Tips

- 1. The SMPIx control bits in the AD1CON2 register:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated, if enabled.

- b) When the CSCNA bit in the AD1CON2 registers is set to '1', this determines when the ADC analog scan channel list, defined in the AD1CSSL/AD1CSSH registers, starts over from the beginning.

- c) When the DMA peripheral is not used (ADDMAEN = 0), this determines when the ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0.

- d) When the DMA peripheral is used (ADDMAEN = 1), this determines when the DMA Address Pointer is incremented after a sample/conversion operation. ADC1BUF0 is the only ADC buffer used in this mode. The ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0. The DMA address is incremented after completion of every 32nd sample/conversion operation. Conversion results are stored in the ADC1BUF0 register for transfer to RAM using DMA.

- 2. When the DMA module is disabled (ADDMAEN = 0), the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF, regardless of which analog inputs are being used subject to the SMPIx bits and the condition described in 1c) above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- 3. When the DMA module is enabled (ADDMAEN = 1), the ADC module has only 1 ADC result buffer (i.e., ADC1BUF0) per ADC peripheral and the ADC conversion result must be read, either by the CPU or DMA Controller, before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (AD1CON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely, even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in Manual Sample mode, particularly where the user's code is setting the SAMP bit (AD1CON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

5. Enabling op amps, comparator inputs and external voltage references can limit the availability of analog inputs (ANx pins). For example, when Op Amp 2 is enabled, the pins for ANO, AN1 and AN2 are used by the op amp's inputs and output. This negates the usefulness of Alternate Input mode since the MUXA selections use AN0-AN2. Carefully study the ADC block diagram to determine the configuration that will best suit your application. Configuration examples are available in the "Analog-to-Digital Converter (ADC)" (DS70621) section in the "dsPIC33/ PIC24 Family Reference Manual".

### 23.3 ADC Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser:<br>http://www.microchip.com/wwwproducts/ |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Devices.aspx?dDocName=en555464                                                                                                                          |

### 23.3.1 KEY RESOURCES

- "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| U-0                                | U-0                                                                                                                                                                                                          | U-0                                                                                                                      | U-0           | U-0                                     | U-0             | U-0     | R/W-0   |  |  |  |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------------|-----------------|---------|---------|--|--|--|

| —                                  | —                                                                                                                                                                                                            | —                                                                                                                        | —             | —                                       | —               | —       | ADDMAEN |  |  |  |

| bit 15                             |                                                                                                                                                                                                              |                                                                                                                          |               |                                         |                 |         | bit 8   |  |  |  |

|                                    |                                                                                                                                                                                                              |                                                                                                                          |               |                                         |                 |         |         |  |  |  |

| U-0                                | U-0                                                                                                                                                                                                          | U-0                                                                                                                      | U-0           | U-0                                     | R/W-0           | R/W-0   | R/W-0   |  |  |  |

| —                                  |                                                                                                                                                                                                              | —                                                                                                                        | —             | —                                       | DMABL2          | DMABL1  | DMABL0  |  |  |  |

| bit 7                              |                                                                                                                                                                                                              |                                                                                                                          |               |                                         |                 |         | bit 0   |  |  |  |

| Levend                             |                                                                                                                                                                                                              |                                                                                                                          |               |                                         |                 |         |         |  |  |  |

| Legend:                            | le hit                                                                                                                                                                                                       |                                                                                                                          | .:.           |                                         | mented bit meet |         |         |  |  |  |

| R = Readable bit W = Writable bit  |                                                                                                                                                                                                              |                                                                                                                          | DIT           | U = Unimplemented bit, read as '0'      |                 |         |         |  |  |  |

| -n = Value at POR '1' = Bit is set |                                                                                                                                                                                                              |                                                                                                                          |               | '0' = Bit is cleared x = Bit is unknown |                 |         |         |  |  |  |

| bit 15-9                           | Unimplemen                                                                                                                                                                                                   | ted: Read as '0                                                                                                          | ,             |                                         |                 |         |         |  |  |  |

| bit 8                              | -                                                                                                                                                                                                            |                                                                                                                          |               |                                         |                 |         |         |  |  |  |

| DILO                               |                                                                                                                                                                                                              | ADDMAEN: ADC1 DMA Enable bit<br>L = Conversion results are stored in the ADC1BUF0 register for transfer to RAM using DMA |               |                                         |                 |         |         |  |  |  |

|                                    | <ul> <li>Conversion results are stored in the ADC1BUF0 register for transfer to RAM using DMA</li> <li>Conversion results are stored in ADC1BUF0 through ADC1BUFF registers; DMA will not be used</li> </ul> |                                                                                                                          |               |                                         |                 |         |         |  |  |  |

| bit 7-3                            | Unimplemen                                                                                                                                                                                                   | ted: Read as '0                                                                                                          | )'            |                                         |                 |         |         |  |  |  |

| bit 2-0                            | DMABL<2:0>                                                                                                                                                                                                   | Selects Numb                                                                                                             | per of DMA Bu | uffer Locations                         | per Analog Inp  | ut bits |         |  |  |  |

|                                    | 111 = Allocates 128 words of buffer to each analog input                                                                                                                                                     |                                                                                                                          |               |                                         |                 |         |         |  |  |  |

|                                    | 110 = Allocates 64 words of buffer to each analog input                                                                                                                                                      |                                                                                                                          |               |                                         |                 |         |         |  |  |  |

|                                    | 101 = Allocates 32 words of buffer to each analog input                                                                                                                                                      |                                                                                                                          |               |                                         |                 |         |         |  |  |  |

|                                    |                                                                                                                                                                                                              | es 16 words of                                                                                                           |               | <b>U</b> 1                              |                 |         |         |  |  |  |

|                                    |                                                                                                                                                                                                              | es 8 words of b<br>es 4 words of b                                                                                       |               |                                         |                 |         |         |  |  |  |

|                                    |                                                                                                                                                                                                              | es 2 words of b                                                                                                          |               |                                         |                 |         |         |  |  |  |

|                                    |                                                                                                                                                                                                              | es 1 word of bu                                                                                                          |               | U I                                     |                 |         |         |  |  |  |

|                                    |                                                                                                                                                                                                              |                                                                                                                          |               | <b>U</b>                                |                 |         |         |  |  |  |

## REGISTER 23-4: AD1CON4: ADC1 CONTROL REGISTER 4

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0      | U-0                                                                                                                                                                        | U-0                                                                                                              | R/W-0                           | R/W-0                 | R/W-0                    | R/W-0                 | R/W-0                 |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------|--------------------------|-----------------------|-----------------------|--|--|--|

| CH0NB      |                                                                                                                                                                            | _                                                                                                                | CH0SB4 <sup>(1)</sup>           | CH0SB3 <sup>(1)</sup> | CH0SB2 <sup>(1)</sup>    | CH0SB1 <sup>(1)</sup> | CH0SB0 <sup>(1)</sup> |  |  |  |

| bit 15     |                                                                                                                                                                            | -                                                                                                                |                                 |                       |                          |                       | bit 8                 |  |  |  |

|            |                                                                                                                                                                            |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |

| R/W-0      | U-0                                                                                                                                                                        | U-0                                                                                                              | R/W-0                           | R/W-0                 | R/W-0                    | R/W-0                 | R/W-0                 |  |  |  |

| CH0NA      |                                                                                                                                                                            | _                                                                                                                | CH0SA4 <sup>(1)</sup>           | CH0SA3 <sup>(1)</sup> | CH0SA2 <sup>(1)</sup>    | CH0SA1 <sup>(1)</sup> | CH0SA0 <sup>(1)</sup> |  |  |  |

| bit 7      |                                                                                                                                                                            |                                                                                                                  |                                 |                       |                          |                       | bit C                 |  |  |  |

|            |                                                                                                                                                                            |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |

| Legend:    |                                                                                                                                                                            |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |

| R = Reada  |                                                                                                                                                                            | W = Writable                                                                                                     |                                 |                       | nented bit, read         |                       |                       |  |  |  |

| -n = Value | e at POR                                                                                                                                                                   | '1' = Bit is set                                                                                                 |                                 | '0' = Bit is clea     | ared                     | x = Bit is unkn       | own                   |  |  |  |

| hit 15     |                                                                                                                                                                            | annal O Nagativa                                                                                                 | Input Coloct for                | r Comple MUX          |                          |                       |                       |  |  |  |

| bit 15     |                                                                                                                                                                            | nannel 0 Negative                                                                                                |                                 |                       |                          |                       |                       |  |  |  |

|            |                                                                                                                                                                            | 1 = Channel 0 negative input is AN1 <sup>(1)</sup><br>0 = Channel 0 negative input is VREFL                      |                                 |                       |                          |                       |                       |  |  |  |

| bit 14-13  | Unimpleme                                                                                                                                                                  | ented: Read as '0                                                                                                | )'                              |                       |                          |                       |                       |  |  |  |

| bit 12-8   | CH0SB<4:0                                                                                                                                                                  | <b>0&gt;:</b> Channel 0 Por                                                                                      | sitive Input Sele               | ect for Sample I      | MUXB bits <sup>(1)</sup> |                       |                       |  |  |  |

|            | <b>CH0SB&lt;4:0&gt;:</b> Channel 0 Positive Input Select for Sample MUXB bits <sup>(1)</sup><br>11111 = Open; use this selection with CTMU capacitive and time measurement |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |

|            | 11110 = Channel 0 positive input is connected to the CTMU temperature measurement diode (CTMU TEMP)                                                                        |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |

|            |                                                                                                                                                                            | 11101 = Reserved                                                                                                 |                                 |                       |                          |                       |                       |  |  |  |

|            | 11100 = Reserved<br>11011 = Reserved                                                                                                                                       |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |

|            | 11011 = Reserved<br>11010 = Channel 0 positive input is the output of OA3/AN6 <sup>(2,3)</sup>                                                                             |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |

|            | 11001 = Channel 0 positive input is the output of OA2/AN0 <sup>(2)</sup>                                                                                                   |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |

|            | 11000 = Channel 0 positive input is the output of OA1/AN3 <sup>(2)</sup>                                                                                                   |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |

|            | 10111 = Reserved                                                                                                                                                           |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |

|            | •                                                                                                                                                                          |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |