Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 256KB (85.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256gp204t-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

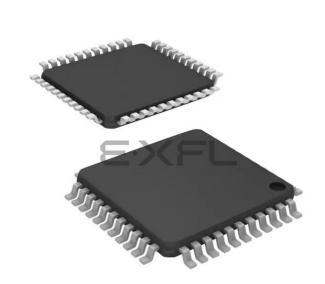

## **Pin Diagrams (Continued)**

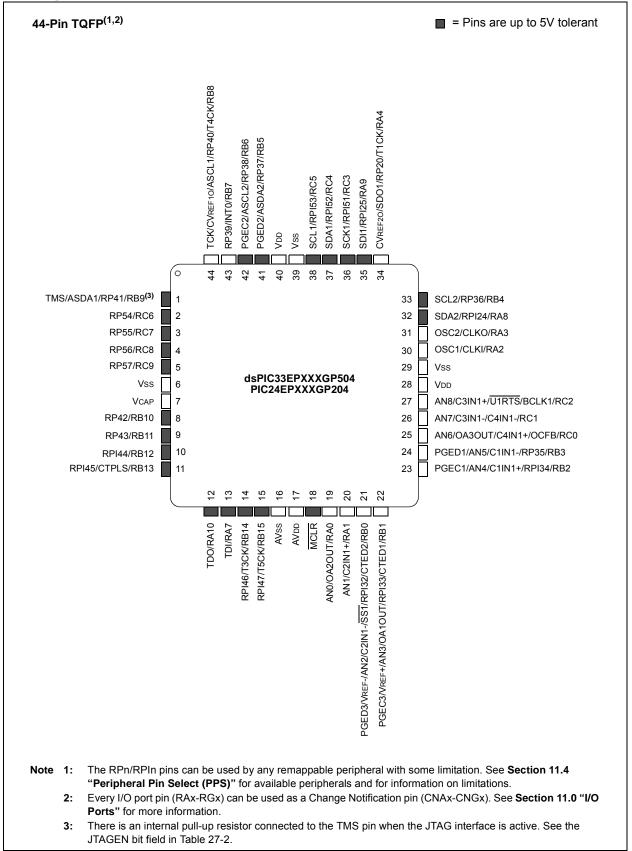

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-6).

Program memory addresses are always word-aligned on the lower word and addresses are incremented, or decremented by two, during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

# 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices reserve the addresses between 0x000000 and 0x000200 for hardcoded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of Flash memory, with the actual address for the start of code at address, 0x000002, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in **Section 7.1** "Interrupt Vector Table".

#### FIGURE 4-6: PROGRAM MEMORY ORGANIZATION

#### TABLE 4-45: DMAC REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|---------|--------|--------|--------|---------------|

| DMA0CON   | 0B00  | CHEN   | SIZE   | DIR    | HALF   | NULLW  |        | _     | _      | _     | _     | AMOD  | E<1:0> | _       | _      | MODE   | <1:0>  | 0000          |

| DMA0REQ   | 0B02  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA0STAL  | 0B04  |        |        |        |        |        |        |       | STA<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0STAH  | 0B06  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA0STBL  | 0B08  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0STBH  | 0B0A  | _      | —      | _      | _      | _      | —      | —     | —      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA0PAD   | 0B0C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0CNT   | 0B0E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA1CON   | 0B10  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | —     | —      | _     | —     | AMOD  | E<1:0> | —       | —      | MODE   | <1:0>  | 0000          |

| DMA1REQ   | 0B12  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA1STAL  | 0B14  |        |        |        |        |        |        |       | STA<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1STAH  | 0B16  | _      | —      | —      | _      | _      | _      | —     | —      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA1STBL  | 0B18  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1STBH  | 0B1A  | _      | —      | _      | _      |        | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA1PAD   | 0B1C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1CNT   | 0B1E  | _      | —      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA2CON   | 0B20  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _      | _     | _     | AMOD  | E<1:0> |         | —      | MODE   | <1:0>  | 0000          |

| DMA2REQ   | 0B22  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA2STAL  | 0B24  |        |        |        |        |        |        |       | STA<18 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2STAH  | 0B26  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA2STBL  | 0B28  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2STBH  | 0B2A  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA2PAD   | 0B2C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2CNT   | 0B2E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA3CON   | 0B30  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _      | _     | _     | AMOD  | E<1:0> | -       | —      | MODE   | <1:0>  | 0000          |

| DMA3REQ   | 0B32  | FORCE  | _      | _      | _      | _      | _      | _     | _      |       |       |       | IRQSE  | L<7:0>  |        |        |        | 00FF          |

| DMA3STAL  | 0B34  |        |        |        |        |        |        |       | STA<18 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3STAH  | 0B36  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA3STBL  | 0B38  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3STBH  | 0B3A  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA3PAD   | 0B3C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3CNT   | 0B3E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMAPWC    | 0BF0  | —      | —      | —      | —      | —      | —      |       | _      | —     | —     |       | —      | PWCOL3  | PWCOL2 | PWCOL1 | PWCOL0 | 0000          |

| DMARQC    | 0BF2  | _      | —      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      | RQCOL3  | RQCOL2 | RQCOL1 | RQCOL0 | 0000          |

| DMAPPS    | 0BF4  | _      | —      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      | PPST3   | PPST2  | PPST1  | PPST0  | 0000          |

| DMALCA    | 0BF6  | _      | _      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      |         | LSTCH  | 1<3:0> |        | 000F          |

| DSADRL    | 0BF8  |        |        |        |        |        |        |       | DSADR< | 15:0> |       |       |        |         |        |        |        | 0000          |

| DSADRH    | 0BFA  | _      | —      | —      | —      | —      | —      | —     | —      |       |       |       | DSADR• | <23:16> |        |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2013 Microchip Technology Inc.

#### 4.5 Instruction Addressing Modes

The addressing modes shown in Table 4-63 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

## 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

#### 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

- Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

#### TABLE 4-63: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |  |  |  |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |  |  |  |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |  |  |  |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |  |  |  |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |  |  |  |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |  |  |  |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |  |  |  |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |  |  |  |

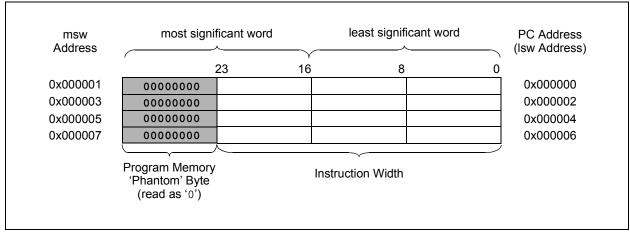

# 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM

In addition, DMA can access the entire data memory space. The Data Memory Bus Arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. Some of the peripherals supported by the DMA Controller include:

- ECAN<sup>™</sup>

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

# FIGURE 8-1: DMA CONTROLLER MODULE

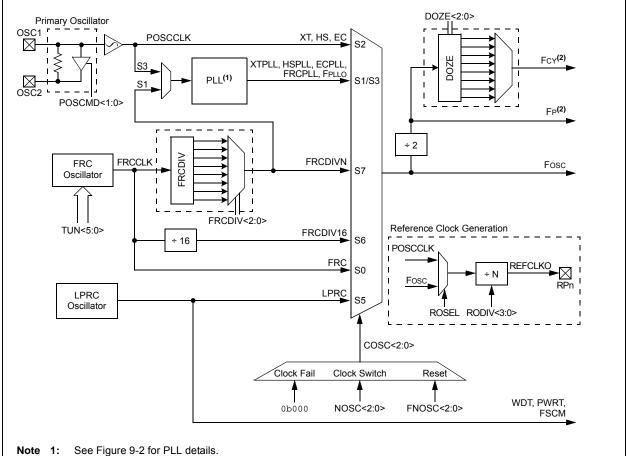

# 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator" (DS70580) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X oscillator system provides:

- On-chip Phase-Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources

- On-the-fly clock switching between various clock sources

- · Doze mode for system power savings

- Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Configuration bits for clock source selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

## FIGURE 9-1: OSCILLATOR SYSTEM DIAGRAM

2: The term, FP, refers to the clock source for all peripherals, while FCY refers to the clock source for the CPU. Throughout this document, FCY and FP are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used with a doze ratio of 1:2 or lower.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0    | U-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|------------|-------|-------|--------|-------|-------|

| —      | —   |            |       | RP43  | R<5:0> |       |       |

| bit 15 |     |            |       |       |        |       | bit 8 |

|        |     |            |       |       |        |       |       |

| U-0    | U-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

| —      | —   | RP42R<5:0> |       |       |        |       |       |

## REGISTER 11-22: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

|   | bit | 7 |

|---|-----|---|

| 1 |     |   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP43R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP43 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP42R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-23: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP55  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------|-----|-------|------------|-------|-------|-------|-------|--|--|

| —     | —   |       | RP54R<5:0> |       |       |       |       |  |  |

| bit 7 |     |       |            |       |       |       | bit 0 |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP55R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP55 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP54R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP54 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 0

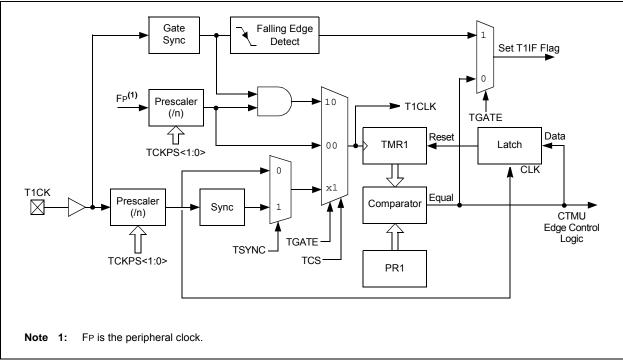

# 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer that can operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated in Asynchronous Counter mode from an external clock source

- The external clock input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler

- A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FCY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit setting for different operating modes are given in the Table 12-1.

| Mode                    | TCS | TGATE | TSYNC |  |  |  |

|-------------------------|-----|-------|-------|--|--|--|

| Timer                   | 0   | 0     | x     |  |  |  |

| Gated Timer             | 0   | 1     | x     |  |  |  |

| Synchronous<br>Counter  | 1   | х     | 1     |  |  |  |

| Asynchronous<br>Counter | 1   | x     | 0     |  |  |  |

#### TABLE 12-1: TIMER MODE SETTINGS

## FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

| R/W-0        | R/W-0                                                                                                    | R/W-0                                  | R/W-0          | U-0               | U-0                 | U-0              | U-0          |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------|----------------------------------------|----------------|-------------------|---------------------|------------------|--------------|--|--|--|--|

|              | TRGD                                                                                                     | V<3:0>                                 |                | —                 |                     | —                | _            |  |  |  |  |

| bit 15       |                                                                                                          |                                        |                |                   |                     |                  | bit 8        |  |  |  |  |

|              |                                                                                                          |                                        |                |                   |                     |                  |              |  |  |  |  |

| U-0          | U-0                                                                                                      | R/W-0                                  | R/W-0          | R/W-0             | R/W-0               | R/W-0            | R/W-0        |  |  |  |  |

| _            |                                                                                                          |                                        |                | TRGSTF            | RT<5:0> <b>(1)</b>  |                  |              |  |  |  |  |

| bit 7        |                                                                                                          |                                        |                |                   |                     |                  | bit          |  |  |  |  |

|              |                                                                                                          |                                        |                |                   |                     |                  |              |  |  |  |  |

| Legend:      | 1. 1.4                                                                                                   |                                        |                |                   |                     | (0)              |              |  |  |  |  |

| R = Readab   |                                                                                                          | W = Writable                           |                | •                 | nented bit, read    |                  |              |  |  |  |  |

| -n = Value a | t POR                                                                                                    | '1' = Bit is set                       |                | '0' = Bit is clea | ared                | x = Bit is unkn  | own          |  |  |  |  |

|              |                                                                                                          |                                        |                |                   |                     |                  |              |  |  |  |  |

| bit 15-12    |                                                                                                          | <b>)&gt;:</b> Trigger # Ou             | -              |                   |                     |                  |              |  |  |  |  |

|              | 1111 = Trigger output for every 16th trigger event                                                       |                                        |                |                   |                     |                  |              |  |  |  |  |

|              | 1110 = Trigger output for every 15th trigger event<br>1101 = Trigger output for every 14th trigger event |                                        |                |                   |                     |                  |              |  |  |  |  |

|              |                                                                                                          |                                        |                |                   |                     |                  |              |  |  |  |  |

|              |                                                                                                          | ger output for ev<br>ger output for ev |                |                   |                     |                  |              |  |  |  |  |

|              |                                                                                                          | ger output for ev                      |                |                   |                     |                  |              |  |  |  |  |

|              |                                                                                                          | ger output for ev                      |                |                   |                     |                  |              |  |  |  |  |

|              |                                                                                                          | per output for ev                      |                |                   |                     |                  |              |  |  |  |  |

|              |                                                                                                          | per output for ev                      |                |                   |                     |                  |              |  |  |  |  |

|              |                                                                                                          | ger output for ev                      |                |                   |                     |                  |              |  |  |  |  |

|              |                                                                                                          | ger output for ev                      |                |                   |                     |                  |              |  |  |  |  |

|              | 0100 = Trigg                                                                                             | ger output for ev                      | ery 5th trigge | r event           |                     |                  |              |  |  |  |  |

|              |                                                                                                          | ger output for ev                      |                |                   |                     |                  |              |  |  |  |  |

|              |                                                                                                          | ger output for ev                      |                |                   |                     |                  |              |  |  |  |  |

|              |                                                                                                          | ger output for ev                      |                |                   |                     |                  |              |  |  |  |  |

|              | 0000 = Trigg                                                                                             | ger output for ev                      | ery trigger ev | ent               |                     |                  |              |  |  |  |  |

| bit 11-6     | -                                                                                                        | nted: Read as '                        |                |                   |                     |                  |              |  |  |  |  |

| bit 5-0      | TRGSTRT<                                                                                                 | 5:0>: Trigger Po                       | stscaler Start | Enable Select     | bits <sup>(1)</sup> |                  |              |  |  |  |  |

|              | 111111 = Waits 63 PWM cycles before generating the first trigger event after the module is enabled       |                                        |                |                   |                     |                  |              |  |  |  |  |

|              |                                                                                                          |                                        |                |                   |                     |                  |              |  |  |  |  |

|              | •                                                                                                        |                                        |                | ·                 |                     |                  |              |  |  |  |  |

|              | •                                                                                                        |                                        |                | -                 |                     |                  |              |  |  |  |  |

|              | •                                                                                                        |                                        |                | -                 |                     |                  |              |  |  |  |  |

|              | •<br>•<br>•                                                                                              | aits 2 PW/M ava                        | les hefore co  | nerating the fire | t trigger event :   | after the module | a is anabled |  |  |  |  |

|              |                                                                                                          | /aits 2 PWM cyc<br>/aits 1 PWM cyc     |                |                   |                     |                  |              |  |  |  |  |

# REGISTER 16-12: TRGCONx: PWMx TRIGGER CONTROL REGISTER

# REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 6         | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)<br>Used in conjunction with the SCLREL bit.<br>1 = Enables software or receives clock stretching<br>0 = Disables software or receives clock stretching |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5         | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                                     |

|               | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                                       |

| bit 4         | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                   |

|               | <ul> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits ACKDT data bit. Hardware is clear at the end of the master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul>              |

| bit 3         | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                   |

|               | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware is clear at the end of the eighth bit of the master receive data byte.</li> <li>0 = Receive sequence is not in progress</li> </ul>                                             |

| bit 2         | <b>PEN:</b> Stop Condition Enable bit (when operating as $I^2C$ master)                                                                                                                                                                       |

| 511 2         | 1 = Initiates Stop condition on SDAx and SCLx pins. Hardware is clear at the end of the master Stop sequence.                                                                                                                                 |

| <b>h</b> :+ 4 | 0 = Stop condition is not in progress                                                                                                                                                                                                         |

| bit 1         | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                  |

|               | <ul> <li>1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware is clear at the end of the<br/>master Repeated Start sequence.</li> <li>0 = Repeated Start condition is not in progress</li> </ul>                            |

| bit 0         | <b>SEN:</b> Start Condition Enable bit (when operating as $l^2C$ master)                                                                                                                                                                      |

|               | <ul> <li>1 = Initiates Start condition on SDAx and SCLx pins. Hardware is clear at the end of the master Start sequence.</li> <li>0 = Start condition is not in progress</li> </ul>                                                           |

**Note 1:** When performing master operations, ensure that the IPMIEN bit is set to '0'.

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

## REGISTER 21-24: CxRXOVF1: ECANx RECEIVE BUFFER OVERFLOW REGISTER 1

| RXOVF7  | RXOVF6                                                               | RXOVF5 | RXOVF4 | RXOVF3 | RXOVF2 | RXOVF1 | RXOVF0 |  |

|---------|----------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|

| bit 7   |                                                                      |        |        |        |        |        | bit 0  |  |

|         |                                                                      |        |        |        |        |        |        |  |

| Legend: | gend: C = Writable bit, but only '0' can be written to clear the bit |        |        |        |        |        |        |  |

| Legend:           | C = Writable bit, but only '0' can be written to clear the bit |                                    |                    |  |  |  |

|-------------------|----------------------------------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                                               | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 15-0 RXOVF<15:0>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

#### REGISTER 21-25: CxRXOVF2: ECANx RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writable bit, but or | C = Writable bit, but only '0' can be written to clear the bit |                    |  |  |  |  |

|-------------------|--------------------------|----------------------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit                                          | t, read as '0'     |  |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared                                           | x = Bit is unknown |  |  |  |  |

bit 15-0 RXOVF<31:16>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

| PTG Output<br>Number | PTG Output Description                                  |

|----------------------|---------------------------------------------------------|

| PTGO0                | Trigger/Synchronization Source for OC1                  |

| PTGO1                | Trigger/Synchronization Source for OC2                  |

| PTGO2                | Trigger/Synchronization Source for OC3                  |

| PTGO3                | Trigger/Synchronization Source for OC4                  |

| PTGO4                | Clock Source for OC1                                    |

| PTGO5                | Clock Source for OC2                                    |

| PTGO6                | Clock Source for OC3                                    |

| PTGO7                | Clock Source for OC4                                    |

| PTGO8                | Trigger/Synchronization Source for IC1                  |

| PTGO9                | Trigger/Synchronization Source for IC2                  |

| PTGO10               | Trigger/Synchronization Source for IC3                  |

| PTGO11               | Trigger/Synchronization Source for IC4                  |

| PTGO12               | Sample Trigger for ADC                                  |

| PTGO13               | Sample Trigger for ADC                                  |

| PTGO14               | Sample Trigger for ADC                                  |

| PTGO15               | Sample Trigger for ADC                                  |

| PTGO16               | PWM Time Base Synchronous Source for PWM <sup>(1)</sup> |

| PTGO17               | PWM Time Base Synchronous Source for PWM <sup>(1)</sup> |

| PTGO18               | Mask Input Select for Op Amp/Comparator                 |

| PTGO19               | Mask Input Select for Op Amp/Comparator                 |

| PTGO20               | Reserved                                                |

| PTGO21               | Reserved                                                |

| PTGO22               | Reserved                                                |

| PTGO23               | Reserved                                                |

| PTGO24               | Reserved                                                |

| PTGO25               | Reserved                                                |

| PTGO26               | Reserved                                                |

| PTGO27               | Reserved                                                |

| PTGO28               | Reserved                                                |

| PTGO29               | Reserved                                                |

| PTGO30               | PTG Output to PPS Input Selection                       |

| PTGO31               | PTG Output to PPS Input Selection                       |

# TABLE 24-2: PTG OUTPUT DESCRIPTIONS

Note 1: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

| Bit Field              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GCP                    | General Segment Code-Protect bit<br>1 = User program memory is not code-protected<br>0 = Code protection is enabled for the entire program memory space                                                                                                                                                                                                                                                                                     |

| GWRP                   | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                                                                                                                                                                                           |

| IESO                   | <ul> <li>Two-Speed Oscillator Start-up Enable bit</li> <li>1 = Start up device with FRC, then automatically switch to the user-selected oscillator source when ready</li> <li>0 = Start up device with user-selected oscillator source</li> </ul>                                                                                                                                                                                           |

| PWMLOCK <sup>(1)</sup> | PWM Lock Enable bit<br>1 = Certain PWM registers may only be written after a key sequence<br>0 = PWM registers may be written without a key sequence                                                                                                                                                                                                                                                                                        |

| FNOSC<2:0>             | Oscillator Selection bits<br>111 = Fast RC Oscillator with Divide-by-N (FRCDIVN)<br>110 = Fast RC Oscillator with Divide-by-16 (FRCDIV16)<br>101 = Low-Power RC Oscillator (LPRC)<br>100 = Reserved; do not use<br>011 = Primary Oscillator with PLL module (XT + PLL, HS + PLL, EC + PLL)<br>010 = Primary Oscillator (XT, HS, EC)<br>001 = Fast RC Oscillator with Divide-by-N with PLL module (FRCPLL)<br>000 = Fast RC Oscillator (FRC) |

| FCKSM<1:0>             | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                                                                           |

| IOL1WAY                | Peripheral Pin Select Configuration bit<br>1 = Allow only one reconfiguration<br>0 = Allow multiple reconfigurations                                                                                                                                                                                                                                                                                                                        |

| OSCIOFNC               | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is the clock output<br>0 = OSC2 is a general purpose digital I/O pin                                                                                                                                                                                                                                                                                                          |

| POSCMD<1:0>            | Primary Oscillator Mode Select bits<br>11 = Primary Oscillator is disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                                                                                                                           |

| FWDTEN                 | <ul> <li>Watchdog Timer Enable bit</li> <li>1 = Watchdog Timer is always enabled (LPRC oscillator cannot be disabled. Clearing the SWDTEN bit in the RCON register will have no effect.)</li> <li>0 = Watchdog Timer is enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register)</li> </ul>                                                                                                 |

| WINDIS                 | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer in Non-Window mode<br>0 = Watchdog Timer in Window mode                                                                                                                                                                                                                                                                                                                              |

| PLLKEN                 | PLL Lock Enable bit<br>1 = PLL lock is enabled<br>0 = PLL lock is disabled<br>nly available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.                                                                                                                                                                                                                                                                                           |

# TABLE 27-2: CONFIGURATION BITS DESCRIPTION

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

2: When JTAGEN = 1, an internal pull-up resistor is enabled on the TMS pin. Erased devices default to JTAGEN = 1. Applications requiring I/O pins in a high-impedance state (tri-state) in Reset should use pins other than TMS for this purpose.

| DC CHARACTERISTICS |                     |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |            |        |           |  |

|--------------------|---------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|-----------|--|

| Parameter<br>No.   | Тур.                | Max. | Units                                                                                                                                                                                                                                                                                   | Conditions |        |           |  |

| Idle Current (III  | dle) <sup>(1)</sup> |      |                                                                                                                                                                                                                                                                                         |            |        |           |  |

| DC40d              | 3                   | 8    | mA                                                                                                                                                                                                                                                                                      | -40°C      |        |           |  |

| DC40a              | 3                   | 8    | mA                                                                                                                                                                                                                                                                                      | +25°C      | - 3.3V | 10 MIPS   |  |

| DC40b              | 3                   | 8    | mA                                                                                                                                                                                                                                                                                      | +85°C      | 3.3V   | 10 101195 |  |

| DC40c              | 3                   | 8    | mA                                                                                                                                                                                                                                                                                      | +125°C     | ]      |           |  |

| DC42d              | 6                   | 12   | mA                                                                                                                                                                                                                                                                                      | -40°C      |        |           |  |

| DC42a              | 6                   | 12   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3V   | 20 MIPS   |  |

| DC42b              | 6                   | 12   | mA                                                                                                                                                                                                                                                                                      | +85°C      |        | 20 1011-5 |  |

| DC42c              | 6                   | 12   | mA                                                                                                                                                                                                                                                                                      | +125°C     |        |           |  |

| DC44d              | 11                  | 18   | mA                                                                                                                                                                                                                                                                                      | -40°C      |        | 40 MIPS   |  |

| DC44a              | 11                  | 18   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3V   |           |  |

| DC44b              | 11                  | 18   | mA                                                                                                                                                                                                                                                                                      | +85°C      | 5.50   | 40 1011-3 |  |

| DC44c              | 11                  | 18   | mA                                                                                                                                                                                                                                                                                      | +125°C     |        |           |  |

| DC45d              | 17                  | 27   | mA                                                                                                                                                                                                                                                                                      | -40°C      |        |           |  |

| DC45a              | 17                  | 27   | mA                                                                                                                                                                                                                                                                                      | +25°C      | - 3.3V | 60 MIPS   |  |

| DC45b              | 17                  | 27   | mA                                                                                                                                                                                                                                                                                      | +85°C      | 3.3V   |           |  |

| DC45c              | 17                  | 27   | mA                                                                                                                                                                                                                                                                                      | +125°C     | ]      |           |  |

| DC46d              | 20                  | 35   | mA                                                                                                                                                                                                                                                                                      | -40°C      |        |           |  |

| DC46a              | 20                  | 35   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3V   | 70 MIPS   |  |

| DC46b              | 20                  | 35   | mA                                                                                                                                                                                                                                                                                      | +85°C      | ]      |           |  |

#### TABLE 30-7: DC CHARACTERISTICS: IDLE CURRENT (lidle)

**Note 1:** Base Idle current (IIDLE) is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- $\overline{\text{MCLR}}$  = VDD, WDT and FSCM are disabled

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- The NVMSIDL bit (NVMCON<12>) = 1 (i.e., Flash regulator is set to standby while the device is in Idle mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- JTAG is disabled

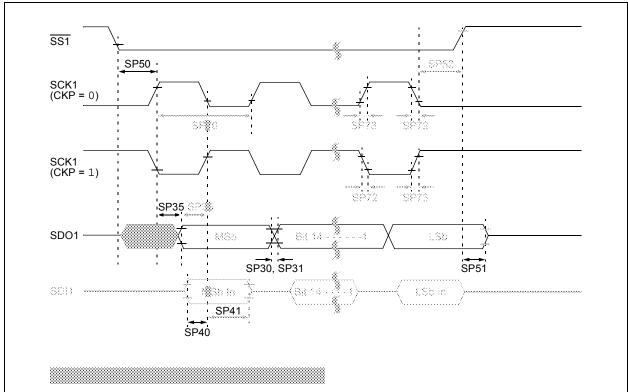

#### FIGURE 30-28: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

# TABLE 30-47:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0)TIMING REQUIREMENTS

|        |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                |  |

|--------|-----------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------------------|--|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                                                                                                                                                                                                                                                  | Typ. <sup>(2)</sup> | Max. | Units | Conditions                     |  |

| SP70   | FscP                  | Maximum SCK1 Input Frequency                 | —                                                                                                                                                                                                                                                                                     | —                   | 15   | MHz   | (Note 3)                       |  |

| SP72   | TscF                  | SCK1 Input Fall Time                         | —                                                                                                                                                                                                                                                                                     | —                   | _    | ns    | See Parameter DO32 (Note 4)    |  |

| SP73   | TscR                  | SCK1 Input Rise Time                         | —                                                                                                                                                                                                                                                                                     | —                   | _    | ns    | See Parameter DO31 (Note 4)    |  |

| SP30   | TdoF                  | SDO1 Data Output Fall Time                   | —                                                                                                                                                                                                                                                                                     | _                   | _    | ns    | See Parameter DO32<br>(Note 4) |  |

| SP31   | TdoR                  | SDO1 Data Output Rise Time                   | —                                                                                                                                                                                                                                                                                     | —                   | _    | ns    | See Parameter DO31 (Note 4)    |  |

| SP35   | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge    | —                                                                                                                                                                                                                                                                                     | 6                   | 20   | ns    |                                |  |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge | 30                                                                                                                                                                                                                                                                                    | —                   | _    | ns    |                                |  |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge   | 30                                                                                                                                                                                                                                                                                    | —                   | _    | ns    |                                |  |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge    | 30                                                                                                                                                                                                                                                                                    | —                   | _    | ns    |                                |  |

| SP50   | TssL2scH,<br>TssL2scL | SS1 ↓ to SCK1 ↑ or SCK1 ↓<br>Input           | 120                                                                                                                                                                                                                                                                                   | —                   | _    | ns    |                                |  |

| SP51   | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance       | 10                                                                                                                                                                                                                                                                                    | —                   | 50   | ns    | (Note 4)                       |  |

| SP52   | TscH2ssH,<br>TscL2ssH | SS1                                          | 1.5 Tcy + 40                                                                                                                                                                                                                                                                          | —                   |      | ns    | (Note 4)                       |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 66.7 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

| AC CHARACTERISTICS |                   |                               |                           | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le Ta \le +85^{\circ}C$ for Industrial |             |                                 |                                                  |  |  |

|--------------------|-------------------|-------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------------|--------------------------------------------------|--|--|

| Param<br>No.       | Symbol<br>TLO:SCL | Characteristic <sup>(4)</sup> |                           | Min. <sup>(1)</sup>                                                                                                                                     | -40<br>Max. | <sup>0°</sup> C ≤ IA ≤<br>Units | +125°C for Extended Conditions                   |  |  |

| IM10               |                   | Clock Low Time                | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                         | _           | μS                              |                                                  |  |  |

|                    |                   |                               | 400 kHz mode              | TCY/2 (BRG + 2)                                                                                                                                         |             | ,<br>μS                         |                                                  |  |  |

|                    |                   |                               | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                                                                                                                         |             | μs                              |                                                  |  |  |

| IM11               | THI:SCL           | Clock High Time               | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                         |             | μS                              |                                                  |  |  |

|                    |                   |                               | 400 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                         |             | μ <b>S</b>                      |                                                  |  |  |

|                    |                   |                               | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                                                                                                                         |             | μS                              |                                                  |  |  |

| IM20               | TF:SCL            | SDAx and SCLx<br>Fall Time    | 100 kHz mode              |                                                                                                                                                         | 300         | ns                              | CB is specified to be from 10 to 400 pF          |  |  |

|                    |                   |                               | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                             | 300         | ns                              |                                                  |  |  |

|                    |                   |                               | 1 MHz mode <sup>(2)</sup> |                                                                                                                                                         | 100         | ns                              |                                                  |  |  |

| IM21               | TR:SCL            | SDAx and SCLx<br>Rise Time    | 100 kHz mode              |                                                                                                                                                         | 1000        | ns                              | CB is specified to be                            |  |  |

|                    |                   |                               | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                             | 300         | ns                              | from 10 to 400 pF                                |  |  |

|                    |                   |                               | 1 MHz mode <sup>(2)</sup> |                                                                                                                                                         | 300         | ns                              | -                                                |  |  |

| IM25               | TSU:DAT           | Data Input<br>Setup Time      | 100 kHz mode              | 250                                                                                                                                                     |             | ns                              |                                                  |  |  |

|                    |                   |                               | 400 kHz mode              | 100                                                                                                                                                     |             | ns                              |                                                  |  |  |

|                    |                   |                               | 1 MHz mode <sup>(2)</sup> | 40                                                                                                                                                      |             | ns                              | -                                                |  |  |

| IM26               | Thd:dat           | Data Input<br>Hold Time       | 100 kHz mode              | 0                                                                                                                                                       |             | μS                              |                                                  |  |  |

|                    |                   |                               | 400 kHz mode              | 0                                                                                                                                                       | 0.9         | μ <b>S</b>                      |                                                  |  |  |

|                    |                   |                               | 1 MHz mode <sup>(2)</sup> | 0.2                                                                                                                                                     |             | μs                              | -                                                |  |  |

| IM30               | Tsu:sta           | Start Condition<br>Setup Time | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                         |             | μ <b>S</b>                      | Only relevant for<br>Repeated Start<br>condition |  |  |

|                    |                   |                               | 400 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                         |             | μS                              |                                                  |  |  |

|                    |                   |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                                                                                                                         |             | μs                              |                                                  |  |  |

| IM31               | THD:STA           | Start Condition<br>Hold Time  | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                         |             | μ <b>s</b>                      | After this period, the                           |  |  |

|                    |                   |                               | 400 kHz mode              | Tcy/2 (BRG +2)                                                                                                                                          |             | μS                              | first clock pulse is                             |  |  |

|                    |                   |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                                                                                                                         |             | μS                              | generated                                        |  |  |