Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

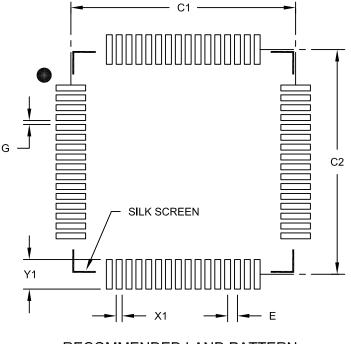

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-VQFN (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256gp206-e-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.5 **Programmer's Model**

The programmer's model for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X is shown in Figure 3-2. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions. Table 3-1 lists a description of each register.

In addition to the registers contained in the programmer's model, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/

MC20X devices contain control registers for Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only), Bit-Reversed Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only) and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory mapped, as shown in Table 4-1.

| Register(s) Name                                      | Description                                               |

|-------------------------------------------------------|-----------------------------------------------------------|

| W0 through W15                                        | Working Register Array                                    |

| ACCA, ACCB                                            | 40-Bit DSP Accumulators                                   |

| PC                                                    | 23-Bit Program Counter                                    |

| SR                                                    | ALU and DSP Engine STATUS Register                        |

| SPLIM                                                 | Stack Pointer Limit Value Register                        |

| TBLPAG                                                | Table Memory Page Address Register                        |

| DSRPAG                                                | Extended Data Space (EDS) Read Page Register              |

| DSWPAG                                                | Extended Data Space (EDS) Write Page Register             |

| RCOUNT                                                | REPEAT Loop Count Register                                |

| DCOUNT <sup>(1)</sup>                                 | DO Loop Count Register                                    |

| DOSTARTH <sup>(1,2)</sup> , DOSTARTL <sup>(1,2)</sup> | DO Loop Start Address Register (High and Low)             |

| DOENDH <sup>(1)</sup> , DOENDL <sup>(1)</sup>         | DO Loop End Address Register (High and Low)               |

| CORCON                                                | Contains DSP Engine, DO Loop Control and Trap Status bits |

#### TABLE 3-1: PROGRAMMER'S MODEL REGISTER DESCRIPTIONS

Note 1: This register is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

2: The DOSTARTH and DOSTARTL registers are read-only.

#### TABLE 4-24: CRC REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 15         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0 |       |  |   |           |    |          | All<br>Resets |        |         |       |         |           |   |   |      |

|-----------|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|---|-----------|----|----------|---------------|--------|---------|-------|---------|-----------|---|---|------|

| CRCCON1   | 0640  | CRCEN  | —                                                                                                                                                                                                              | CSIDL |  | V | WORD<4:0  | )> |          | CRCFUL        | CRCMPT | CRCISEL | CRCGO | LENDIAN | _         | _ | — | 0000 |

| CRCCON2   | 0642  |        | _                                                                                                                                                                                                              | _     |  | D | WIDTH<4:0 | )> |          | _             |        | _       |       | F       | PLEN<4:0> |   |   | 0000 |

| CRCXORL   | 0644  |        | X<15:1>0                                                                                                                                                                                                       |       |  |   |           |    |          |               | 0000   |         |       |         |           |   |   |      |

| CRCXORH   | 0646  |        |                                                                                                                                                                                                                |       |  |   |           |    | X·       | <31:16>       |        |         |       |         |           |   |   | 0000 |

| CRCDATL   | 0648  |        |                                                                                                                                                                                                                |       |  |   |           |    | CRC Data | Input Low V   | Vord   |         |       |         |           |   |   | 0000 |

| CRCDATH   | 064A  |        | CRC Data Input High Word                                                                                                                                                                                       |       |  |   |           |    |          |               | 0000   |         |       |         |           |   |   |      |

| CRCWDATL  | 064C  |        | CRC Result Low Word 0                                                                                                                                                                                          |       |  |   |           |    |          |               | 0000   |         |       |         |           |   |   |      |

| CRCWDATH  | 064E  |        | CRC Result High Word 00                                                                                                                                                                                        |       |  |   |           |    |          |               | 0000   |         |       |         |           |   |   |      |

Legend: — = unimplemented, read as '0'. Shaded bits are not used in the operation of the programmable CRC module.

# TABLE 4-25: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC202/502 AND PIC24EPXXXGP/MC202 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5         | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|------------|--------|--------|-------|-------|-------|------------|---------------|-------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  | —      | —      |        | RP35R<5:0> |        |        |       |       | _     | _          | RP20R<5:0>    |       |       |        |       |       |               |

| RPOR1        | 0682  | _      | _      |        | RP37R<5:0> |        |        |       |       | _     | Ι          | RP36R<5:0> 00 |       |       |        |       |       | 0000          |

| RPOR2        | 0684  | _      | _      |        | RP39R<5:0> |        |        |       | _     | Ι     | RP38R<5:0> |               |       |       |        | 0000  |       |               |

| RPOR3        | 0686  | _      | _      |        | RP41R<5:0> |        |        |       |       | _     | Ι          | RP40R<5:0>    |       |       |        |       | 0000  |               |

| RPOR4        | 0688  | _      | _      |        | RP43R<5:0> |        |        |       |       | —     | _          |               |       | RP42F | R<5:0> |       |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-26: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC203/503 AND PIC24EPXXXGP/MC203 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5      | Bit 4      | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|------------|------------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  |        | —      |        |        | RP35F  | R<5:0> |       |       | _     | _     |            | RP20R<5:0> |       |        |       |       |               |

| RPOR1        | 0682  | _      | _      |        |        | RP37F  | ۲<5:0> |       |       | _     | _     |            |            | RP36F | २<5:0> |       |       | 0000          |

| RPOR2        | 0684  | _      | _      |        |        | RP39F  | २<5:0> |       |       | _     | —     |            |            | RP38F | R<5:0> |       |       | 0000          |

| RPOR3        | 0686  | _      | _      |        |        | RP41F  | २<5:0> |       |       | _     | —     |            |            | RP40F | R<5:0> |       |       | 0000          |

| RPOR4        | 0688  | _      | _      |        |        | RP43F  | ۲<5:0> |       |       | _     | _     | RP42R<5:0> |            |       |        | 0000  |       |               |

| RPOR5        | 068A  | _      | _      | _      | _      | _      | _      |       | _     | _     | _     | _          | _          | _     | _      |       |       | 0000          |

| RPOR6        | 068C  | _      | —      | —      | _      | _      | _      | _     | —     | _     | —     |            |            | RP56F | R<5:0> |       |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

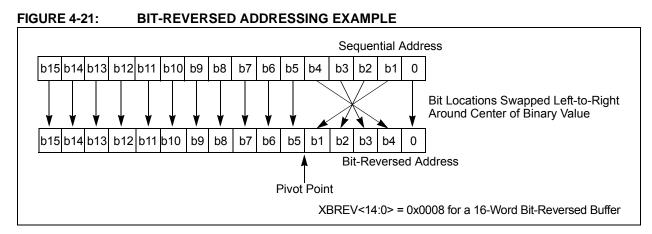

#### TABLE 4-64: BIT-REVERSED ADDRESSING SEQUENCE (16-ENTRY)

|    | Normal Address |    |    |         |    |    | Bit-Rev | ersed Ac | ldress  |

|----|----------------|----|----|---------|----|----|---------|----------|---------|

| A3 | A2             | A1 | A0 | Decimal | A3 | A2 | A1      | A0       | Decimal |

| 0  | 0              | 0  | 0  | 0       | 0  | 0  | 0       | 0        | 0       |

| 0  | 0              | 0  | 1  | 1       | 1  | 0  | 0       | 0        | 8       |

| 0  | 0              | 1  | 0  | 2       | 0  | 1  | 0       | 0        | 4       |

| 0  | 0              | 1  | 1  | 3       | 1  | 1  | 0       | 0        | 12      |

| 0  | 1              | 0  | 0  | 4       | 0  | 0  | 1       | 0        | 2       |

| 0  | 1              | 0  | 1  | 5       | 1  | 0  | 1       | 0        | 10      |

| 0  | 1              | 1  | 0  | 6       | 0  | 1  | 1       | 0        | 6       |

| 0  | 1              | 1  | 1  | 7       | 1  | 1  | 1       | 0        | 14      |

| 1  | 0              | 0  | 0  | 8       | 0  | 0  | 0       | 1        | 1       |

| 1  | 0              | 0  | 1  | 9       | 1  | 0  | 0       | 1        | 9       |

| 1  | 0              | 1  | 0  | 10      | 0  | 1  | 0       | 1        | 5       |

| 1  | 0              | 1  | 1  | 11      | 1  | 1  | 0       | 1        | 13      |

| 1  | 1              | 0  | 0  | 12      | 0  | 0  | 1       | 1        | 3       |

| 1  | 1              | 0  | 1  | 13      | 1  | 0  | 1       | 1        | 11      |

| 1  | 1              | 1  | 0  | 14      | 0  | 1  | 1       | 1        | 7       |

| 1  | 1              | 1  | 1  | 15      | 1  | 1  | 1       | 1        | 15      |

In addition, DMA transfers can be triggered by timers as well as external interrupts. Each DMA channel is unidirectional. Two DMA channels must be allocated to read and write to a peripheral. If more than one channel receives a request to transfer data, a simple fixed priority scheme based on channel number, dictates which channel completes the transfer and which channel, or channels, are left pending. Each DMA channel moves a block of data, after which, it generates an interrupt to the CPU to indicate that the block is available for processing.

The DMA Controller provides these functional capabilities:

- Four DMA channels

- Register Indirect with Post-Increment Addressing mode

- Register Indirect without Post-Increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU interrupt after half or full block transfer complete

- Byte or word transfers

- · Fixed priority channel arbitration

- Manual (software) or automatic (peripheral DMA requests) transfer initiation

- One-Shot or Auto-Repeat Block Transfer modes

- Ping-Pong mode (automatic switch between two SRAM start addresses after each block transfer is complete)

- DMA request for each channel can be selected from any supported interrupt source

- Debug support features

The peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |

|-------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| INT0 – External Interrupt 0   | 00000000                             | _                                                       | _                                                      |

| IC1 – Input Capture 1         | 0000001                              | 0x0144 (IC1BUF)                                         | —                                                      |

| IC2 – Input Capture 2         | 00000101                             | 0x014C (IC2BUF)                                         | —                                                      |

| IC3 – Input Capture 3         | 00100101                             | 0x0154 (IC3BUF)                                         | —                                                      |

| IC4 – Input Capture 4         | 00100110                             | 0x015C (IC4BUF)                                         | —                                                      |

| OC1 – Output Compare 1        | 0000010                              | _                                                       | 0x0906 (OC1R)<br>0x0904 (OC1RS)                        |

| OC2 – Output Compare 2        | 00000110                             | _                                                       | 0x0910 (OC2R)<br>0x090E (OC2RS)                        |

| OC3 – Output Compare 3        | 00011001                             | _                                                       | 0x091A (OC3R)<br>0x0918 (OC3RS)                        |

| OC4 – Output Compare 4        | 00011010                             | —                                                       | 0x0924 (OC4R)<br>0x0922 (OC4RS)                        |

| TMR2 – Timer2                 | 00000111                             | _                                                       | _                                                      |

| TMR3 – Timer3                 | 00001000                             | —                                                       | _                                                      |

| TMR4 – Timer4                 | 00011011                             | —                                                       | _                                                      |

| TMR5 – Timer5                 | 00011100                             | —                                                       | —                                                      |

| SPI1 Transfer Done            | 00001010                             | 0x0248 (SPI1BUF)                                        | 0x0248 (SPI1BUF)                                       |

| SPI2 Transfer Done            | 00100001                             | 0x0268 (SPI2BUF)                                        | 0x0268 (SPI2BUF)                                       |

| UART1RX – UART1 Receiver      | 00001011                             | 0x0226 (U1RXREG)                                        | —                                                      |

| UART1TX – UART1 Transmitter   | 00001100                             | —                                                       | 0x0224 (U1TXREG)                                       |

| UART2RX – UART2 Receiver      | 00011110                             | 0x0236 (U2RXREG)                                        |                                                        |

| UART2TX – UART2 Transmitter   | 00011111                             | —                                                       | 0x0234 (U2TXREG)                                       |

| ECAN1 – RX Data Ready         | 00100010                             | 0x0440 (C1RXD)                                          | _                                                      |

| ECAN1 – TX Data Request       | 01000110                             | —                                                       | 0x0442 (C1TXD)                                         |

| ADC1 – ADC1 Convert Done      | 00001101                             | 0x0300 (ADC1BUF0)                                       | —                                                      |

#### TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

#### 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the powersaving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the ECAN<sup>™</sup> module has been configured for 500 kbps, based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the ECAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

#### 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

| Note: | If a PMD bit is set, the corresponding        |

|-------|-----------------------------------------------|

|       | module is disabled after a delay of one       |

|       | instruction cycle. Similarly, if a PMD bit is |

|       | cleared, the corresponding module is          |

|       | enabled after a delay of one instruction      |

|       | cycle (assuming the module control regis-     |

|       | ters are already configured to enable         |

|       | module operation).                            |

#### 10.5 Power-Saving Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

#### 10.5.1 KEY RESOURCES

- "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER     | <u>R 10-2: PMD</u> 2 | 2: PERIPHER                                         | AL MODULE       | DISABLE C         | ONTROL RE       | GISTER 2        |       |  |  |

|--------------|----------------------|-----------------------------------------------------|-----------------|-------------------|-----------------|-----------------|-------|--|--|

| U-0          | U-0                  | U-0                                                 | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |

| _            |                      | —                                                   |                 | IC4MD             | IC3MD           | IC2MD           | IC1MD |  |  |

| bit 15       |                      |                                                     |                 |                   |                 |                 | bit   |  |  |

| U-0          | U-0                  | U-0                                                 | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |

|              |                      |                                                     |                 | OC4MD             | OC3MD           | OC2MD           | OC1MD |  |  |

| bit 7        |                      |                                                     |                 |                   |                 |                 | bit   |  |  |

|              |                      |                                                     |                 |                   |                 |                 |       |  |  |

| Legend:      | 1.1.1                |                                                     |                 |                   |                 |                 |       |  |  |

| R = Readab   |                      | W = Writable b                                      | Dit             | •                 | nented bit, rea |                 |       |  |  |

| -n = Value a | at POR               | '1' = Bit is set                                    |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |  |  |

| bit 15-12    | Unimplemen           | ted: Read as '0                                     | ,               |                   |                 |                 |       |  |  |

| bit 11       | -                    | t Capture 4 Mod                                     |                 |                   |                 |                 |       |  |  |

|              | •                    | ture 4 module is                                    |                 |                   |                 |                 |       |  |  |

|              | 0 = Input Cap        | oture 4 module is                                   | s enabled       |                   |                 |                 |       |  |  |

| bit 10       | IC3MD: Input         | t Capture 3 Mod                                     | ule Disable bit |                   |                 |                 |       |  |  |

|              |                      | 1 = Input Capture 3 module is disabled              |                 |                   |                 |                 |       |  |  |

|              |                      | oture 3 module is                                   |                 |                   |                 |                 |       |  |  |

| bit 9        |                      | Capture 2 Mod                                       |                 |                   |                 |                 |       |  |  |

|              |                      | oture 2 module is<br>oture 2 module is              |                 |                   |                 |                 |       |  |  |

| bit 8        | IC1MD: Input         | t Capture 1 Mod                                     | ule Disable bit |                   |                 |                 |       |  |  |

|              | 1 = Input Cap        | oture 1 module is<br>oture 1 module is              | s disabled      |                   |                 |                 |       |  |  |

| bit 7-4      |                      | ted: Read as '0                                     |                 |                   |                 |                 |       |  |  |

| bit 3        | OC4MD: Out           | put Compare 4                                       | Module Disable  | e bit             |                 |                 |       |  |  |

|              |                      | ompare 4 modul                                      |                 |                   |                 |                 |       |  |  |

|              | -                    | ompare 4 modu                                       |                 |                   |                 |                 |       |  |  |

| bit 2        |                      | put Compare 3                                       |                 | e bit             |                 |                 |       |  |  |

|              | •                    | ompare 3 modul                                      |                 |                   |                 |                 |       |  |  |

| L:1 4        | -                    | ompare 3 modul                                      |                 | . h.:4            |                 |                 |       |  |  |

| bit 1        |                      | put Compare 2                                       |                 |                   |                 |                 |       |  |  |

|              | $\perp$ – Output Co  | ompare 2 modu                                       |                 |                   |                 |                 |       |  |  |

|              | 0 = Output Co        | ompare 2 modul                                      | le is enabled   |                   |                 |                 |       |  |  |

| bit 0        | •                    | ompare 2 modul<br>put Compare 1                     |                 | e bit             |                 |                 |       |  |  |

| bit 0        | OC1MD: Out           | ompare 2 modul<br>put Compare 1 l<br>ompare 1 modul | Module Disable  | e bit             |                 |                 |       |  |  |

#### ~

### 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.4.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

#### 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs. In comparison, some digital-only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include  $I^2C^{TM}$  and the PWM. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheralselectable pin is handled in two different ways, depending on whether an input or output is being mapped.

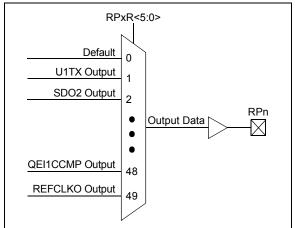

#### 11.4.4.2 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 11-18 through Register 11-27). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-3 and Figure 11-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 11-3: MULTIPLEXING REMAPPABLE OUTPUT FOR RPn

#### 11.4.4.3 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn pins is possible. This includes both many-toone and one-to-many mappings of peripheral inputs and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

#### TABLE 11-3: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

| Function                | RPxR<5:0> | Output Name                                   |

|-------------------------|-----------|-----------------------------------------------|

| Default PORT            | 000000    | RPn tied to Default Pin                       |

| U1TX                    | 000001    | RPn tied to UART1 Transmit                    |

| U2TX                    | 000011    | RPn tied to UART2 Transmit                    |

| SDO2                    | 001000    | RPn tied to SPI2 Data Output                  |

| SCK2                    | 001001    | RPn tied to SPI2 Clock Output                 |

| SS2                     | 001010    | RPn tied to SPI2 Slave Select                 |

| C1TX <sup>(2)</sup>     | 001110    | RPn tied to CAN1 Transmit                     |

| OC1                     | 010000    | RPn tied to Output Compare 1 Output           |

| OC2                     | 010001    | RPn tied to Output Compare 2 Output           |

| OC3                     | 010010    | RPn tied to Output Compare 3 Output           |

| OC4                     | 010011    | RPn tied to Output Compare 4 Output           |

| C1OUT                   | 011000    | RPn tied to Comparator Output 1               |

| C2OUT                   | 011001    | RPn tied to Comparator Output 2               |

| C3OUT                   | 011010    | RPn tied to Comparator Output 3               |

| SYNCO1 <sup>(1)</sup>   | 101101    | RPn tied to PWM Primary Time Base Sync Output |

| QEI1CCMP <sup>(1)</sup> | 101111    | RPn tied to QEI 1 Counter Comparator Output   |

| REFCLKO                 | 110001    | RPn tied to Reference Clock Output            |

| C4OUT                   | 110010    | RPn tied to Comparator Output 4               |

Note 1: This function is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This function is available in dsPIC33EPXXXGP/MC50X devices only.

### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 11-26: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|---------|-------|-------|

| —      | —   |       |       | RP118 | 3R<5:0> |       |       |

| bit 15 |     |       |       |       |         |       | bit 8 |

|        |     |       |       |       |         |       |       |

| U-0    | U-0 | U-0   | U-0   | U-0   | U-0     | U-0   | U-0   |

| —      | —   |       | —     | _     | _       | —     | _     |

| bit 7  |     |       |       |       |         |       | bit 0 |

|        |     |       |       |       |         |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP118R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP118 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 11-27: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|---------|-------|-------|

| —     | —   |       |       | RP120 | )R<5:0> |       |       |

| bit 7 |     |       |       |       |         |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **RP120R<5:0>:** Peripheral Output Function is Assigned to RP120 Output Pin bits (see Table 11-3 for peripheral function numbers)

#### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER (CONTINUED)

| bit 6-4 | SYNCSRC<2:0>: Synchronous Source Selection bits <sup>(1)</sup><br>111 = Reserved<br>100 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-0 | 100 = Reserved<br>011 = PTGO17 <sup>(2)</sup><br>010 = PTGO16 <sup>(2)</sup><br>001 = Reserved<br>000 = SYNCI1 input from PPS<br>SEVTPS<3:0>: PWMx Special Event Trigger Output Postscaler Select bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1111 = 1:16 Postscaler generates Special Event Trigger on every sixteenth compare match event</li> <li>.</li> <l< td=""></l<></ul> |

|         | 0000 = 1:1 Postscaler generates Special Event Trigger on every second compare match event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

- **Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

#### 18.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\frac{1}{SSx}$ .

| Note: | This   | insures    | that  | the       | first | fr | ame |

|-------|--------|------------|-------|-----------|-------|----|-----|

|       | transr | nission    | after | initializ | ation | is | not |

|       | shifte | d or corru | pted. |           |       |    |     |

- 2. In Non-Framed 3-Wire mode, (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = 0, always place a pull-down resistor on SSx.

- **Note:** This will insure that during power-up and initialization the master/slave will not lose Sync due to an errant SCKx transition that would cause the slave to accumulate data shift errors for both transmit and receive appearing as corrupted data.

- FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame Sync pulse is active on the SSx pin, which indicates the start of a data frame.

- Note: Not all third-party devices support Frame mode timing. Refer to the SPIx specifications in Section 30.0 "Electrical Characteristics" for details.

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPIx data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

To avoid invalid slave read data to the master, the user's master software must ensure enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF Transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPIx Shift register and is empty once the data transmission begins.

#### 18.2 SPI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 18.2.1 KEY RESOURCES

- "Serial Peripheral Interface (SPI)" (DS70569) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- SPRE<2:0>: Secondary Prescale bits (Master mode)<sup>(3)</sup> bit 4-2 111 = Secondary prescale 1:1 110 = Secondary prescale 2:1 000 = Secondary prescale 8:1 bit 1-0 PPRE<1:0>: Primary Prescale bits (Master mode)<sup>(3)</sup> 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- Note 1: The CKE bit is not used in Framed SPI modes. Program this bit to '0' for Framed SPI modes (FRMEN = 1).

- 2: This bit must be cleared when FRMEN = 1.

- 3: Do not set both primary and secondary prescalers to the value of 1:1.

| R/W-0         | R/W-0                                                                                       | R/W-0                                                                                                                                                                                  | R/W-0                                                                                                                                     | R/W-0                                                                                    | R/W-0                                 | R/W-0           | R/W-0 |

|---------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------|-----------------|-------|

| ITRIM5        | ITRIM4                                                                                      | ITRIM3                                                                                                                                                                                 | ITRIM2                                                                                                                                    | ITRIM1                                                                                   | ITRIM0                                | IRNG1           | IRNG0 |

| bit 15        |                                                                                             |                                                                                                                                                                                        |                                                                                                                                           |                                                                                          |                                       |                 | bit   |

|               |                                                                                             |                                                                                                                                                                                        |                                                                                                                                           |                                                                                          |                                       |                 |       |

| U-0           | U-0                                                                                         | U-0                                                                                                                                                                                    | U-0                                                                                                                                       | U-0                                                                                      | U-0                                   | U-0             | U-0   |

|               |                                                                                             |                                                                                                                                                                                        | _                                                                                                                                         |                                                                                          | _                                     | _               | _     |

| bit 7         |                                                                                             |                                                                                                                                                                                        |                                                                                                                                           |                                                                                          |                                       |                 | bit   |

| Legend:       |                                                                                             |                                                                                                                                                                                        |                                                                                                                                           |                                                                                          |                                       |                 |       |

| R = Readabl   | e bit                                                                                       | W = Writable                                                                                                                                                                           | bit                                                                                                                                       | U = Unimplem                                                                             | nented bit, read                      | 1 as '0'        |       |

| -n = Value at | POR                                                                                         | '1' = Bit is set                                                                                                                                                                       |                                                                                                                                           | '0' = Bit is clea                                                                        |                                       | x = Bit is unkr | nown  |

|               |                                                                                             |                                                                                                                                                                                        |                                                                                                                                           |                                                                                          |                                       |                 |       |

|               | 011110 = Ma<br>•                                                                            | ximum positive                                                                                                                                                                         | e change from                                                                                                                             |                                                                                          | 1 + 00 /0                             |                 |       |

|               | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | nimum positive<br>nimum positive<br>minal current c<br>nimum negative                                                                                                                  | change from r<br>change from r<br>output specified<br>e change from                                                                       | nominal current<br>nominal current<br>l by IRNG<1:0><br>nominal curren<br>nominal curren | + 4%<br>+ 2%<br>t – 2%                |                 |       |

|               | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                          | nimum positive<br>nimum positive<br>minal current o<br>nimum negative<br>nimum negative<br>ximum negative                                                                              | change from r<br>change from r<br>output specified<br>e change from<br>e change from                                                      | nominal current<br>nominal current<br>l by IRNG<1:0><br>nominal curren                   | + 4%<br>+ 2%<br>-<br>t – 2%<br>t – 4% |                 |       |

| bit 9-8       | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                          | nimum positive<br>nimum positive<br>minal current o<br>nimum negative<br>nimum negative<br>ximum negative<br>current Source<br>ase Current <sup>(2)</sup><br>se Current <sup>(2)</sup> | change from r<br>change from r<br>output specified<br>e change from<br>e change from<br>ve change from<br>e change from<br>a Range Select | nominal current<br>nominal current<br>l by IRNG<1:0><br>nominal curren<br>nominal curren | + 4%<br>+ 2%<br>-<br>t – 2%<br>t – 4% |                 |       |

#### REGISTER 22-3: CTMUICON: CTMU CURRENT CONTROL REGISTER

2: Refer to the CTMU Current Source Specifications (Table 30-56) in Section 30.0 "Electrical Characteristics" for the current range selection values.

Most instructions are a single word. Certain double-word instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it executes as a NOP.

The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the Program Counter is changed as a result of the instruction, or a PSV or Table Read is performed, or an SFR register is read. In these cases, the execution takes multiple instruction cycles with the additional instruction cycle(s) executed as a NOP. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

Note: For more details on the instruction set, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157). For more information on instructions that take more than one instruction cycle to execute, refer to **"CPU"** (DS70359) in the *"dsPIC33/PIC24 Family Reference Manual"*, particularly the **"Instruction Flow Types"** section.

| Field               | Description                                                                          |

|---------------------|--------------------------------------------------------------------------------------|

| #text               | Means literal defined by "text"                                                      |

| (text)              | Means "content of text"                                                              |

| [text]              | Means "the location addressed by text"                                               |

| {}                  | Optional field or operation                                                          |

| $a \in \{b, c, d\}$ | a is selected from the set of values b, c, d                                         |

| <n:m></n:m>         | Register bit field                                                                   |

| .b                  | Byte mode selection                                                                  |

| .d                  | Double-Word mode selection                                                           |

| .S                  | Shadow register select                                                               |

| .w                  | Word mode selection (default)                                                        |

| Acc                 | One of two accumulators {A, B}                                                       |

| AWB                 | Accumulator write back destination address register ∈ {W13, [W13]+ = 2}              |

| bit4                | 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$        |

| C, DC, N, OV, Z     | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                 |

| Expr                | Absolute address, label or expression (resolved by the linker)                       |

| f                   | File register address ∈ {0x00000x1FFF}                                               |

| lit1                | 1-bit unsigned literal $\in \{0,1\}$                                                 |

| lit4                | 4-bit unsigned literal ∈ {015}                                                       |

| lit5                | 5-bit unsigned literal ∈ {031}                                                       |

| lit8                | 8-bit unsigned literal ∈ {0255}                                                      |

| lit10               | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode               |

| lit14               | 14-bit unsigned literal ∈ {016384}                                                   |

| lit16               | 16-bit unsigned literal ∈ {065535}                                                   |

| lit23               | 23-bit unsigned literal ∈ {08388608}; LSb must be '0'                                |

| None                | Field does not require an entry, can be blank                                        |

| OA, OB, SA, SB      | DSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate          |

| PC                  | Program Counter                                                                      |

| Slit10              | 10-bit signed literal ∈ {-512511}                                                    |

| Slit16              | 16-bit signed literal ∈ {-3276832767}                                                |

| Slit6               | 6-bit signed literal ∈ {-1616}                                                       |

| Wb                  | Base W register ∈ {W0W15}                                                            |

| Wd                  | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                    |

| Wdo                 | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |

#### TABLE 28-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

| DC CHARACTERISTICS |                       | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |        |                     |            |      |                                                                |

|--------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------|------------|------|----------------------------------------------------------------|

| Param<br>No.       | Symbol Characteristic |                                                                                                                                                                                                      |        | Тур. <sup>(1)</sup> | Conditions |      |                                                                |

|                    |                       | Program Flash Memory                                                                                                                                                                                 |        |                     |            |      |                                                                |

| D130               | Eр                    | Cell Endurance                                                                                                                                                                                       | 10,000 | —                   | _          | E/W  | -40°C to +125°C                                                |

| D131               | Vpr                   | VDD for Read                                                                                                                                                                                         | 3.0    | —                   | 3.6        | V    |                                                                |

| D132b              | VPEW                  | VDD for Self-Timed Write                                                                                                                                                                             | 3.0    | —                   | 3.6        | V    |                                                                |

| D134               | TRETD                 | Characteristic Retention                                                                                                                                                                             | 20     | _                   |            | Year | Provided no other specifications are violated, -40°C to +125°C |

| D135               | IDDP                  | Supply Current during<br>Programming <sup>(2)</sup>                                                                                                                                                  | —      | 10                  |            | mA   |                                                                |

| D136               | IPEAK                 | Instantaneous Peak Current<br>During Start-up                                                                                                                                                        | —      | —                   | 150        | mA   |                                                                |

| D137a              | TPE                   | Page Erase Time                                                                                                                                                                                      | 17.7   | —                   | 22.9       | ms   | TPE = 146893 FRC cycles,<br>TA = +85°C (See <b>Note 3)</b>     |

| D137b              | Тре                   | Page Erase Time                                                                                                                                                                                      | 17.5   | —                   | 23.1       | ms   | TPE = 146893 FRC cycles,<br>TA = +125°C (See <b>Note 3)</b>    |

| D138a              | Tww                   | Word Write Cycle Time                                                                                                                                                                                | 41.7   | —                   | 53.8       | μs   | Tww = 346 FRC cycles,<br>TA = +85°C (See <b>Note 3)</b>        |

| D138b              | Tww                   | Word Write Cycle Time                                                                                                                                                                                | 41.2   | —                   | 54.4       | μs   | Tww = 346 FRC cycles,<br>TA = +125°C (See <b>Note 3)</b>       |

#### TABLE 30-14: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

2: Parameter characterized but not tested in manufacturing.

3: Other conditions: FRC = 7.37 MHz, TUN<5:0> = 011111 (for Minimum), TUN<5:0> = 100000 (for Maximum). This parameter depends on the FRC accuracy (see Table 30-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). For complete details on calculating the Minimum and Maximum time, see Section 5.3 "Programming Operations".

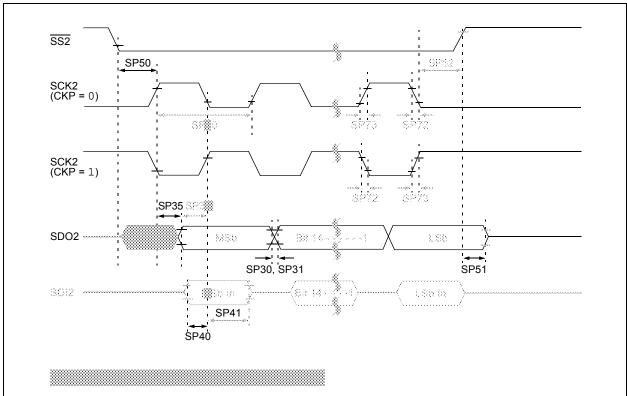

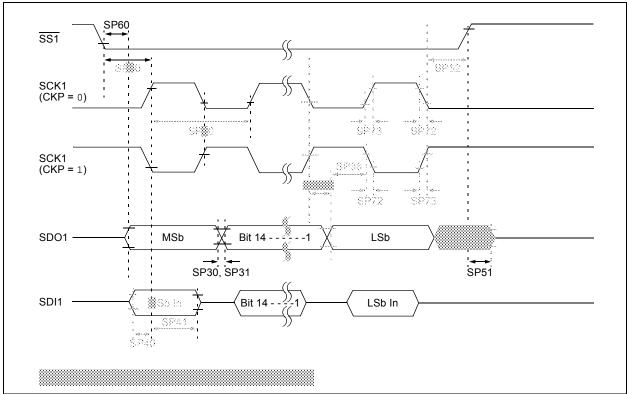

#### FIGURE 30-20: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

FIGURE 30-26: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

#### 31.1 High-Temperature DC Characteristics

#### TABLE 31-1: OPERATING MIPS VS. VOLTAGE

|                |                            |                              | Max MIPS                                                              |

|----------------|----------------------------|------------------------------|-----------------------------------------------------------------------|

| Characteristic | VDD Range<br>(in Volts)    | Temperature Range<br>(in °C) | dsPIC33EPXXXGP50X,<br>dsPIC33EPXXXMC20X/50X and<br>PIC24EPXXXGP/MC20X |

| HDC5           | 3.0 to 3.6V <sup>(1)</sup> | -40°C to +150°C              | 40                                                                    |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules, such as the ADC, may have degraded performance. Device functionality is tested but not characterized.

#### TABLE 31-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                 | Symbol | Min | Тур         | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------------|------|------|

| High-Temperature Devices                                                                                                                                                               |        |     |             |      |      |

| Operating Junction Temperature Range                                                                                                                                                   | TJ     | -40 | _           | +155 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                    | TA     | -40 | _           | +150 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     | I   | Pint + Pi/c | )    | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                      | PDMAX  | (   | TJ — TA)/θJ | IA   | W    |

#### TABLE 31-3: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |                |                | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +150^{\circ}C \end{array}$ |     |     |       |                 |  |  |  |

|--------------------|----------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|-----------------|--|--|--|

| Parameter<br>No.   | Symbol         | Characteristic | Min                                                                                                                                                                                             | Тур | Max | Units | Conditions      |  |  |  |