Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Decans                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 256КВ (85.5К х 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K × 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

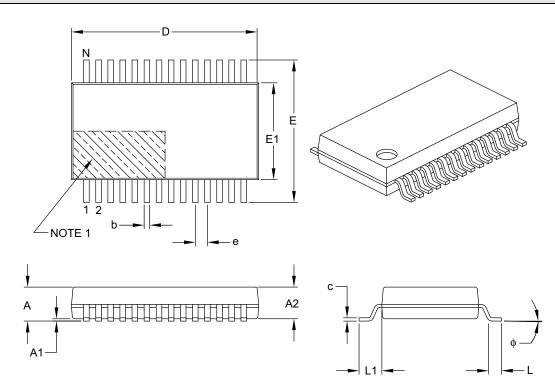

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256gp206-e-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

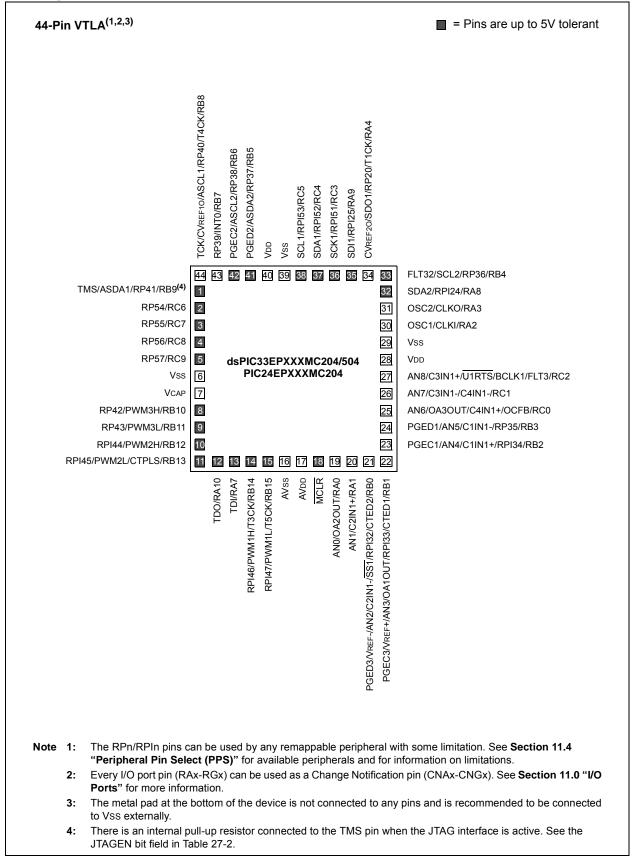

### Pin Diagrams (Continued)

| TABLE 4   | -12:     | PWM RI         | EGISTE                    | R MAP      | FOR de      | sPIC33E      | PXXXN   | AC20X/50 | DX AND F | PIC24EP | PXXXM | C20X [ | DEVICE | S ONI | _Y    |           |       |               |

|-----------|----------|----------------|---------------------------|------------|-------------|--------------|---------|----------|----------|---------|-------|--------|--------|-------|-------|-----------|-------|---------------|

| File Name | Addr.    | Bit 15         | Bit 14                    | Bit 13     | Bit 12      | Bit 11       | Bit 10  | Bit 9    | Bit 8    | Bit 7   | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1     | Bit 0 | All<br>Resets |

| PTCON     | 0C00     | PTEN           | —                         | PTSIDL     | SESTAT      | SEIEN        | EIPU    | SYNCPOL  | SYNCOEN  | SYNCEN  | SY    | NCSRC< | 2:0>   |       | SEV   | /TPS<3:0> |       | 0000          |

| PTCON2    | 0C02     | _              | PCLKDIV<2:0> 000          |            |             |              |         |          |          |         |       | 0000   |        |       |       |           |       |               |

| PTPER     | 0C04     |                | PTPER<15:0> 00F8          |            |             |              |         |          |          |         |       | 00F8   |        |       |       |           |       |               |

| SEVTCMP   | 0C06     |                |                           |            |             |              |         |          | SEVTCMP< | 5:0>    |       |        |        |       |       |           |       | 0000          |

| MDC       | 0C0A     |                |                           |            |             |              |         |          | MDC<15:  | )>      |       |        |        |       |       |           |       | 0000          |

| CHOP      | 0C1A     | CHPCLKEN       | HPCLKEN CHOPCLK<9:0> 0000 |            |             |              |         |          |          |         |       |        |        |       |       |           |       |               |

| PWMKEY    | 0C1E     |                | PWMKEY<15:0> 0000         |            |             |              |         |          |          |         |       |        |        |       |       |           |       |               |

| Legend: - | – = unir | mplemented, re | ead as '0'.               | Reset valu | es are show | vn in hexade | ecimal. |          |          |         |       |        |        |       |       |           |       |               |

## TABLE 4-13: PWM GENERATOR 1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

|           | 10.   |         |        |         |                                                                             |          | I OIT U |       |           |          |       | 1102-   |       |       |          |       |        |               |

|-----------|-------|---------|--------|---------|-----------------------------------------------------------------------------|----------|---------|-------|-----------|----------|-------|---------|-------|-------|----------|-------|--------|---------------|

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12                                                                      | Bit 11   | Bit 10  | Bit 9 | Bit 8     | Bit 7    | Bit 6 | Bit 5   | Bit 4 | Bit 3 | Bit 2    | Bit 1 | Bit 0  | All<br>Resets |

| PWMCON1   | 0C20  | FLTSTAT | CLSTAT | TRGSTAT | FLTIEN                                                                      | CLIEN    | TRGIEN  | ITB   | MDCS      | DTC<     | :1:0> | DTCP    | _     | MTBS  | CAM      | XPRES | IUE    | 0000          |

| IOCON1    | 0C22  | PENH    | PENL   | POLH    | DLH POLL PMOD<1:0> OVRENH OVRENL OVRDAT<1:0> FLTDAT<1:0> CLDAT<1:0> SWAP OS |          |         |       |           |          | OSYNC | C000    |       |       |          |       |        |               |

| FCLCON1   | 0C24  | _       |        | (       | CLSRC<4:                                                                    | 0>       |         | CLPOL | CLMOD     |          | FL    | TSRC<4: | )>    |       | FLTPOL   | FLTMO | D<1:0> | 0000          |

| PDC1      | 0C26  |         |        |         | PDC1<15:0>                                                                  |          |         |       |           |          |       | FFF8    |       |       |          |       |        |               |

| PHASE1    | 0C28  |         |        |         | PHASE1<15:0>                                                                |          |         |       |           |          |       | 0000    |       |       |          |       |        |               |

| DTR1      | 0C2A  | _       | _      |         |                                                                             |          |         |       |           | DTR1<13: | 0>    |         |       |       |          |       |        | 0000          |

| ALTDTR1   | 0C2C  | _       | _      |         |                                                                             |          |         |       | А         | LTDTR1<1 | 3:0>  |         |       |       |          |       |        | 0000          |

| TRIG1     | 0C32  |         |        |         |                                                                             |          |         |       | TRGCMP<18 | 5:0>     |       |         |       |       |          |       |        | 0000          |

| TRGCON1   | 0C34  |         | TRGDI  | V<3:0>  |                                                                             | _        | _       | _     | _         | _        | _     |         |       | TRG   | STRT<5:0 | >     |        | 0000          |

| LEBCON1   | 0C3A  | PHR     | PHF    | PLR     | PLF                                                                         | FLTLEBEN | CLLEBEN | _     | _         | _        | _     | BCH     | BCL   | BPHH  | BPHL     | BPLH  | BPLL   | 0000          |

| LEBDLY1   | 0C3C  | _       | _      | —       | LEB<11:0>                                                                   |          |         |       |           |          |       |         | 0000  |       |          |       |        |               |

| AUXCON1   | 0C3E  | —       | —      | _       | BLANKSEL<3:0> CHOPSEL<3:0> CHOPHEN CHOPLEN                                  |          |         |       |           |          |       | 0000    |       |       |          |       |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-41: PMD REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | —      | —      | _      | CMPMD  | _      | _      | CRCMD  | _     | —     | _      | —      | —      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      |        | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      | PWM3MD | PWM2MD | PWM1MD | _      | _     | _     | _      | _      | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| PIVID7       | 0760  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

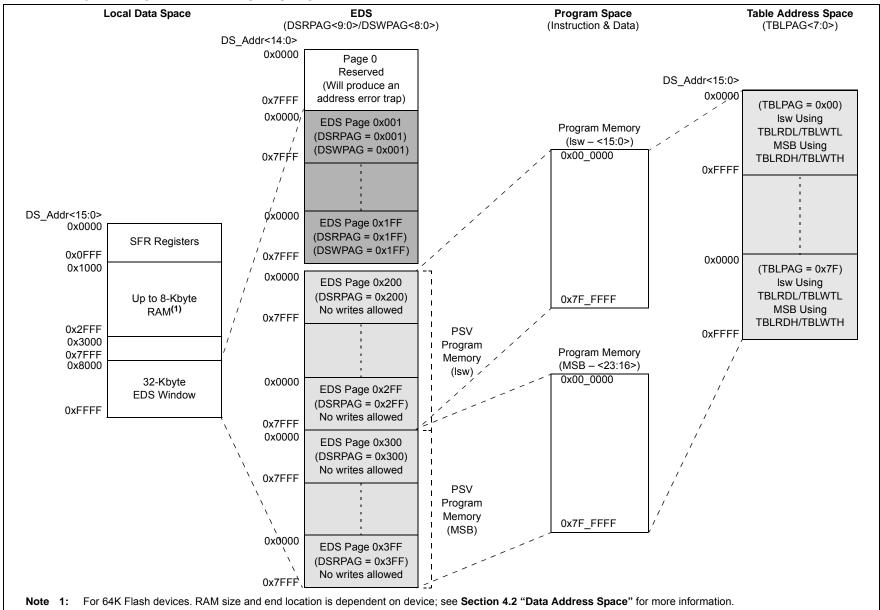

### EXAMPLE 4-3: PAGED DATA MEMORY SPACE

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0                                                                                          | U-0                                                                                                                                                                     | U-0                                                                             | R-0               | R-0              | R-0             | R-0     |

|-----------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------|------------------|-----------------|---------|

|                 | —                                                                                            |                                                                                                                                                                         |                                                                                 | ILR3              | ILR2             | ILR1            | ILR0    |

| bit 15          |                                                                                              |                                                                                                                                                                         |                                                                                 |                   |                  |                 | bit 8   |

| R-0             | R-0                                                                                          | R-0                                                                                                                                                                     | R-0                                                                             | R-0               | R-0              | R-0             | R-0     |

| VECNUM7         | VECNUM6                                                                                      | VECNUM5                                                                                                                                                                 | VECNUM4                                                                         | VECNUM3           | VECNUM2          | VECNUM1         | VECNUM0 |

| bit 7           |                                                                                              |                                                                                                                                                                         |                                                                                 |                   |                  |                 | bit C   |

| Legend:         |                                                                                              |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |

| R = Readable    | bit                                                                                          | W = Writable                                                                                                                                                            | bit                                                                             | U = Unimplen      | nented bit, read | as '0'          |         |

| -n = Value at I | POR                                                                                          | '1' = Bit is set                                                                                                                                                        |                                                                                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |

| bit 15-12       | Unimplemen                                                                                   | ted: Read as '                                                                                                                                                          | 0'                                                                              |                   |                  |                 |         |

| bit 11-8        | -                                                                                            | w CPU Interru                                                                                                                                                           |                                                                                 | el bits           |                  |                 |         |

|                 |                                                                                              | Interrupt Priorit                                                                                                                                                       | -                                                                               |                   |                  |                 |         |

|                 | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |

|                 | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |

|                 |                                                                                              | Interrupt Priorif<br>Interrupt Priorif                                                                                                                                  |                                                                                 |                   |                  |                 |         |

| bit 7-0         | VECNUM<7:0                                                                                   | >: Vector Nun                                                                                                                                                           | nber of Pendin                                                                  | g Interrupt bits  |                  |                 |         |

|                 | 11111111 = 2                                                                                 | 255, Reserved                                                                                                                                                           | ; do not use                                                                    |                   |                  |                 |         |

|                 | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |

|                 | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |

|                 | 00001000 = 8<br>00000111 = 7<br>00000110 = 8<br>00000101 = 8<br>00000100 = 7<br>00000011 = 3 | 9, IC1 – Input (<br>8, INT0 – Exter<br>7, Reserved; d<br>6, Generic soft<br>5, DMAC error<br>4, Math error tr<br>3, Stack error t<br>2, Generic hard<br>1, Address erro | rnal Interrupt C<br>o not use<br>error trap<br>trap<br>rap<br>d trap<br>or trap | )                 |                  |                 |         |

### REGISTER 7-7: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

### 10.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into Standby when Sleep mode is entered by clearing the VREGS (RCON<8>) and VREGSF (RCON<11>) bits (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) and VREGSF (RCON<11>) bits can be set to keep the internal regulator and the Flash regulator active during Sleep mode.

### 10.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- · A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the Interrupt Service Routine (ISR).

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral; for example, the TSIDL bit in the Timer1 Control register (T1CON<13>).

### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

| U-0          | U-0                 | U-0                                | U-0   | U-0              | U-0              | U-0             | U-0   |

|--------------|---------------------|------------------------------------|-------|------------------|------------------|-----------------|-------|

| —            | —                   | —                                  | _     | —                | —                | —               | _     |

| bit 15       |                     |                                    |       |                  |                  |                 | bit 8 |

|              |                     |                                    |       |                  |                  |                 |       |

| U-0          | R/W-0               | R/W-0                              | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| —            |                     |                                    |       | INT2R<6:0>       |                  |                 |       |

| bit 7        |                     |                                    |       |                  |                  |                 | bit 0 |

|              |                     |                                    |       |                  |                  |                 |       |

| Legend:      |                     |                                    |       |                  |                  |                 |       |

| R = Readal   | ole bit             | W = Writable                       | bit   | U = Unimpler     | mented bit, read | as '0'          |       |

| -n = Value a | at POR              | '1' = Bit is set                   |       | '0' = Bit is cle | ared             | x = Bit is unkr | iown  |

|              |                     |                                    |       |                  |                  |                 |       |

| bit 15-7     | Unimplemen          | ted: Read as 'd                    | )'    |                  |                  |                 |       |

| bit 6-0      |                     | Assign Externa<br>-2 for input pin |       |                  | orresponding RI  | Pn Pin bits     |       |

|              | 1111001 <b>= lr</b> | put tied to RPI                    | 121   |                  |                  |                 |       |

|              |                     |                                    |       |                  |                  |                 |       |

|              |                     |                                    |       |                  |                  |                 |       |

|              | 0000001 – Ir        | put tied to CMI                    | ⊃1    |                  |                  |                 |       |

|              |                     | put tied to Civil                  |       |                  |                  |                 |       |

|              |                     |                                    |       |                  |                  |                 |       |

|              |                     |                                    |       |                  |                  |                 |       |

### REGISTER 11-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

### REGISTER 11-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0<br>— T2CKR<6:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |                     |                  |       |                  |                  |                 |       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------|------------------|-------|------------------|------------------|-----------------|-------|

| U-0       R/W-0       R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0          | U-0                 | U-0              | U-0   | U-0              | U-0              | U-0             | U-0   |

| U-0       R/W-0       R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _            | -                   | —                | _     | —                | —                | —               | —     |

| —       T2CKR<6:0>         bit 7       t         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 15       |                     |                  |       |                  |                  |                 | bit 8 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                  |                  |                 |       |

| bit 7       Image: Constraint of the system of | U-0          | R/W-0               | R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . <td< td=""><td>—</td><td></td><td></td><td></td><td>T2CKR&lt;6:0&gt;</td><td>&gt;</td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —            |                     |                  |       | T2CKR<6:0>       | >                |                 |       |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 7        |                     |                  |       |                  |                  |                 | bit 0 |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |                     |                  |       |                  |                  |                 |       |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Legend:      |                     |                  |       |                  |                  |                 |       |

| bit 15-7 Unimplemented: Read as '0'<br>bit 6-0 T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121<br>0000001 = Input tied to CMP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R = Readab   | ole bit             | W = Writable I   | bit   | U = Unimpler     | mented bit, read | as '0'          |       |

| bit 6-0 <b>T2CKR&lt;6:0&gt;:</b> Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -n = Value a | at POR              | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

| bit 6-0 <b>T2CKR&lt;6:0&gt;:</b> Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                     |                  |       |                  |                  |                 |       |

| (see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121<br>0000001 = Input tied to CMP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 15-7     | Unimplemen          | ted: Read as 'd  | )'    |                  |                  |                 |       |

| 1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 6-0      |                     | •                |       | · · ·            | he Correspondir  | ng RPn pin bits | 5     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       | ,                |                  |                 |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                  |                  |                 |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                  |                  |                 |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | 0000001 = Ir        | nout tied to CM  | ⊃1    |                  |                  |                 |       |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |                     |                  |       |                  |                  |                 |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | 0000000 <b>- II</b> | iput tied to vss |       |                  |                  |                 |       |

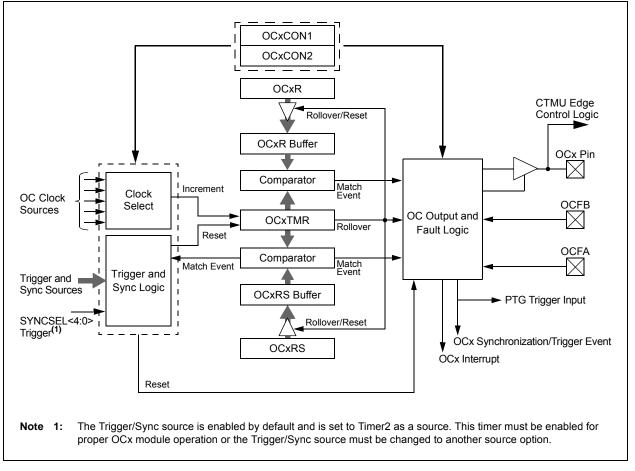

# 15.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Output Compare" (DS70358) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The output compare module can select one of seven available clock sources for its time base. The module compares the value of the timer with the value of one or two compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the compare register value. The output compare module generates either a single output pulse or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events and trigger DMA data transfers.

Note: See "Output Compare" (DS70358) in the "dsPIC33/PIC24 Family Reference Manual" for OCxR and OCxRS register restrictions.

## 17.0 QUADRATURE ENCODER INTERFACE (QEI) MODULE (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Quadrature Encoder Interface (QEI)" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This chapter describes the Quadrature Encoder Interface (QEI) module and associated operational modes. The QEI module provides the interface to incremental encoders for obtaining mechanical position data.

The operational features of the QEI module include:

- 32-Bit Position Counter

- 32-Bit Index Pulse Counter

- 32-Bit Interval Timer

- 16-Bit Velocity Counter

- 32-Bit Position Initialization/Capture/Compare High register

- 32-Bit Position Compare Low register

- x4 Quadrature Count mode

- External Up/Down Count mode

- External Gated Count mode

- External Gated Timer mode

- Internal Timer mode

Figure 17-1 illustrates the QEI block diagram.

## 17.1 QEI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this UDL increases |

|-------|---------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                                               |

|       | http://www.microchip.com/wwwproducts/                                                                   |

|       | Devices.aspx?dDocName=en555464                                                                          |

### 17.1.1 KEY RESOURCES

- "Quadrature Encoder Interface" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER (CONTINUED)

| bit 2 | <b>HOMIEN:</b> Home Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled            |

|-------|--------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IDXIRQ:</b> Status Flag for Index Event Status bit<br>1 = Index event has occurred<br>0 = No Index event has occurred |

| bit 0 | <b>IDXIEN:</b> Index Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled           |

Note 1: This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

# 19.1 I<sup>2</sup>C Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this UDL increases |

|-------|---------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                                               |

|       | http://www.microchip.com/wwwproducts/                                                                   |

|       | Devices.aspx?dDocName=en555464                                                                          |

### 19.1.1 KEY RESOURCES

- "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS70330) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| -                             |           |                 |            |                   |                  |                    |                       |  |  |

|-------------------------------|-----------|-----------------|------------|-------------------|------------------|--------------------|-----------------------|--|--|

| R-0, HSC                      | R-0, HSC  | U-0             | U-0        | U-0               | R/C-0, HS        | R-0, HSC           | R-0, HSC              |  |  |

| ACKSTAT                       | TRSTAT    | —               | —          | —                 | BCL              | GCSTAT             | ADD10                 |  |  |

| bit 15                        |           |                 |            |                   |                  |                    | bit 8                 |  |  |

|                               |           |                 |            |                   |                  |                    |                       |  |  |

| R/C-0, HS                     | R/C-0, HS | R-0, HSC        | R/C-0, HSC | R/C-0, HSC        | R-0, HSC         | R-0, HSC           | R-0, HSC              |  |  |

| IWCOL                         | I2COV     | D_A             | Р          | S                 | R_W              | RBF                | TBF                   |  |  |

| bit 7                         |           |                 |            |                   |                  |                    | bit 0                 |  |  |

|                               |           |                 |            |                   |                  |                    |                       |  |  |

| Legend:                       |           | C = Clearab     | le bit     | HS = Hardwa       | re Settable bit  | HSC = Hardware S   | ettable/Clearable bit |  |  |

| R = Readable bit W = Writable |           |                 | e bit      | U = Unimplen      | nented bit, read | as '0'             |                       |  |  |

| -n = Value at                 | t POR     | '1' = Bit is se | et         | '0' = Bit is clea | ared             | x = Bit is unknown |                       |  |  |

### REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER

| hit 15    | ACKSTAT: Acknowledge Status bit (when operating as I <sup>2</sup> C™ master, applicable to master transmit operation)                          |