Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256gp206-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

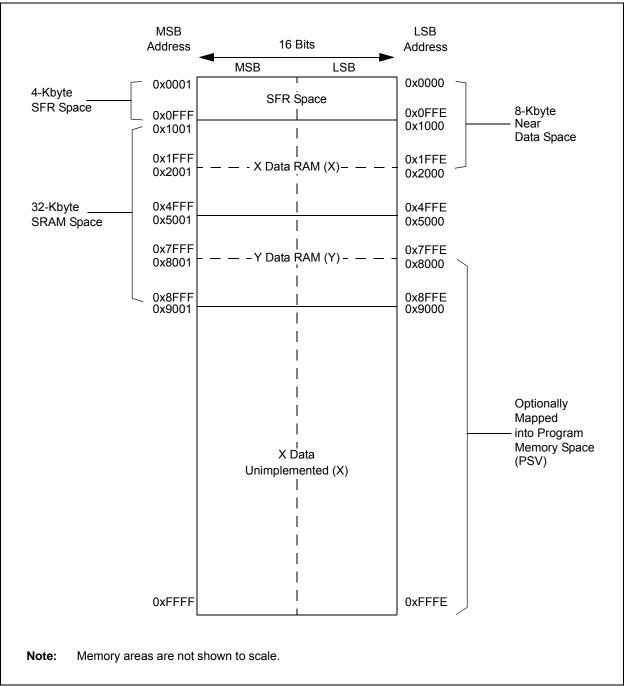

# FIGURE 4-10: DATA MEMORY MAP FOR dsPIC33EP256MC20X/50X AND dsPIC33EP256GP50X DEVICES

## TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|---------|---------|--------|-------|-------|----------|---------|---------|---------|---------|--------|---------|--------|---------------|

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR | COVAERR | COVBERR | OVATE  | OVBTE | COVTE | SFTACERR | DIV0ERR | DMACERR | MATHERR | ADDRERR | STKERR | OSCFAIL |        | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP | _       | _       | _      | _     | _     | _        | —       | _       | _       | —       | INT2EP | INT1EP  | INT0EP | 8000          |

| INTCON3      | 08C4  |        | _      | _      | —       | _       | _      |       | _     | _        | —       | DAE     | DOOVR   | —       | _      | _       |        | 0000          |

| INTCON4      | 08C6  |        | _      |        |         |         | Ι      | _     |       |          | —       | _       |         | —       |        |         | SGHT   | 0000          |

| INTTREG      | 08C8  | _      | _      | _      | _       |         | ILR<   | 3:0>  |       |          |         |         | VECNU   | M<7:0>  |        |         |        | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

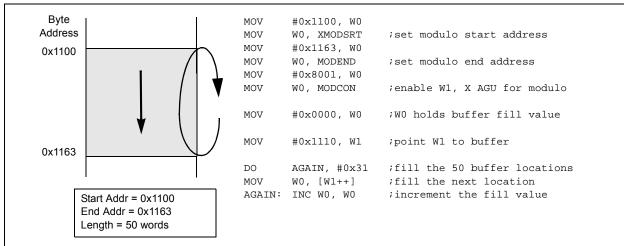

## 4.6 Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

## 4.6.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified, and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

| Note: | Y space Modulo Addressing EA calcula- |

|-------|---------------------------------------|

|       | tions assume word-sized data (LSb of  |

|       | every EA is always clear).            |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.6.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W register (YWM), to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit is set at MODCON<14>.

## FIGURE 4-20: MODULO ADDRESSING OPERATION EXAMPLE

| R/SO-0 <sup>(1</sup>         | ) R/W-0 <sup>(1)</sup>                     | R/W-0 <sup>(1)</sup>        | R/W-0                         | U-0                     | U-0                     | U-0                     | U-0                    |

|------------------------------|--------------------------------------------|-----------------------------|-------------------------------|-------------------------|-------------------------|-------------------------|------------------------|

| WR                           | WREN                                       | WRERR                       | NVMSIDL <sup>(2)</sup>        | _                       |                         | —                       |                        |

| bit 15                       | I                                          | 1                           | 1                             |                         |                         |                         | bit 8                  |

|                              |                                            |                             |                               |                         |                         |                         |                        |

| U-0                          | U-0                                        | U-0                         | U-0                           | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>   |

| _                            | —                                          | —                           | —                             | NVMOP3 <sup>(3,4)</sup> | NVMOP2 <sup>(3,4)</sup> | NVMOP1 <sup>(3,4)</sup> | NVMOP0 <sup>(3,4</sup> |

| bit 7                        |                                            |                             |                               |                         |                         |                         | bit (                  |

| lagandi                      |                                            | SO - Sottab                 | la Only hit                   |                         |                         |                         |                        |

| L <b>egend:</b><br>R = Reada | ble hit                                    | SO = Settab<br>W = Writable | -                             | II – I Inimplem         | nented bit, read        | ae 'O'                  |                        |

| -n = Value                   |                                            | '1' = Bit is se             |                               | '0' = Bit is clea       |                         | x = Bit is unkr         |                        |

|                              |                                            | 1 - Dit 13 30               |                               |                         |                         |                         | lowin                  |

| bit 15                       | WR: Write Co                               | ontrol bit(1)               |                               |                         |                         |                         |                        |

|                              |                                            |                             | ory program or                | erase operation         | on; the operatio        | n is self-timed         | and the bit is         |

|                              | cleared b                                  | y hardware o                | nce the operati               | on is complete          |                         |                         |                        |

|                              | -                                          |                             | ration is comple              | ete and inactive        | 9                       |                         |                        |

| bit 14                       | WREN: Write                                |                             | n/erase operati               | 000                     |                         |                         |                        |

|                              |                                            |                             | /erase operatio               |                         |                         |                         |                        |

| oit 13                       |                                            |                             | Error Flag bit <sup>(1)</sup> |                         |                         |                         |                        |

|                              | 1 = An impro                               | per program o               | r erase sequend               |                         | rmination has oc        | curred (bit is se       | t automatically        |

|                              |                                            | et attempt of th            | e WR bit)<br>operation com    | olotod pormally         |                         |                         |                        |

| bit 12                       |                                            |                             | le Control bit <sup>(2)</sup> | Sieteu normaliy         |                         |                         |                        |

|                              |                                            |                             | r goes into Star              | ndbv mode duri          | ina Idle mode           |                         |                        |

|                              |                                            |                             | r is active durin             |                         |                         |                         |                        |

| bit 11-4                     | Unimplemen                                 | ted: Read as                | '0'                           |                         |                         |                         |                        |

| bit 3-0                      | NVMOP<3:0>                                 | NVM Operation               | ation Select bits             | <sub>3</sub> (1,3,4)    |                         |                         |                        |

|                              | 1111 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1110 = Rese<br>1101 = Rese                 |                             |                               |                         |                         |                         |                        |

|                              | 1100 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1011 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1010 = Rese<br>0011 = Memo                 |                             | e operation                   |                         |                         |                         |                        |

|                              | 0010 = Rese                                | rved                        | -                             |                         |                         |                         |                        |

|                              |                                            |                             | ord program ope               | eration <sup>(5)</sup>  |                         |                         |                        |

|                              | 0000 <b>= Rese</b>                         | rvea                        |                               |                         |                         |                         |                        |

|                              | These bits can onl                         | -                           |                               |                         |                         |                         |                        |

|                              | If this bit is set, the (TVREG) before Fla |                             |                               |                         | d upon exiting lo       | dle mode, there         | is a delay             |

|                              | All other combinati                        |                             | •                             |                         |                         |                         |                        |

| <b>.</b> .                   |                                            |                             |                               | in ploinenteu.          |                         |                         |                        |

| 4:                           | Execution of the P                         | wrsav instruc               | tion is ianored               | while any of th         | e NVM operatio          | ns are in progr         | ess.                   |

## REGISTER 5-1: NVMCON: NONVOLATILE MEMORY (NVM) CONTROL REGISTER

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cle | ared                               | x = Bit is unkr | x = Bit is unknown |       |  |

|------------------------------------|-------|-------|------------------|------------------------------------|-----------------|--------------------|-------|--|

| R = Readable bit W = Writable bit  |       |       | bit              | U = Unimplemented bit, read as '0' |                 |                    |       |  |

| Legend:                            |       |       |                  |                                    |                 |                    |       |  |

|                                    |       |       |                  |                                    |                 |                    |       |  |

| bit 7                              |       |       |                  |                                    |                 |                    | bit C |  |

|                                    |       |       | NVMAD            | )R<23:16>                          |                 |                    |       |  |

| R/W-x                              | R/W-x | R/W-x | R/W-x            | R/W-x                              | R/W-x           | R/W-x              | R/W-x |  |

| bit 15                             |       |       |                  |                                    |                 |                    | bit 8 |  |

| _                                  | —     | —     | —                | —                                  | _               | —                  | —     |  |

| U-0                                | U-0   | U-0   | U-0              | U-0                                | U-0             | U-0                | U-0   |  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMADR<23:16>:** Nonvolatile Memory Write Address High bits Selects the upper 8 bits of the location to program or erase in program Flash memory. This register may be read or written by the user application.

#### REGISTER 5-3: NVMADRL: NONVOLATILE MEMORY ADDRESS REGISTER LOW

| R/W-x                                                           | R/W-x | R/W-x          | R/W-x           | R/W-x        | R/W-x           | R/W-x    | R/W-x |

|-----------------------------------------------------------------|-------|----------------|-----------------|--------------|-----------------|----------|-------|

|                                                                 |       |                | NVMA            | DR<15:8>     |                 |          |       |

| bit 15                                                          |       |                |                 |              |                 |          | bit 8 |

| R/W-x                                                           | R/W-x | R/W-x          | R/W-x           | R/W-x        | R/W-x           | R/W-x    | R/W-x |

|                                                                 |       |                | NVMA            | DR<7:0>      |                 |          |       |

| bit 7                                                           |       |                |                 |              |                 |          | bit 0 |

| Legend:                                                         |       |                |                 |              |                 |          |       |

| R = Readable                                                    | bit   | W = Writable b | it              | U = Unimpler | nented bit, rea | d as '0' |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit |       |                | x = Bit is unkr | nown         |                 |          |       |

bit 15-0 NVMADR<15:0>: Nonvolatile Memory Write Address Low bits

Selects the lower 16 bits of the location to program or erase in program Flash memory. This register may be read or written by the user application.

#### REGISTER 5-4: NVMKEY: NONVOLATILE MEMORY KEY

| U-0                                                                  | U-0                                                                     | U-0 | U-0  | U-0     | U-0 | U-0  | U-0   |

|----------------------------------------------------------------------|-------------------------------------------------------------------------|-----|------|---------|-----|------|-------|

| —                                                                    | —                                                                       | —   | _    | —       | —   | —    | —     |

| bit 15                                                               |                                                                         |     |      |         |     |      | bit 8 |

|                                                                      |                                                                         |     |      |         |     |      |       |

| W-0                                                                  | W-0                                                                     | W-0 | W-0  | W-0     | W-0 | W-0  | W-0   |

|                                                                      |                                                                         |     | NVMK | EY<7:0> |     |      |       |

| bit 7                                                                |                                                                         |     |      |         |     |      | bit 0 |

|                                                                      |                                                                         |     |      |         |     |      |       |

| Legend:                                                              |                                                                         |     |      |         |     |      |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                         |     |      |         |     |      |       |

| -n = Value at P                                                      | = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |     |      |         |     | nown |       |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMKEY<7:0>:** Key Register (write-only) bits

| R/W-0         | R/W-0                                     | U-0                                    | U-0           | R/W-0                 | U-0               | R/W-0            | R/W-0         |

|---------------|-------------------------------------------|----------------------------------------|---------------|-----------------------|-------------------|------------------|---------------|

| TRAPF         | R IOPUWR                                  | —                                      | _             | VREGSF                | —                 | CM               | VREGS         |

| bit 15        |                                           |                                        |               |                       |                   |                  | bit 8         |

|               |                                           | DANIO                                  | DAMO          | DAMA                  | DAMO              |                  |               |

| R/W-0         |                                           | R/W-0                                  | R/W-0         | R/W-0                 | R/W-0             | R/W-1            | R/W-1         |

| EXTR<br>bit 7 | SWR                                       | SWDTEN <sup>(2)</sup>                  | WDTO          | SLEEP                 | IDLE              | BOR              | POR           |

|               |                                           |                                        |               |                       |                   |                  | bit (         |

| Legend:       |                                           |                                        |               |                       |                   |                  |               |

| R = Reada     | able bit                                  | W = Writable I                         | oit           | U = Unimpler          | mented bit, read  | d as '0'         |               |

| -n = Value    | at POR                                    | '1' = Bit is set                       |               | '0' = Bit is cle      | ared              | x = Bit is unkı  | nown          |

|               |                                           |                                        |               |                       |                   |                  |               |

| bit 15        | •                                         | Reset Flag bit                         |               |                       |                   |                  |               |

|               |                                           | onflict Reset ha<br>onflict Reset ha   |               | d                     |                   |                  |               |

| bit 14        | •                                         | gal Opcode or                          |               |                       | et Flag bit       |                  |               |

|               |                                           | I opcode detec                         |               |                       | •                 | lized W registe  | er used as ar |

|               |                                           | Pointer caused                         |               |                       |                   |                  |               |

|               | -                                         | l opcode or Uni                        |               | egister Reset h       | as not occurred   | d                |               |

| bit 13-12     | -                                         | ted: Read as '                         |               |                       | . 1.9             |                  |               |

| bit 11        |                                           | ash Voltage Reg<br>Itage regulator i   |               |                       | p bit             |                  |               |

|               |                                           | ltage regulator (                      |               | •                     | ing Sleep         |                  |               |

| bit 10        |                                           | ted: Read as '                         | -             | ,,                    | <b>5 F</b>        |                  |               |

| bit 9         | CM: Configur                              | ation Mismatch                         | Flag bit      |                       |                   |                  |               |

|               | 1 = A Configu                             | uration Mismatc<br>uration Mismatc     | h Reset has   |                       |                   |                  |               |

| bit 8         | VREGS: Volta                              | age Regulator S                        | Standby Durir | ng Sleep bit          |                   |                  |               |

|               | •                                         | egulator is active<br>egulator goes in | •             | •                     | еер               |                  |               |

| bit 7         | EXTR: Extern                              | nal Reset (MCL                         | R) Pin bit    |                       |                   |                  |               |

|               |                                           | Clear (pin) Res<br>Clear (pin) Res     |               |                       |                   |                  |               |

| bit 6         | SWR: Softwa                               | re RESET (Instr                        | uction) Flag  | bit                   |                   |                  |               |

|               |                                           | instruction has instruction has        |               |                       |                   |                  |               |

| bit 5         | SWDTEN: So                                | oftware Enable/                        | Disable of W  | DT bit <sup>(2)</sup> |                   |                  |               |

|               | 1 = WDT is e<br>0 = WDT is di             |                                        |               |                       |                   |                  |               |

| bit 4         | WDTO: Watc                                | hdog Timer Tim                         | e-out Flag bi | it                    |                   |                  |               |

|               |                                           | e-out has occur<br>e-out has not oc    |               |                       |                   |                  |               |

| Note 1:       | All of the Reset sta<br>cause a device Re |                                        | set or cleare | d in software. S      | Setting one of th | ese bits in soft | ware does not |

| 2:            | If the FWDTEN Co<br>SWDTEN bit settir     | onfiguration bit i                     | s '1' (unprog | rammed), the V        | VDT is always e   | enabled, regard  | lless of the  |

# REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

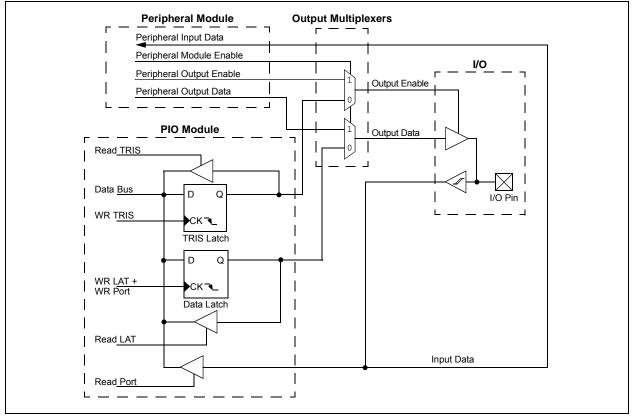

# 11.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS70598) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Many of the device pins are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

# 11.1 Parallel I/O (PIO) Ports

Generally, a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through," in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have eight registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Latch register (LATx) read the latch. Writes to the Latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device is disabled. This means the corresponding LATx and TRISx registers and the port pin are read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

## 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.4.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

#### 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs. In comparison, some digital-only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include  $I^2C^{TM}$  and the PWM. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheralselectable pin is handled in two different ways, depending on whether an input or output is being mapped.

| R/W-0      | R/W-0                                                                    | R/W-0                                                | R/W-0                           | U-0               | U-0              | U-0                    | R/W-0        |

|------------|--------------------------------------------------------------------------|------------------------------------------------------|---------------------------------|-------------------|------------------|------------------------|--------------|

| FLTMD      | FLTOUT                                                                   | FLTTRIEN                                             | OCINV                           | —                 | _                | —                      | OC32         |

| bit 15     | ·                                                                        |                                                      |                                 |                   | ·                |                        | bit          |

|            |                                                                          |                                                      |                                 |                   |                  |                        |              |

| R/W-0      | R/W-0, HS                                                                | R/W-0                                                | R/W-0                           | R/W-1             | R/W-1            | R/W-0                  | R/W-0        |

| OCTRIC     | G TRIGSTAT                                                               | OCTRIS                                               | SYNCSEL4                        | SYNCSEL3          | SYNCSEL2         | SYNCSEL1               | SYNCSEL      |

| bit 7      |                                                                          |                                                      |                                 |                   |                  |                        | bit          |

| Legend:    |                                                                          | HS = Hardwa                                          | re Settable bit                 |                   |                  |                        |              |

| R = Reada  | able bit                                                                 | W = Writable                                         | bit                             | U = Unimplem      | nented bit, read | l as '0'               |              |

| -n = Value | at POR                                                                   | '1' = Bit is set                                     |                                 | '0' = Bit is clea | ared             | x = Bit is unkn        | iown         |

|            |                                                                          |                                                      |                                 |                   |                  |                        |              |

| bit 15     | 1 = Fault mo<br>cleared i                                                | t Mode Select b<br>ode is maintain<br>n software and | ed until the Fa<br>a new PWM pe | eriod starts      |                  |                        |              |

|            |                                                                          | de is maintaine                                      | d until the Faul                | t source is rem   | loved and a ne   | w PWM period           | starts       |

| bit 14     | FLTOUT: Fau                                                              |                                                      | . –                             |                   |                  |                        |              |

|            |                                                                          | tput is driven hi<br>tput is driven lo               |                                 |                   |                  |                        |              |

| bit 13     |                                                                          | ault Output Sta                                      |                                 |                   |                  |                        |              |

|            |                                                                          | is tri-stated on                                     |                                 | 'n                |                  |                        |              |

|            | •                                                                        | I/O state is defi                                    |                                 |                   | ault condition   |                        |              |

| bit 12     | OCINV: Outp                                                              | ut Compare x I                                       | nvert bit                       |                   |                  |                        |              |

|            |                                                                          | out is inverted<br>out is not invert                 | ed                              |                   |                  |                        |              |

| bit 11-9   | Unimplemen                                                               | ted: Read as '                                       | כי                              |                   |                  |                        |              |

| bit 8      | OC32: Casca                                                              | ide Two OCx M                                        | odules Enable                   | bit (32-bit oper  | ration)          |                        |              |

|            |                                                                          | module operate module operate                        |                                 |                   |                  |                        |              |

| bit 7      |                                                                          | tput Compare x                                       |                                 | Select bit        |                  |                        |              |

|            |                                                                          | OCx from the s                                       |                                 |                   | CSELx bits       |                        |              |

|            |                                                                          | nizes OCx with                                       |                                 |                   |                  | S                      |              |

| bit 6      | TRIGSTAT: T                                                              | imer Trigger St                                      | atus bit                        |                   |                  |                        |              |

|            |                                                                          | urce has been <sup>.</sup><br>urce has not be        |                                 |                   | d clear          |                        |              |

| bit 5      |                                                                          | put Compare x                                        |                                 | •                 |                  |                        |              |

|            | 1 = OCx is tr                                                            | • •                                                  | ·                               |                   |                  |                        |              |

|            | 0 = Output C                                                             | ompare x mod                                         | ule drives the C                | OCx pin           |                  |                        |              |

| Note 1:    | Do not use the O                                                         | Cx module as i                                       | ts own Svnchro                  | nization or Tric  | aaer source.     |                        |              |

|            | When the OCy m                                                           |                                                      | -                               |                   |                  | module uses t          | he OCv       |

|            | module as a Trigg                                                        |                                                      |                                 |                   |                  |                        |              |

| 3:         | Each Output Con<br><b>"Peripheral Trig</b><br>PTGO0 = OC1<br>PTGO1 = OC2 |                                                      |                                 |                   |                  | n source. See <b>S</b> | Section 24.0 |

|            | PTGO2 = OC3 $PTGO3 = OC4$                                                |                                                      |                                 |                   |                  |                        |              |

## REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|------------------------------------|-------|-------|-------|-----------------------------------------|-------|-------|-------|--|

|                                    |       |       | INTHL | D<31:24>                                |       |       |       |  |

| bit 15                             |       |       |       |                                         |       |       | bit 8 |  |

|                                    |       |       |       |                                         |       |       |       |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|                                    |       |       | INTHL | D<23:16>                                |       |       |       |  |

| bit 7                              |       |       |       |                                         |       |       | bit 0 |  |

|                                    |       |       |       |                                         |       |       |       |  |

| Legend:                            |       |       |       |                                         |       |       |       |  |

| R = Readable bit W = Writable bit  |       |       | oit   | U = Unimplemented bit, read as '0'      |       |       |       |  |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |

bit 15-0 INTHLD<31:16>: Hold Register for Reading and Writing INT1TMRH bits

## REGISTER 17-20: INT1HLDL: INTERVAL 1 TIMER HOLD LOW WORD REGISTER

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|-----------------------------------|-------|------------------|------------------------------------|-----------------------------------------|-------|-------|-------|

|                                   |       |                  | INTHL                              | .D<15:8>                                |       |       |       |

| bit 15                            |       |                  |                                    |                                         |       |       | bit 8 |

|                                   |       |                  |                                    |                                         |       |       |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                                   |       |                  | INTH                               | _D<7:0>                                 |       |       |       |

| bit 7                             |       |                  |                                    |                                         |       |       | bit 0 |

|                                   |       |                  |                                    |                                         |       |       |       |

| Legend:                           |       |                  |                                    |                                         |       |       |       |

| R = Readable bit W = Writable bit |       |                  | U = Unimplemented bit, read as '0' |                                         |       |       |       |

| -n = Value at P                   | OR    | '1' = Bit is set |                                    | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

|                                   |       |                  |                                    |                                         |       |       |       |

bit 15-0 INTHLD<15:0>: Hold Register for Reading and Writing INT1TMRL bits

#### REGISTER 25-4: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT CONTROL REGISTER (CONTINUED)

- bit 3-0 SELSRCA<3:0>: Mask A Input Select bits

- 1111 = FLT4 1110 = FLT2 1101 = PTGO19 1100 = PTGO18 1011 = Reserved 1010 = Reserved 1001 = Reserved 1000 = Reserved 0111 = Reserved 0110 = Reserved 0101 = PWM3H 0100 = PWM3L 0011 = PWM2H 0010 = PWM2L 0001 = PWM1H 0000 = PWM1L

# REGISTER 25-5: CMxMSKCON: COMPARATOR x MASK GATING CONTROL REGISTER (CONTINUED)

bit 3 ABEN: AND Gate B Input Enable bit 1 = MBI is connected to AND gate 0 = MBI is not connected to AND gate bit 2 ABNEN: AND Gate B Input Inverted Enable bit 1 = Inverted MBI is connected to AND gate 0 = Inverted MBI is not connected to AND gate bit 1 AAEN: AND Gate A Input Enable bit 1 = MAI is connected to AND gate 0 = MAI is not connected to AND gate bit 0 AANEN: AND Gate A Input Inverted Enable bit 1 = Inverted MAI is connected to AND gate 0 = Inverted MAI is not connected to AND gate

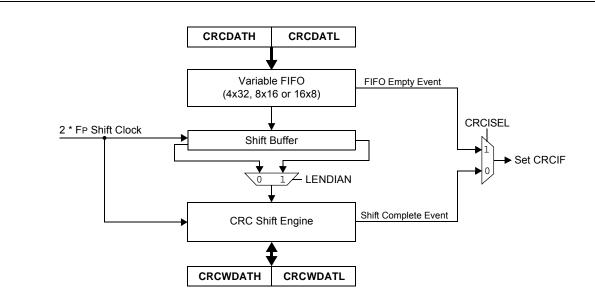

# 26.0 PROGRAMMABLE CYCLIC REDUNDANCY CHECK (CRC) GENERATOR

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Programmable Cyclic Redundancy Check (CRC)" (DS70346) of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The programmable CRC generator offers the following features:

- User-programmable (up to 32nd order) polynomial CRC equation

- Interrupt output

- Data FIFO

The programmable CRC generator provides a hardware implemented method of quickly generating checksums for various networking and security applications. It offers the following features:

- User-programmable CRC polynomial equation, up to 32 bits

- Programmable shift direction (little or big-endian)

- · Independent data and polynomial lengths

- Configurable interrupt output

- Data FIFO

A simplified block diagram of the CRC generator is shown in Figure 26-1. A simple version of the CRC shift engine is shown in Figure 26-2.

#### FIGURE 26-1: CRC BLOCK DIAGRAM

| AC CHARACTERISTICS |           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |                     |      |       |                                                                                                             |

|--------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|------|-------|-------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol    | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                           | Min. | Тур. <sup>(2)</sup> | Max. | Units | Conditions                                                                                                  |

| SY00               | Τρυ       | Power-up Period                                                                                                                                                                                                                                                                         | _    | 400                 | 600  | μS    |                                                                                                             |

| SY10               | Tost      | Oscillator Start-up Time                                                                                                                                                                                                                                                                |      | 1024 Tosc           |      |       | Tosc = OSC1 period                                                                                          |

| SY12               | Twdt      | Watchdog Timer<br>Time-out Period                                                                                                                                                                                                                                                       | 0.81 | 0.98                | 1.22 | ms    | WDTPRE = 0,<br>WDTPOST<3:0> = 0000, using<br>LPRC tolerances indicated in F21<br>(see Table 30-20) at +85°C |

|                    |           |                                                                                                                                                                                                                                                                                         | 3.26 | 3.91                | 4.88 | ms    | WDTPRE = 1,<br>WDTPOST<3:0> = 0000, using<br>LPRC tolerances indicated in F21<br>(see Table 30-20) at +85°C |

| SY13               | Tioz      | I/O High-Impedance<br>from MCLR Low or<br>Watchdog Timer Reset                                                                                                                                                                                                                          | 0.68 | 0.72                | 1.2  | μS    |                                                                                                             |

| SY20               | TMCLR     | MCLR Pulse Width (low)                                                                                                                                                                                                                                                                  | 2    | _                   |      | μS    |                                                                                                             |

| SY30               | TBOR      | BOR Pulse Width (low)                                                                                                                                                                                                                                                                   | 1    | _                   |      | μS    |                                                                                                             |

| SY35               | TFSCM     | Fail-Safe Clock Monitor<br>Delay                                                                                                                                                                                                                                                        | _    | 500                 | 900  | μS    | -40°C to +85°C                                                                                              |

| SY36               | TVREG     | Voltage Regulator<br>Standby-to-Active mode<br>Transition Time                                                                                                                                                                                                                          | _    | —                   | 30   | μS    |                                                                                                             |

| SY37               | Toscdfrc  | FRC Oscillator Start-up<br>Delay                                                                                                                                                                                                                                                        | 46   | 48                  | 54   | μS    |                                                                                                             |

| SY38               | Toscdlprc | LPRC Oscillator Start-up<br>Delay                                                                                                                                                                                                                                                       |      | —                   | 70   | μS    |                                                                                                             |

# TABLE 30-22:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMERTIMING REQUIREMENTS

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

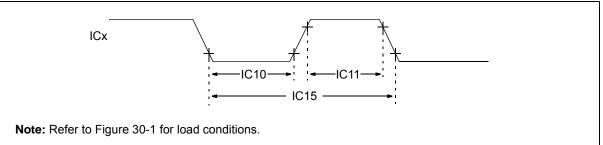

## FIGURE 30-6: INPUT CAPTURE x (ICx) TIMING CHARACTERISTICS

#### TABLE 30-26: INPUT CAPTURE x MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                                                |      |       |                                  |                                  |

|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------|-------|----------------------------------|----------------------------------|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup>                                                                                                                                                                                                                                                          | Min.                                           | Max. | Units | Conditions                       |                                  |

| IC10               | TccL   | ICx Input Low Time                                                                                                                                                                                                                                                                      | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25 |      | ns    | Must also meet<br>Parameter IC15 |                                  |

| IC11               | ТссН   | ICx Input High Time                                                                                                                                                                                                                                                                     | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25 | —    | ns    | Must also meet<br>Parameter IC15 | N = prescale value<br>(1, 4, 16) |

| IC15               | TccP   | ICx Input Period                                                                                                                                                                                                                                                                        | Greater of<br>25 + 50<br>or<br>(1 Tcy/N) + 50  | _    | ns    |                                  |                                  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

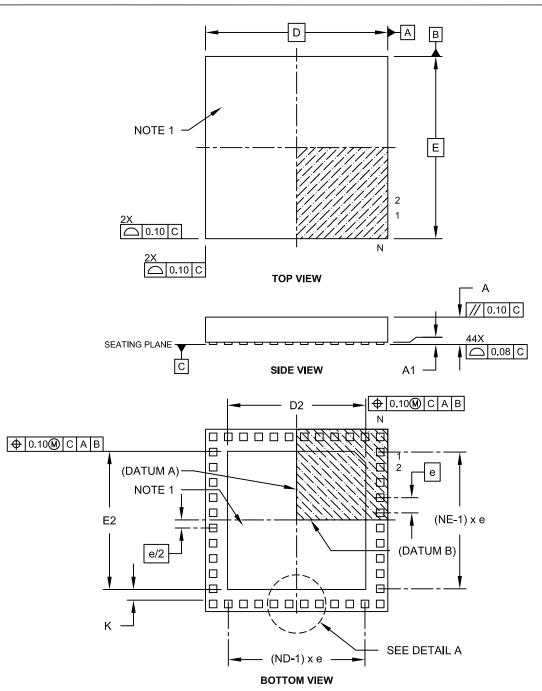

## 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-157C Sheet 1 of 2

## 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |      |          |      |  |  |

|----------------------------|-------------|------|----------|------|--|--|

| Dimension                  | MIN         | NOM  | MAX      |      |  |  |

| Contact Pitch              | act Pitch E |      | 0.65 BSC |      |  |  |

| Optional Center Pad Width  | W2          |      |          | 6.60 |  |  |

| Optional Center Pad Length | T2          |      |          | 6.60 |  |  |

| Contact Pad Spacing        | C1          |      | 8.00     |      |  |  |

| Contact Pad Spacing        | C2          |      | 8.00     |      |  |  |

| Contact Pad Width (X44)    | X1          |      |          | 0.35 |  |  |

| Contact Pad Length (X44)   | Y1          |      |          | 0.85 |  |  |

| Distance Between Pads      | G           | 0.25 |          |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103B

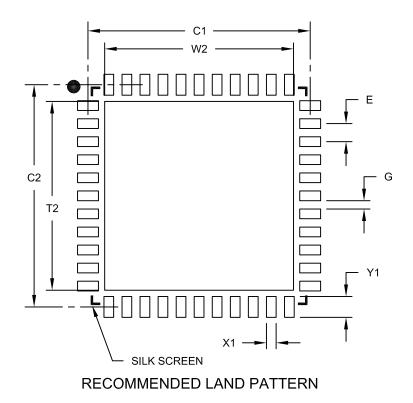

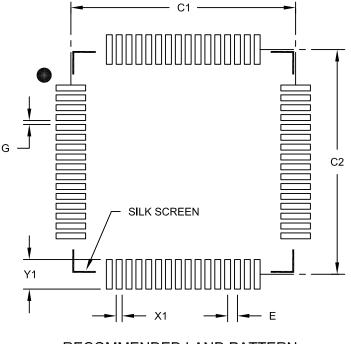

64-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | N   | <b>/ILLIMETER</b> | S        |      |

|--------------------------|-----|-------------------|----------|------|

| Dimensio                 | MIN | NOM               | MAX      |      |

| Contact Pitch            | E   |                   | 0.50 BSC |      |

| Contact Pad Spacing      | C1  |                   | 11.40    |      |

| Contact Pad Spacing      | C2  |                   | 11.40    |      |

| Contact Pad Width (X64)  | X1  |                   |          | 0.30 |

| Contact Pad Length (X64) | Y1  |                   |          | 1.50 |

| Distance Between Pads    | G   | 0.20              |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2085B

# INDEX

## Α

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| AC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                            |

| 10-Bit ADC Conversion Requirements 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5                                                                            |

| 12-Bit ADC Conversion Requirements 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3                                                                            |

| ADC Module45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9                                                                            |

| ADC Module (10-Bit Mode)461, 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3                                                                            |

| ADC Module (12-Bit Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3                                                                            |